(54) УСТРОЙСТВО ДЛЯ ВЫЧИТАНИЯ ПО МОДУЛЮ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания по модулю | 1981 |

|

SU1012242A1 |

| Арифметическое устройство в системе остаточных классов | 1983 |

|

SU1107122A1 |

| Устройство для модульного умножения | 1980 |

|

SU968808A2 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| Устройство для умножения по модулю | 1981 |

|

SU1001086A1 |

| Арифметическое устройство в системе остаточных классов | 1981 |

|

SU999050A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для умножения и сложения чисел по модулю | 1979 |

|

SU885999A1 |

Изобретение относится к вычисли. тельной технике.

Известно устройство для сложения чисел в системе остаточных классов, содержащее двоичные матрицы сложения, группы элементов ИЛИ, блок управления, комбинационные схемы, группу элементов И и соответствующие связи ГИ.

Недостаток устройства - большое количество оборудования.

Наиболее близким к предлагаемому является отличительный сумматор-вычитатель в системе остаточных классов, содержащий три двоично-десятичных операидных дешифратора с выходными кодовыми шинами, первый из которых соединен с входами первой группы ключевых схем, выходы которых связаны с входами соответствующих входных вентильных сборок, второй дешифратор выходами подключен к соответствующим входам формирователей, входы первого . и второго дешифраторов соединены с шиной управляющего сигнала, выходную вентильную сборку и импульсные усилители выходных сигналов, а Тс1кже координатно-узловые трансформаторы, пассивную кодовую линейку, и вторую группу ключевых схем, причем выходы входных вентильных сборок и формирователей соединены через соответствующие первичные обмотки координатно-узловыл трансформаторов, вторичные обмотки которых Соединены с соответствующими входами выходных вентильных сборок, выходы этих вентильных сборок связаны с первой группой входов пассивной кодовой линейки, которая по второй группе входов соединена с выходами

10 второй группы ключевых схем, соединенных по входам с соответствующими выходными шинами третьего дешифратора, выходы пассивной кодовой линейки соединены с соответствующи15ми входами импульсных усилителей выходных сигналов 2.

Однако это устройство характеризуется большим количеством оборудования.

26

Цель изобретения - уменьшение объема оборудования.

Поставленная цель достигается тем, что устройство для вычитания по модулю, содержащее первый и второй де25шифраторы, входы которых являются входами операндов устройства, первую и вторую группы ключей, первую и вторую группы, элементов ИЛИ, чтервый коммутатор, содержит выхолпоП ре30гистр, сумматор по МО.ПУЛЮ дра, трртыо

Группу элементов ИЛИ, девять элементов ИЛИ, восемь элементов И, второй коммутатор, причем i-и и(р - j - 1)-и выходы дешифраторов (i 0,1,2,.., Р-1; Р - модуль) подключены соответственно к первому и второму входам j-ro элемента ИЛИ j 1,2,.,., Р--1)/2 при Р - нечетном, J 1,...,Р/2 при Р - четном соответственно первой и второй группы, первая группа k-х выходов k О, 1, 2,..,, Р-1/2 при Р - нечетном, к О, 1, 2,.,,,Р/2 при.Р - четном соответственно первого и второго дешифраторов подключена к входам соответственно первого и второго элементов ИЛИ, выходы которых подключены соответственно к первому и второму входам сумматора по модулю два, вторая группа -х выходов г « (P-U/2+1 , . . . , Р-1 при Р - нечетном, г р/2+1, . . . ,Р-1 при Р - четном соответственно первого и второго дешифраторов подключена к входам соответственно третьего и четвертого элементов ИЛИ, выходы которых подключены соответственно к третьему и -четвертому входам сумматора по модулю два, выходы элементов ИЛИ первой и второй групп подключены к первым входам соответствующих ключей первой и второй группы, вторые входы которых объединены и подключены к выходам соответственно первого и второго элементов И, первые .входы которых подключены соответственно к нулевому и единичному выходам сумматора по модулю два, а вторые входы объединены и являются управляющим входом устрой,ства, выходы ключей первой и второй группы подключены соответственно к первой и второй группам входов соответственно первого и второго коммутаторов, j-e выходы первого и второго

коммутаторов подключены к соответствующим входам пятого элемента ИЛИ и соответстбенно к первым и третьим входам J-X элементов ИЛИ третьей группы, {P-j)-e выходы первого и второго коммутаторов подключены к. соответствующим входам шестого элемента ИЛИ и соответственно к вторым и четвертым входам j-X элементов ИЛИ третьей группы, первые входы третьего и пятого, четвертого и шестого элементов И попарно объединены и подключены к выходам соответственно пятого и шестого элементов ИЛИ, вторые входы третьего, четвертого, пятого и шестого элементов И объединены и подключены к выходу седьмого элемента входа которого подключены к выходам седьмого и восьмого элементов И соответственно, первые входы которых подключены соответственно к выходам второго и четвертого элементов ИЛИ, а вторые входы объединены и подключены к выходу первого элемента ИЛИ, выходы третьего и шестого, пятого и четвертого элементов И подключены попарно к вхбдам восьмого и девятого элементов ИЛИ соответственно, выходы которых подключены соответственно к первому и: второму входам выходного регистра,выходы элементов ИЛИ третьей группы подключены к соответствующим е-м входам е 3, 4,...,(P+i;/2+2 при Р - нечетном; Е 3,4,. ., ,Р/24-2 при Р - четном выходного регистра, выходы которого являются выходами устройства.

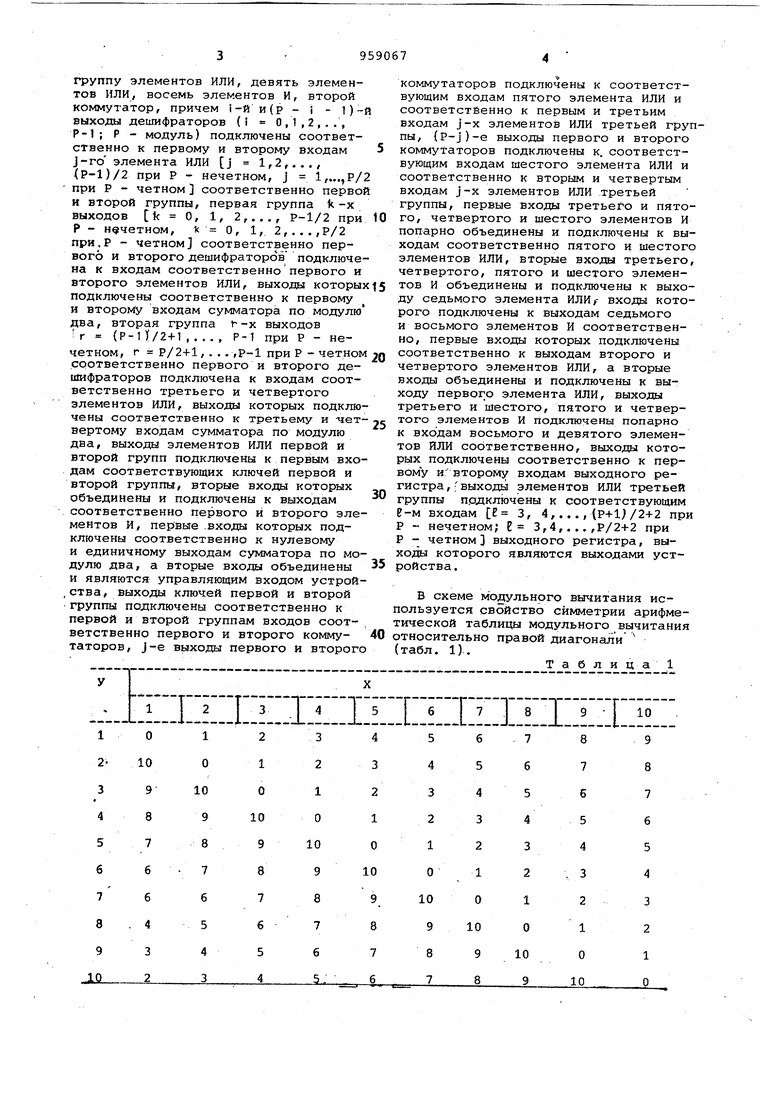

В схеме модульного вычитания используется свойство симметрии арифметической таблицы модульного вычитания относительно правой диагонали (табл. 1).

Таблица

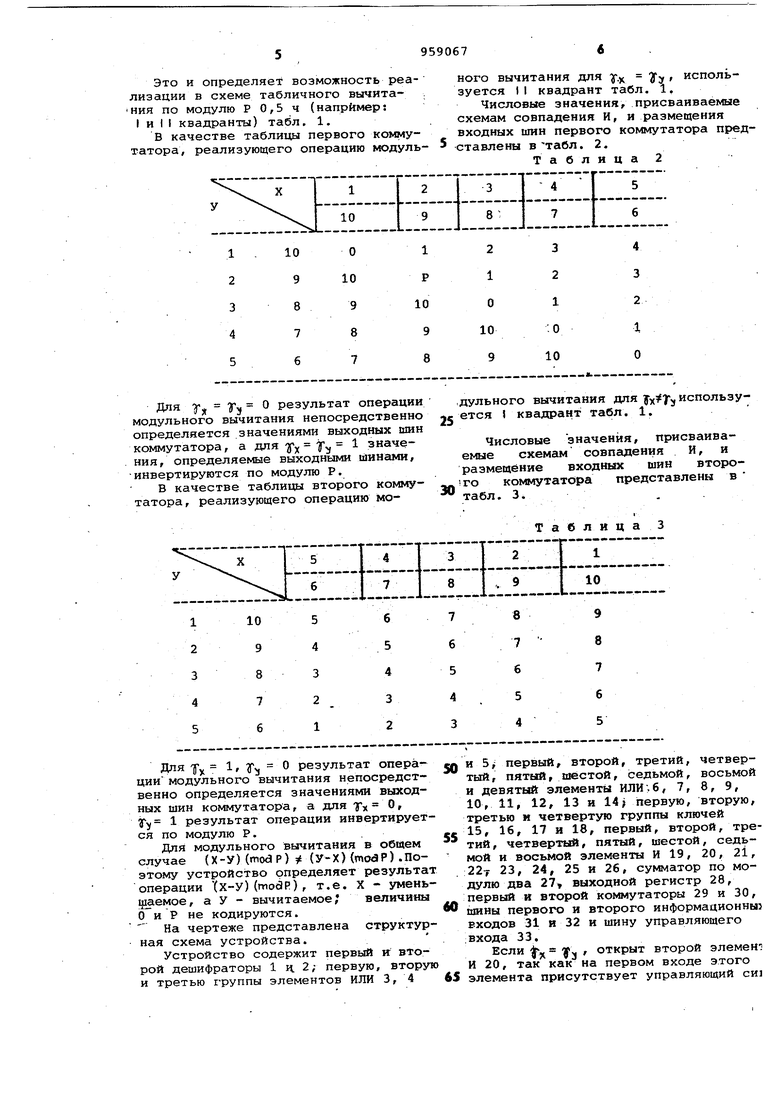

Это и определяет возможность реализации в схеме табличного вычитания по модулю Р 0,5 ч (например:Числовые значения, присваиваемые

I и I I квадранты) табл, 1. .схемам совпадения И, и размещения

В качестве таблицы первого комму-входных шин первого коммутатора предтатора, реализующего операцию модуль-5 ставлены втабл. 2.

Для Т« Тч О результат операции модульного вычитания непосредственно определяется значениями выходных шин коммутатора, а для -jpj , 1 значения, определяемые выходными шинами, инвертируются по модулю Р.

В качестве таблицы второго коммутатора, реализующего операцию моДХля Jy 1, sj О результат операции модульного вычитания непосредственно определяется значениями выходных шин коммутатора, а для Тх О, у 1 результат операции инвертируется по модулю Р.

Для модульного вычитания в общем случае (Х-У) (moap) э« (У-Х) (modP) .Поэтому устройство определяет результат операции (Х-У) () , т.е. X - уменьшаемое, а У - вычитаемое; величины О и Р не кодируются.

На чертеже представлена структурная схема устройства.

Устройство содержит первый к второй дешифраторы 1 ч. 2; первую, вторую и третью группы элементов ИЛИ 3,4

ного вычитания для y.) Уу используется П квадрант табл. 1.

Таблица2

,дульного вычитания для - - кспользу25 ется I квадрант табл. 1.

Числовые значения, присваиваемые ск&мам совпадения И, и размещение входных шин второ го коммутатора представлены в

30

табл. 3.

и 5 первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы ИЛИ;б, 7, 8, 9, 10, 11, 12, 13 и 14) первую, вторую, третью и четвертую группы ключей 15, 16, 17 и 18, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И 19, 20, 2i, 227 23, 24, 25 и 26, сумматор по модулю два 27 выходной регистр 28, первый и второй коммутаторы 29 и 30, ины первого и второго информационные входов 31 и 32 и шину управляющего входа 33.

Если 1,, , открыт второй элеменИ 20, так как на первом входе этого

элемента присутствует управляющий си1

нал шины 33, а на втором - сигнал нулевого выхода сумматора 27, Таким образом, сигналы входных операндов X и У через третью и четвертую группы ключей 17 и 18 поступают соответственно на первую и вторую группу входбв второго коммутатора 30-. Выходной сигнал коммутатора 30 поступает на вход пятого или шестого- элемента ИЛИ 10 и 11 и через элементы И 21, 22, 23 и 24, через элементы ИЛИ 13 или 14, на нулевой или,единичный вход выходного регистра 28. Одновременно сигнал с коммутатора 30 поступает на первый или второй вход-одного из элементов ИЛИ группы 5 и далее на соответствующий вход регистру 28.

Если I открыт первый элемент И 19.

Операнды X и V поступают на соответствующие входы первого коммутатоipa 29. Прохождение сигнала с коммутатора 29 аналогично прохождению сигнала с коммутатора 30.

Наличие сигнала на выходе девятого элемента ИЛИ 14 указывает необходимость инвертирования индекса кода табличного умножения - результата операции.

Таким образом, введение в состав устройства выходного регистра, коммутатора, восьми элементов И, девяти элементов ИЛИ, группы элементов ИЛИ и сумматора по модулю два позволяет уменьшить объем оборудования.

формула изобретения

Устойство для вычитания по модулю содержащее первый и второй дешифраторы, входы которых являются входами операндов устройства, первую и вторую группы ключей, первую и вторую группы элементов ИЛИ, первый коммутатор, отличающееся тем, что, с целью уменьшения объема оборудования, оно содержит выходной регистр, сумматор по модулю два,третью группу элементов ИЛИ, девять элементов ИЛИ, восемь элементов И, второй коммутатор, причем i-и иСР-т - 1)-й выходы дешифраторов (i 0,l,2i.., Р-1, R- модуль) подключены соответственно к первому и второму входам J-ro элемента ИЛИ j 1,2,.., (Р -1)/2 при Р - нечетном, j -1, 2, .. ., Р/2 при Р - четном соответственно первой и второй группы, первая группа V-x выходов t О, 1, 2,..., (р-1)/2 при Р- нечетном, V О, 1, 2,...,Р/2 при Р - четном соответственно первого второго дешифраторов подключена к входам соответственно первого и второго элементов .ИЛИ, выходы которых подключены соответственно к первому и второму входам сумматора по модулю два, вторая группа г-х выходов Г г (p-ij/i -|... Р-1 при Р - нечетном; г-р/2+1, . . . , Р-1 при Р - четном соответственно первого и второго дешифраторов подключена к входам соответственно третьего и четвертого элементов ИЛИ, выходы которых подключены соответственно к третьему и четвертому входам сумматора по модулю два, выходы элементов ИЛИ первой и второй групп подключены к первым входам соответствующих ключей первой

0 и второй группы, вторые входы которых объединены и подключены к выходам соответственно первого и второго элементов И, первые входы которых под- : ключены соответственно к нулевому и

5 единичному выходам сумматора по модулю два, а вторые входы объединены и являются управляющим входом устройства, выходы ключей первой и второй группы подключены соответственно к

0 первой и второй группам входов соответственно первого и Второго комму-- таторов, j-е выходы первого и второго коммутаторов подключены к соответстеующим входам пятого элемента 1ЛИ

5 и соответственно к первым и третьим входам j-X элементов ИЛИ третьей группы, (Р-j -е выходы первого и в торого коммутаторов подключены к соответствующим входам шестого элемента ИЛИ и соответственно к вторым и четвертым входам j-х элементов ИЛИ третьей группы, первые входы третьего и пятого, четвертого и шестого элементов И попарно объединены и подключены к выходам соответственно пятого и шестого элементов ИЛИ, вторые входы третьего, четвертого, пятого и шестого элементов И объединены и подключены к выходу седьмого элемента ИЛИ, входы которого подключены к

выходам седьмого и восьмого элементов И соответственно, первые входы которых подключены соответственно к выходам второго и четвертого элементов и)1И, а вторые входы объединены и подключены к выходу цервого элемента ИЛИ, выходы третьего и шесг того, пятого и четвертого элементов И подключены Попарно к входам ВОСБМО. го и девятого элементов ИЛИ соответственно, выходы которых подключены соответстве.нно к первому и второму входам выходного регистра, выходы элементов ИЛИ третьей группы подключены к соответствующим -м входам

5 2 3, 4,. j.,{P+l) при Р - нечетном; Е 3, 4,...,Р/2+2 при Р - четном выходного регистра, выходы которого являются Выходами устройства.

Источники информации, ; принятые во внимание при экспертизе

5 (прототип).

Авторы

Даты

1982-09-15—Публикация

1980-12-08—Подача