регистра соединен с первым входом первого умножителя, выход второго регистра подключен к вторым входам перBoho умножнтеля и первого сумматора, выход которого соединен через шестой регистр с первым входом второго умножителя, второй вход которого подклю чен к выходу четвертого регистра, выход первого умножителя подключен через седьмой регистр к первому информационному . входу второго сумматора, второй информационный вход которого через восьмой регистр подключен к выходу второго умножителя, выход ВТОрого сумматора соединен с входом делителя, выход которого подключен че103 рез девятый регистр к первому информационному входу третьего сумматора, второй информационный вход которого соединен с выходом пятого регистра, выход третьего сумматора подключен ко входу десятого регистра, выходы которого являются выходами блока, причем в первом блоке вычислений, второй управляющий вход первого сумматора соединен с первым выходом триггера знака, а во втором блоке вычислений второй управляющий вход первого сумматора соединен с вторым выходом триггера знака, вход триггера знака соединен с первым управляющим входом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования излучений гетеродина приемника | 1981 |

|

SU972525A1 |

| Устройство для моделирования излучений гетеродина | 1977 |

|

SU734735A1 |

| Устройство для моделирования полосы частот с маркером | 1981 |

|

SU970396A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ ЖИДКОСТНОГО РАКЕТНОГО ДВИГАТЕЛЯ И УСТРОЙСТВА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2085755C1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Устройство для регулирования давления | 1988 |

|

SU1674075A1 |

| Цифровой согласованный фильтр для импульсных эхо-сигналов | 1981 |

|

SU964979A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КООРДИНАТ ИСТОЧНИКА ИЗЛУЧЕНИЯ | 1981 |

|

SU1840936A1 |

| Устройство для контроля работы транспортного средства | 1986 |

|

SU1345222A1 |

1. yCTPOflCTBO ДЛЯ МОДЕЛИРОВАНИЯ РАДИОПРИЕМНИКА, содержащее . программный блок, элемент ИЛИ и сумматор, о т л- и ч а ю щ е е с я тем, что, с целью по.вышения быстродейстВИЯ, оно дополнительно содержит блок ьюделирования гетеродина, три блока моделирования полосы частот, три схе- мы сравнения кодов, реверсивный .сметчик, два- блока вычислений, причем группы выходов реверсивного счетчика и обоих блоков вычислений соединены с первой группой входов соответствующей схемы сравнения кодов, к вто0ЫМ группам входов которых подключены группа выходов сумматора и груп па информационных, входов блока моделирования гетеродина, выход которого является первым выходом устройства, выход каждой схемы сравнения кодов . соединен с информационным входом со отеетствующего блока моделирования полосы частот, выходы которых соединены соответственно с входами элемента ИЛИ, выход которого является . вторым устройства, выход Установка программного блока соединен с первь К1и управляющими, а выход у станов ка-1 - со вторыми управляю-.щи ми входакв блока моделирования гетеродина, блоков моделирования полосы частот, реверсивного счетчика и обоих блоков илчислений выхоАыУстановка-2и Установка- 3(программного блока соединены соответственно с третьими и.четвертыми управляющиьш входами блока моделирования гетеродина и блоков моделирования полосы частот, выход синхроимпульсов программного блока соединен с пятыми управляющими входами блока моделирования гетеродина блоков моделирования полосы частот и первым входом сумматора, выход Сбрх)с програмного. блока соединен с шестыми управляю§ щими входами блока моделирования гетеродина, блоков моделирования полосы частот, третьими управляю цими вхо- дами реверсивного счетмика и обоих блоков вычислений и вторым входом сумматора./ 2. Устройство по п.1, о т л и ч аю щ е е с я тем, что блок вычислений содержит элемент задержки, десять регистров,, три сумматора, два-умножитеSD Ю ля, делитель и триггер , первый и третий управляющие входы блока выэо числений соединены со входами первого :А второго, третьего, четвертого и пятого регистров, второй управляющий вход блока вычислений подключен ко входу элемента задержки, пять выходов котот рого соединены соответственно с управляющими входами первого сумматора, первого и второго умножителей, первым управляюиим входом второго сумматора, управляющим входом делителя и управляющим входом третьего сумматора,выход первого perliCTpa подключен к первому ; входу первого сумматора,выход третьего.;

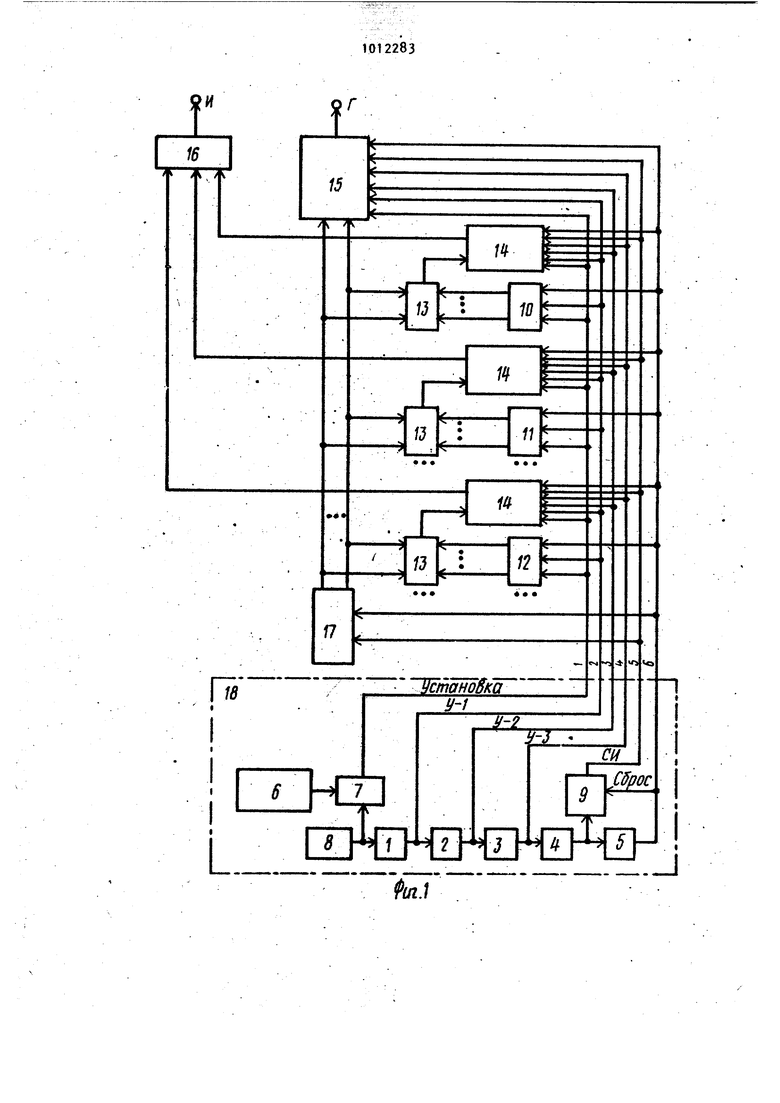

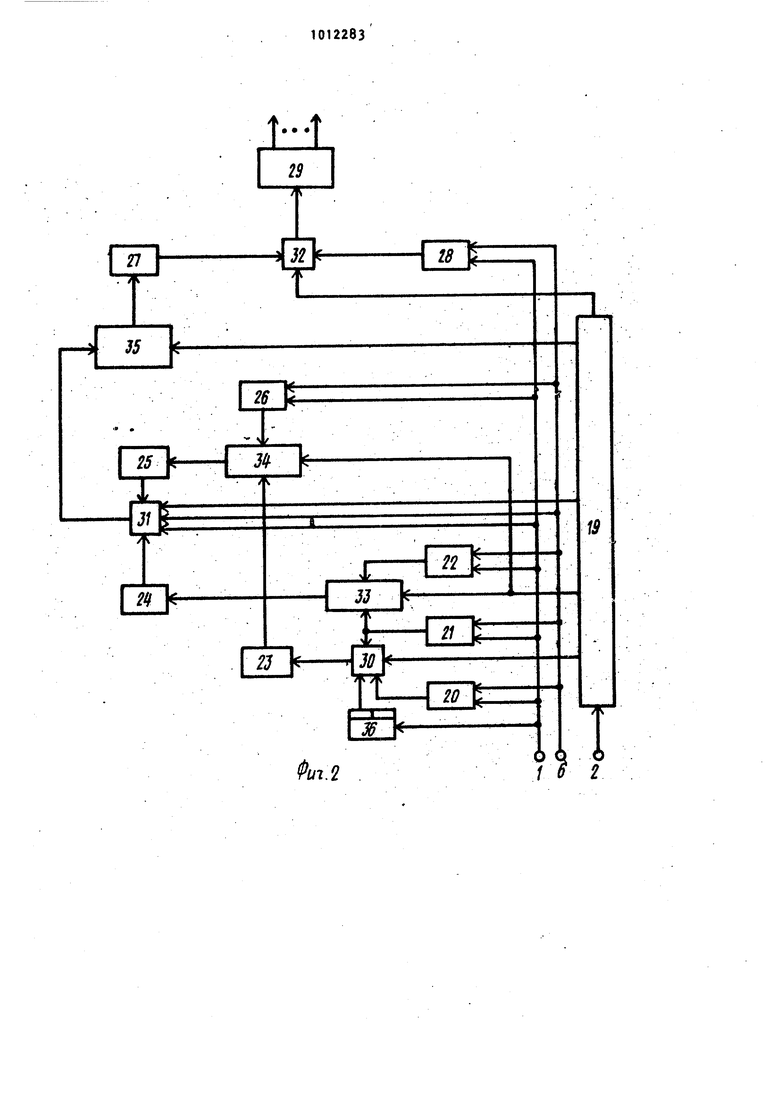

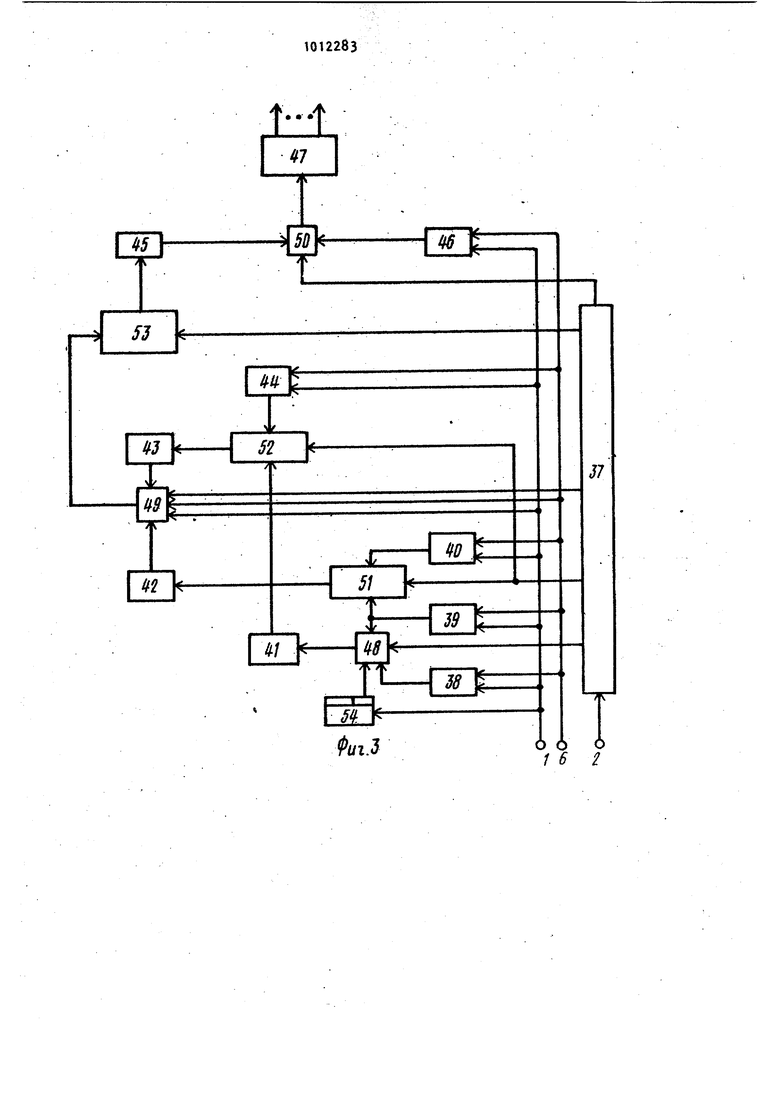

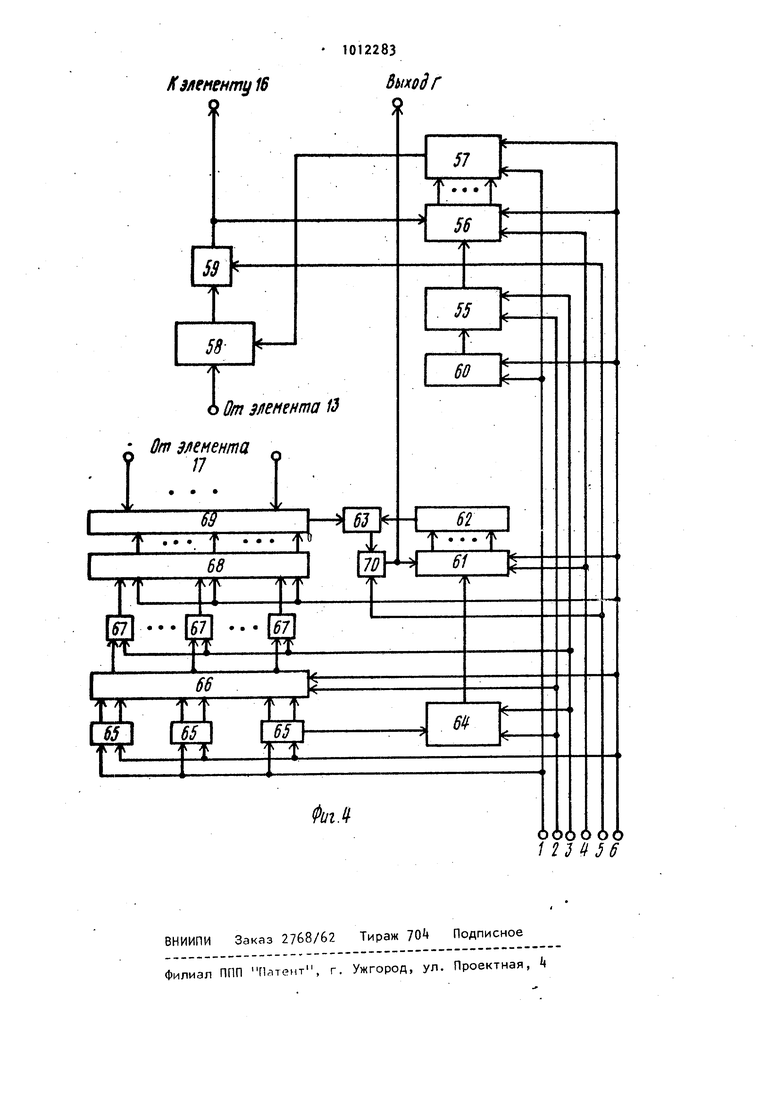

Изобретение относится к электрон ному моделированию в радиотехнике и может быть использовано для решения задач по обеспечению электромагнитной совместимости радиоэлектронных средств. /ft Известна математическая модель электромагнитного воздействия на ра диоприемник полезных и мешающих сиг налов, предназначенных для анализа электромагнитной обстановки и прогн зирования условий ЭМС РЭС tO Математическое моделирование пре полагает широкое применение ЭЦВМ. О нако использование и применение математической модели приводит к длительным и трудоемким операциям по составлению и отладке программ с привлечением квалифицированных специадистов. Наиболее близким по технической сущности к изобретению является уст рой.ство для моделирования частотног размещения каналов приема радиоприемника, содержащее блок управления, выходы Сброс и Пуск которого подключены соответственно к первому и второму входам синхронизатора,десятичные реверсивные счетчики, элемент ИЛИ, элемент И, триггеры, деся тичный счет мик, блоки формирования каналов побочного приема, сумматор и блок Оормирования полосы пропускание t 2. К недостаткам этого устройства относится длительность проведения подготовительных операций. Цель изобретения - повышение быстродействия устройства. Указанная цель достигается TeMj что в устройство., содержащее программный блок, элемент Ш1И и сумматор, дополнительно введены блок моделирования гетеродина, три блока моделирования полосы частот, три схемы сравнения кодов, реверсивный счетчик, два блока вычислений, группы выходов.реверсивного счетчика и обоих блоков вычислений соединены с первой группой входов соответствующей схемы сравнения кодов, к вторым группам входов которых подключена группа выходов сумматора и группа входов информационных входов блока моделирования гетеродина, выход которого является первым выходом устройства, выход каждой схемы сравнения кодов соединен с информационным входом.соответствующего блока моделирования, полосы частот, выходы которых соединены соответственно с входами элемента ИЛИ, выход которого является вторым выходом устройства, выход Установка программного блока соединен с (первыми управляющими, а выход Установка-1 - со вторыми управляющими входами блоков моделирования гетеродина, блоков моделирования полосы частот, реверси вного счетчика и обоих блоков вычиспежй, выходы Установка-2 и Ус таноака-3 программного блока сое{ йены соответственно с tpeTbHMM и четвертыми yпpaвляюlци 4и входами блока моделирования гетероди на и блоkoB моделирования полосы частот, выход (хнхроимпуль сов программного блоке, соединен с пятыми управляющими входами блока моделирования гетеродина, блоков моделироважя полосы частот и первым входом сумматора, выход Сброс программного блока сое динен с шестыми управляющими входаw« блока моделирования гетеродина, блоков моделирования полосы частот, третьими управляющими входами реверсивного и обоих блоков вычислений и вторым входом сумматора Кроме того, блоквычисле)ний содержит элемент задержки, десять регистров, три сумматора, два умножителя. Делитель и триггер знака, первый и третий управляющие входы блока вычислений соединены со входами пер «эго, второго,третьего, четвертого и пятого регистров, второй . управляющий вход блока вы слений подключен ко входу элемента задержки, пять выходов которого соединены соответственно с управляющими входами первого сумматора, первого и второго умножителей, первым.управляющим входом второго сумматора, управляющим входом делителя иуправляющим входом третьего сумматора, выход пер вого регистра подключен к первому входу первого сумматора, выход третьего регистра соединен с первым вхо дом первого умножителя, выход второго регистра подключен к вторым вхо дам первого умножителя и первого сум матора, выход которого соединен чере шестой регистр с первым входом второго умножителя, второй вход которого подключен к выходу четвертого регистра, выход первого умножителя подключен через седьмой регистр к первому информационному входу второго сумматора, второй информационный вход которого через восьмой регистр подключён к выходу второго умножителя, выход второго сумматора соединен с входом делителя, выход ко торого подключен через девятый- ре:гистр К первому информационному входу третьегосумматора, втедюЙ информационный вход Которого соединен с выходом пятого регистра, выход 3.4 третьего сумматора подключен ко вхоу десятого регистра, выходы KOTC JUго являются, выходами блока, причем в первом блоке вычислений,второй управляющий вход первого.сумматора соединен с первым выходом триггера знака а во втором блоке вычислений второй управляющий вход первого сумматора соединен со вторым выходом триггера знака, вход триггера знака в обоих вычислителях соединен с первым управляющим входом блока. На фиг. 1 изображена структурная схема предложенного устройства; на фиг.Z- i-схемы отдельных блоков устройства. Устройство содержит элементы 1-5 задержки, пульт 6 ввода,, блок 7 преобразования в двоичный код, элемент 8 пуска, синхронизатор 9, реверсивный счет1(к 10, первый 11 и второй 12 блоки вычислений, схемы 13 сравнения кодов, блоки 14 моделирования полосы частот, блок 15 моделирования гетеродина, элемент ИЛИ 16, сумматор 17- Группа структурно объединенных блоков 1-9 образует программный блок 18. Структурная схема блока 11 (фиг.2 содержит элемент задержки 19, первый, второй, третий, шестой, седьмой, восьмой, четвертый, девятый, пятый и десятый регистры 20-29, первый - третий сумматоры 30-32, первый и второй умножители 33 и 3, делитель 35, триггер Зб знака. Структурная схема блока 12(фиг.З} содержит элемент 37 задержки, пера й, второй, третий, шестой, седьмой восьмой, четвертый, девятый, пятый и десятый регистры ,первыйЧ третий сумматоры 48-50, первый и вто-. рой умножители 51 и 52, делитель 53 триггер Знака 5. Структурно вычислитель 12 отличается от вычислителя 11 только тем, что к сумматору 48 подключен не первый, а второй выход знакового триггер. 5. Блок 14 (фиг. 4 содержит умножитель 55, регистр-счетчик 5б дешиф- . ратор кода 57« триггер 58, элемент И 59 и регистр 60. Блок 15 содер)Ю1т регистр-Счетчик 61, дешифратор 62 кода, триггер 63, умножитель 64, регистры б5, сумматор 66, группу элементов И 67, регистр 68, схему б9 сравнения кодов, элемент И 70. Устройство работает следующим образом. . На пульте набираются числа fetf Э, , &, которые означают соответ ственно частоту настройки радиоприе ника, его промежуточную частоту, п ловины полос пропускания по основно му и побочным каналам приема, половину полосы излучения гетеродина. О новременно на пульте 6 включается с нал Верхняя настройка приемника Нижняя настдля случая fp 7 f|.-(B заройка приемника для f, висимости от конструкции моделируемого приемника). Эти числа в блоке преобразуются в двоичный код. Затем элемен.та 8 подается импульсный сигнал через цепочку 1-5 элементов задержки; При этом осуществляется заданный режим работы программного бл ка 18. По мере прохождения сигнала через цепочку 1-5, выходные шины .бл ка 18 через заданные интервалы поступают сигналы Установка У-1,У-2 У-3, СИ, Сброс. По команде Установка с блока 7 передаются коды чисел: fj, и f в блоки 10-12 и 15,Рс|2.в блок. 15; и в блоки 10-12 и 1Ц, по этой же команде в блоки 10-12 передается сигнал о знаке -f или - соответственно для случаев нижней или верх ней настройки приемника.g Через интервал времени, необходимый для выполнения команды Установка с второго выхода программного блока 18 подается команда У-1 По этой команде в блоке 15, в реверсивном счетчике 10 и в вычислите лях 11 и 12 соответственно вычисляются значения С V ilcliV}M) i - lSlciOl J}iM.lL K. причем знак + соответствует верхней настройке приемника. В блоках И вычисляются значения полос пропускания по основному и побочным каналам приема. После выполнения вычислений с тре тьего выхода программного блока 18 подается команда У-2. При этом вычисленные значения в двоичном коде передаются в выходные регистры блоков 1 4 и 15 . Затем с четвертого выхода npoi раммного блока 18 в модель гетеродина 15 и на регистры-счетчики бло283«ков lit подается команда У-3 по которой триггерные ячейки регистргсчетчиков соединяются по схеме.счетчика обратного хода. Через время задержки, необходимое для выполнения команды У-3, в программном блоке 18 включается синхро низатор 9. При этом с пятого вьхода программного блока на входы блоков 1, в блок 15 и сумматор 17 поступают синхроимпульсы, а с выхода сумматора 17 снимается код суммы. Код суммируемых синхроимпульсов постоянно сравнивается в схемах 13 сравнения кодов с коДами чисел , кппи fKvm , вычисленных и записанных в блоках 10, 11 и 12. При равенстве сравниваемых чисел со схемы13 подается сигнал в блок 1А, по которому синхроимпульсы через блок Ш начинают поступать на вход элемента ИЛИ 16. Количество импульсов,пропускаемых блоком 1, определяется величиной моделируемой полосы пропускания по основному или побочным ка.налам приема. Блок моделирования полосы частот работает следующим образом. Дешифратор 57 предварительно настраивается на код числа 0. По команде Установка в регистр 60 записывается код числа Рд/2.Через проме- жуток времени, необходимый для записи и передачи указанного числа, по втоР° У выходу программного блока 18 выдается сигнал Установка-1,поступающий в блок 55,который является командой на умножение числа Ро/2 на два. ледующая команда Установка-2 ВЫзывает передачи числа блока 55 в регистр-счетчик 56, который в ис- . ходном состоянии имеет структуру регистра. Затем в регистр-счетчик поступает команда Установка-3jj в соответствии с которой структура блока 5б предобразуется по схеме счетчика обратного хода. Моделирование полосы частот начинается с момента подачи сигнала с элемента 13 на вход триггера 58, который при этом срабатывает -и открывает элемент И 59. В результате синхроимпульсы, поступающие из блока 18, проходят через элемент И 59 на входы блоков 16 и 56.. Вычитание в счетчике продолжается до поступления FQ-ГО синхроимпульса, отсчитанного от момента открытия элемента И 59. В момент обнуления счетчика 56 7;10 на выходе дешифратора 57 образуется сигнал, который возвращает триггер 58 в исходное положение. При это элемент И 59 закрывается и поступ ление синхроимпульсов на вход элемента 16 прекращается. Работа блоков 1, соединенных через схемы 13 с вычислителями 11 и 12 отличается от изложенного только .тем, что продолжается на интервале следования Fp синхроимпульсов. Поступившие с блоков 1A синхроимпульсы подаются через элемент ИЛИ 16 на выход устройства. Процесс моделирования излучения гетеродина происходит независимо от моделирования каналов радиоприема ка поступлении на вход блока 15 ffсинхроимпульсов,отсчитанных от момента включения синхронизатора, с вы хода блока 15 на выход устройства Подается FQ синхроимпульсов, моделирующих излучение гетеродина. Блок 15 работает следующим лбразом. : Дешифратор предварительно настра(Ивается на нулевой код. По команде Установка -В регистрах 65 записываются коды чисел fj., ир|5|2.2атем по команде Установка-1 в сумматоре 66 вычисляется значение частоты tfnp4FG|2)-. Одновременно в блоке 6ч число %/2 умножается на два. По Уста новка-2 числоР(,|1записывается в регистр 68, а число FQ-в регистре-счет чике б1, который в исходном состоя- НИИ соединен по схеме регистра. По команде Установка-3 он соединяется по схеме обратного хода. Блок 15 включается в процесс моделирования в момент прохождения f -го синхроимпульса, отсчитанного от моьюнта включежя синхронизатора 9. В указанный момент коды чисел, за писанные в блоках17 и 68, совпадают ив блоке б9 вырабатывается сигнал, который с пЬмоцью т|риггера 63 откры. вает элемент И 70. С момента его открытия через него проходит FQ синхроимпульсов, которые поступают на выход устройств и на вход блока 61 . Счетчик обратного хода блока 6l обнуляется на синхроимпульсе. При этом в дешифраторе кода 62 образуется сигнал который возвращаеУ триггер 63 в исходное состояние, элемент И 70 закрывается и процесс моделиро38вания излучения гетеродина прекраща ется.. Таким образом, за счет работы группы блоков 10, 13 и 1 t с выхода блоков Ц на вход элемента подаются синхроимпульсы с f. - -го по %-v -и, которые моделируют основной канал приема. Группы блоков 11Т 13, 12, 13, U моделируют побочные каналы приема передачей на выход устройства, .синхроимпульсов с Номера/ c v / np j-p no номер Р с HOMepd il b :5) i1 la ПО номер cOft-i) , Ь IVMО. ; рлок 11 работает следующим образом. В соответствии с командой Установка из программного блока 18 пере даются коды: числа 1 в регистр 20, числа п в регистр 21, числа f в регистр 22, числа fnp регистр 26 и числа Fp|l в регистр 28. Одновременно в сумматор 31 передается сигнал знака, переводящий его в ре«им суммирования или вычитания в зависимости от нижней или верхней настройки моделируемого приемника. Включается также знаковый триггер 36, подготавливающий сумматор 30 к операции сложежя. По команде Установка-1 импульсный сигнал поступает на вход элемента 19 задержки. С первого выхода этого элемента сигнал поступает в сумматор 30, в котором производится сложение чисел п и.1, записанных в регистрах 21 и 20. Результат суммирования передается в регистр 23. По сигналу, поступившему с второго выхода элеменУа , осуществляется перемножениь; чисел п и f,, хранящихся в регистрах 21и 22, а в блоке 3 перемножаются числа п+1 записанные в регистрах 23 и 26. Результаты умножения с блоков 33 и 3 передаются соответственно в регистры 2k и 25. По сигналу, поступившему с третье.го выхода элемента задержки, в сумматоре 31 производится операция сложения или вычитания (в зависимости от ранее поданного сигнала) чисел . nf. и (n+l)f,,p, хранимых в регистрах 2Ц и 25. Результат вычисления,по.5 -,v лученный в сумматоре ЗЦпередаетСИ в блок 35 в котором по сигналу с че вертого выхода элемента задержки 19 осуществляется деление на число т. После делеййя результат вычислений записывается в регистр 27. По сигналу с пятого выхода элемен та задержки в сумматоре 32 из числа хранимого в регистре 27 вычитается число, записанное в регистре 28. РеЗУЛЬТаТ выч4та А1« С-()$йР .Mf.apa. m .- . -.. дается в выходной регистр 29 вычис лителя 11. нкционированйе бл.ока 12 . гично изложенному,за исключением того, что в сумматоре ЦБ осуществляется не сложение, а вычитание чисел Нп и 1.. . 285.10 Таким образом, за счет работы блоков 10, 13 lA и 11, 13, Ни 12, 13, liic выходов блоков 1 на вход элемента ИЛИ 16 и далее на выход устрой16 и ства подаются серии синхроимпульсов, с помощью которых моделируются основной и побочный каналы приема р иоприемника. . По окончании цикла моделирования с шестого выхода программного 18 подается команда Сброс, приводящая элементы устройства в исходное состояние. Положительный эффект изобретения заключается в увели.чении быстродействия устройства, которое дбстигат ется за счет исключения подготовительных операций моделирования.

1

16

/ . / V

15

« Ш

f

fi/

/

k-r

f

/J

f4f

.г

12

/3

М1}Ч

26 t

ч

18

IS

1 6 2

Кзл менту 16

ды)(одг

Щ1Г -

Авторы

Даты

1983-04-15—Публикация

1981-06-17—Подача