Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах статистической обработки геоакустических или радиолокационных сигналов.

Известен цифровой фильтр, реализующий алгоритм цифровой фильтрации на основе решения линейных разностных уравнений с постоянными коэффициентами и содержащий дискретизатор, аналого-цифровой преобразователь, умножители, элементы задержки и сумматор Г13.

Выбор временной (импульсной ) или частотной характеристики для построения такого фильтра предполагает априорные сведения о временных или частотных параметрах импульсных эхосигналов, а это, в свою очередь, требует предварительного статистического анализа фильтруемых сигналов и шумов, действующих на входе фильтра.

Наиболее близок к предложенному цифровой фильтр, содержащий элементы задержки, умножители, сумматор, причем элементы задержки соединены последовательно, кроме того, выход каждого элемента задержки соединен с входом соответствующего умножителя,на

вторые Ьходы которого подаются весовые коэффициенты, выходы умножителей соединены с соответствующими .входам11 сумматора Выход сумматора является выходдм цифрового фильтра 2.

Недостатком такого фильтра является то, что для каждой реализации импульсных эхо-сигналов необходимо подбирать весовые коэффициенты вре10менной характеристики фильтра, что приводит к увеличению времени ofSpaботкИ эхо-сигналов.

Цель изобретения - увеличение точности фильтрации.

15

Поставленная цель достигается тем, что в цифровой фильтр для импульсных эхо-сигналов, содержащий умножитель, . выход которого соединен с первым входом сумматора, выход которого являет20ся выходом фильтра, аналого-цифровой преобразователь, вход которого является входом фильтра, введены блок управления, блок записи, блок анализа знаков, первый и второй блоки памяти,

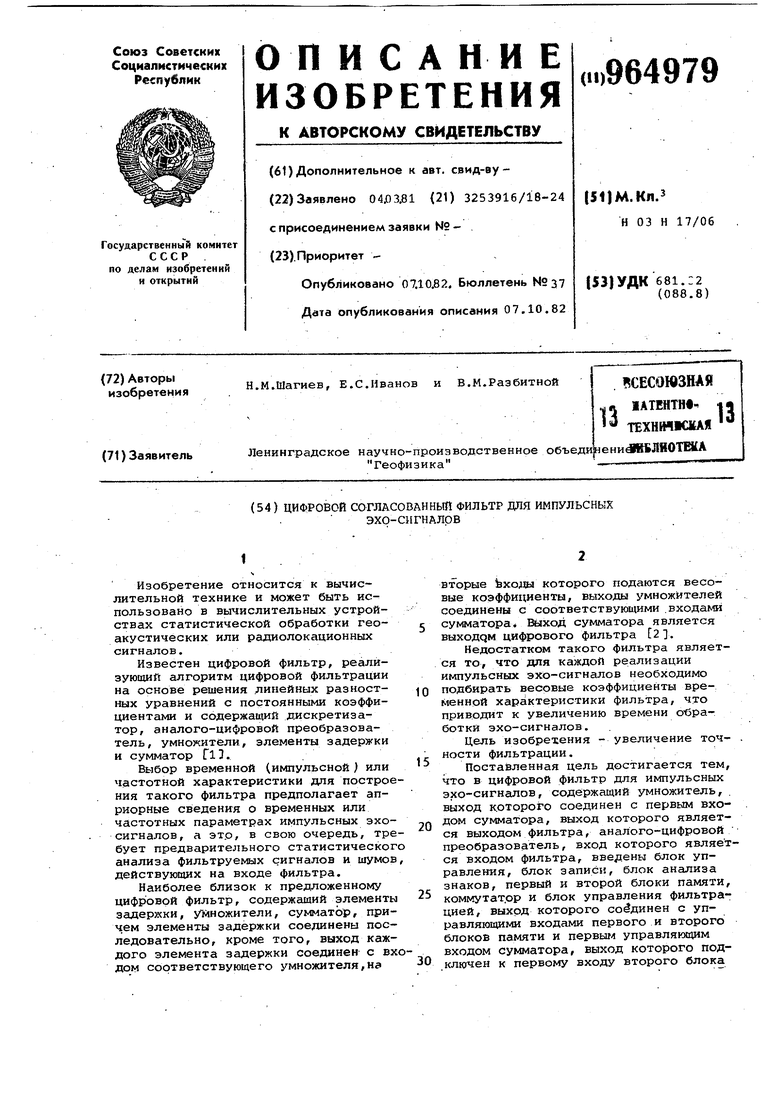

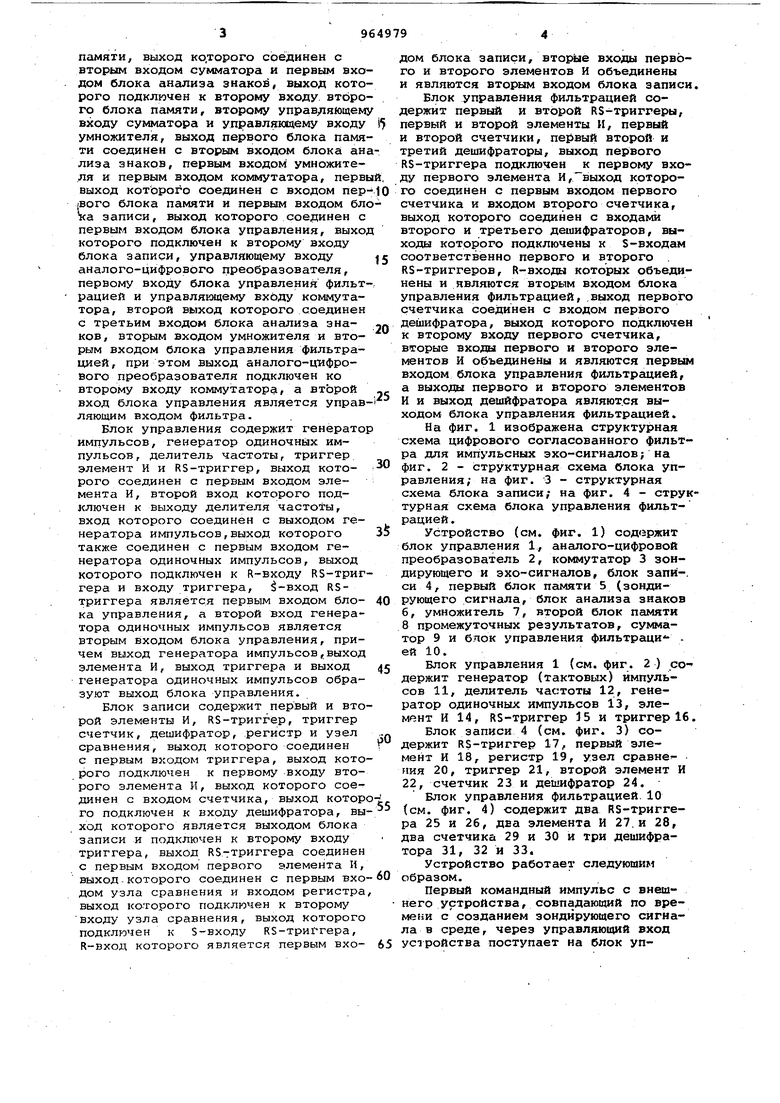

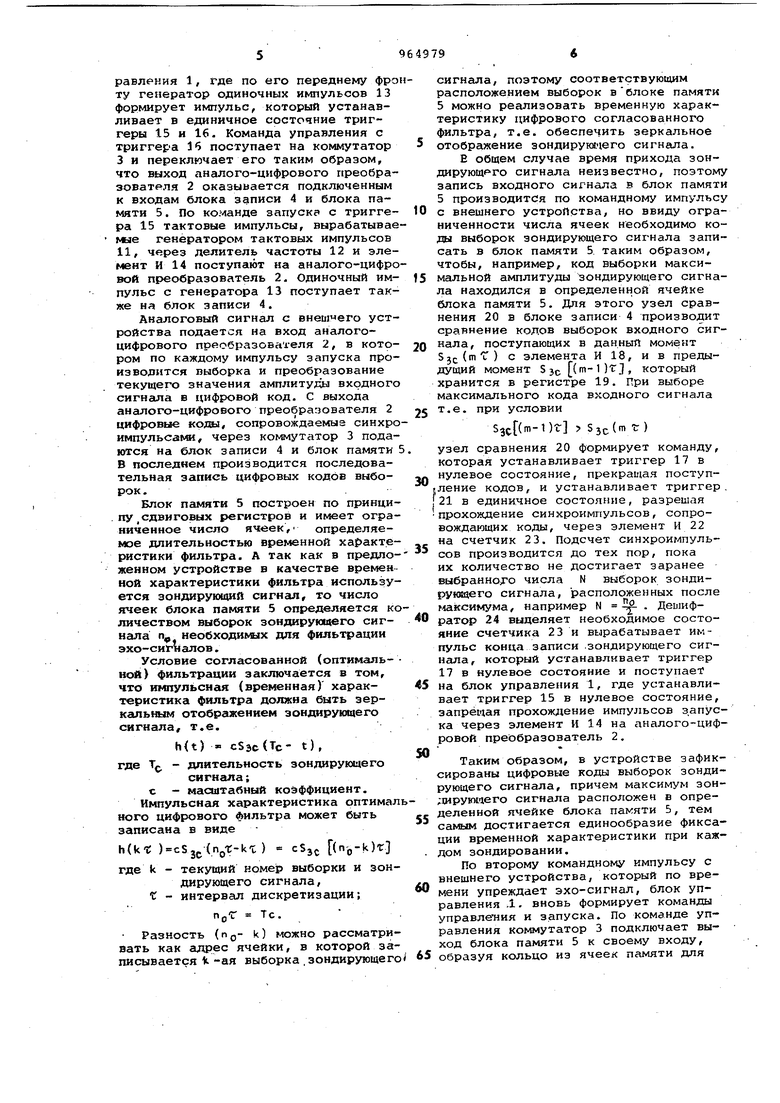

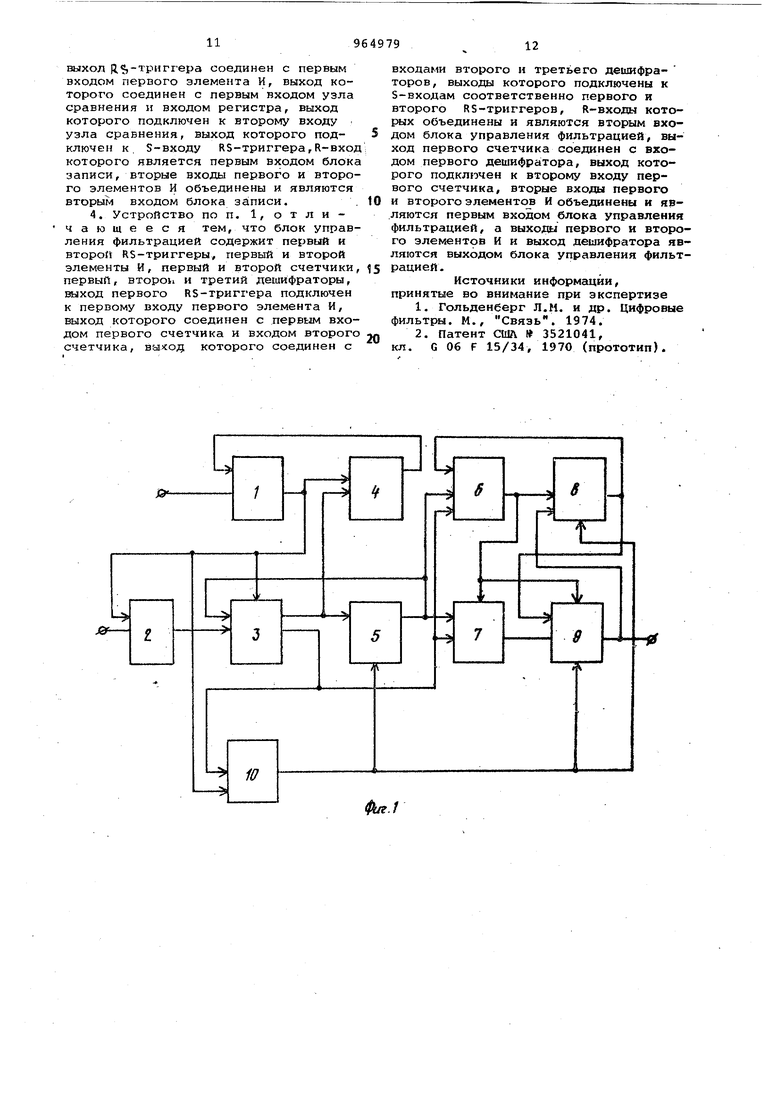

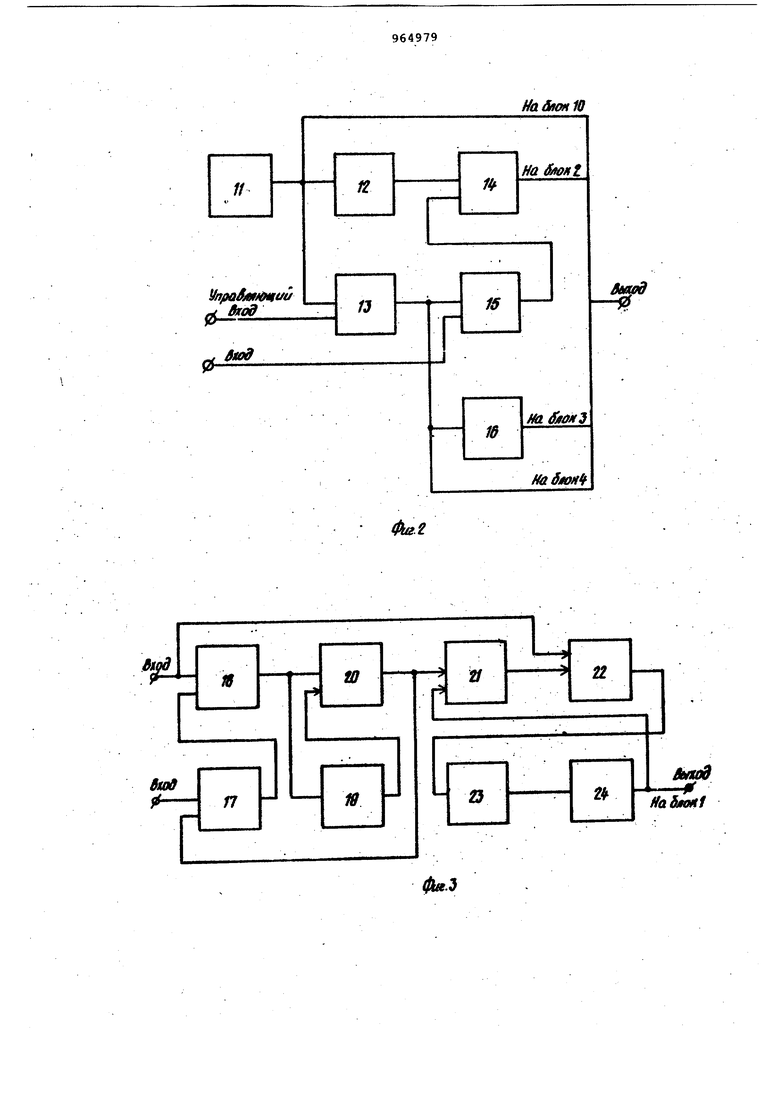

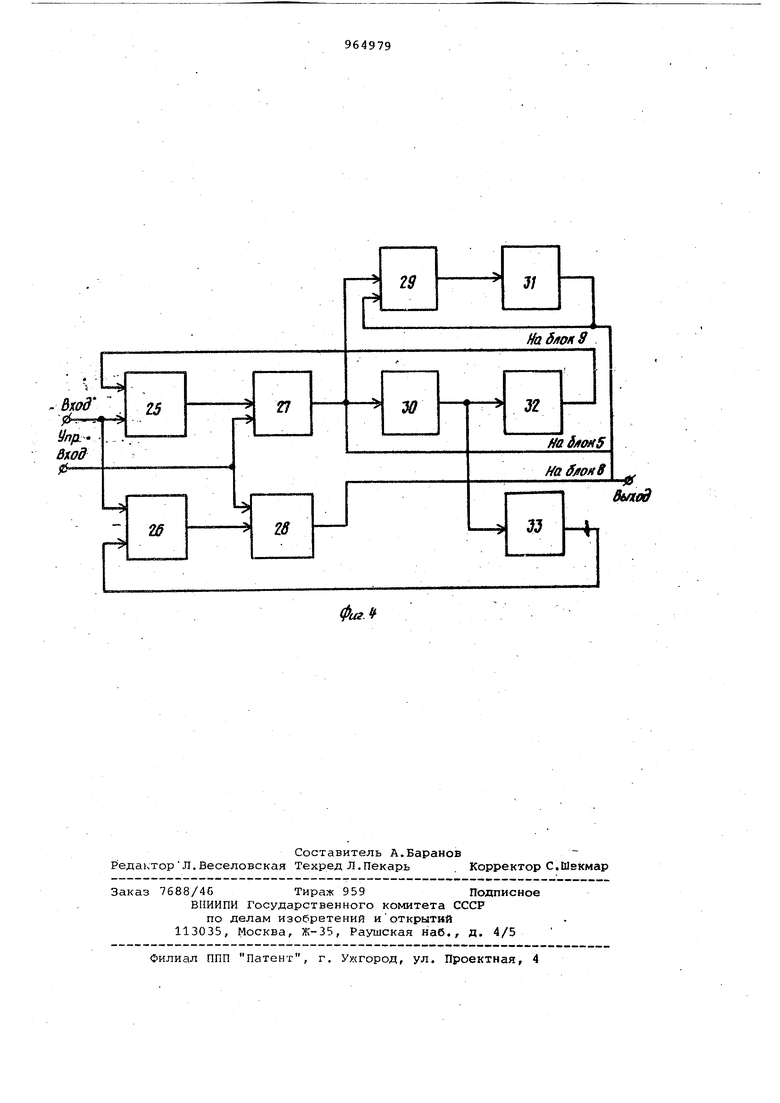

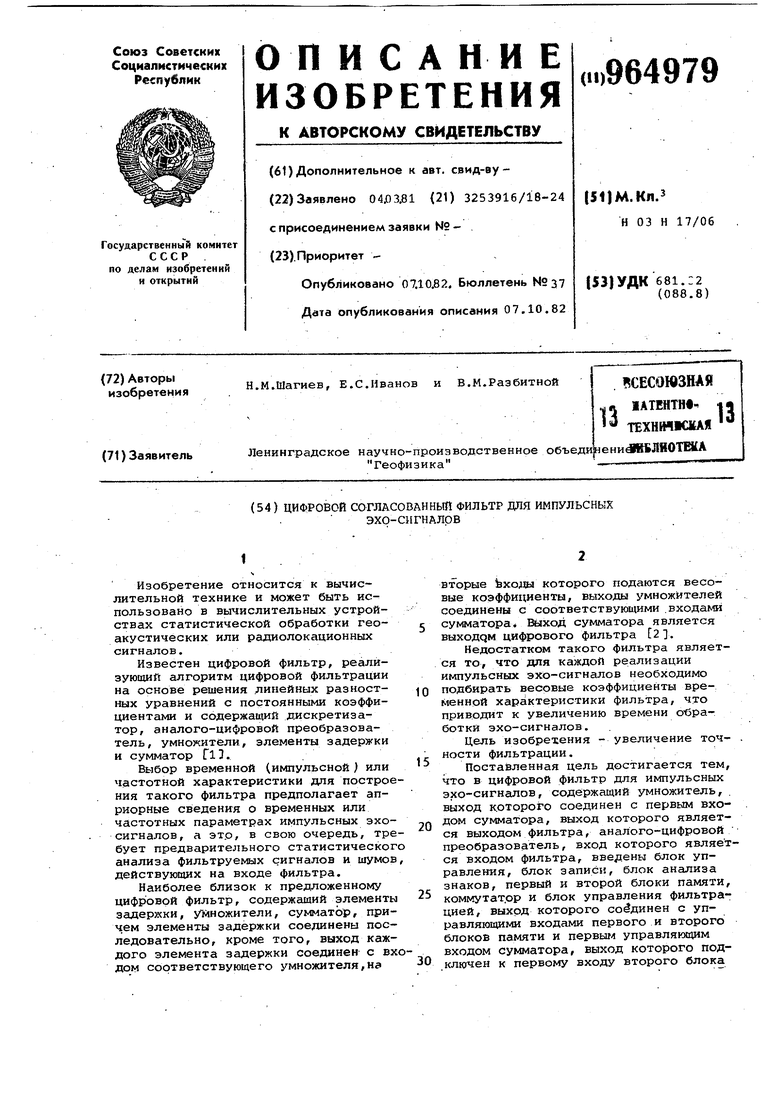

25 коммутат.ор и блок управления фильтрацией, выход которого соединен с управляющими входами первого и второго блоков памяти и первыгч управляющим входом сумматора, выход которого под30клктчен к первому входу второго блока памяти, выход которого соединен с вторым входом сумматора и первым вхо дом блока анализа знаков, выход кото рого подключен к второму входу второ го блока памяти, второму управ/1я1ощем входу сумматора и управляющему входу умножителя, выход первого блока памя ти соединен с вторым входом блока ан лиза знаков, первым входом умножителя и первым входом коммутатора, первы выход котЬрого соединен с входом пер iBoro блока памяти и первым входом бло ка записи, выход которого соединен с первым входом блока управления, выход которого подключен к второму входу блока записи, управляющему входу аналого-цифрового преобразователя, первому входу блока управления фильтрацией и управляющему входу коммутатора, второй выход которого соединен с третьим входом блока анализа знаков, вторым входом умножителя и вторым входом блока управления фильтрацией, при этом выход аналого-цифрового преобразователя подключен ко второму входу коммутатора, а второй вход блока управления является управляющим входом фильтра. Блок управления содержит генератор импульсов, генератор одиночных импульсов, делитель частоты, триггер элемент И и RS-триггер, выход которого соединен с первым входом элемента И, второй вход которого подключен к выходу делителя частоты, вход которого соединен с выходом генератора импульсов,выход которого также соединен с первым входом генератора одиночных импульсов, выход которого подключен к R-входу RS-триггера и входу триггера, -вход RSтриггера является первым входом блока управления, а второй вход генератора одиночных импульсов является вторым входом блока управления, причем выход генератора импульсов,выход элемента И, выход триггера и выход генератора одиночных импульсов образуют выход блока управления. Блок записи содержит первый и второй элементы И, RS-триггер, триггер счетчик, дешифратор, регистр и узел сравнения, выход которого соединен с первым входом триггера, выход которого подключен к первому входу второго элемента И, выход которого соединен с входом счетчика, выход которо го подключен к входу дешифратора, вы ход которого является выходом блока записи и подключен к второму входу триггера, выход RS-триггера соединен с первым входом первого элемента Н, выход - которого соединен с первым входом узла сравнения и входом регистра выход которого подключен к второму входу узла сравнения, выход которого подключен к S-вхолу RS-триГгера, R-вход которого является первым входом блока записи, вторые входы первого и второго элементов и объединены и являются вторым входом блока записи. Блок управления фильтрацией содержит первый и второй RS-триггеры, первый и второй элементы И, первый и второй счетчики, первый второй и третий дешифраторы, выход первого RS-триггера подключен к первому входу первого элемента И,выход которого соединен с первым входом первого счетчика и входом второго счетчика, выход которого соединен с входами второго и третьего дешифраторов, выходы которого подключены к S-входам соответственно первого и второго . RS-триггеров, R-входы которых объединены и являются вторым входом блока управления фильтрацией, .выход первого счетчика соединен с входом первого дешифратора, выход которого подключен к второму входу первого счетчика, вторые входы первого и второго элементов И объединены и являются первым входом блока управления фильтрацией, а выхода первого и второго элементов И и выход дешифратора являются выходом блока управления фильтрацией. На фиг. 1 изображена структурная схема цифрового согласованного фильтра для импульсных эхо-сигналов; на фиг. 2 - структурная схема блока управления; на фиг. 3 - структурная схема блока записи; на фиг. 4 - структурная схема блока управления фильтрацией. Устройство (см. фиг. 1) содзржит блок управления 1, аналого-цифровой преобразователь 2, коммутатор 3 зондирующего и эхо-сигналов, блок запи-. си 4, первый блок памяти 5 (зондирующего сигнала, блок анализа знаков б, умножитель 7, второй блок памяти 8 промежуточных результатов, сумматор 9 и блок управления фильтраци . ей 10. Блок управления 1 (см. фиг. 2 ) содержит генератор (тактовых) импульсов 11, делитель частоты 12, генератор одиночных импульсов 13, элемент И 14, RS-триггер 15 и триггер 16. Блок записи 4 (см. фиг. 3) содержит RS-триггер 17, первый элемент И 18, регистр 19, узел сравне ния 20, триггер 21, второй элемент И 22, счетчик 23 и дешифратор 24. Блок управления фильтрацией. 10 (см. фиг. 4) содержит два RS-триггера 25 и 26, два элемента И 27. и 28, два счетчика 29 и 30 и три дешифратора 31, 32 и 33. Устройство работает следующим образом. Первый командный импульс с внешнего устройства, совпадающий по времени с созданием зондирующего сигнала в среде, через управляющий вход усэройства поступает на блок управления 1, где по его переднему фро ту генератор одиночных импульсов 13 формирует импульс, который устанавливает в единичное состояние триггеры 15 и 16. Команда управления с триггера 16 поступает на коммутатор 3 и переключает его таким образом, что выход аналого-цифрового преобразователя 2 оказывается подключенным к входам блока записи 4 и блока памяти 5. По команде запуска с триггера 15 тактовые импульсы, вырабатывае мые генератором тактовых импульсов 11, через делитель частоты 12 и элемент И 14 поступают на ангшого-цифро вой преобразователь 2. Одиночный импульс с генератора 13 поступает также на блок записи 4. Ансшоговый сигнал с устройства подается на вход аналогоцифрового преобразователя 2, в котором по каждому импульсу запуска производится выборка и преобразование текущего значения амплитуды входного сигнала в цифровой код. С выхода анёьлого-цифрового преобрагзователя 2 цифровые коды, сопровождаемый синхро импульсами, через коммутатор 3 подаются на блок записи 4 и блок памяти В последнем производится последовательная запись цифровых кодов выборок.. Блок Пс1мяти 5 построен по принци. пу,сдвиговых регистров и имеет ограниченное число ячеек, определяемое длительностью временной характеристики фильтра. А так как в предложенном устройстве в качестве времен ной характеристики фильтра используется зондирующий сигнал, то число ячеек блока памяти 5 определяется ко личеством выборок зондирующего сигнала п необходимых для фильтрации эхо-сиГналов, Условие согласованной (оптимальной) фильтрации заключается в том, что импульснгм (временная) характеристика фильтра должна быть зеркальным отображением зондирукяцего сигнала, т.е. ) - с5эс(Тс- t), где Т - длительность зондирукяцего сигнала; с - масштабный коэффициент. Импульсная характеристика оптимал ного цифрового фильтра может быть записана в виде h(ki; )cS3(njjt-kt ) cSjc Г( где k - текущий номер выборки и зондирующего сигнала, t - интервал дискретизации; Тс. Разность (пр- k) можно рассматривать как адрес ячейки, в которой записывается V -ая выборка.зондирующего сигнала, поэтому соответствующим расположением выборок вблоке памяти 5 можно реализовать временную характеристику цифрового согласованного фильтра, т.е. обеспечить зеркальное отображение зондиругачего сигнала. Е общем случае время прихода зондирующего сигнала неизвестно, поэтому запись входного сигнала в блок памяти 5 производится по командному импульсу с внешнего устройства, но ввиду ограниченности числа ячеек необходимо коды выборок зондирующего сигнала записать в блок памяти 5. таким образом, чтобы, например, код выборки максимальной амплитуды зондирующего сигнала находился в определенной ячейке блока памяти 5. Для этого узел сравнения 20 в блоке записи 4 производит сравнение кодов выборок входного сигнала, поступающих в данный момент Sjc(mT) с элемента И 18, и в предыдущий момент S зс (т-1)Т, который хранится в регистре 19. При выборе максимального кода входного сигнала т.е. при условии S3cf(ni-Of 5зс(п t ) узел сравнения 20 формирует команду, которая устанавливает триггер 17 в нулевое состояние, прекращая поступление кодов, и устанавливает триггер. 21 в единичное состояние, разрешая прохождение синхроимпульсов, сопровождающих коды , через элемент И 22 на счетчик 23. Подсчет синхроимпульсов производится до тех пор, пока их количество не достигает заранее выбраннО)ГО числа N выборок зондируквдего сигнала, расположенных после максимума, например N . Дешифратор 24 выделяет необходимое состояние счетчика 23 и вырабатывает импульс конца записи .зондирующего сигнала, который устанавливает триггер 17 в нулевое состояние и поступает на блок управления 1, где устанавливает триггер 15 в нулевое состояние, запрещая прохождение импульсов з.апуска через элемент И 14 на аналого-цифровой преобразователь 2. Таким образом, в устройстве зафиксированы цифровые коды выборок зондирующего сигнала, причем максимум зон;1ируюк1его сигнала расположен в определенной ячейке блока памяти 5, тем самым достигается единообразие фиксации временной характеристики при каждом зондировании. По второму командному импульсу с внешнего устройства, который по времени упреждает эхо-сигнал, блок управления Л. вновь формирует команды управле-ния и запуска. По команде управления коммутатор 3 подключает выход блока памяти 5 к своему входу, образуя кольцо из ячеек памяти для циркуляции по ним кодов выборок зондирующего сигнала, и выход аналогоцифрового преобразователя 2 - к вхо дам блока анализа знаков б, умножителя 7 и блока управления фильтрацие 10. По команде запуска в блоке управления 1 формируются импульсы запуска аналого-цифрового преобразователя 2 с прежней частотой следования f 3. Аналоговыйсигнал с внешнего устройства помается на аналого-цифровой преобразователь 2, в котором по кажд му импульсу запуска производится вы борка и преобразование текущего значения амплитуды входного сигнала в цифровой код. G выхода аналого-цифрового преобразователя 2 через коммутатор 3 цифровые кода подаются на первый вход умножителя 7, знак кода выборки входного- сигнала поступает на блок анализа знаков б, а синхроимпульсы, сопровождэмщие цифровой код,- на блок управления фильтрацией 10. По каждому синхроимпульсу тригге ры 25 и 26 устанавливаются в единичвое состояние, разрешая прохождение через элемент И 27 последовательности из (по+ 1) тактовых импуль сов, частота следования которых fjдрлжна быть больше в (пд+1) раз, чем частота импульсов запуска f, г.е, f т () f 3 . Последовательность из (пд4-1) трктовых импульсов с элемента И 27 подается на счетчик 29 и бло памяти 5, где она используется для обеспечения циркуляции кодой выборок зондирующего сигнала. Но так как блок памяти 5 имеет Пдячеек, а ,такто вых импульсов (), то-в нем производится один дополнительный сдвиг кодов выборок зондирующего сигнала в каждом цикле запуска аналого-цифрово го преобразователя 2. Такой режим циркуляции необходим для реализации алгоритма цифровой согласованной фил рации, В блоке управления фильтрацИ ей 10 вырабатывается также скользящий импульс, который подается на су матор 9 для вывода результата фильтр ции, который в каждом цикле запуска образуется в разные такты (скользит по тактам), т.е. в первом цикле он образуется в пд-омтакте, во втором ци ле - в (п0- 1)-ом такте и т.д., в Пд-ом цикле - в первом такте, а в (по+ 1)-ом цикле - снова в пдтакТе, {П{1+ 2)-ом цикле - в (п-- 1)-ом такте и т.д. Скользящий импульс вырабатывает ся с помощью счетчика 29 с дешифратора nj,-го импульса 31. Навход счетчика 29 подается последовательность из (по+ 1) импульсов через элемент И 27. При вряцелении дешифратора 31 По-го импульса он подается на сумматор 9 лля вывода результата фнльтрации, и задним фронтом этого ийпульса сбрасывается счетчик 29, После сброса н счётчик поступает еще один импульс с элемента И 27.. В следующем цикле запуска счетчик 29 начинает считать уже с первого импульса, а сбрасывается ( 1)-м импульсом,после чего в него записываются уже два импульса и т.д./ Последовательности из (пр+1) тактовых импульсов вырабатываются в блоке управления фильтрацией с помощью счетчика 30 и дешифраторов 32 и 33. Дешифратор. 33 выделяет состояние счетчика 30 после прихода о -го импульса и вырабатывает импульс, которым устанавливает триггер 26 в нулевое состояние и запрещает прохождение импульсов через элемент И 28. Таким образом, с элемента И 28 выходит последовательность из «о тактовых импульсов. Дешифратор 32 выделяет сое тояние счетчика 30 после прихода (по+ 1)-го импульса и вырабатывает импульс, которым устанавливает триггер 25 в нулевое состояние и.запрещает прохождение тактовых импульсов через элемент И 27 на счетчик 30 и на выход блока управления фильтрацией. С блока управления фильтрацией 10 тактовые импульсы через элемент И 28 подаются на блок памяти В, где они используются для записи цифровых коДов, поступающих с сумматора 9, и считывания кодов промежуточных результатов на сумматор 9 И знака указанных кодов на блок анализа знаков б. В зависимости от 2 наков кодов выборок входного(S i gn -Sjx) и зондирующего (Sign 83)сигналов,а также знака кода промежуточного ре- зультата (Sign Snp) блок анализа знаков 6 вырабатывает коман- « ду в на считывание прямого или обатного кода с умножителя 7 на суматор 9, команду Q- на считывание пря- мого или обратного кода с сумматора 9 на блок 8 и команду + блока памя ти 8 на сумматор 9 согласно следующим огическим выражениям: , Cm Sign 5ц,Ф Sign Cm S i gn Spj, f Cm Sign Spp g (Cm Sign S p+CJiir S i gn Snp ) P где Cm - знак произведения .; P - сигнал переноса сумматора. При каждом цикле запуска код выорки входного сигнала Sgjj(iT ) оступает на один из входов умножиеля 7 и сохраняется на нем до приода кода следу ощего цикла излучеия SBX ( +l)t . На второй вход умножителя 7 при аждом цикле запуска подаются пд одов выборок зондирующего сигнала. умножителе 7 производится последовательное умножение кода выборки входного сигнала Sg(IC ) на все Пд кодов выборки зондирунщего сигнала эс (о l)гJ Парные произведения с выхода умножителя 7 подаются на один из входов сумматора 9, на второй вход которого поступают коды промежуточных результатов из блока памяти 8. Промежуточные (частичные суммы парных произведений с выхода сумматора 9 записываются в блок памяти 8. В один из тактов,, соответ ствуюций скользящему импульсу, код промежуточной сумьай выводится с сумматора 9 на выход устройства, а в этот момент в блок памяти 8 записывается нулевой код, т.е. происходит сброс одной из ячеек блока памя ти 8. В процессе работы устройства реализуется следуклчий алгоритм цифровой согласованной фильтрации f/i S,-t(no-k)t3sJ(n-k)t где п - текущий номер выборки входного сигнала. Причем, при п k « О, Таким образом, перезапись зондирующего сигнала при каждом зондировании и использовании его кодов выборок в качестве импульсной (временной)характеристики фильтра создае в сравнении с прототипом оптимальный режим фильтрации для каждой реализации импульсных эхо-сигналов.. Выбор максимсшьного значения зондирующего сигнала и запись его в определенную ячейку блока питания независимо от времени прихода обеспечивает стабильность иктульсной характеристики цифрового фильтра для каждои реализации эхо-сигнала. Выработка скользящего, импульса позволяет непосредственно в процессе фильтраци выводить резуль-таты на внешнее устройство и не затрачивать время на поиск результата фильтрации после окончания цикла обработки. Формула изобретения 1. Цифровой согласованный фильтр для импульсных эхо-сигналов, содержащий умножитель; выход которого сое динен с первым входом сумматора, выход которого является выходом фильтр аналого-цифровой преобразователь, вход которого является входом фильтр отличающийся тем, что, с целью повышения точности фильтраци в него введены блок управления, блок записи, блок анализа знаков, первый и второй блоки памяти, коглмутатор .и блок управления фил трацией, выход которого соединен с управляющими вхо дами первого и второго блоков памяти и первым управляющим входом сумматора, выход которого подключен к первому входу второго блока памяти, выход которого соединен с вторым входом сумматора и первым входом блока анализа знаков, выход которого под- ключеи к второму входу второго блока памяти, второму управляющему входу сумматора и управляющему входу умножителя, выход первого блока памяти соединен с вторым входом блока анализа знаков, первым входом-умножителя и первым входом коммутатора, первый шлход которого соединен с входом первого блока памяти и первым входом блока записи, выход которого соединен с первым входом блока управления, вь.ход которого подключен к второму входу блока записи, управлякадему входу аналого-цифрового преобразователя, первому входу блока управления фильтрацией и управляющему входу коммутатора второй выход которого соединен с третьим входом блока анализа знаков, вторым входом умножителя и -вторым входом блока управления фильтрацией, при этом выход аналого-цифрового преобразователя подключен к второму входу коммутатора, а второй вход блока управления является управляющим входом фильтра. . 2.Устройство по п. 1 о т ли чающееся тем, что блок управления содержит генератор импульсов, генератор одиночных импульсов, делитель частоты, триггер, элемент И и RS-триггер, выход которого соединен с первым входом элемента И, второй вход которого подключен к выходу делителя частоты, вход которого соединен с выходом генератора импульсов, выход которого также соединен с первым входом генератора одиночных импульсов, выход которого подключен к R-входу КЗ-триггера и входу триггера, S-вход RS-триггера является первым входом блока управления, а второй вход генератора одиночных импульсов является вторым входом блока управления, причем выход генератора импульсов, выход элемента И, выход триггера и выход генератора одиночных импульсов образуют выход блока управления. . 3.Устройство по п. 1, о т л и чающееся тем, что блок записи содержит первый и второй элементы И, RS -триггер, триггер, счетчик, деиифратор, регистр и узел, сравнения, выход которого соединен.с первым входом триггера, выход которого подключе к первому входу, второго элемента И, выход которого соединен с входом счетчика, рыход которого подключен к входу дешифратора, выход которого является выходом блока записи и подключен к второму входу триггера. выхол R.«,-триггера соелинен с первым входом первого элемента И, выхол которого соединен с первым входом узла сравнения н входом регистра, выход которого подключен к второму входу . узла сравнения, выход которого подключен к, S-входу К5-триггера,К-вход которого является первым входом блока записи, вторые входы первого и второго элементов И объединены и являются вторым входом блока записи. 4. Устройство по п. 1, о т л и чающееся тем, что блок управления фильтрацией содержит первый и второй RS-триггеры, первый и второй элементы И, первый и второй счетчики первый, второь и третий дешифраторы, выход первого RS-триггера подключен к первому входу первого элемента И, выход которого соединен с первым входом первого счетчика и входом второго счетчика, выход которого соединен с входами второго и третьего дешифраторов, выходы которого подключены к S-входам соответственно первого и второго RS-триггеров, R-входы которых объединены и являются вторым входом блока управления фильтрацией, выход первого счетчика соединен с входом первого дешифратора, выход которого подключен к второму входу первого счетчика, вторые входы первого и второго элементов И объединены и являются первым входом блока управления фильтрацией, а выходы первого и второго элементов И и выход дешифратора являются выходом блока управления фильтрацией. Источники информации, принятые во внимание при экспертизе 1,Гольденберг Л.М. и др. Цифровые фильтры. М., Связь. 1974. 2.Патент США 3521041, кл. G 06 F 15/34, 1970 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой согласованный фильтр для импульсных эхо-сигналов | 1983 |

|

SU1104658A2 |

| Анализатор гармоник | 1988 |

|

SU1663571A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Устройство для цифровой обработки сигналов | 1988 |

|

SU1575203A1 |

| Устройство для предварительной фильтрации входных сигналов узкополосных цифровых фильтров | 1990 |

|

SU1739481A1 |

| Цифровой фильтр | 1986 |

|

SU1350825A1 |

| Цифровой фильтр | 1988 |

|

SU1566469A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Многоканальный цифровой интерполирующий фильтр | 1986 |

|

SU1401480A1 |

| Способ компенсации фазовых искажений в многоканальных системах аналого-цифрового преобразования сигналов и устройство для его реализации | 2019 |

|

RU2723566C1 |

11

УпраЛли ии

Леад

fMod

0На&юнП

На &юя1

1

Вмрд -0

15

Г

ftafyoM

ftadMft

4ke2

Авторы

Даты

1982-10-07—Публикация

1981-03-04—Подача