Предлагаемое изобретение относится к области вычислительной техники и предназначено, в частности, для цифровой обработки массивов данных в реальном масштабе времени.

Известен способ цифровой обработки сигналов, выполняющий быстрое преобразование Фурье (БПФ) (см. патент N 0329023 ЕПВ, МКИ 4 G 06 F 15/332/HONEYWELL INC. (US); заяв. 16.02.88; опубл. 23.08.89), заключающийся в последовательном выполнении следующих операций:

- вводят данные для обработки;

- распределяют значения операндов;

- производят одновременное выполнение четырех групп арифметических действий над операндами в параллельных кодах;

- распределяют результаты обработки;

- выводят результаты обработки.

Признаки данного способа, совпадающие с признаками заявляемого, следующие:

- ввод данных для обработки;

- распределение значений операндов;

- вывод результатов обработки.

Недостатки данного способа заключаются в недостаточных функциональных возможностях ввиду вычисления только операций БПФ и недостаточной производительности, так как одновременно выполняются только четыре группы арифметических действий над операндами в параллельных кодах. Для расширения функциональных возможностей и увеличения производительности требуется усложнение алгоритмов арифметических действий над операндами в параллельных кодах и увеличение числа одновременно выполняемых арифметических действий.

Причины, препятствующие достижению требуемого технического результата, заключаются в недостаточных функциональных возможностях, в сложности выполнения арифметических действий над операндами в параллельных кодах и сложности коммутации чисел, представленных в параллельном коде, что требует значительного увеличения времени выполнения сложных операций цифровой обработки сигналов и больших аппаратурных затрат при реализации способа, что в свою очередь препятствует выполнению процессора, реализующего данный способ, в виде интегральной схемы.

Известно устройство для цифровой обработки сигналов, выполняющее БПФ (см. патент N 0329023 ЕПВ, МКИ 4 G 06 F 15/332/HONEYWELL INC. (US); заяв. 16.02.88; опубл. 23.08.89), которое представляет собой процессор массива цифровых сигналов, реализующий алгоритм БПФ по основанию "4". Процессор реализован в виде интегральной схемы с четырехкаскадным конвейером и может выполнять "бабочку" БПФ по основанию "4" над четырьмя комплексными операндами каждые 80 нс. Используя вариант алгоритма с частотным прореживанием, процессор на первом шаге выполняет распределение значений комплексных операндов с помощью первого каскада, второй каскад выполняет операции сложения и вычитания, третий каскад производит умножение операндов, четвертый каскад распределяет значения выходных операндов. Процессор может быть перенастроен для выполнения алгоритма БПФ над двумя наборами комплексных чисел за 80 нс.

Процессор содержит коммутатор данных, поступающих на основные входы, четыре канала обработки, блок вывода и блок управления. Каждый канал обработки состоит из входных регистров, сумматора-вычитателя, умножителя и арифметического устройства. Входы данных процессора соединены через коммутатор данных с основными и дополнительными входами каждого канала обработки, которые являются входами соответственно первого и второго входных регистров. Выход первого входного регистра каждого канала обработки соединен с входом сумматора-вычитателя своего канала, первый выход которого соединен с первым входом умножителя своего канала, а вторые выходы всех сумматоров-вычитателей процессора объединены посредством шины перекрестного вычисления. Второй вход умножителя каждого канала соединен с выходом второго входного регистра своего канала, а выход каждого умножителя соединен с входом арифметического устройства своего канала. Выходы арифметических устройств всех каналов соединены с входами блока вывода процессора.

Признаки устройства, общие с признаками заявляемого технического решения, следующие: каналы обработки сигналов, блок управления и блок вывода.

Недостатки данного процессора заключаются в малых функциональных возможностях ввиду вычисления только операций БПФ и малой производительности, так как производится одновременное выполнение арифметических действий только в 4 каналах обработки. Для расширения функциональных возможностей и увеличения производительности требуется усложнение алгоритмов арифметических действий над операндами в параллельных кодах и увеличение числа каналов обработки.

Причины, препятствующие достижению требуемого технического результата, заключаются в недостаточных функциональных возможностях, в сложности выполнения арифметических действий над операндами в параллельных кодах и сложности коммутации чисел, представленных в параллельном коде, что требует значительного увеличения времени выполнения сложных операций цифровой обработки сигналов и больших аппаратурных затрат при реализации устройства, что в свою очередь препятствует выполнению процессора, реализующего данный способ, в виде интегральной схемы.

Известен способ выполнения базовых операций БПФ с основанием 16 (см. патент N 92/18940 PCT, МКИ 5 G 06 F 15/332/SHARP KABUSHIKI KAISHA (JP/JP)(JP); SHARP MICROELECTRONICS TECHNOLOGY INC. (US/US)(US); заяв. 18.04.91; опубл. 29.10.92), заключающийся в последовательном выполнении следующих действий:

- вводят массив данных для обработки;

- распределяют значения операндов;

- производят одновременное выполнение четырех групп арифметических действий над операндами в параллельных кодах;

- накапливают промежуточные результаты;

- распределяют значения промежуточных результатов;

- производят одновременное выполнение четырех групп арифметических действий над промежуточными результатами в параллельных кодах;

- распределяют результаты обработки;

- выводят результаты обработки.

Признаки данного способа, совпадающие с признаками заявляемого, следующие:

- введение массива данных для обработки;

- распределение значений операндов;

- распределение результатов обработки;

- вывод результатов обработки.

Недостатки данного способа заключаются в недостаточных функциональных возможностях ввиду вычисления только операций БПФ и недостаточной производительности, так как одновременно выполняются только четыре группы арифметических действий над операндами в параллельных кодах. Для расширения функциональных возможностей и увеличения производительности способа требуется усложнение алгоритмов арифметических действий над операндами в параллельных кодах и увеличение числа одновременно выполняемых арифметических действий.

Причины, препятствующие достижению требуемого технического результата, заключаются в недостаточных функциональных возможностях, в сложности выполнения арифметических действий над операндами в параллельных кодах и сложности коммутации чисел, представленных в параллельном коде, что требует значительного увеличения времени выполнения сложных операций цифровой обработки сигналов и больших аппаратурных затрат при реализации способа, что в свою очередь препятствует выполнению процессора, реализующего данный способ, в виде интегральной схемы.

Известен процессор для выполнения базовых операций БПФ с основанием 16 (см. патент N 92/18940 PCT, МКИ 5 G 06 F 15/332/SHARP KABUSHIKI KAISHA (JP/JP)(JP); SHARP MICROELECTRONICS TECHNOLOGY INC. (US/US)(US); заяв. 18.04.91; опубл. 29.10.92), содержащий встроенную память, коммутатор данных, поступающих на основные входы, четыре канала обработки, блок вывода, выполняющий роль коммутатора результатов, и блок управления. Каждый канал обработки состоит из входных регистров, сумматора-вычитателя, умножителя и арифметического устройства. Входы данных процессора и выходы встроенной памяти соединены через коммутатор данных с основными и дополнительными входами каждого канала обработки, которые являются входами соответственно первого и второго входных регистров. Выход первого входного регистра каждого канала обработки соединен со входом сумматора-вычитателя своего канала, первый выход которого соединен с первым входом умножителя своего канала, а вторые выходы всех сумматоров-вычитателей процессора объединены посредством шины перекрестного вычисления. Второй вход умножителя каждого канала соединен с выходом второго входного регистра своего канала, а выход каждого умножителя соединен с входом арифметического устройства своего канала. Выходы арифметических устройств всех каналов соединены с входами встроенной памяти и с входами блока вывода процессора.

Признаки устройства, общие с признаками заявляемого технического решения, следующие: каналы обработки сигналов, блок управления и блок вывода.

Недостатки данного процессора заключаются в недостаточных функциональных возможностях ввиду вычисления только операций БПФ и недостаточной производительности, так как производится одновременное выполнение арифметических действий только в четырех каналах обработки. Для расширения функциональных возможностей и увеличения производительности устройства требуется усложнение алгоритмов арифметических действий над операндами в параллельных кодах и увеличение числа каналов обработки.

Причины, препятствующие достижению требуемого технического результата, заключаются в недостаточных функциональных возможностях, в сложности выполнения арифметических действий над операндами в параллельных кодах и сложности коммутации чисел, представленных в параллельном коде, что требует значительного увеличения времени выполнения сложных операций цифровой обработки сигналов и больших аппаратурных затрат при реализации способа, что в свою очередь препятствует выполнению процессора, реализующего данный способ, в виде интегральной схемы.

Известен способ цифровой обработки информации (см. патент N 2032215 РФ, МКИ 6 G 06 F 15/16, Соколов А.А. и др. Институт точной механики и вычислительной техники им. С.А.Лебедева. РАН; заяв. 27.10.92; опубл. 27.04.95), при использовании которого выполняют следующую последовательность функциональных действий:

- вводят и запоминают массив данных;

- формируют команды и управляющие сигналы;

- декодируют команды;

- коммутируют адреса в соответствии со схемой приоритета;

- коммутируют операнды;

- выполняют арифметические действия над операндами в параллельных кодах;

- коммутируют результаты обработки;

- выдают результаты обработки.

Признаки данного способа, совпадающие с признаками заявляемого, следующие:

- ввод и запоминание массива данных;

- формирование команд и управляющих сигналов;

- коммутация операндов;

- коммутация результатов обработки;

- вывод результатов обработки.

Недостаток данного способа заключается в недостаточной производительности, так как одновременно выполняется только одно арифметическое действие над операндами в параллельных кодах. Для повышения производительности способа требуется увеличение числа одновременно выполняемых арифметических действий.

Причины, препятствующие достижению требуемого технического результата, заключаются в сложности выполнения арифметических действий над операндами в параллельных кодах и сложности коммутации чисел, представленных в параллельном коде, что требует увеличения времени выполнения сложных операций цифровой обработки сигналов, например алгоритма БПФ, и больших аппаратурных затрат при реализации способа, что в свою очередь препятствует выполнению процессора, реализующего данный способ, в виде интегральной схемы.

Известен конвейерный процессор (см. патент N 2032215 РФ, МКИ 6 G 06 F 15/16/ Соколов А.А. и др. Институт точной механики и вычислительной техники им. С. А.Лебедева. РАН; заяв. 27.10.92; опубл. 27.04.95), содержащий коммутатор записи, коммутатор адресов, коммутатор управления памятью, коммутатор операндов, коммутатор результатов, память, формирователь управляющих сигналов, формирователи потоков команд, арифметический блок и блок обмена. Процессор может быть использован для построения вычислительных систем при обработке данных физико-математических экспериментов, для научных расчетов.

Признаки устройства, совпадающие с признаками заявляемого технического решения, следующие: коммутатор операндов, коммутатор результатов, формирователь управляющих сигналов и арифметический блок.

Недостаток данного устройства заключается в недостаточной производительности, так как одновременно выполняется только одно арифметическое действие над операндами в параллельных кодах. Для повышения производительности требуется увеличение числа арифметических блоков.

Причины, препятствующие достижению требуемого технического результата, заключаются в сложности выполнения арифметических действий над операндами в параллельных кодах и сложности коммутации чисел, представленных в параллельном коде, что требует увеличения времени выполнения сложных операций цифровой обработки сигналов, например алгоритма БПФ, и больших аппаратурных затрат при реализации способа, что в свою очередь препятствует выполнению процессора, реализующего данный способ, в виде интегральной схемы.

Известен способ цифровой обработки информации, наиболее близкий к заявляемому, (см. патент N 2030785 РФ, МКИ G 06 F 15/16/ Жабин В.И. и др. (UA), Киевский политехнический институт (UA); заяв. 21.09.90; опуб. 10.03.95), содержащий следующие действия:

- ввод управляющих слов;

- ввод массива данных;

- запись массива данных в буферную память;

- формирование команд и управляющих сигналов;

- распределение команд и данных на n групп;

- выполнение заданных операций в n группах данных;

- коммутация результатов вычислений;

- вывод результатов вычислений.

Признаки данного способа, совпадающие с признаками заявляемого, следующие:

- ввод управляющих слов;

- ввод массива данных;

- формирование команд и управляющих сигналов;

- распределение данных на n групп;

- выполнение заданных операций в n группах данных;

- коммутация результатов вычислений;

- вывод результатов вычислений.

Причины, препятствующие достижению требуемого технического результата, заключаются в сложности выполнения арифметических действий над операндами в параллельных кодах и сложности коммутации чисел, представленных в параллельном коде, что требует значительного увеличения времени выполнения сложных операций цифровой обработки сигналов и больших аппаратурных затрат при реализации способа, что в свою очередь препятствует выполнению процессора, реализующего данный способ, в виде интегральной схемы.

Известно вычислительное устройство, наиболее близкое к заявляемому (см. патент N 2030785 РФ, МКИ 6 G 06 F 15/16/ Жабин В.И. и др. (UA), Киевский политехнический институт (UA); заяв. 21.09.90; опубл. 10.03.95), содержащее блок ввода данных, коммутатор записи данных и результатов, n блоков обработки информации, блоки памяти операндов и управляющих слов, блоки буферной памяти данных и команд, блок управления, регистр данных, регистр адреса, блок вывода, шифратор, элементы ИЛИ. Устройство может быть использовано при построении высокопроизводительных систем для решения задач, алгоритмы которых имеют последовательно-параллельную структуру.

Признаки прототипа, совпадающие с признаками заявляемого технического решения, следующие: n блоков обработки информации, блок вывода и блок управления.

Причины, препятствующие достижению требуемого технического результата, заключаются в больших аппаратурных затратах при выполнении арифметических действий над операндами в параллельных кодах и сложности коммутации чисел, представленных в параллельном коде, что требует значительного увеличения времени выполнения сложных операций цифровой обработки сигналов и больших аппаратурных затрат, что в свою очередь препятствует выполнению процессора в виде интегральной схемы.

Задачей, на решение которой направлено предлагаемое техническое решение, является повышение производительности и расширение функциональных возможностей цифровой обработки сигналов с возможностью реализации на устройствах в виде сверхбольших интегральных схем (СБИС) без увеличения аппаратурных затрат.

Технический результат, достигаемый при осуществлении изобретения, заключается в увеличении тактовой частоты обработки до сотен МГц СБИС при высоком распараллеливании выполнения арифметических операций цифровой обработки сигналов, включая БПФ, операции цифровой фильтрации, перемножения массивов комплексных и действительных данных и т.п., без увеличения аппаратурных затрат, что позволяет реализацию технического решения в виде СБИС.

Заявляемый технический результат достигается тем, что в способе цифровой обработки сигналов, заключающемся во введении сигналов данных в параллельном дополнительном двоичном коде с частотой внешней синхронизации, команды задания операции цифровой обработки сигналов данных и управляющих сигналов, запоминании сигналов данных в количестве, необходимом для одновременного выполнения n групп арифметических операций, формировании кодов настройки и коммутации сигналов данных и результатов обработки в соответствии с командой задания операции цифровой обработки, считывании запомненных сигналов данных, распределении запомненных сигналов данных на n групп, коммутации результатов обработки, запоминании результатов обработки, выводе результатов обработки, после считывания запомненные сигналы данных преобразуют из параллельного дополнительного двоичного кода в последовательный знакоразрядный код, распределяют запомненные сигналы данных на n групп посредством коммутации сигналов данных в последовательных знакоразрядных кодах, выполняют поразрядные вычисления в избыточной системе счисления над n группами сигналов данных в соответствии с кодом операции цифровой обработки сигналов, с внутренней частотой синхронизации, а полученные результаты обработки коммутируют и запоминают в знакоразрядных кодах, запомненные результаты обработки выводят с внешней частотой синхронизации с одновременным преобразованием в параллельный дополнительный двоичный код, причем действия над сигналами данных и результатами обработки выполняют одновременно.

Технический результат достигается также тем, что в устройство, содержащее блок управления, коммутатор операндов, коммутатор результатов и n каналов обработки, где n = 1, 2, ..., N, в котором шина управляющих сигналов и шина команд устройства подключены соответственно к управляющим и к информационным входам блока управления, выходы которого подключены к управляющим входам коммутатора операндов, коммутатора результатов и каналов обработки, выходы каналов обработки соединены с информационными входами коммутатора результатов, введены блоки ортогональной регистровой памяти, входные преобразователи информации и выходной преобразователь результатов, причем первая и вторая шины данных устройства подключены к информационным входам соответственно первого и второго блоков ортогональной регистровой памяти, управляющие входы блоков регистровой памяти, входных преобразователей информации и выходного преобразователя результатов подключены к выходам блока управления, выходы первого и второго блоков ортогональной регистровой памяти подключены к информационным входам соответственно первого и второго входных преобразователей информации, выходы которых соединены соответственно с первой и второй группами информационных входов коммутатора операндов, у которого группы выходов с первой по n-ю соединены с информационными входами каналов обработки соответственно с первого по n-й, первая группа выходов коммутатора результатов подключена к информационным входам выходного преобразователя результатов, а вторая группа выходов соединена с третьей группой информационных входов коммутатора операндов, выходы выходного преобразователя результатов соединены с шиной результатов устройства.

Технический результат достигается также тем, что канал обработки содержит коммутаторы данных, арифметические блоки, сумматоры и регистры задержки, причем управляющие входы канала обработки соединены с управляющими входами первого и второго коммутаторов данных, регистров задержки, сумматоров и арифметических блоков, информационные входы первого коммутатора данных соединены с информационными входами канала обработки, первый и второй выходы первого коммутатора данных подключены к информационным входам первого арифметического блока, третий выход первого коммутатора данных подключен к первому информационному входу первого регистра задержки, четвертый и пятый выходы первого коммутатора данных подключены к информационным входам второго арифметического блока, шестой и седьмой выходы первого коммутатора данных подключены к информационным входам третьего арифметического блока, восьмой выход первого коммутатора данных подключен к первому информационному входу второго регистра задержки, девятый и десятый выходы первого коммутатора данных подключены к информационным входам четвертого арифметического блока, выходы первого и третьего арифметических блоков соединены с первыми информационными входами соответственно первого и второго сумматоров, выходы второго и четвертого арифметических блоков соединены со вторыми информационными входами соответственно первого и второго регистров задержки и со вторыми информационными входами соответственно первого и второго сумматоров, выходы которых соединены соответственно с первым и третьим информационными входами второго коммутатора данных, второй и четвертый информационные входы которого подключены к выходам соответственно первого и второго регистров задержки, первый и третий выходы второго коммутатора данных соединены соответственно с первым информационным входом третьего сумматора и со вторым информационным входом четвертого сумматора, второй выход второго коммутатора данных соединен со вторым информационным входом третьего сумматора и с первым информационным входом четвертого сумматора, четвертый и шестой выходы второго коммутатора данных соединены соответственно с первым информационным входом пятого сумматора и со вторым информационным входом шестого сумматора, пятый выход второго коммутатора данных соединен со вторым информационным входом пятого сумматора и с первым информационным входом шестого сумматора, а выходы сумматоров с третьего по шестой являются выходами канала обработки.

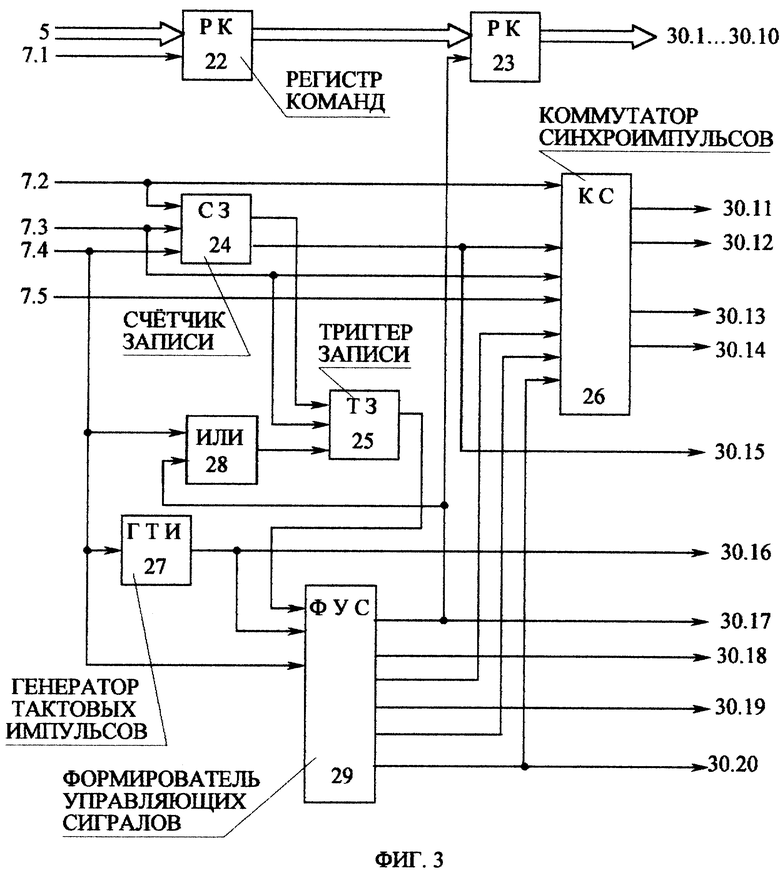

Технический результат достигается также тем, что блок управления содержит регистры команд, счетчик записи, триггер записи, коммутатор синхроимпульсов, генератор тактовых импульсов, элемент ИЛИ и формирователь управляющих сигналов, причем выходы первого регистра команд подключены к информационным входам второго регистра команд, первый выход счетчика записи соединен с информационным входом триггера записи, а второй выход подключен ко второму входу коммутатора синхроимпульсов, вход установки нуля счетчика записи соединен со входом установки нуля генератора тактовых импульсов, с первым входом элемента ИЛИ, с третьим входом формирователя управляющих сигналов и подключен к четвертому управляющему входу блока управления, второй управляющий вход которого соединен с входом разрешения счета счетчика записи и с первым входом коммутатора синхроимпульсов, вход установки нуля триггера записи соединен с выходом элемента ИЛИ, первый управляющий вход блока управления соединен с входом синхронизации первого регистра команд, информационные входы которого подключены к информационным входам блока управления 6, третий управляющий вход которого соединен с входами синхронизации счетчика записи и триггера записи и с третьим входом коммутатора синхроимпульсов, четвертый вход которого соединен с пятым управляющим входом блока управления 6, выход триггера записи соединен с первым входом формирователя управляющих сигналов, первый выход которого соединен со вторым входом элемента ИЛИ и с входом синхронизации второго регистра команд, а второй вход соединен с выходом генератора тактовых импульсов, третий и пятый выходы формирователя управляющих сигналов соединены соответственно с пятым и шестым входами коммутатора синхроимпульсов, седьмой вход которого соединен с шестым выходом формирователя управляющих сигналов, выходы второго регистра команд являются выходами блока управления с первого по десятый, выходы коммутатора синхроимпульсов и второй выход счетчика записи являются выходами блока управления с одиннадцатого по пятнадцатый, выход генератора тактовых импульсов и первый выход формирователя управляющих сигналов являются шестнадцатым и семнадцатым выходами блока управления, а второй, четвертый и шестой выходы формирователя управляющих сигналов являются выходами блока управления соответственно с восемнадцатого по двадцатый.

Доказательство наличия причинно-следственной связи между заявляемыми признаками изобретения и достигаемым техническим результатом заключается в следующем.

Обработка цифровых сигналов осуществляется с внутренней тактовой частотой, в несколько раз превышающей частоту ввода данных, благодаря тому, что переводят обрабатываемые данные, представленные в параллельном дополнительном коде и поступающие для обработки с частотой внешней синхронизации, в последовательный знакоразрядный код, который позволяет выполнять поразрядные вычисления старшими разрядами вперед с большой тактовой частотой (до сотен МГц). Результаты вычислений выводятся в параллельном дополнительном коде. Большая скорость обработки достигается также распараллеливанием арифметических операций в n каналах обработки, каждый из которых настраивают с помощью кода операций на выполнение широкого класса операций цифровой обработки сигналов.

Реализация арифметических блоков, сумматоров и коммутаторов, которые коммутируют последовательные каналы информации, для выполнения поразрядных вычислений старшими разрядами вперед требует относительно низких аппаратурных затрат, например канал обработки при обработке чисел с фиксированной точкой требует для своей реализации не более 10 тысяч вентилей на кристалле БИС, что дает широкие возможности для разработки СБИС цифровой обработки сигналов различной производительности.

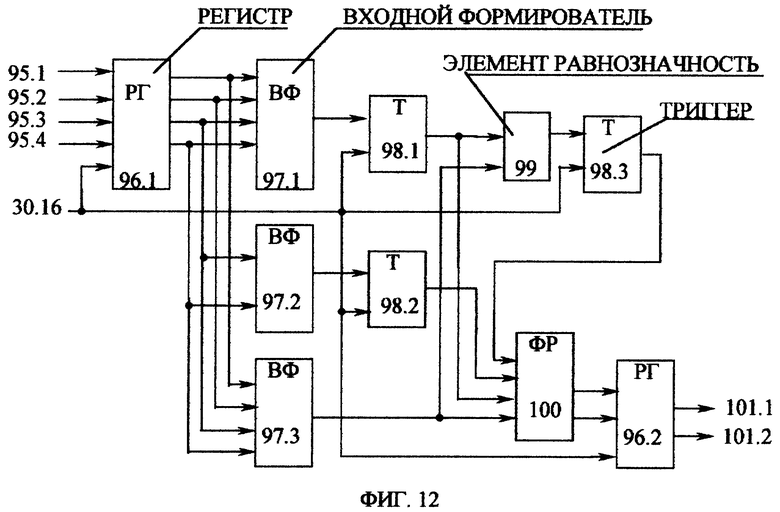

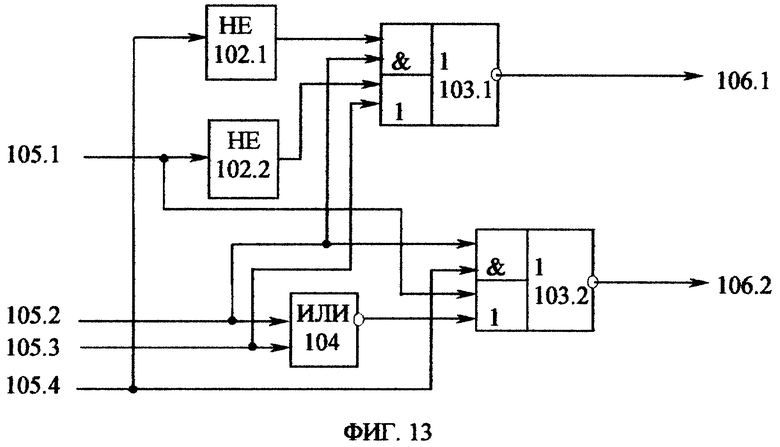

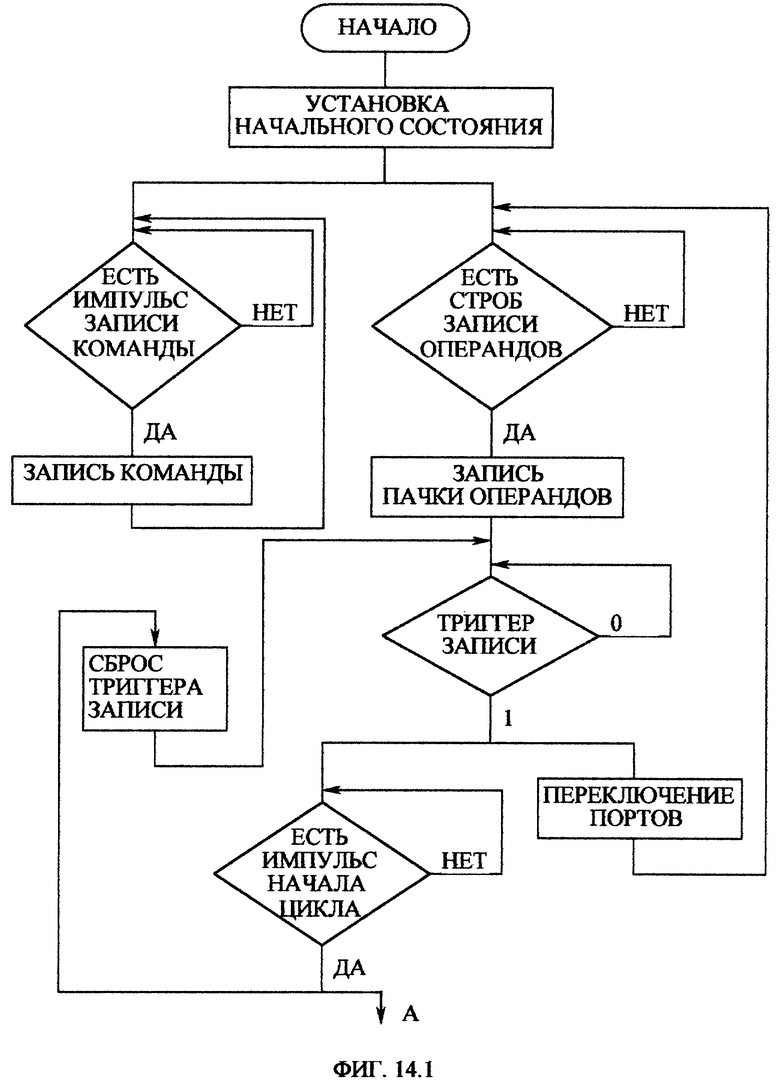

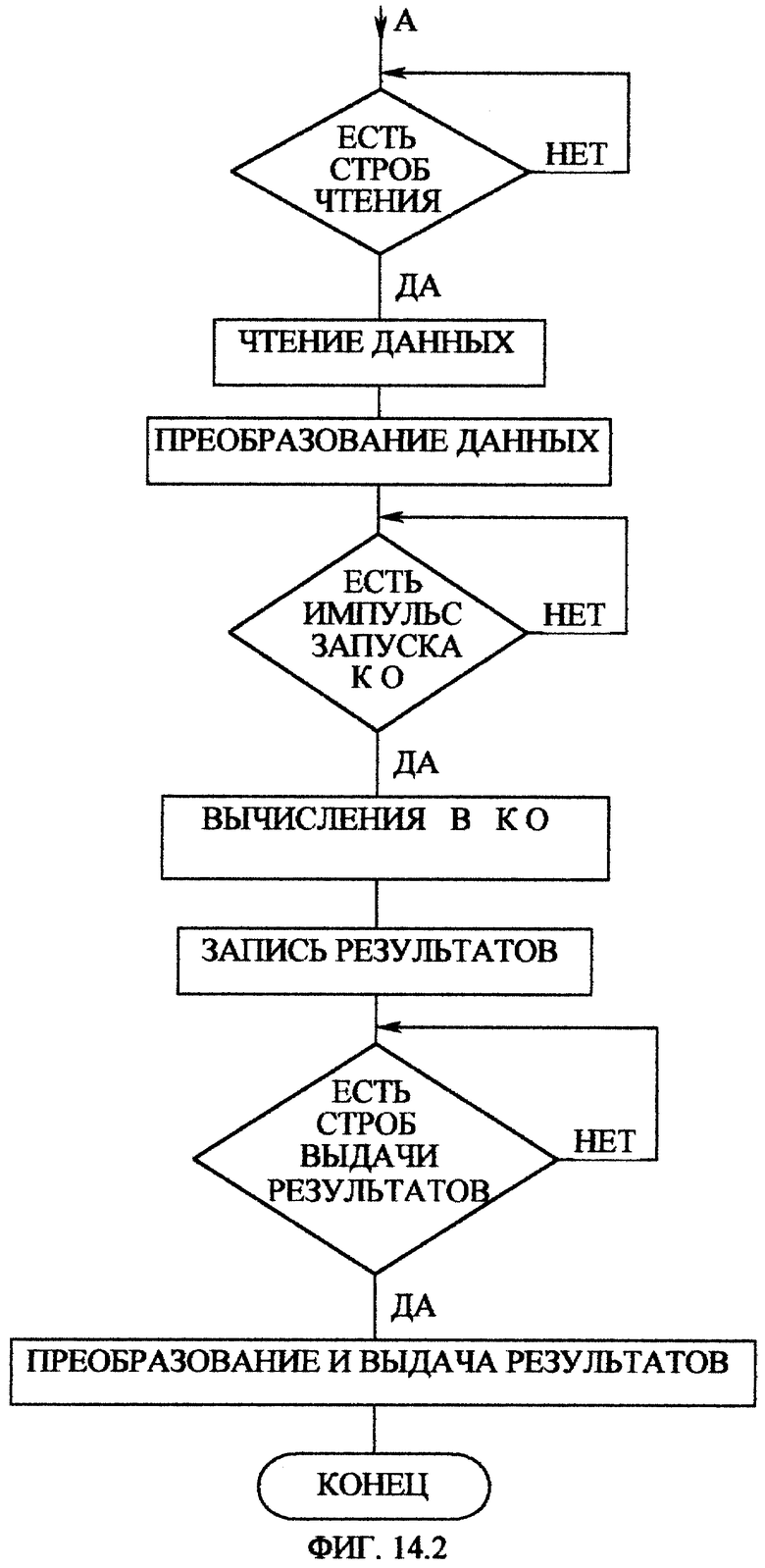

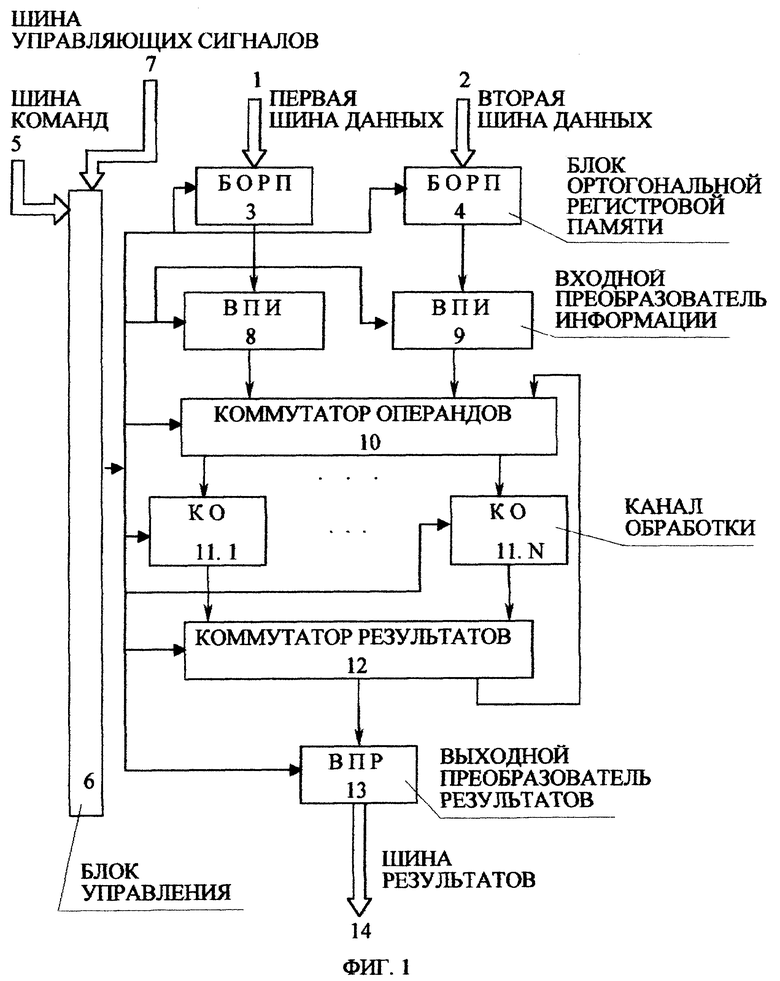

Изобретение поясняется чертежами, где на фиг. 1 изображена функциональная схема устройства цифровой обработки сигналов, на фиг. 2 - функциональная схема канала обработки, на фиг. 3 - функциональная схема блока управления, на фиг. 4 - функциональная схема формирователя управляющих сигналов блока управления, на фиг. 5 - функциональная схема коммутатора синхроимпульсов блока управления, на фиг. 6 - функциональная схема блока ортогональной регистровой памяти, на фиг. 7 - функциональная схема канала преобразования входного преобразователя информации, на фиг. 8 - функциональная схема выходного преобразователя результатов, на фиг. 9 - функциональная схема регистра выходного преобразователя результатов, на фиг. 10 - функциональная схема арифметического блока канала обработки, на фиг. 11 - функциональная схема формирователя произведения арифметического блока канала обработки, на фиг. 12 - функциональная схема сумматора канала обработки, на фиг. 13 - функциональная схема формирователя результата сумматора канала обработки, на фиг. 14 - блок-схема алгоритма работы устройства, и таблицами, где в таблице 1 приведен порядок коммутации первого коммутатора данных 16 канала обработки, в таблице 2 приведен порядок коммутации второго коммутатора данных 20 канала обработки, в таблице 3 приведен порядок коммутации коммутатора результатов 12 устройства.

Заявляемый способ цифровой обработки сигналов состоит из следующей совокупности действий.

Вводят сигналы данных в параллельном дополнительном двоичном коде с частотой внешней синхронизации, команды для задания необходимых операций обработки сигналов и управляющие сигналы.

Запоминают сигналы данных в количестве, необходимом для одновременного выполнения n групп арифметических операций.

Формируют коды настройки и коммутации сигналов данных и результатов обработки в соответствии с полученной командой задания операции цифровой обработки таким образом, чтобы определенной операции цифровой обработки сигналов соответствовали определенные коды настройки и коммутации, т.е. присваивают операциям цифровой обработки сигналов данных соответствующие коды команды.

Считывают запомненные сигналы данных последовательным кодом старшими разрядами вперед, с частотой внутренней синхронизации, с одновременным преобразованием в знакоразрядный код.

Распределяют сигналы данных на n групп посредством коммутации сигналов данных в последовательном знакоразрядном коде.

Выполняют поразрядные вычисления в избыточной системе счисления над n группами сигналов данных, представленных последовательным знакоразрядным кодом, в соответствии с кодом операции, с частотой внутренней синхронизации.

Коммутируют последовательные коды полученных результатов обработки n групп сигналов данных и запоминают их в знакоразрядных кодах.

Преобразуют запомненные результаты обработки в параллельный дополнительный двоичный код с одновременным выводом их с частотой внешней синхронизации.

Все действия над сигналами данных и результатами обработки выполняют одновременно, т.е. вводят и запоминают новый (i+1)-й массив сигналов данных на фоне обработки предыдущего запомненного i-го массива сигналов данных с одновременным преобразованием и выводом результатов обработки (i-1)-го массива сигналов, а также одновременно считывают запомненный i-й массив сигналов данных, преобразуют в знакоразрядный код, распределяют сигналы данных на n групп, выполняют поразрядные вычисления в избыточной системе счисления над n группами сигналов данных, коммутируют последовательные коды полученных результатов обработки и запоминают их в знакоразрядных кодах.

Устройство, реализующее заявляемый способ (см. фиг. 1), содержит первую и вторую шины данных 1 и 2, первый и второй блоки ортогональной регистровой памяти 3 и 4, шину команд 5, блок управления 6, шину управляющих сигналов 7, первый и второй входные преобразователи информации 8 и 9, коммутатор операндов 10, каналы обработки 11.1, ... 11.N, коммутатор результатов 12, выходной преобразователь результатов 13 и шину результатов 14.

Блоки и узлы устройства взаимосвязаны между собой следующим образом.

Первая и вторая шины данных устройства 1 и 2 подключены к информационным входам соответственно первого и второго блоков ортогональной регистровой памяти 3 и 4, а шина команд устройства 5 подключена к информационным входам блока управления 6. Шина управляющих сигналов 7 устройства подключена к управляющим входам блока управления 6, выходы которого подключены к управляющим входам первого и второго блоков ортогональной регистровой памяти 3 и 4, первого и второго входных преобразователей информации 8 и 9, коммутатора операндов 10, каналов обработки 11.1, ... 11.N, коммутатора результатов 12 и выходного преобразователя результатов 13. Выходы первого и второго блоков ортогональной регистровой памяти 3 и 4 подключены к информационным входам соответственно первого и второго входных преобразователей информации 8 и 9, выходы которых соединены соответственно с первой и второй группами информационных входов коммутатора операндов 10, группы выходов с первой по n-ю которого соединены с информационными входами каналов обработки соответственно с 11.1 по 11.N. Выходы каналов обработки соответственно с 11.1 по 11.N соединены с информационными входами коммутатора результатов 12, первая группа выходов которого подключена к информационным входам выходного преобразователя результатов 13, а вторая группа выходов подключена к третьей группе информационных входов коммутатора операндов 10. Выходы выходного преобразователя результатов 13 соединены с шиной результата 14 устройства.

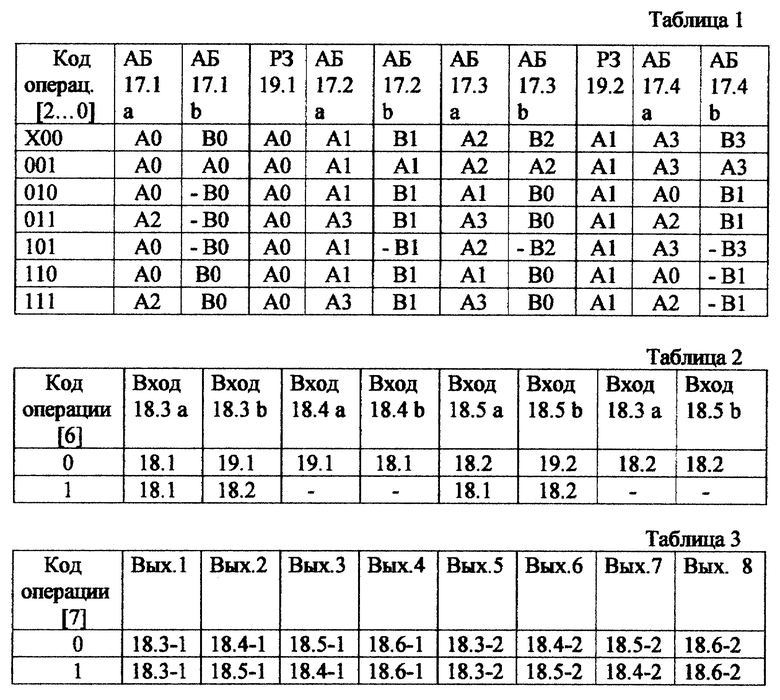

Канал обработки 11 (см. фиг. 2) содержит управляющие входы 15, первый коммутатор данных 16, четыре арифметических блока 17.1, ..., 17.4, шесть сумматоров 18.1, ..., 18.6, два регистра задержки 19.1 и 19.2, второй коммутатор данных 20 и информационные входы 21. Управляющие входы 15 канала обработки 11 соединены с управляющими входами первого коммутатора данных 16, арифметических блоков 17.1, ..., 17.4, сумматоров 18.1, ..., 18.6, первого и второго регистров задержки 19.1 и 19.2, второго коммутатора данных 20, а информационные входы первого коммутатора данных 16 соединены с информационными входами 21 канала обработки. Первый и второй выходы первого коммутатора данных 16 подключены к информационным входам первого арифметического блока 17.1, третий выход первого коммутатора данных 16 подключен к первому информационному входу первого регистра задержки 19.1, четвертый и пятый выходы первого коммутатора данных 16 подключены к информационным входам второго арифметического блока 17.2, шестой и седьмой выходы первого коммутатора данных 16 подключены к информационным входам третьего арифметического блока 17.3, восьмой выход первого коммутатора данных 16 подключен к первому информационному входу второго регистра задержки 19.2, девятый и десятый выходы первого коммутатора данных 16 подключены к информационным входам четвертого арифметического блока 17.4.

Выходы первого и третьего арифметических блоков 17.1 и 17.3 соединены с первыми информационными входами соответственно первого и второго сумматоров 18.1 и 18.2. Выход второго арифметического блока 17.2 соединен со вторыми информационными входами первого сумматора 18.1 и первого регистра задержки 19.1. Выход четвертого арифметического блока 17.4 соединен со вторыми информационными входами второго сумматора 18.2 и второго регистра задержки 19.2. Выходы первого и второго сумматоров 18.1 и 18.2 соединены соответственно с первой и третьей группами информационных входов второго коммутатора данных 20, вторая и четвертая группы информационных входов которого подключены к выходам соответственно первого и второго регистров задержки 19.1 и 19.2. Первый и третий выходы второго коммутатора данных 20 соединены соответственно с первым информационным входом третьего сумматора 18.3 и со вторым информационным входом четвертого сумматора 18.4. Второй выход второго коммутатора данных 20 соединен со вторым информационным входом третьего сумматора 18.3 и с первым информационным входом четвертого сумматора 18.4. Четвертый и шестой выходы второго коммутатора данных 20 соединены соответственно с первым информационным входом пятого сумматора 18.5 и со вторым информационным входом шестого сумматора 18.6. Пятый выход второго коммутатора данных 20 соединен со вторым информационным входом пятого сумматора 18.5 и с первым информационным входом шестого сумматора 18.6. Выходы сумматоров с третьего по шестой 18.3, 18.4, 18.5 и 18.6 являются выходами канала обработки 11.

Блок управления 6 (см. фиг. 3) содержит первый и второй регистры команд 22 и 23, счетчик записи 24, триггер записи 25, коммутатор синхроимпульсов 26, генератор тактовых импульсов 27, элемент ИЛИ 28, формирователь управляющих сигналов 29. Выходы первого регистра команд 22 подключены к информационным входам второго регистра команд 23. Первый выход счетчика записи 24 соединен с информационным входом триггера записи 25, а второй выход подключен ко второму входу коммутатора синхроимпульсов 26. Вход установки нуля счетчика записи 24 соединен со входом установки нуля генератора тактовых импульсов 27, с первым входом элемента ИЛИ 28, с третьим входом формирователя управляющих сигналов 29 и подключен к четвертому управляющему входу 7.4 блока управления 6, второй управляющий вход 7.2 которого соединен с входом разрешения счета счетчика записи 24 и с первым входом коммутатора синхроимпульсов 26, а первый управляющий вход 7.1 блока управления 6 соединен с входом синхронизации первого регистра команд 22, информационные входы которого подключены к информационным входам блока управления 6, соединенным с шиной команд 5 устройства.

Вход установки нуля триггера записи 25 соединен с выходом элемента ИЛИ 28. Третий управляющий вход 7.3 блока управления 6 соединен с входами синхронизации счетчика записи 24 и триггера записи 25 и с третьим входом коммутатора синхроимпульсов 26, четвертый вход которого соединен с пятым управляющим входом 7.5 блока управления 6. Выход триггера записи 25 соединен с первым входом формирователя управляющих сигналов 29, первый выход которого соединен со вторым входом элемента ИЛИ 28 и с входом синхронизации второго регистра команд 23, а второй вход соединен с выходом генератора тактовых импульсов 27. Третий и пятый выходы формирователя управляющих сигналов 29 соединены соответственно с пятым и шестым входами коммутатора синхроимпульсов 26, седьмой вход которого подключен к шестому выходу формирователя управляющих сигналов 29. Выходы второго регистра команд 23 являются выходами с первого по десятый 30.1, ..., 30.10 блока управления 6, а выходы коммутатора синхроимпульсов 26 и второй выход счетчика записи 24 являются выходами с одиннадцатого по пятнадцатый 30.11, ..., 30.15 блока управления 6. Выход генератора тактовых импульсов 27 и первый выход формирователя управляющих сигналов 29 являются шестнадцатым и семнадцатым выходами 30.16 и 30.17 блока управления 6. Второй, четвертый и шестой выходы формирователя управляющих сигналов 29 являются выходами с восемнадцатого по двадцатый 30.18, ..., 30.20 блока управления 6.

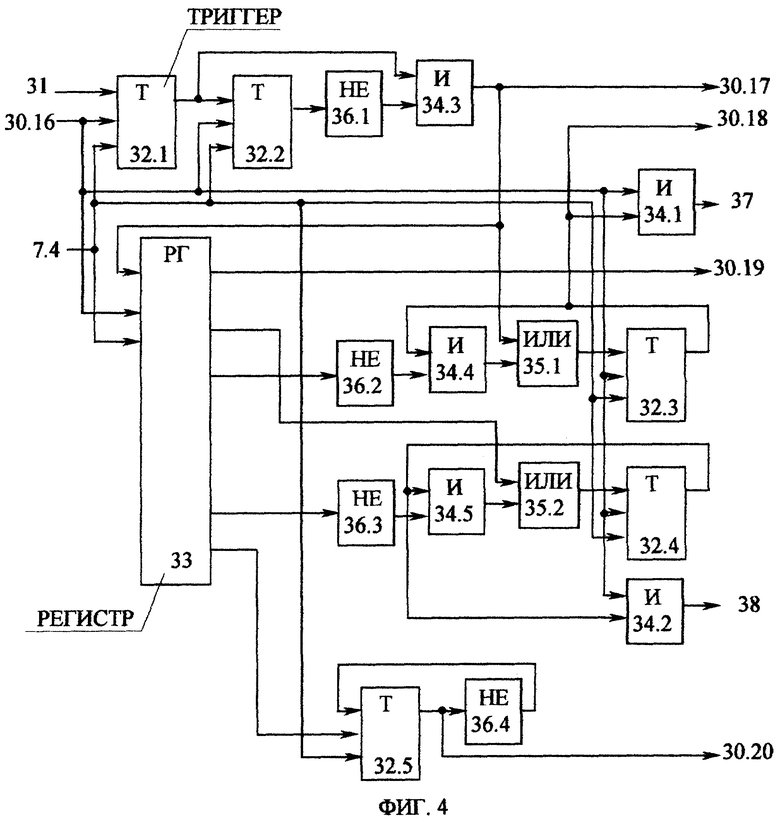

Формирователь управляющих сигналов (ФУС) 29 блока управления 6 содержит (см. фиг. 4) пять триггеров 32.1, ..., 32.5, регистр 33, пять элементов И 34.1, . .., 34.5, два элемента ИЛИ 35.1 и 35.2, четыре инвертора 36.1, ..., 36.4. Первый вход 31 ФУС 29 соединен с информационным входом первого триггера 32.1, а второй вход ФУС 29 соединен с выходом 30.16 блока управления 6 и с входами синхронизации триггеров 32.1, ..., 32.4, с входом синхронизации регистра 33 и с первыми входами первого и второго элементов И 34.1 и 34.2. Третий вход ФУС 29 соединен с четвертым управляющим входом 7.4 блока управления 6 и с входами установки нуля триггеров 32.1, ..., 32.5 и регистра 33. Выход первого триггера 32.1 подключен к первому входу третьего элемента И 34.3 и к информационному входу второго триггера 32.2, выход которого соединен с входом первого инвертора 36.1. Выход первого инвертора 36.1 подключен ко второму входу третьего элемента И 34.3, выход которого соединен с информационным входом регистра 33 и с первым входом первого элемента ИЛИ 35.1. Вход второго инвертора 36.2 соединен с третьим выходом регистра 33, а выход подключен ко второму входу четвертого элемента И 34.4, выход которого соединен со вторым входом первого элемента ИЛИ 35.1.

Вход третьего инвертора 36.3 соединен с четвертым выходом регистра 33, а выход подключен ко второму входу пятого элемента И 34.5, выход которого соединен со вторым входом второго элемента ИЛИ 35.2. Первый вход второго элемента ИЛИ 35.2 соединен со вторым выходом регистра 33, а выходы первого и второго элементов ИЛИ 35.1 и 35.2 соединены с информационными входами соответственно третьего и четвертого триггеров 32.3 и 32.4. Выход третьего триггера 32.3 соединен со вторым входом первого элемента И 34.1 и с первым входом четвертого элемента И 34.4, а выход четвертого триггера 32.4 соединен со вторым входом второго элемента И 34.2 и с первым входом пятого элемента И 34.5. Вход и выход четвертого инвертора 36.4 соединены соответственно с выходом и с информационным входом пятого триггера 32.5, вход синхронизации которого соединен с пятым выходом регистра 33. Третий и пятый выходы 37 и 38 ФУС 29 соединены с выходами соответственно первого и второго элементов И 34.1 и 34.2. Выход третьего элемента И 34.3 соединен с первым выходом ФУС 29 и является семнадцатым выходом 30.17 блока управления 6. Второй и шестой выходы ФУС 29 соединены с выходами соответственно третьего и пятого триггеров 32.3 и 32.5 и являются соответственно восемнадцатым и двадцатым выходами 30.18 и 32.20 блока управления 6, а четвертый выход ФУС 29 соединен с первым выходом регистра 33 и является девятнадцатым выходом 30.19 блока управления 6.

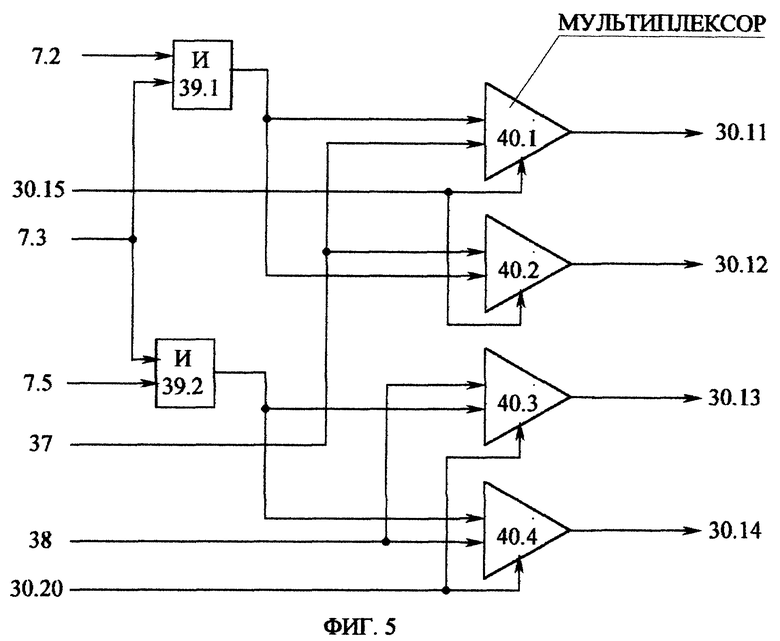

Коммутатор синхроимпульсов 26 блока управления содержит (см. фиг. 5) первый и второй элементы И 39.1 и 39.2 и четыре мультиплексора 40.1, ..., 40.4. Выход первого элемента И 39.1 соединен с первым информационным входом первого мультиплексора 40.1 и со вторым информационным входом второго мультиплексора 40.2. Управляющие входы первого и второго мультиплексоров 40.1 и 40.2 соединены со вторым входом коммутатора синхроимпульсов 26, который подключен к выходу 30.15 блока управления 6. Первый вход коммутатора синхроимпульсов 26 соединен со вторым управляющим входом 7.2 блока управления 6 и с первым входом первого элемента И 39.1, второй вход которого соединен с первым входом второго элемента И 39.2, с третьим входом коммутатора синхроимпульсов 26 и с третьим управляющим входом 7.3 блока управления 6. Второй вход второго элемента И 39.2 подключен к четвертому входу коммутатора синхроимпульсов 26, соединенного с пятым управляющим входом 7.5 блока управления 6.

Второй информационный вход первого мультиплексора 40.1 и первый информационный вход второго мультиплексора 40.2 соединены с пятым входом 37 коммутатора синхроимпульсов 26, шестой вход 38 которого соединен с первым информационным входом третьего мультиплексора 40.3 и со вторым информационным входом четвертого мультиплексора 40.4. Управляющие входы третьего и четвертого мультиплексоров 40.3 и 40.4 соединены с седьмым входом коммутатора синхроимпульсов 26 и с выходом 30.20 блока управления 6. Выход второго элемента И 39.2 соединен со вторым информационным входом третьего мультиплексора 40.3 и с первым информационным входом четвертого мультиплексора 40.4. Первый и второй выходы коммутатора синхроимпульсов 26 соединены с выходами соответственно первого и второго мультиплексоров 40.1 и 40.2 и являются выходами 30.11 и 30.12 блока управления 6, а третий и четвертый выходы коммутатора синхроимпульсов 26 соединены с выходами соответственно третьего и четвертого мультиплексоров 40.3 и 40.4 и являются выходами 30.13 и 30.14 блока управления 6.

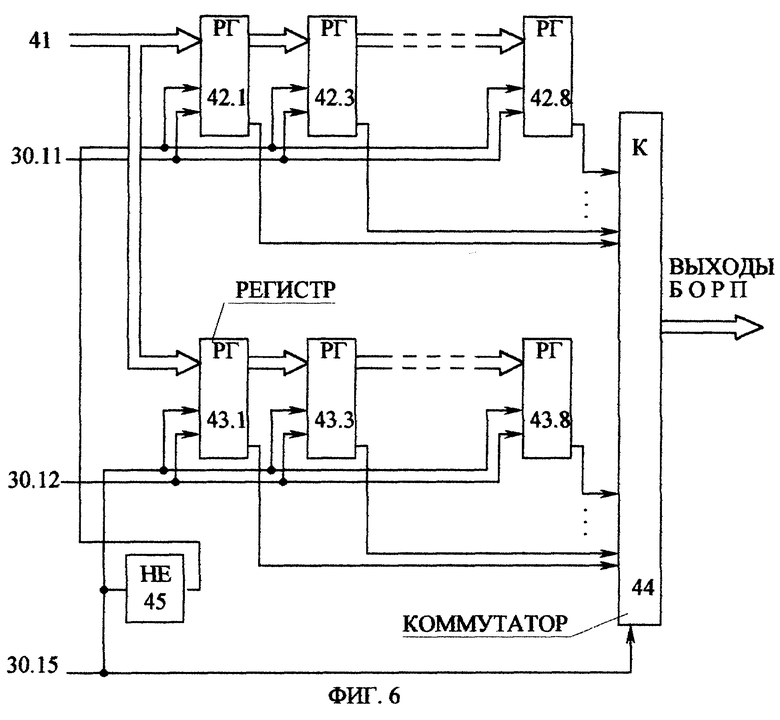

Блок ортогональной регистровой памяти (БОРП) 3 или 4 содержит (см. фиг. 6) восемь регистров 42.1, ..., 42.8 первого порта памяти, восемь регистров 43.1, ..., 43.8 второго порта памяти, коммутатор 44 и инвертор 45. Информационные входы 41 БОРП 3 соединены с первой шиной данных 1 устройства и с информационными входами первых регистров 42.1 и 43.1. Информационные входы 41 БОРП 4 соединены со второй шиной данных 2 устройства и с информационными входами первых регистров 42.1 и 43.1. Параллельные выходы первых регистров 42.1 и 43.1 соответственно первого и второго портов памяти БОРП подключены к параллельным информационным входам вторых регистров 42.2 и 43.2 соответственно первого и второго портов памяти БОРП и т.д. Выходы старшего разряда всех регистров подключены к информационным входам коммутатора 44, выходы которого являются выходами БОРП. Вход инвертора 45 соединен с управляющим входом коммутатора 44, с входами переключения режима работы регистров 43.1, ..., 43.8 второго порта памяти БОРП и с третьим управляющим входом БОРП, который соединен с выходом 30.15 блока управления 6, а выход инвертора 45 соединен с входами переключения режима работы регистров 42.1, ..., 42.8 первого порта памяти БОРП. Первый управляющий вход БОРП соединен с выходом 30.11 блока управления 6 и с входами синхронизации регистров 42.1, ..., 42.8 первого порта памяти БОРП, а второй управляющий вход БОРП соединен с выходом 30.12 блока управления 6 и с входами синхронизации регистров 43.1, ..., 43.8 второго порта памяти БОРП.

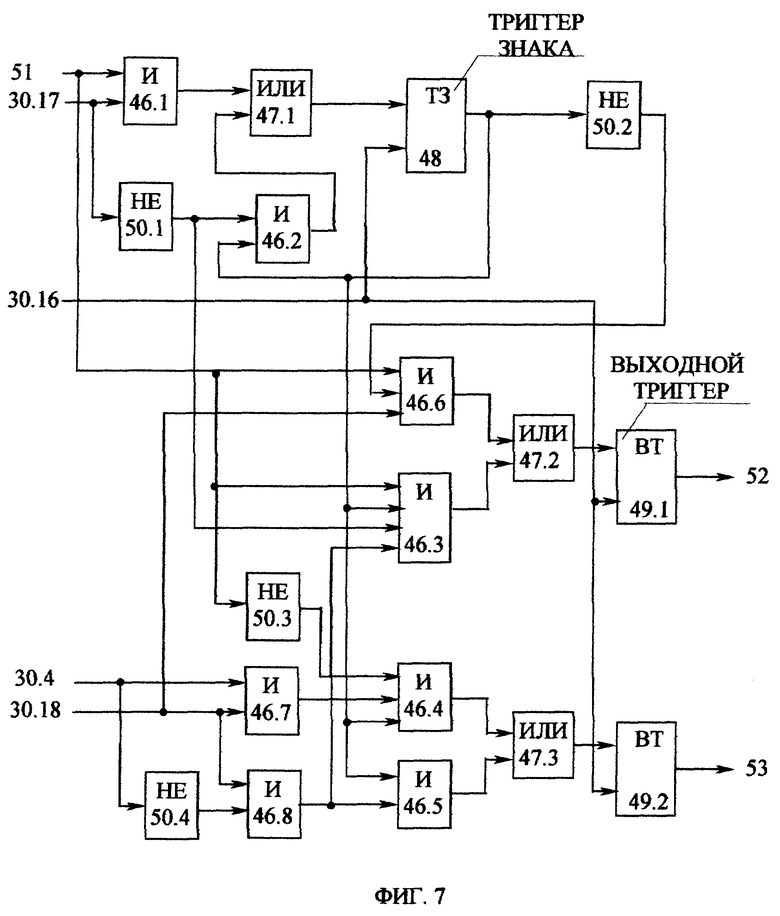

Входной преобразователь информации (ВПИ) 8 и 9 имеет восемь каналов преобразования (КП), каждый из которых содержит (см. фиг. 7) восемь элементов И 46.1, ..., 46.8, три элемента ИЛИ 47.1, ..., 47.3, триггер знака 48, выходные триггеры 49.1 и 49.2 и четыре инвертора 50.1, ..., 50.4. Выход первого элемента И 46.1 соединен с первым входом первого элемента ИЛИ 47.1, второй вход которого подключен к выходу второго элемента И 46.2, а выход соединен с информационным входом триггера знака 48. Первый вход второго элемента И 46.2 соединен с выходом первого инвертора 50.1 и с третьим входом третьего элемента И 46.3, а его второй вход соединен с выходом триггера знака 48, с третьим входом четвертого элемента И 46.4, с первым входом пятого элемента И 46.5, с входом второго инвертора 50.2 и со вторым входом третьего элемента И 46.3. Выходы шестого и третьего элементов И 46.6 и 46.3 соединены соответственно с первым и вторым входами второго элемента ИЛИ 47.2, выход которого подключен к информационному входу первого выходного триггера 49.1. Выход второго инвертора 50.2 соединен со вторым входом шестого элемента И 46.6, а выход третьего инвертора 50.3 соединен с первым входом четвертого элемента И 46.4. Выход четвертого инвертора 50.4 соединен со вторым входом восьмого элемента И 46.8, а выход седьмого элемента И 46.7 соединен со вторым входом четвертого элемента И 46.4. Выход восьмого элемента И 46.8 соединен с четвертым входом третьего элемента И 46.3 и со вторым входом пятого элемента И 46.5. Выходы четвертого и пятого элементов И 46.4 и 46.5 соединены соответственно с первым и вторым входами третьего элемента ИЛИ 47.3, выход которого подключен к информационному входу второго выходного триггера 49.2.

Информационный вход 51 КП соединен с первыми входами первого, третьего и шестого элементов И 46.1, 46.3 и 46.6 и с входом третьего инвертора 50.3. Второй управляющий вход ВПИ является вторым управляющим входом каждого из КП и соединен с выходом 30.16 блока управления 6 и с входами синхронизации триггеров 48, 49.1 и 49.2 КП, а первый управляющий вход ВПИ является первым управляющим входом каждого из КП и соединен с выходом 30.17 блока управления 6, со вторым входом первого элемента И 46.1, с третьим входом пятого элемента И 46.5 и с входом первого инвертора 50.1. Третий управляющий вход ВПИ является третьим управляющим входом каждого из КП и соединен с выходом 30.4 блока управления 6, с первым входом седьмого элемента И 46.7 и с входом четвертого инвертора 50.4, а четвертый управляющий вход ВПИ является четвертым управляющим входом каждого из КП и соединен с выходом 30.18 блока управления 6, с третьим входом шестого элемента И 46.6, со вторым входом седьмого элемента И 46.7 и с первым входом восьмого элемента И 46.8. Выходы первого и второго выходных триггеров 49.1 и 49.2 являются выходами 52 и 53 КП соответственно положительных и отрицательных значений преобразованных данных.

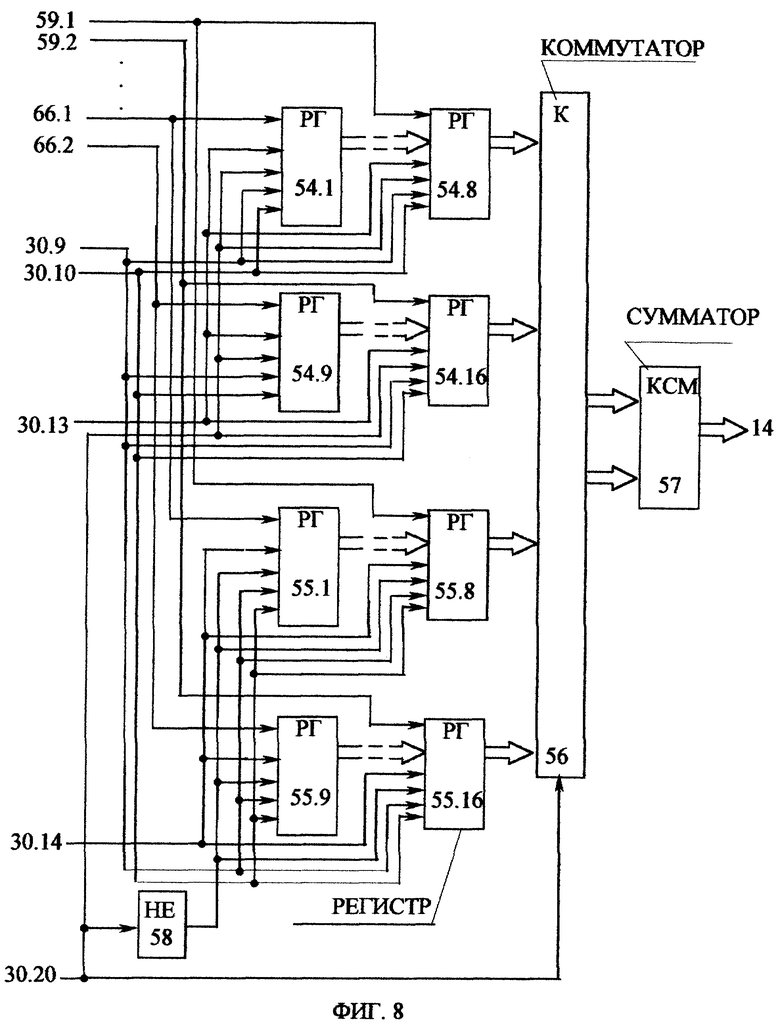

Выходной преобразователь результатов (ВПР) 13 содержит (см. фиг. 8) 19-разрядные регистры 54.1, ..., 54.8 положительных значений результатов и 19-разрядные регистры 54.9, ..., 54.16 отрицательных значений результатов первого порта памяти ВПР, 19-разрядные регистры 55.1, ..., 55.8 положительных значений результатов и 19-разрядные регистры 55.9, ..., 55.16 отрицательных значений результатов второго порта памяти ВПР, коммутатор 56, 20-разрядный комбинационный сумматор 57 и инвертор 58. Параллельные выходы первой пары регистров 54.1, 54.9 и 55.1, 55.9 первого и второго портов памяти ВПР соединены с параллельными информационными входами второй пары регистров 54.2, 54.10 и 55.2, 55.10 соответственно первого и второго портов памяти ВПР и т.д., а выходы последней 8-й пары регистров 54.8, 54.16 и 55.8, 55.16 первого и второго портов памяти ВПР соединены с информационными входами коммутатора 56, первая и вторая группы выходов которого подключены соответственно к первой и второй группам входов комбинационного сумматора 57.

Первый и второй управляющие входы ВПР соединены с выходами 30.9 и 30.10 блока управления 6 и с первым и вторым управляющими входами всех регистров 54.1, . . ., 54.16 и 55.1, ..., 55.16 ВПР. Третий управляющий вход ВПР соединен с выходом 30.13 блока управления 6 и с входами синхронизации регистров 54.1, ..., 54.16 первого порта памяти ВПР, входы переключения режима работы которых соединены с управляющим входом коммутатора 56, со входом инвертора 58, с пятым управляющим входом ВПР и с выходом 30.20 блока управления 6. Четвертый управляющий вход ВПР соединен с выходом 30.14 блока управления 6 и с входами синхронизации регистров 55.1, ..., 55.16 второго порта памяти ВПР, входы переключения режима работы которых соединены с выходом инвертора 58. Последовательные информационные входы положительных значений результатов ВПР 59.1, ..., 66.1 соединены соответственно с последовательными информационными входами регистров 54.8, ..., 54.1 и 55.8, ..., 55.1 первого и второго портов памяти ВПР. Последовательные информационные входы отрицательных значений результатов ВПР 59.2, ..., 66.2 соединены соответственно с последовательными информационными входами регистров 54.16, ..., 54.9 и 55.16, ..., 55.9 первого и второго портов памяти ВПР. Выходы комбинационного сумматора 57 являются выходами ВПР и соответственно выходами 14 устройства.

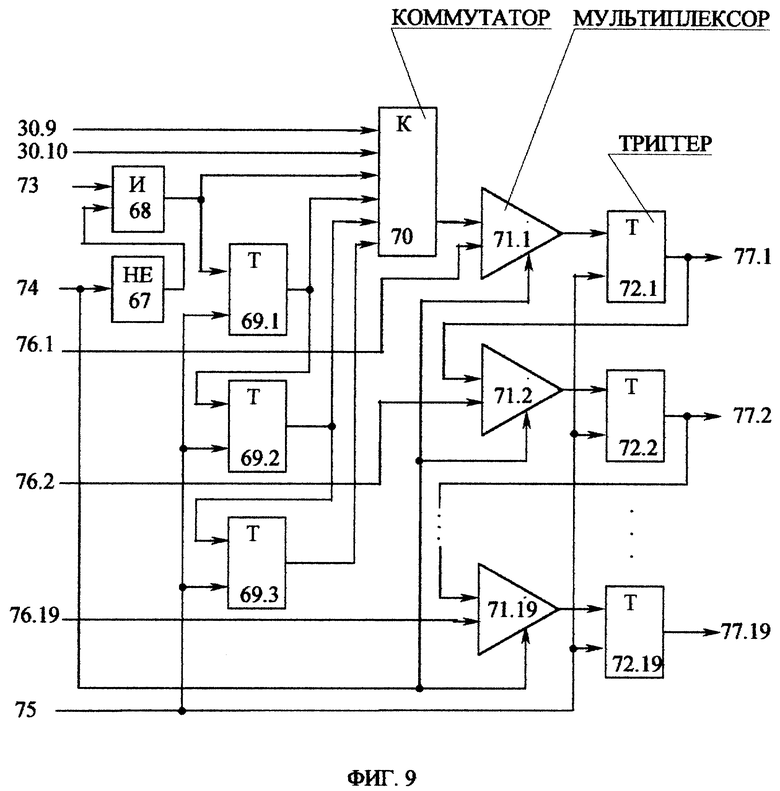

Регистр 54 ВПР содержит (см. фиг. 9) инвертор 67, элемент И 68, триггеры задержки 69.1, 69.2 и 69.3, коммутатор 70, мультиплексоры 71.1, ..., 71.19 и триггеры памяти 72.1, . . ., 72.19. Выход инвертора 67 соединен со вторым входом элемента И 68, выход которого подключен к информационному входу первого триггера задержки 69.1 и к первому информационному входу коммутатора 70, первый и второй управляющие входы которого соединены соответственно с первым и вторым управляющими входами 30.9 и 30.10 регистра 54. Второй информационный вход коммутатора 70 соединен с выходом первого триггера задержки 69.1 и с информационным входом второго триггера задержки 69.2, выход которого соединен с информационным входом третьего триггера задержки 69.3 и с третьим информационным входом коммутатора 70. Выход третьего триггера задержки 69.3 соединен с четвертым входом коммутатора 70, выход которого подключен к первому входу первого мультиплексора 71.1. Выходы мультиплексоров с 71.1 по 71.19 соединены с информационными входами триггеров памяти соответственно с 72.1 по 72.19, а первый информационный вход 73 регистра 54 соединен с первым входом элемента И 68. Управляющие входы мультиплексоров 71.1, ..., 71.19 соединены с входом инвертора 67 и с входом 74 переключения режима работы регистра 54, вход синхронизации 75 которого соединен с входами синхронизации триггеров 69.1, ..., 69.3 и 72.1, ..., 72.19. Первые информационные входы мультиплексоров с 71.2 по 71.19 подключены к выходам триггеров соответственно с 72.1 по 72.18, а вторые информационные входы мультиплексоров с 71.1 по 71.19 подключены к информационным входам регистра 54 соответственно с 76.1 по 76.19. Выходы триггеров памяти соответственно с 72.1 по 72.19 являются выходами 77.1, ..., 77.19 регистра 54.

Регистр 55 ВПР отличается от регистра 54 только тем, что содержит второй инвертор 67.2, вход которого соединен с выходом коммутатора 70, а выход подключен к первому входу первого мультиплексора 71.1.

Арифметический блок (АБ) 17 канала обработки 11 (см. фиг. 2) содержит (см. фиг. 10) четыре регистра задержки 78.1, ..., 78.4, формирователь произведения 79, коммутатор 80, первый и второй сумматоры результата 81.1 и 81.2, первый и второй регистры результата 82.1 и 82.2 и сумматор 83. Выходы первого регистра задержки 78.1 соединены с информационными входами формирователя произведения 79 и второго регистра задержки 78.2, выходы которого подключены к информационным входам третьего регистра задержки 78.3, а выходы третьего регистра задержки 78.3 соединены с информационными входами четвертого регистра задержки 78.4. Выходы четвертого регистра задержки 78.4 соединены с информационными входами коммутатора 80 соответственно с первого по четвертый. Первая и вторая группы выходов формирователя произведения 79 соединены со вторыми группами входов соответственно первого и второго сумматоров результата 81.1 и 81.2, первые группы входов которых соединены с соответствующими выходами младших разрядов соответственно первого и второго регистров результата 82.1 и 82.2, а выходы первого и второго сумматоров результата 81.1 и 81.2 соединены с информационными входами соответственно первого и второго регистров результата 82.1 и 82.2.

Выходы переноса первого и второго сумматоров результата 81.1 и 81.2 и выходы старшего разряда первого и второго регистров результата 82.1 и 82.2 соединены с информационными входами коммутатора 80 соответственно с пятого по восьмой, выходы которого подключены к информационным входам сумматора 83. Первый управляющий вход АБ соединен с выходом 30.4 блока управления 6 и с управляющим входом коммутатора 80, а второй управляющий вход АБ соединен с выходом 30.16 блока управления 6 и с входами синхронизации регистров задержки 78.1, ..., 78.4, формирователя произведения 79, первого и второго регистров результата 82.1 и 82.2 и сумматора 83. Третий управляющий вход АБ соединен с выходом 30.19 блока управления 6 и с входами установки нуля формирователя произведения 79 и первого и второго регистров результата 82.1 и 82.2, а информационные входы 84.1, ..., 84.4 АБ соединены с информационными входами первого регистра задержки 78.1. Выходы сумматора 83 являются выходами 86.1 и 86.2 соответственно положительных и отрицательных значений результата АБ.

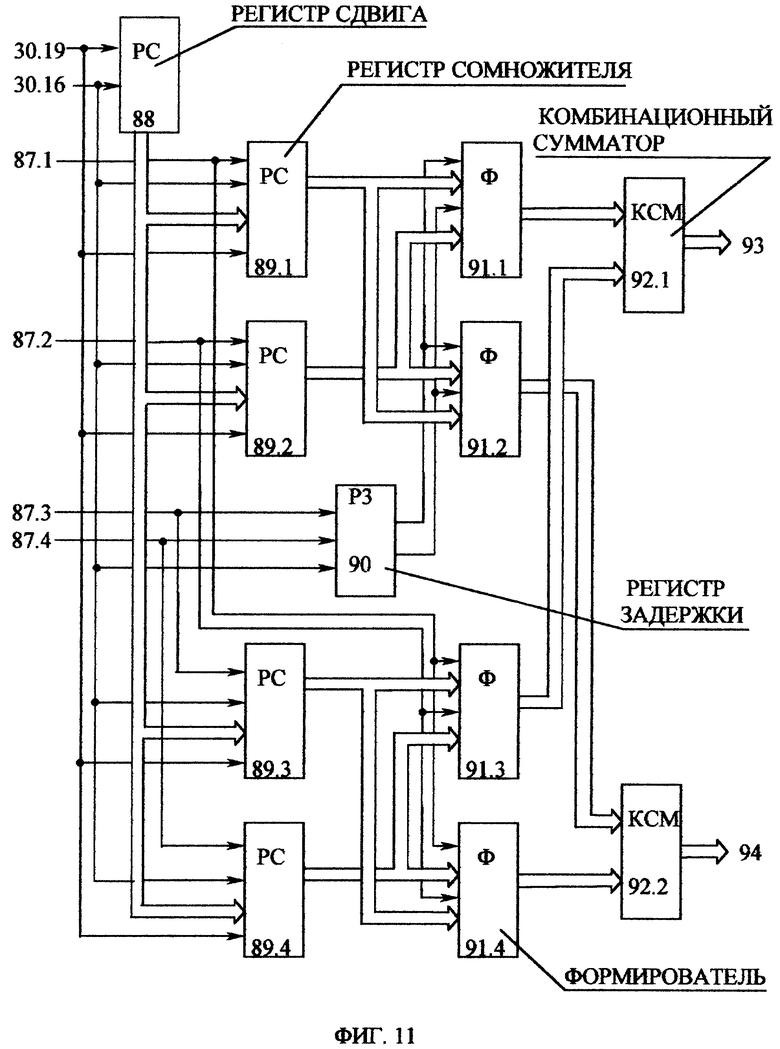

Формирователь произведения (ФП) 79 арифметического блока 17 (см. фиг. 10) канала обработки 11 (см. фиг. 2) содержит (см. фиг. 11) регистр сдвига 88, регистры сомножителя 89.1, ..., 89.4, регистр задержки 90, формирователи 91.1, ..., 91.4 и первый и второй комбинационные сумматоры 92.1 и 92.2. Выходы регистра сдвига 88 соединены с входами разрешения записи регистров сомножителей 89.1, . .., 89.4, а первый и второй выходы регистра задержки 90 подключены соответственно к первому и второму информационным входам первого и второго формирователей 91.1 и 91.2, выходы которых соединены с первой группой информационных входов соответственно первого и второго комбинационных сумматоров 92.1 и 92.2. Выходы первого регистра сомножителя 89.1 соединены с первой группой информационных входов первого формирователя 91.1 и со второй группой информационных входов второго формирователя 91.2, а выходы второго регистра сомножителя 89.2 соединены с первой группой информационных входов второго формирователя 91.2 и со второй группой информационных входов первого формирователя 91.1. Выходы третьего регистра сомножителя 89.3 соединены с первой группой информационных входов третьего формирователя 91.3 и со второй группой информационных входов четвертого формирователя 91.4, а выходы четвертого регистра сомножителя 89.4 соединены с первой группой информационных входов четвертого формирователя 91.4 и со второй группой информационных входов третьего формирователя 91.3.

Первый информационный вход 87.1 ФП соединен с информационным входом первого регистра сомножителя 89.1 и с первыми информационными входами третьего и четвертого формирователей 91.3 и 91.4, а второй информационный вход 87.2 соединен с информационным входом второго регистра сомножителя 89.2 и со вторыми информационными входами третьего и четвертого формирователей 91.3 и 91.4, выходы которых соединены со второй группой информационных входов соответственно первого и второго комбинационных сумматоров 92.1 и 92.2. Третий информационный вход 87.3 ФП соединен с информационным входом третьего регистра сомножителя 89.3 и с первым информационным входом регистра задержки 90, а четвертый информационный вход 87.4 ФП соединен со вторым информационным входом регистра задержки 90 и с информационным входом четвертого регистра сомножителя 89.4. Первый управляющий вход ФП соединен с выходом 30.19 блока управления 6, с информационным входом регистра сдвига 88 и с входами установки нуля регистров сомножителей 89.1, ..., 89.4, а второй управляющий вход ФП соединен с выходом 30.16 блока управления 6 и с входами синхронизации регистра сдвига 88, регистров сомножителей 89.1, ..., 89.4 и регистра задержки 90. Выходы первого и второго комбинационных сумматоров 92.1 и 92.2 являются соответственно первой и второй группами выходов 93 и 94 ФП.

Сумматор 18 канала обработки 11 (см. фиг. 2) и сумматор 83 АБ 17 (см. фиг. 10) содержат (см. фиг. 12) первый и второй регистры 96.1 и 96.2, входные формирователи 97.1, ..., 97.3, триггеры 98.1, ..., 98.3, элемент РАВНОЗНАЧНОСТЬ 99 и формирователь результата 100. Информационные входы 95.1, .. ., 95.4 сумматора соединены с информационными входами первого регистра 96.1, а вход синхронизации сумматора соединен с выходом 30.16 блока управления 6 и с входами синхронизации регистров 96.1 и 96.2 и триггеров 98.1, ..., 98.3. Первый и второй выходы первого регистра 96.1 соединены соответственно с первым и вторым входами первого и третьего входных формирователей 97.1 и 97.3, третий и четвертый входы которых подключены соответственно к третьему и четвертому выходам первого регистра 96.1, а первый и второй входы второго входного формирователя 97.2 соединены соответственно со вторым и четвертым выходами первого регистра 96.1. Выходы первого и второго входных формирователей 97.1 и 97.2 соединены с информационными входами соответственно первого и второго триггеров 98.1 и 98.2, а выход третьего входного формирователя 97.3 соединен со вторым входом элемента РАВНОЗНАЧНОСТЬ 99 и с четвертым входом формирователя результата 100, третий вход которого подключен к выходу первого триггера 98.1 и к первому входу элемента РАВНОЗНАЧНОСТЬ 99. Первый и второй входы формирователя результата 100 соединены с выходами соответственно третьего и второго триггеров 98.3 и 98.2, а выходы формирователя результата 100 подключены к информационным входам второго регистра 96.2. Информационный вход третьего триггера 98.3 соединен с выходом элемента РАВНОЗНАЧНОСТЬ 99, а выходы второго регистра 96.2 являются выходами 101.1 и 101.2 соответственно положительных и отрицательных значений результата сумматора.

Формирователь результата (ФР) 100 сумматоров 18 и 83 содержит (см. фиг. 13) первый и второй инверторы 102.1 и 102.2, первый и второй элементы 2И-3ИЛИ-НЕ 103.1 и 103.2 и элемент 2ИЛИ-НЕ 104. Выходы первого и второго инверторов 102.1 и 102.2 соединены соответственно с первым и третьим входами первого элемента 2И-3ИЛИ-НЕ 103.1, второй вход которого соединен с первыми входами второго элемента 2И-3ИЛИ-НЕ 103.2 и элемента 2ИЛИ-НЕ 104 и со вторым входом 105.2 ФР, а четвертый вход первого элемента 2И-3ИЛИ-НЕ 103.1 соединен со вторым входом элемента 2ИЛИ-НЕ 104 и с третьим входом 105.3 ФР. Первый вход 105.1 ФР соединен с входом второго инвертора 102.2 и с третьим входом второго элемента 2И-3ИЛИ-НЕ 103.2, четвертый вход которого соединен с выходом элемента 2ИЛИ-НЕ 104, а второй вход подключен к четвертому входу 105.4 ФР и к входу первого инвертора 102.1. Выходы первого и второго элементов 2И-3ИЛИ-НЕ 103.1 и 103.2 являются соответственно первым и вторым выходами 106.1 и 106.2 ФР.

Устройство работает согласно алгоритму работы, приведенному на фиг. 14.

По шине управляющих сигналов 7 устройства (см. фиг. 1) в блок управления (БУ) 6 поступает сигнал установки начального состояния устройства, который запускает генератор тактовых импульсов и обнуляет все триггеры и регистры БУ 6. Начальное состояние остальных блоков устройства устанавливается в процессе работы устройства. По шине команд 5 поступает код операции и записывается в блок управления 6 импульсом записи команд, поступающим по шине управляющих сигналов 7. По шине управляющих сигналов 7 устройства в БУ 6 поступают строб записи операндов и импульсы внешней синхронизации для записи в регистры одного из портов блоков ортогональной регистровой памяти (БОРП) 3 и 4 k-разрядных (где k - разрядность входных сигналов) операндов, поступающих в устройство соответственно по первой и второй шинам данных 1 и 2. В нулевом цикле работы устройства запись входных данных производится в регистры первых портов памяти БОРП 3 и 4, а в каналы обработки подаются нулевые значения операндов. По окончании записи 4N операндов (пачки входных операндов для одного цикла обработки) в каждый из двух БОРП 3 и 4 БУ 6 вырабатывает сигнал переключения портов памяти БОРП 3 и 4 и импульс начала цикла обработки.

По импульсу начала цикла обработки в блоке управления 6 формируется строб чтения операндов, по которому производится чтение операндов из регистров одного из портов каждого из БОРП 3 и 4 на входы входных преобразователей информации (ВПИ) 8 и 9. В первом цикле работы устройства из регистров первого порта памяти каждого из БОРП 3 и 4 производится чтение первой пачки данных, записанных в нулевом цикле работы устройства. Одновременно, с приходом по шине управляющих сигналов 7 устройства в БУ 6 следующего строба записи операндов, в регистры второго порта памяти БОРП 3 и 4 записывается следующая пачка k-разрядных входных операндов, поступающих в устройство соответственно по первой и второй шинам данных 1 и 2.

Из блока управления 6 подается код операции в коммутатор операндов 10, в каналы обработки (КО) 11.1, ... 11.N, в коммутатор результатов (КР) 12 и в выходной преобразователь результатов (ВПР) 13 устройства, а также выдаются синхроимпульсы и управляющие сигналы для выполнения цикла обработки пачки входных операндов. Управляющие сигналы, включая и синхроимпульсы, подаются из БУ 6 в БОРП 3 и 4, в ВПИ 8 и 9, в каналы обработки (КО) 11.1, ... 11.N и в ВПР 13.

В каждом цикле обработки из регистров памяти БОРП 3 и 4 выдаются последовательным кодом, старшими разрядами вперед, операнды предыдущего цикла записи. Чтение данных из БОРП 3 и 4 производится с частотой внутреннего генератора синхроимпульсов БУ 6. Информация с выходов БОРП 3 и 4 поступает на информационные входы соответственно первого и второго ВПИ 8 и 9, где операнды преобразуются в знакоразрядный код.

Преобразованные в знакоразрядный код операнды (по двухразрядной шине АР и AM каждый) поступают в коммутатор операндов 10, который коммутирует потоки данных из первого и второго ВПИ 8 и 9 и из КР 12 на информационные входы КО 11.1, ..., 11.N. В каждый из n каналов обработки поступает восемь операндов. По импульсу запуска КО, поступающему из БУ 6, в КО производятся поразрядные вычисления в избыточной системе счисления, в соответствии с кодом операции, с частотой внутренней синхронизации. Полученные в КО 11, ..., 11.N результаты вычислений коммутируются в коммутаторе результатов 12 в выходной преобразователь результатов (ВПР) 13 в соответствии с порядком их выдачи из устройства. Положительные и отрицательные значения результатов вычислений накапливаются в 8N (k+3)-разрядных регистрах одного из портов памяти ВПР 13. По окончании записи результатов вычислений БУ 6 выдает сигнал переключения портов памяти ВПР 13, и с приходом строба выдачи результатов по шине управляющих сигналов 7 устройства полученные результаты обработки с частотой внешней синхронизации выдаются в параллельном дополнительном коде на выходную шину 14 устройства с одновременным преобразованием результатов вычислений из знакоразрядного кода в параллельный дополнительный код.

В устройстве производится одновременное выполнение многих процессов обработки данных: запись входных операндов в регистры БОРП; чтение данных из БОРП; преобразование данных в ВПИ в знакоразрядный код; выполнение операций в КО (умножение, суммирование, БПФ и т.д.); преобразование результатов обработки в параллельный дополнительный код; вывод результатов.

Предлагаемый способ цифровой обработки сигналов позволяет увеличивать частоту внутренних синхроимпульсов и число каналов обработки в зависимости от величины кристалла СБИС и технологии его изготовления, т.е. увеличивать производительность устройства.

Цикл обработки сигналов в устройстве составляет 20 тактов внутренних синхроимпульсов и при частоте этих импульсов 100 МГц равен 200 пс. При этом устройство может выполнить за один цикл обработки 8 комплексных умножений или две "бабочки" БПФ, т.е. производительность устройства составляет 40 млн. операций комплексного умножения в секунду. Для одного цикла обработки необходимо подать в устройство 4N операндов. При N = 2 для одного цикла обработки требуется подать 8 операндов, т.е. запись операндов может осуществляться с частотой 40 МГц. При двухкаскадной архитектуре каналов обработки (например, при N = 4), при которой входы второго каскада каналов обработки соединены с выходами каналов обработки первого каскада и с выходами второго входного преобразователя информации 8, с помощью коммутаторов операндов и результатов также требуется подать 8 операндов. При этом производительность устройства составит 80 млн. операций комплексного умножения в секунду.

Рассмотрим работу и примеры технической реализации блоков устройства при N = 2 и при 10-разрядном коде операций.

Работа устройства начинается с установки начального состояния блока управления (БУ) 6 (см. фиг. 3). По шине управляющих сигналов 7 устройства на четвертый управляющий вход 7.4 блока управления БУ 6 поступает сигнал запуска генератора тактовых импульсов (ГТИ) 27 и обнуления всех триггеров и регистров БУ 6 (счетчика записи 24, триггера записи 25 и формирователя управляющих сигналов 29). По шине команд 5 устройства подается код операции обработки, выполняемой в устройстве, который записывается в первый регистр команд 22 БУ. По шине управляющих сигналов 7 устройства на второй и третий управляющие входы 7.2 и 7.3 БУ 6 поступают строб записи операндов и импульсы внешней синхронизации, а на пятый управляющий вход 7.5 БУ 6 поступает строб выдачи результатов обработки. Строб записи операндов подается на вход разрешения счета счетчика записи 24 и на первый вход коммутатора синхроимпульсов 26. Импульсы внешней синхронизации подаются на входы синхронизации счетчика записи 24 и триггера записи 25, а также на третий вход коммутатора синхроимпульсов 26.

Счетчик записи 24 подсчитывает число записываемых операндов и по окончании записи 4N операндов (пачки входных операндов для одного цикла обработки) триггер записи 25 переходит в единичное состояние по сигналу переноса (N+1)-го разряда счетчика записи 24 и по первому же тактовому импульсу генератора тактовых импульсов ГТИ 27 запускается формирователь управляющих сигналов (ФУС) 29. С выхода старшего (N+2)-го разряда счетчика записи 24 на второй вход коммутатора синхроимпульсов 26 подается строб переключения синхроимпульсов регистров БОРП 3 и 4. С выходов второго регистра команд 23 на выходы 32.1, . . . , 32.10 БУ 6 выдается код операции, выполняемой в устройстве. С первого и второго выходов коммутатора 26 на выходы 32.11 и 32.12 БУ 6 выдаются синхроимпульсы регистров соответственно первого и второго портов памяти БОРП 3 и 4, сигнал переключения которых выдается с выхода старшего разряда счетчика записи 24 на выход 30.15 БУ 6. С третьего и четвертого выходов коммутатора 26 на выходы 30.13 и 30.14 БУ 6 выдаются синхроимпульсы регистров соответственно первого и второго портов памяти ВПР 13, сигнал переключения которых выдается с шестого выхода ФУС 29 на выход 30.20 БУ 6, на выход 32.16 которого выдаются внутренние синхроимпульсы генератора тактовых импульсов 27.

С первого выхода ФУС 29 на выход 32.17 БУ 6 выдается импульс начала цикла обработки для записи значений знаковых разрядов входных операндов в триггеры знака ВПИ 8 и 9. Импульс начала цикла обработки сбрасывает в нулевое состояние триггер записи 28 и переписывает код операции с выходов буферного регистра команд 22 в рабочий регистр команд 23, с выходов которого код операции подается на выходы 30.1, ..., 30.10 БУ 6. С четвертого выхода ФУС 29 на выход 30.19 БУ 6 выдается импульс запуска вычислений в каналах обработки 11.1, ..., 11.N. Цикл чтения пачки данных из БОРП 3 и 4 заканчивается раньше цикла записи новой пачки данных. По окончании записи новой пачки данных переключается режим работы регистров БОРП 3 и 4 и запускается новый цикл обработки.

С приходом сигнала окончания записи пачки данных с выхода триггера записи 25 БУ 6 на информационный вход триггера 32.1 ФУС 29 (см. фиг 4) вырабатывает одиночный импульс начала цикла обработки (триггеры 32.1 и 32.2, инвертор 36.1 и элемент И 34.3), который подается на информационные входы первого разряда регистра сдвига 33 и третьего триггера 32.3. Третий триггер 32.3 переходит в единичное состояние по заднему фронту синхроимпульса, поступающего на вход синхронизации ФСУ 29 со входа 30.16, вырабатывая строб чтения операндов, который стробирует синхроимпульсы, поступающие на первый вход элемента И 34.1. При этом на второй и третий выходы 30.18 и 37 ФУС 29 выдаются соответственно строб чтения операндов длительностью 16 тактов внутренней частоты синхронизации и 16 синхроимпульсов, которые подаются в коммутатор синхроимпульсов 26 ФУС 29. Сброс триггера 32.3 и соответственно строба чтения операндов в нулевое состояние производится импульсом с выхода 16-го разряда регистра 33. Импульс с выхода 14-го разряда регистра 33 поступает на информационный вход четвертого триггера 32.4 и перебрасывает его в единичное состояние по заднему фронту синхроимпульса, вырабатывая строб чтения результатов, длительностью 19 тактов внутренней частоты синхронизации, который стробирует синхроимпульсы, поступающие на первый вход элемента И 34.2. При этом на пятый выход 38 ФУС 29 выдается 19 синхроимпульсов с выхода генератора 27, которые подаются в коммутатор синхроимпульсов 26 ФУС 29. Сброс триггера 32.4 и соответственно строба чтения результатов в нулевое состояние производится импульсом с выхода 33-го разряда регистра 33. Импульс с выхода 34-го разряда регистра 33 поступает на вход синхронизации пятого триггера 32.5, который вырабатывает сигнал переключения портов памяти выходного преобразователя результатов 13 и выдает его на шестой выход 30.20 ФУС 29 устройства и на седьмой вход коммутатора синхроимпульсов 26.

Синхроимпульсы внешней синхронизации, поступающие на второй вход элемента И 39.1 и на первый вход элемента И 39.2 коммутатора синхроимпульсов 26 (см. фиг. 5) со входа 7.3 устройства, стробируются стробом записи операндов, поступающим на первый вход коммутатора синхроимпульсов 26 со входа 7.2 устройства, и стробом вывода результатов, поступающим на четвертый вход коммутатора синхроимпульсов 26 со входа 7.5 устройства. Первый и второй мультиплексоры 40.1 и 40.2 коммутатора синхроимпульсов 26 коммутируют пачки синхроимпульсов внешней синхронизации с выхода элемента И 39.1 и пачки синхроимпульсов внутренней синхронизации с пятого входа 37 коммутатора синхроимпульсов 26. Третий и четвертый мультиплексоры 40.3 и 40.4 коммутатора синхроимпульсов 26 коммутируют пачки синхроимпульсов внешней синхронизации с выхода элемента И 39.2 и пачки синхроимпульсов внутренней синхронизации с шестого входа 38 коммутатора синхроимпульсов 26. Первый и второй мультиплексоры 40.1 и 40.2 переключаются сигналом переключения синхроимпульсов регистров соответственно первого и второго портов памяти БОРП 3 и 4, подаваемым на второй вход 30.15 коммутатора синхроимпульсов 26, а третий и четвертый мультиплексоры 40.3 и 40.4 коммутатора синхроимпульсов 26 переключаются сигналом переключения синхроимпульсов регистров соответственно первого и второго портов памяти ВПР 13, подаваемым на седьмой вход 30.20 коммутатора синхроимпульсов 26.

Если сигнал на втором входе 30.15 коммутатора синхроимпульсов 26 равен нулю, то с выхода первого мультиплексора 40.1 на выход 3.11 БУ 6 выдается 8N импульсов записи операндов на входы синхронизации регистров первых портов памяти БОРП 3 и 4, а с выхода второго мультиплексора 40.2 на выход 30.12 БУ 6 выдается 16 импульсов чтения операндов (тактовые импульсы генератора 27 БУ) на входы синхронизации регистров вторых портов памяти БОРП 3 и 4.

Если сигнал на втором входе 30.15 коммутатора синхроимпульсов 26 равен единице, то с выхода первого мультиплексора 40.1 на выход 30.11 БУ 6 выдается 16 импульсов чтения операндов (тактовые импульсы генератора 27 БУ) на входы синхронизации регистров первых портов памяти БОРП 3 и 4, а с выхода второго мультиплексора 40.2 на выход 30.12 БУ 6 выдается 8N импульсов записи операндов на входы синхронизации регистров вторых портов памяти БОРП 3 и 4.

Если сигнал на седьмом входе 30.20 коммутатора синхроимпульсов 26 равен нулю, то с выхода третьего мультиплексора 40.3 на выход 30.13 БУ 6 выдается 19 импульсов записи результатов на входы синхронизации регистров первого порта памяти ВПР 13, а с выхода четвертого мультиплексора 40.4 на выход 30.14 БУ 6 выдается 8N импульсов вывода результатов на входы синхронизации регистров второго порта памяти ВПР 13.

Если сигнал на седьмом входе 30.20 коммутатора синхроимпульсов 26 равен единице, то с выхода третьего мультиплексора 40.3 на выход 30.13 БУ 6 выдается 8N импульсов вывода результатов на входы синхронизации регистров первого порта памяти ВПР 13, а с выхода четвертого мультиплексора 40.4 на выход 30.14 БУ 6 выдается 19 импульсов записи результатов на входы синхронизации регистров второго порта памяти ВПР 13.

Входные операнды в виде k-разрядных чисел в параллельном дополнительном коде подаются в устройство по двум шинам данных 1 и 2 и поступают на информационные входы 41 БОРП (см. фиг. 6). В регистрах двухпортовых БОРП 3 и 4 накапливаются входные операнды, которые поступают со входа 41 БОРП на параллельные информационные входы первых регистров 42.1 и 43.1 первого и второго портов памяти БОРП и далее продвигаются на параллельные информационные входы регистров 42.2, ..., 42.8 и 43.2, ..., 43.8. На третий управляющий вход БОРП с выхода 30.15 БУ 6 подается сигнал переключения портов памяти БОРП.

Если сигнал на третьем управляющем входе БОРП равен нулю, то регистры 42.1, ..., 42.8 первых портов памяти БОРП 3 и 4 работают в режиме параллельной записи входных операндов, а регистры 43.1, ..., 43.8 вторых портов памяти БОРП 3 и 4 работают в режиме выдачи последовательных кодов ранее записанных операндов. При этом в регистры 42.1, ..., 42.8 первых портов памяти БОРП 3 и 4 запишется по 8N k-разрядных операндов, поступающих в устройство соответственно по первой и второй k-разрядным шинам данных 1 и 2, а коммутатор 44 БОРП выдаст на выходы БОРП последовательным кодом старшими разрядами вперед 8N операндов из регистров 43.1, ..., 43.8 вторых портов памяти каждого из БОРП 3 и 4.

Если сигнал на третьем управляющем входе БОРП равен единице, то регистры 42.1, . . . , 42.8 первых портов памяти БОРП 3 и 4 работают в режиме выдачи последовательных кодов ранее записанных операндов, а регистры 43.1, ..., 43.8 вторых портов памяти БОРП 3 и 4 работают в режиме параллельной записи входных операндов. При этом в регистры 43.1, ..., 43.8 вторых портов памяти БОРП 3 и 4 запишется по 8N k-разрядных операндов, а коммутатор 44 БОРП выдаст на выходы БОРП последовательным кодом старшими разрядами вперед 8N операндов из регистров 42.1, ..., 42.8 первых портов памяти каждого из БОРП 3 и 4.

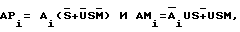

Входные преобразователи информации (ВПИ) 8 и 9 преобразуют входные операнды из дополнительного кода в знакоразрядный код, в котором каждый i-й разряд операнда Ai представлен двумя шинами: APi - положительных значений i-го разряда операнда и AMi - отрицательных значений i-го разряда операнда. Каждый из ВПИ 8 и 9 имеет 8N каналов преобразования (КП), на информационный вход 51 которого (см. фиг 7) подается последовательным кодом старшими разрядами вперед преобразуемый операнд A. В отсутствии строба чтения операндов на четвертом управляющем входе 30.18 КП на выходы 52 и 53 КП выдаются нули. С приходом импульса начала цикла обработки M на второй управляющий вход 30.17 КП по переднему фронту синхроимпульса, поступающего на вход синхронизации 30.16 КП, в триггер знака 48 запишется значение знакового разряда преобразуемого операнда S. В зависимости от знака операнда S и от управляющего сигнала управления U, поступающего на третий управляющий вход 30.4, КП вырабатывает положительные APi и отрицательные AMi значения i-го разряда операнда Ai в соответствии с логическими выражениями

где Ai - значение i-го разряда операнда на входе 51 КП; APi - положительное значение i-го разряда операнда на первом выходе 52 КП; AMi - отрицательное значение i-го разряда операнда на втором выходе 53 КП; U - сигнал выполнения операции умножения в АБ 17; S - значение знакового разряда операнда Ai; M - строб записи знака операнда в триггер знака 48 КП (одиночный импульс с выхода 30.17 БУ).

Преобразованные в знакоразрядный код операнды (по двухразрядной шине AP и AM каждый) поступают в коммутатор операндов 10 (см. фиг. 2), который коммутирует потоки данных от ВПИ 8 и 9 и от коммутатора результатов 12 на входы каналов обработки 11.1, ..., 11.N. В данном примере реализации устройства коммутатор операндов 10 пропускает на i-й выход значения операнда с i-го входа, т.е. коммутирует только потоки данных от ВПИ 8 и 9.

Первый коммутатор данных 16 канала обработки (КО) 11 (см. фиг. 2) в общем случае может коммутировать на любой вход любого АБ 17.1, ...,17.4 операнд с любого входа КО. В рассматриваемом примере при 11-разрядном коде операции первый коммутатор данных 16 управляется значениями трех первых разрядов [2.. . 0] кода заданной операции, который подается на управляющие входы 15 КО с входов 30.1, ..., 30.3 БУ 6. Первый коммутатор данных 16 КО 11 коммутирует входные данные Ai (с выходов первого ВПИ 8) и Bi (с выходов второго ВПИ 9) на первый и второй входы a и b арифметических блоков АБ 17.1, ..., 17.4 и на первые входы регистров задержки 19.1 и 19.2 (см. таблицу 1).

АБ 17.1, ..., 17.4 (см. фиг. 2) выполняют операцию умножения двух операндов "A x B", если четвертый разряд [3] кода операции, поступающий с выхода 30.4 БУ 6, находится в единичном состоянии, или операцию суммирования "A + B" двух операндов, если четвертый разряд [3] кода операции находится в нулевом состоянии.

Для получения отрицательных значений операнда "B" коммутатор данных 16 подает по шине BP отрицательные значения операнда B, а по шине BM коммутатор данных 16 подает положительные значения операнда B, т.е. инвертирует знак каждого значащего разряда.

Сумматоры 18.1 и 18.2 (см. фиг. 2) выполняют операцию "a + b", если пятый разряд [4] кода операции, поступающий с выхода 30.5 БУ 6, находится в нулевом состоянии, или операцию "a + 0", если пятый разряд [4] кода операции находится в единичном состоянии.

Регистры задержки 19.1 и 19.2 КО (см. фиг. 2) служат для выравнивания задержки конвейера данных и выдают на свои выходы задержанный на 12 тактов операнд с выхода первого коммутатора данных 16, если пятый разряд [4] кода операции находится в нулевом состоянии, или задержанный на 4 такта результат с выходов соответственно второго и четвертого АБ 17.2 и 17.4, если пятый разряд [4] кода операции находится в единичном состоянии.

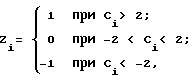

Второй коммутатор данных 20 (см. фиг. 2) коммутирует данные с выходов первого и второго сумматоров 18.1 и 18.2 и с выходов первого и второго регистров задержки 19.1 и 19.2 на входы сумматоров с третьего 18.3 по шестой 18.6 и управляется в рассматриваемом примере шестым разрядом [5] кода операции (см. таблицу 2), который подается с выхода 30.6 БУ 6.

Сумматоры 18.3, 18.4, 18.5 и 18.6 (см. фиг. 2) работают в зависимости от состояния седьмого разряда [6] кода операций, подаваемого с выхода 30.7 БУ 6. Если седьмой разряд кода операций равен нулю, то сумматоры 18.3, ..., 18.6 выполняют операцию "a + b", а если седьмой разряд кода операций равен единице, то сумматоры 18.3, ..., 18.6 выполняют операцию "a + 0".

Коммутатор результатов 12 (см. фиг. 1) коммутирует результаты вычислений в КО 11.1, ..., 11.N на входы ВПР 13 в соответствии с порядком их выдачи на выход 14 устройства и управляется в рассматриваемом примере восьмым разрядом [7] кода операции (см. таблицу 3), подаваемым с выхода 30.8 БУ 6.