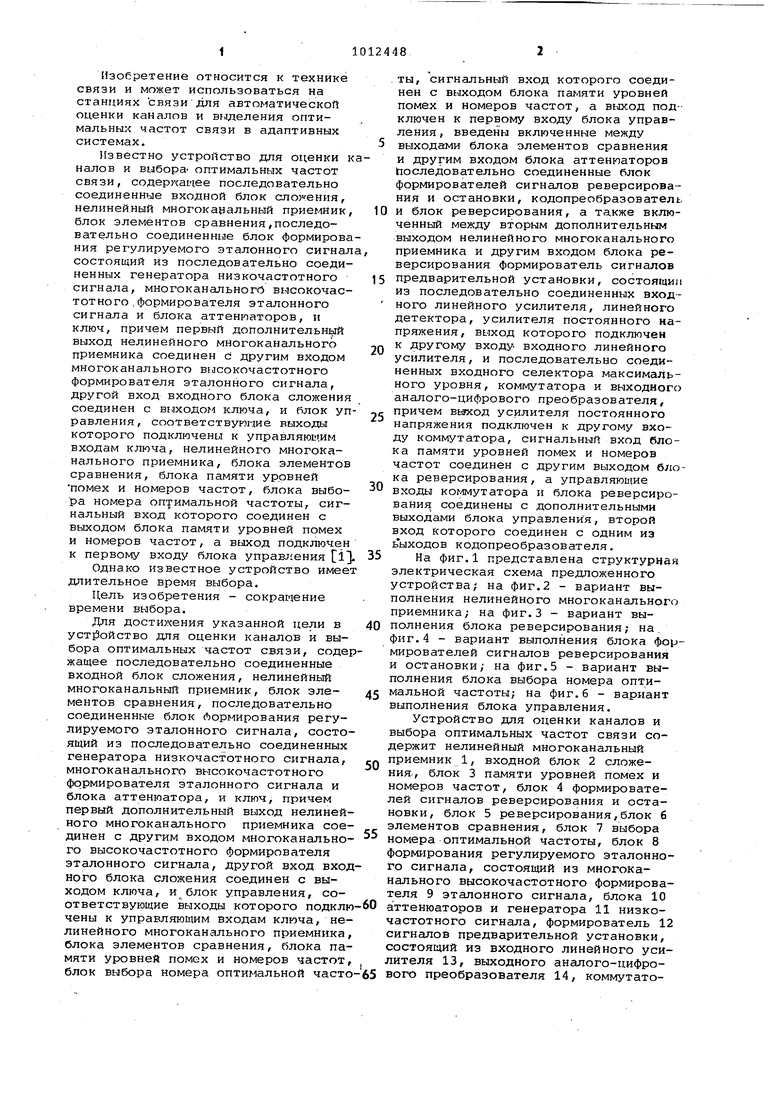

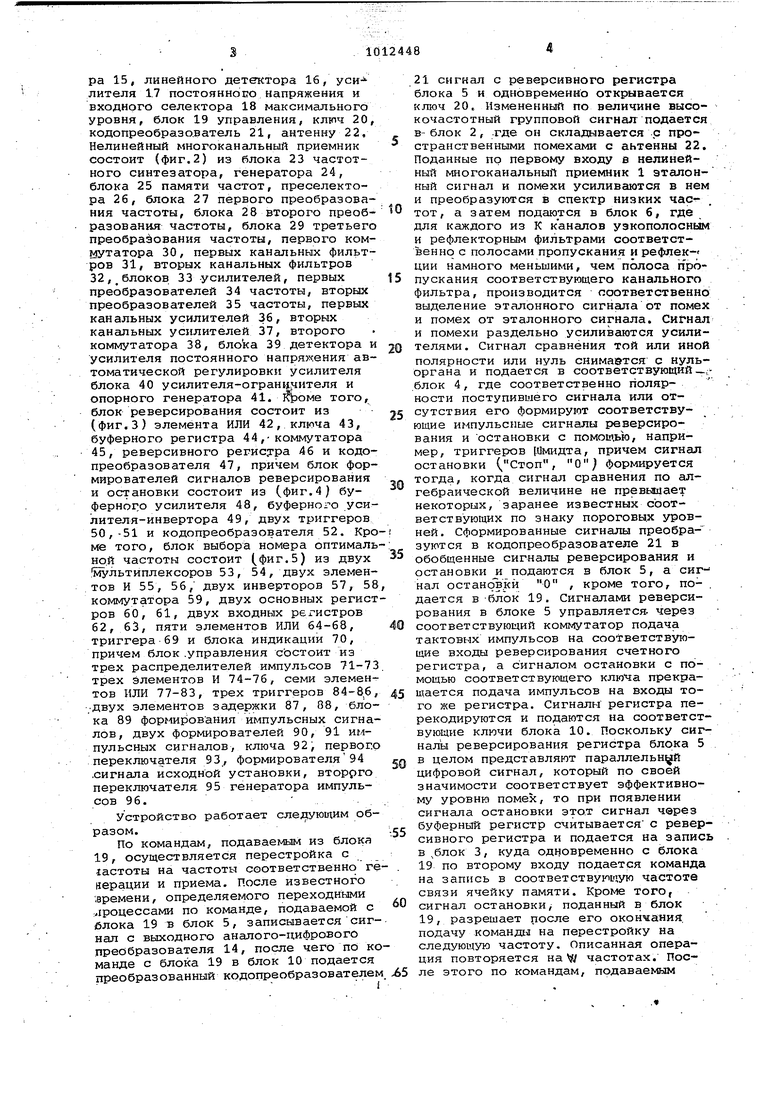

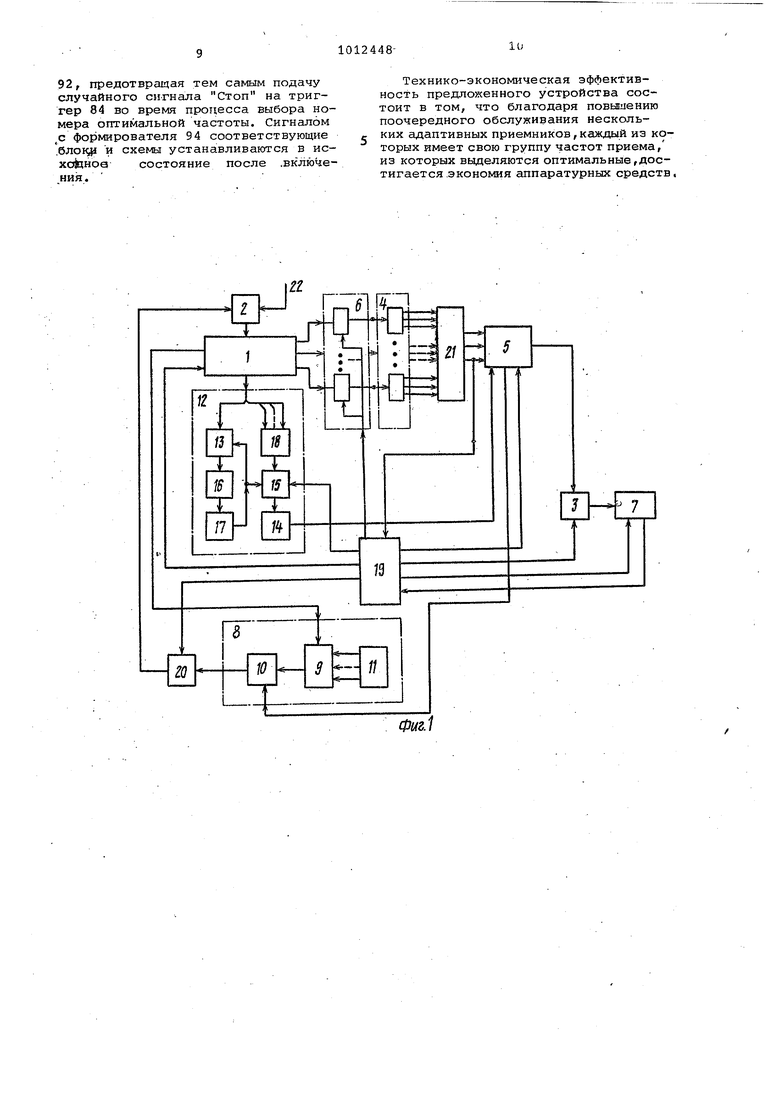

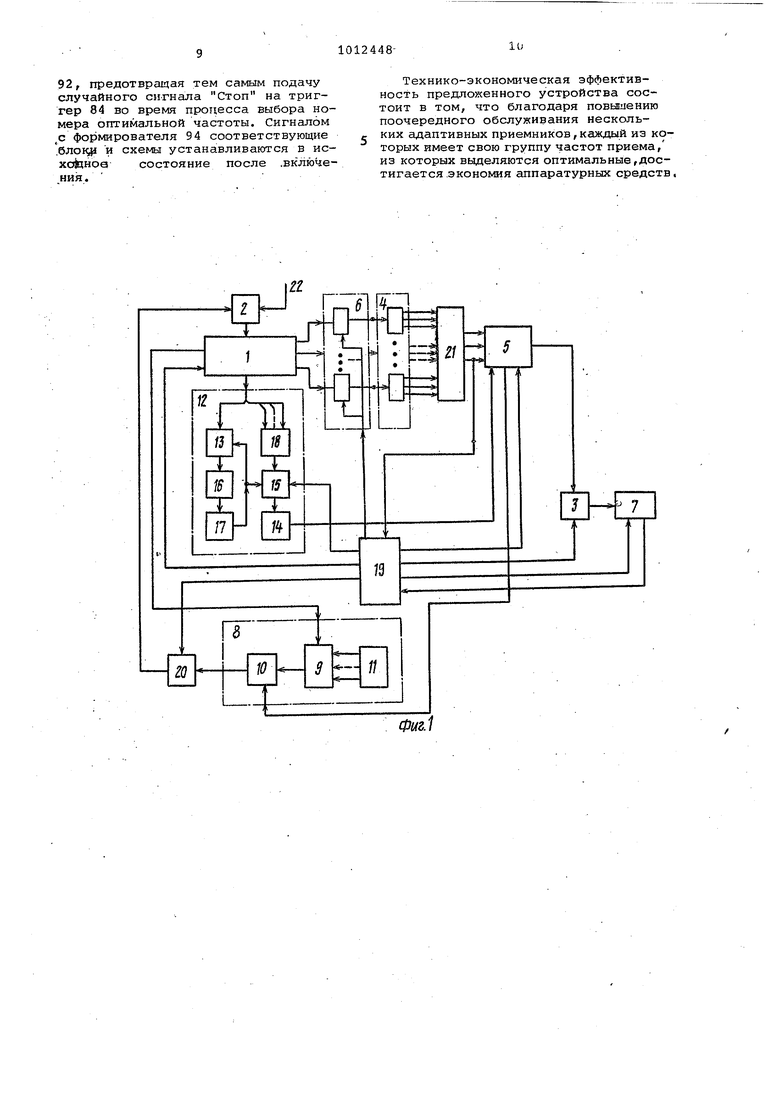

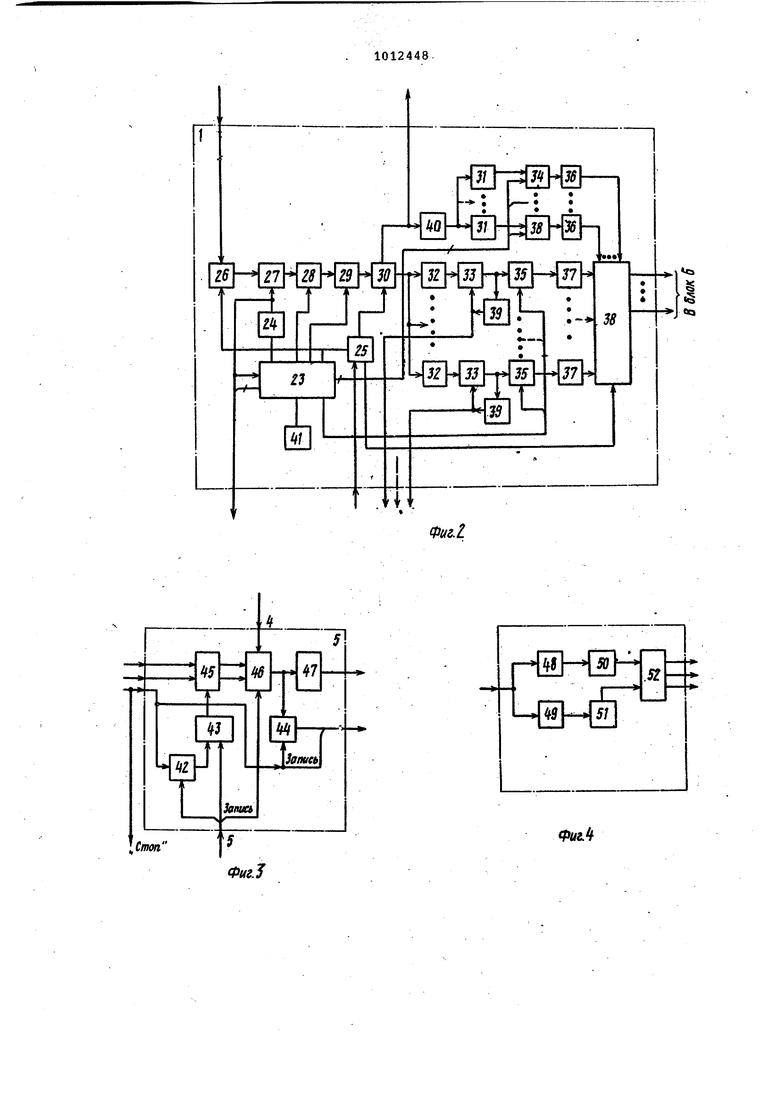

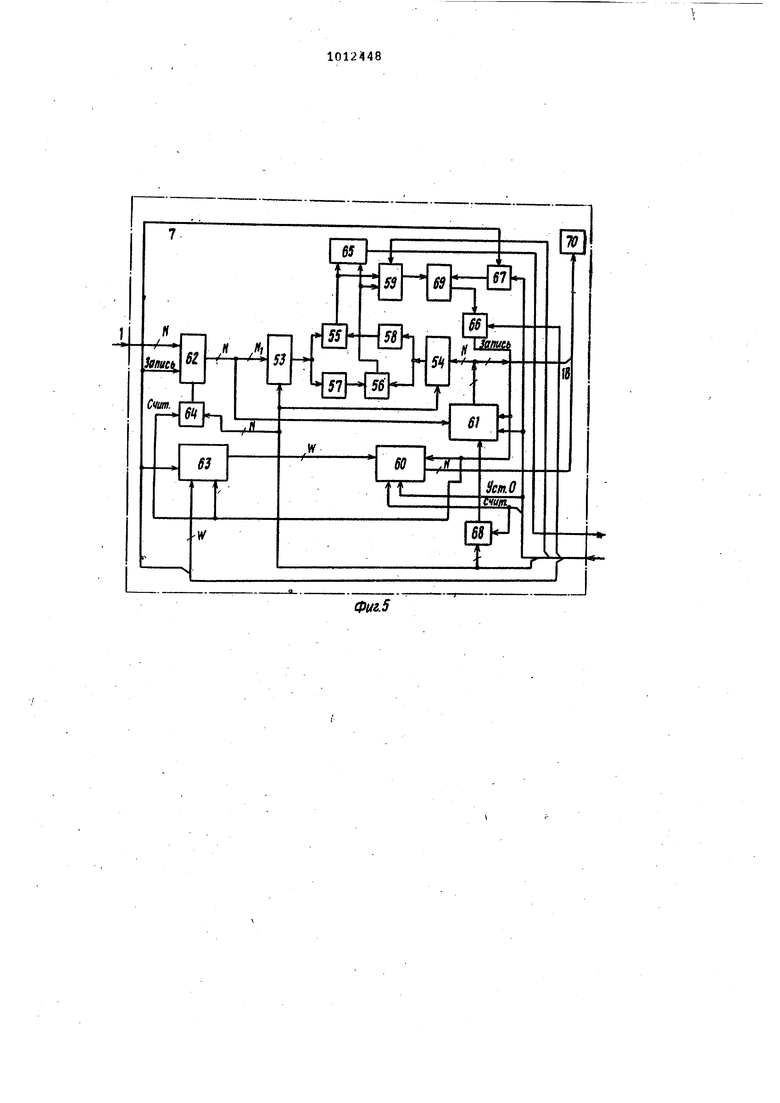

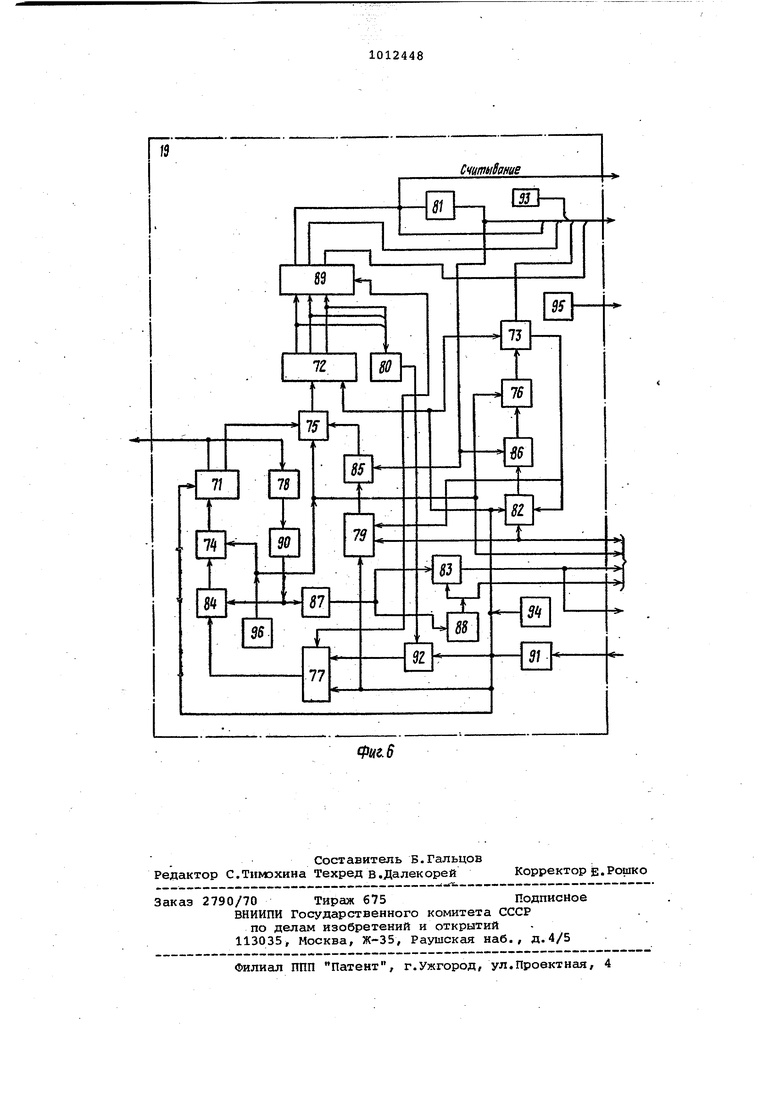

Изобретение относится к технике связи и может использоваться на станциях связи для автоматической оценки каналов и враделения оптимальных частот связи в адаптивных системах. Известно устройство для оценки к налов и выбора оптимальных частот связи, содерка чее последовательно соединенные входной блок сложения, нелинейный многоканальный приемник, блок элементов сравнения,последовательно соединенные блок формирова ния регулируемого эталонного сигнал состоящий из последовательно соединенных генератора низкочастотного сигнала, многоканального высокочастотного .формирователя эталонного сигнала и блока аттенюаторов, и ключ, причем первый дополнительньгй выход нелинейного многоканального приемника соединен с другим входом многоканального высокочастотного формирователя эталонного сигнала, другой вход входного блока сложения соединен с выходом ключа, и блок уп равления , соответствупгдие выходы которого подключены к управляющим входам ключа, нелинейного многоканального приемника, блока элементов сравнения, блока памяти уровней помех и номеров частот, блока выбора номера оптимальной частоты, сигнальный вход которого соединен с выходом блока памяти уровней помех и номеров частот, а выход подключен к первому входу блока управления Ci Однако известное устройство имее длительное время выбора. Цель изобретения - сокращение времени выбора. Для достижения указанной цели в уст13ойство для оценки каналов и выбора оптимальных частот связи, соде жащее последовательно соединенные входной блок сложения, нелинейный многоканальный приемник, блок элементов сравнения, последовательно соединенные блок (Нормирования регулируемого эталонного сигнала, состо ящий из последовательно соединенных генератора низкочастотного сигнала, многоканального высокочастотного формирователя эталонного сигнала и блока аттенюатора, и ключ, причем первый дополнительный выход нелиней ного многоканального приемника сое динен с другим входом многоканально го высокочастотного формирователя эталонного сигнала, другой вход вхо ного блока сложения соединен с выходом ключа, и блок управления, соответствующие выходы которого подкл чены к управляющим входам ключа, не линейного многоканального приемника блока элементов сравнения, блока па мяти уровней помех и номеров частот блок выбора номера оптимальной част ты, сигнальный вход которого соединен с выходом блока па 1яти уровней помех и номеров частот, а выход под-ключе н к первому входу блока управления, введены включенные между выходами блока элементов сравнения и другим входом блока аттенюаторов (последовательно соединенные блок формирователей сигналов реверсирования и остановки, кодопреобразователь и блок реверсирования, а также включенный между вторым дополнительным выходом нелинейного многоканального приемника и другим входом блока реверсирования формирователь сигналов предварительной установки, состоящил из последовательно соединенных входного линейного усилителя, линейного детектора, усилителя постоянного напряжения, выход которого подключен к другому входу- входного линейного усилителя, и последовательно соединенных входного селектора максимального уровня, коммутатора и выходного аналого-цифрового преобразователя, причем вьгход усилителя постоянного напряжения подключен к другому входу коммутатора, сигнальный вход блока памяти уровней помех и номеров частот соединен с другим выходом блока реверсирования, а управляющие входы коммутатора и блока реверсирования соединены с дополнительными выходами блока управления, второй вход Которого соединен с одним из ьыходов кодопреобразователя. На фиг.1 представлена структурная электрическая схема предложенного устройства; на фиг.2 - вариант выполнения нелинейного многоканального приемника; на фиг.3 - вариант выполнения блока реверсирования; на. фиг.4 - вариант выполнения блока формирователей сигналов реверсирования и остановки; на фиг.5 - вариант выполнения блока выбора номера оптимальной частоты; на фиг.б - вариант выполнения блока управления. Устройство для оценки каналов и выбора оптимальных частот связи содержит нелинейный многоканальный приемник 1, входной блок 2 сложения,, блок 3 памяти уровней помех и номеров частот, блок 4 формирователей сигналов реверсирования и остановки, блок 5 реверсирования,блок 6 элементов сравнения, блок 7 выбора номера оптимальной частоты, блок 8 формирования регулируемого эталонного сигнала, состоящий из многоканального высокочастотного формирователя 9 эталонного сигнала, блока 10 аттенюаторов и генератора 11 низкочастотного сигнала, формирователь 12 Сигналов предварительной установки, состоящий из входного линейного усилителя 13, выходного аналого-цифрового преобразователя 14, коммутатоpa 15, линейного детектора 16, уси- лителя 1.7 постоянного напряжения и входного селектора 18 максимального уровня, блок 19 управления, ключ 20, кодопреобраэо,ватель 21, антенну 22, Нелинейный многоканальный приемник состоит (фиг.2) из блока 23 частотного синтезатора, генератора 24, блока 25 памяти частот, преселектора 26, блока 27 первого преобразования частоты, блока 28 второго преобразования частоты, блока 29 третьего преобразования частоты, первого коммутатора 30, первых канальных фильтров 31, вторых канальных фильтров 32,блоков 33 усилителей, первых преобразователей 34 частоты, вторых преобразователей 35 частоты, первых канальных усилителей 36, вторых канальных усилителей 37, второго коммутатора 38, блока 39 детектора и усилителя постоянного напряжения автоматической регулировки усилителя блока 40 усилителя-огран5;1чителя и опорного генератора 41. 1 |зоме того, блок реверсирования состоит из (фиг.З) элемента ИЛИ 42, ключа 43, буферного регистра 44,-коммутатора 45, реверсивного регистра 46 и кодопреобразователя 47, причем блок формирователей сигналов реверсирования и остановки состоит из (фиг.4) буферного усилителя 48, буферного усилителя-инвертора 49, двух триггеров 50,-51 и кодопреобразователя 52. Кро ме того, блок выбора номера оптималь ной частоты состоит (фиг.5) из двух мультиплексоров 53, 54, двух элементов И 55, 56, двух инверторов 57, 58 коммутатора 59, двух основных регист ров 60, 61, двух входных регистров 62, 63, пяти элементов ИЛИ 64-68, триггера 69 и блока индикации 70, причем блок .управления состоит из трех распределителей импульсов 71-73 трех элементов И 74-76, семи элементов ИЛИ 77-83, трех триггеров 84-8,6, двух элементов задержки 87, 88, блока 89 формирования импульсных сигналов, двух формирователей 90, 91 импульсных сигналов, ключа 92, первого переключателя 93, формирователя94 .сигнала исходной установки, вторрго переключателя 95 генератора импульсов 96. . Устройство работает следдующим образом. По командам, подаваемым из блока 19, осуществляется перестройка с 1астоты на частоты соответственно ге нерации и приема. После известного времени, определяемого переходными лроцессами по команде, подаваемой с блока 19 в блок 5, записывается сигнал с выходного аналого-цифрового преобразователя 14, после чего пО ко манде с блока 19 в блок 10 подается преобразованный кодопреобразователем 21 сигнал с реверсивного регистра блока 5 и одновременно открывается ключ 20. Измененный по величине высокочастотный групповой сигнал подается в- блок 2 , .где он складывается с пространственными помехами с антенны 22. Поданные по первому входу в нелинейный многоканальный приемник 1 эталонный сигнал и помехи усиливаются в нем и преобразуются в спектр низких частот, а затем подаются в блок 6, где для каждого из К каналов узкополосным и рефлекторным фильтрами соответственно с полосами пропускания и рефяекции намного меньшими, чем полоса пропускания соответствующего канального фильтра, производится соответственно выделение эталонного сигнала от помех и помех от эталонного сигнала. Сигнал и помехи раздельно усиливаются усилителями . Сигнал сравнения той или иной полярности или нуль снимается с нульоргана и подается в соответствующий ;блок 4, где соответственно полярности поступившего сигнала или отсутствия его формируют соответствующие импульсные сигналы реверсирования и остановки с помощью, например, триггеров .Чмидта, причем сигнал остановки Стоп, 0 формируется тогда, когда сигнал сравнения по алгебраической величине не превмаает некоторых, заранее известных соответствующих по знаку ПОРОГОВЫ.Х уровней. Сформированные сигналы преобразуются в кодопреобразователе 21 в обобщенные сигналы реверсирования и остановки и подаются в блок 5, а сигнал остановки О , кроме того, подается в-блок 19. Сигналами реверсирования в блоке 5 управляется, через соответствующий коммутатор подача тактовых импульсов на соответствующие входы реверсирования счетного регистра, а сигналом остановки с помощью соответствующего ключа прекращается подача импульсов на входы того же регистра. Сигналы регистра перекодируются и подаются на соответствующие ключи блока 10. Поскольку сигналы реверсирования регистра блока 5 в целом представляют параллельными цифровой сигнал, который по своей значимости соответствует эффективному уровню помех, то при появлении сигнала остановки это.т сигнал через буферный регистр считывается с реверсивного регистра и подается на запись в блок 3, куда одновременно с блока 19 по второму входу подается команда на запись в соответствующую частоте связи ячейку памяти. Кроме того, сигнал остановки, поданный в блок 19, разрешает после его окончания, подачу команды на перестройку на следующую частоту. Описанная операция повторяется наW частотах. После этого по командам, подаваемым одновременно в блоки.3 и 7 по вторы входам, с.блока 3 считывается, а в блок 7 записывается сигнал уровня помехи. Одновременно с этим в блоке 7 производится запись сигнала номера частоты, который по второму входу подается из блока 19. После первой записи в блок 7 подается команда переноса, по которой сигналы уровня помехи и номера частоты считываются из входных регистров и записываются в основные регистры, пос ле чего во входные регистры записываются сигналы уровня помехи и номера второй частоты приема и из бло ка 19 подаются команды поразрядногч сравнения. Выявленный в результате сравнения сигнал уровня помехи с меньшей значимостью и соответствующий ему сигнал номера частоты записываются в соответствующие основные регистры или остаются в них, если они были в них до операции сравнения. -Если в результате сравнения оказывается, что сигналы уровней по мех по своей значимости равны, то преимущество отдается по принципу сигналу в основном регистре. После первого сравнения в блок 7 вводятся сигналы уровня помехи и номера трет ей частоты, а зат.ем производится сравнение сигналов уровней помех вновь введенного и оставшегося в основном регистре. Такое попарное сравнение производится для сигналов уровней помех всех частотных каналов. Выявленный сигнал минимальногб уровня помехи и соответствующий е2чу сигнал номера частоты по команде с блока 19 считываются и записываются в соответствующие регистры хранения, где они хранят.ся до окончания последующего цикла сравнения и .используются для визуальной индикации. После этого начинается цикл оценки уровней помех и выбор номера описанной частоты. В качестве гетеродинных сигналов используются сигналы блока 23 фиг.2) и засинхронизированного через блок 23 генератора 24. Блок 23 работает на базе колебаний высокостабильного опорного генератора 41. Преселектор 26 перестраивается -по сигналам с блока 25 памяти частот, который управляется по командам с блока 19. Для перестройки блока 23. используются сигналы частот приема ..с блока 25. Первый и второй коммутаторы 30 и 38 управляются с блока 25, который одновременно является блоком памяти вида модуляции принимаемых сигналов. В зависимости от вида модуляции сигналов сигнал с первого коммутатора ОО подается или в блок 40 или в фильтры 32. Сигнал с выхода первого коммутатора 30 подается в формирователь 12, где он ограничивается, выделяется частотным дискриминатором и подается на канальные фильтры 31, где производится фильтрация канальных сигналов, которые преобразуются по частоте соответствующими преобразователями 34, на входал которых с блока 23 подаются сигналы гетеродинирования соответствующих частот. Далее сигналы поканально усиливаются усилителями 36 и через второй коммутатор 38 подаются на вход входного блока 2. в фильтрах 32 производится фильтрация канальных сигналов однополосной модуляции. Эти сигналы усиливаются соответствующими усилителями промежуточной частоты блоков 3.3 и преобразовываются по частоте в соответствующих преобразователях 35, на вторыевходы которых подаются соответствующие сигналы гетеродинирования с блока 23. каждый блок 33 канал ых усилителей охвачен АРУ, регулирующее напряжение которой формируется в блоке 39 и подается в соответствующий блок 33 и на соответствующий вход формирователя 12. Во вторых преобразователях 35 частоты канальные сигналы преобразуются по частоте и далее усиливаются. На первом входе блока 4 (фид.4) появляются раздельно во времени сигналы двух полярностей. Соответственно полярности .сигналы усиливаются или буферным усилителем 48 или буферным усилителем-инвертором 49. В зависимости от этого срабатывает дали триггер 50 или триггер 51. Если уровни сигналов недостаточны для срабатывания триггеров или отсутствуют, то оба триггера находятся в ИСХОДНОМ состоянии. Таким образом, сигналы на входах кодопреобразователя 52 или равны оба логическому нулю или на одном из них присутствует логическая единица. В зависимости от наличия этих сигналов кодопреобразователь формирует сигнал реверса Больше ( ), Меньше ( ) и сигнал остановки Стоп (, которые подаются в кодопреобразователь 21, сигналы с которого подаются на коммутатор 45 (фиг.3), Коммутатор 45 в зависимости от сигналов реверса подает тактовые импульсй с ключа 43 на первый или второй вход реверсивного регистра 46, соответственно увеличивая накопление в нем элементарных сигналов или уменьшая. Сигналы реверсивного регистра 46 подаются на кодопреобразователь 47, где они перекодируются и подаются в блок 10. При появлении сигнала О, который Через элемент ИЛИ 42 подается на первый вход ключа 43, на второй вход буферного регистра 44 и в блок 3, ключ 43 закрывается и прекращается подача

через третий вход тактовых импульсов на коммутатор 45 и, следовательно в реверсивный регистр 46. Сигнал остаiHOBKH для буферного регистра 44 является сигналом считывания, а Для блока 3 - сигналом записи, В результате информация с буферного регистра 44 записывается в соответствующую ячейку памяти блока 3. Кроме того, клич 43 на некоторое враки закрывается по команде с блока 19 при перестройке приемника на другую частоту на время переходных процессов в нем, а также при подаче в реверсивный регистр 46 сигнала записи по третьему входу при установке этого регистра в предварительное состояние, которое определяется вводимым по третьему входу в регистр сигналом.

В регистрах 61, 62 (фиг.5) хранятся сигналы уровней помех двух различных частотных кангшов, а в регистрах 63, 60 г сигналы номеров соответствующих частот. Сравнение сигналов производится путем поразрядной подачи сигналов с регистров 61 и 62 с помощью мультиплексоров 53 и 54 на элементы И 55, 56, Если соответствующий разряд основного регистра 61 меньше по своей значимости разряда с входного регистра 62, т,е, является нулем, то он инвертируется в инверторе 58 в единицу и на элемент И 55 подаются две единицы, в результате на его выходе появляется сигнал, который через элемент ИЛИ 65 поступает в блок управления 19, который прекращает подачу сигналов управления на сравнение разрядов. Если разряд с входного рёгистра62 меньше, . чем с основного регистра 61, то рабртают входной регистр 62 и элемент И 56, Коммутатор 59/ управляемый блоком управления, передает сигналы на триггер 51. Если при сравнении сигнал входного регистра 62 окажется, меньшим, чем с основного регистра 61, то сигнал с элемента И 56 через коммутатор 59 поступает на первый вход триггера 69 и опрокиды-вает его, в.свою очередь, через элемент ИЛИ 66 подается сигнал записи по вторым входам в основные регистры 60 и 61, и тот же сигнал, как сигнал считывания, подается через элемент ИЛИ 64 по третьему входу в входной регистр 62 и по третьему вхо ду в входной регистр 63,

Исходное состояние триггера 84. (фиг.6) позволяет сформировать выходной импульс при подаче на- второй ег вход тактового импульса. Этот сигнал через элемент ИЛИ 78 и формирователь 90 по второму входу опрокидывает рсриггер 84, в результате чего прекрадается подача импульсов через элемен|и 74. Кроме того, сигнал с формирова

,теля 90 через элемент задержки 87, например ждущий мультивибратор,- и через элемент ИЛИ 83 подается в блок 5, прекращая подачу там тактовых им-пульсов через ключ на время переходных процессов приперестройке приемника на новую частоту приема. Кроме того, сигнал элемента задержки 87 задерживается элементом задержки 88 .и через элемент ИЛИ 83 воспрещает подачу тактовых импувьсов в реверсивный регистр блока 5, а также одновременно служит сигналом записи при установке этого реверсивного регистра в предварительное состояние сигналами с формирователя 12. В исходное состояние триггер 84 возвращается сигналом Стоп с кодопреобразователя 21. Сигнал со второго входа распределителя импульсов 71 появляется после оценки уровня помех на всех и частотах и подается на первый вход элемента и 75, который при соответствующем сигнале с триггера

85и при подаче тактового сигнала формирует импульс, КОТОЕЙЛЙ по первому входу, подается в распределитель импульсов 72, который совместло с 1соответствующими формирователями блока 89 - собственно элементами И формирует сигналы записи-считывания переноса-1, пёреноса-2 (,сигнал считывания с основных регистров и згаписи в блок индикации в блоке 7 К Кроме того, унитарный сигнал по проводам первого выхода блока 89 используется как сигнал номера частоты приема приемника для подачи в блок 7. Задним фронтом сигнала записи опрокидывается триггер 85 и тем сам предотвращает сигналом своего состояния формирование импульсов окончания сравнения с блока 7 или, при.равенстве по значимости сравниваемых сигналов в блоке 7, импульсов с распределителя импульсов 73. , Задним фронтом сигнала записи опрокидывается триггер 86, который своим сигналом разрешает формированиеэлементом И 76 от тактовых импульсов сигналов на первый вход распределителя импульсов 73, который предназначен для подачи сигналов на ;мулЪтиплекс6ры блока 7. Если в бло1ке 7 при сравнении по значимости

1 сигналы окажутся равными, то на вы:ходе распределителя импульсов 73

появляется , который через .

элемент ИЛИ 82 опрокидалвает триггер

86в исходное состояние, что предотвращает форьшрование импульсов элементом И 76. Кроме того, этот. триггер возвращается в исходное состояние импульсом окончания сравнения с блока 7, который подается через элемент ИЛИ 82. Сигналы с вы1ХОДОВ распределителя импульсов 72 через элемент ИЛИ 80 запирают ключ

92, предотвращая тем самым подачу случайного сигнала Стоп на триггер 84 во время npoiiecca выбора номера оптимальной частоты. Сигналом jC формирователя 94 соответствующие .бло1 и схемы устанавливаются в исхоЬнов состояние после ,включе ния.

Технико-экономическая эффективность предложенного устройства состоит в том, что благодаря повыиению поочередного обслуживания нескольких адаптивных приемников, каждый из которых имеет свою группу частот приема, из которых выделяются оптимальные,достигается .экономия аппаратурных средств.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выделения оптимальных частот связи | 1981 |

|

SU1021000A1 |

| Устройство для контроля телеметрической информации | 1980 |

|

SU920814A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2001 |

|

RU2207729C2 |

| ИЗМЕРИТЕЛЬ УРОВНЯ | 1992 |

|

RU2029248C1 |

| РАДИОЛОКАЦИОННОЕ ПРИЕМНОЕ УСТРОЙСТВО | 1984 |

|

SU1841013A1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

| Устройство автоматического поиска каналов радиосвязи | 1981 |

|

SU995341A1 |

| УСТРОЙСТВО ДЛЯ СОЗДАНИЯ ПОМЕХ РАДИОЛОКАЦИОННЫМ СТАНЦИЯМ | 1994 |

|

RU2054807C1 |

| УСТРОЙСТВО ДИСТАНЦИОННОЙ СИГНАЛИЗАЦИИ | 1992 |

|

RU2032229C1 |

| Приемник сигналов с трехкратной фазовой манипуляцией | 1989 |

|

SU1628219A1 |

УСТРОЙСТВО-ДЛЯ ОЦЕНКИКАНАЛОВ И ВЫБОРА ОПТИМАЛЬНЫХ ЧАСТОТ СВЯЗИ, содержащее последовательно соединенные входной блок сложения, нелинейный многоканальный приемник,блок элементов сравнения, последовательно соединенные блок формирования регулируемого эталонного сигнала, состоящий из последовательно соединенных генератора низкочастотного сигнала, многоканального высокочастотного формирователя эталонного сигнала и блока аттенюаторов, и ключ, причем первый дополнительный выход нелинейного многоканального приемника соединен с другим входом -многоканального высокочастотного формирователя эталонного сигнала, другой вход входного блока сложения соединен с выходом ключа, и блок управления, соответствуйщие выходы которого, подключены к управляющим входам ключа, нелинейного многоканального приемника, блока элементов сравнения, |бл6ка памяти уровней помех и номеров частот, блока выбора номера оптимальной частоты, сигнальный вход которо,го соединен с выходом блока памяти уровней помех и номеров частот, а выход подключен к первому Ъходу блока управления, о т л и ч а ю щ е е с. я тем, что, с целью сокращения времени выбора, в него введены включенные между выходами блока элементов сравнения и другим входом блока аттенюаторов последовательно соединенные блок формирователей сигналов реверсирования и остановки, кодопреобразователь и блок реверсирования, а также включенный между вторым дополнительным выходом нелинейного многоканального приемника и другим входом блока реверсирования формирователь сигналов предварительной установки, состоящий из последователь- но соединенных входного линейного усилителя, линейного дехектор,а,усилителя постоянного напряжения , выход которого подключен к другому входу входного линейного усилителя, и последовательно соединенных входного селектора максимального уровня, коммутатора и выходного аналого-цифрового преобразорателя, причем выход усилителя постоянного напряжения подключен к другому входу коммутатоIS9 ра, сигнальный вход блока памяти уровней помех и- номеров частот сое 4 динен с другим выходом блока реверсирования, а управляющие входы коммутатора и блока реверсирования соединены с дополнительныг1И выходами блока управления, второй вход которого соединен с одним из выходов ;код6преобразо1ватёля.

(.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР 637035, кл.Н 04 В 1/10, 1977 (прототип) | |||

Авторы

Даты

1983-04-15—Публикация

1981-04-27—Подача