Изобретение относится к технике связи и может быть использовано при многоканальной передаче дискретных сообщений.

Известна многоканальная цифровая система передачи и приема информации (см. а. с. 2013012 Н 04 J 3/24, бюл. 9 от 15.05.94), содержащая первый и второй генератор тональных импульсов, первый и второй генераторы псевдослучайных последовательностей, первый и второй синтезаторы частот, первый и второй блоки переключения, передающий блок, приемный блок, распределитель импульсов, формирователь цикловой синхронизации, сумматор, блок цифровой синхронизации, распределитель группового сигнала, индивидуальные передающие блоки, индивидуальные приемные блоки, кодер, декодер, блок относительной фазовой манипуляции, передатчик, приемник, генератор несущей частоты, генератор опорной частоты, блок управления, усилитель, блок слежения за задержкой, блок определения скорости. Она обеспечивает расширение диапазона скоростей передачи группового сигнала, но не позволяет работать с разноскоростными источниками дискретных сообщений.

Известна и многоканальная цифровая система связи (см. а.с. 1453607 Н 04 J 3/24, бюл. 3 от 23.01.89), содержащая передающий групповой блок, приемный групповой блок, передающие и приемные индивидуальные блоки, первый и второй блоки переключения, блок управления, приемник команд, первый и второй генераторы тактовой частоты. Данная система имеет возможность функционировать с изменением скорости считывания передаваемых и принимаемых сигналов, но не обеспечивает распределения пропускной способности между источниками дискретных сообщений.

Известна также система многоканальной связи (см. а.с. 1062872 Н 04 J 3/00, бюл. 47 от 23.12.83), содержащая в передающей части - блоки асинхронного ввода, буферные запоминающие блоки, реверсивные счетчики, блок дисциплин обслуживания, блок управления считыванием, формирователь сигналов управления, генератор импульсов, блок объединения, а в приемной - распределитель, дешифратор сигналов управления, блок управления записью, генератор импульсов, буферные запоминающие блоки и блоки вывода. Известная система обеспечивает повышение пропускной способности за счет учета статистики активности абонентов и распределения пропускной способности между активными источниками информации. Однако передача сообщений в такой системе осуществляется с задержками времени, необходимыми для сбора статистики и обработки управляющих сигналов.

Наиболее близким, как по количеству сходных признаков, так и по достигаемому техническому результату к заявленному устройству является многоканальная система передачи и приема дискретной информации с использованием аппаратуры "Думка" (см. Малиновский С.Т. Сети и системы передачи дискретной информации и АСУ. - М.: Связь, 1979, с. 121... 125). Она содержит на передающей стороне - N источников дискретных сигналов, где N≥2, мультиплексор, блок защиты от ошибок, блок преобразования сигналов. При этом выход мультиплексора подключен к входу блока защиты от ошибок. Выход блока защиты от ошибок подключен к входу блока преобразования сигналов, выход которого в свою очередь является выходом передающей части системы. На приемной стороне она содержит блок преобразования сигналов, блок защиты от ошибок, мультиплексор и N приемников дискретной информации. При этом вход блока преобразования сигналов является входом приемной части системы. Выход блока преобразования сигналов подключен к входу блока защиты от ошибок, а выход блока защиты от ошибок подключен к входу мультиплексора. Данная система обеспечивает одновременную работу нескольких источников передачи дискретных сообщений с различными скоростями.

Общим недостатком аналогов и прототипа является невозможность оперативного распределения пропускной способности группового тракта при изменении числа работающих источников дискретных сообщений и их скорости передачи.

Целью изобретения является разработка системы, обеспечивающей максимальное использование пропускной способности группового тракта при оперативном управлении скоростью передачи источников дискретных сообщений.

Поставленная цель достигается тем, что в известное устройство, содержащее на передающей стороне - N источников дискретных сигналов, где N≥2, мультиплексор, выход которого подключен к входу блока защиты от ошибок, выход которого подключен к входу блока преобразования сигналов, выход которого является выходом передающей части системы и на приемной стороне - блок преобразования сигналов, вход которого является входом приемной части системы, а выход подключен к входу блока защиты от ошибок, выход которого подключен к входу мультиплексора и N приемников дискретной информации, дополнительно введены на передающей стороне - N блоков управления скоростью передачи, блок управления, передающий коммутатор, а на приемной стороне - N блоков управления скоростью приема, блок управления, приемный коммутатор.

На передающей стороне выход j-го источника дискретных сообщений, где j= 1, 2,...N, подключен к информационному входу j-го блока управления скоростью передачи. L выходов j-го блока управления скоростью передачи, где L≥N, подключены к соответствующим L информационным входам j-ой группы входов передающего коммутатора, а М выходов передающего коммутатора, где M≥L≥N, подключены к соответствующим М входам мультиплексора, j-ый управляющий выход блока управления подключен к управляющему входу j-го блока управления скоростью передачи, a Q коммутирующих выходов блока управления подключены к соответствующим Q управляющим входам передающего коммутатора. Служебный вход передающего коммутатора подключен к служебному выходу блока управления.

На приемной стороне вход j-го приемника дискретных сообщений подключен к выходу j-го блока управления скоростью приема. М выходов мультиплексора подключены к соответствующим М входам приемного коммутатора. L информационных выходов j-ой группы выходов приемного коммутатора подключены к соответствующим L информационным входам j-блока управления скоростью приема, j-ый управляющий выход блока управления подключен к управляющему входу j-го блока управления скоростью приема, а Q коммутирующих выходов блока управления подключены к соответствующим Q управляющим входам приемного коммутатора. Служебный выход приемного коммутатора подключен к служебному входу блока управления.

Каждый блок управления скоростью передачи состоит из формирователя тактовых импульсов, первой, второй и третьей линии задержки, регистра сдвига и параллельного регистра. Третий выход формирователя тактовых импульсов подключен к входам второй и третьей линии задержки. Второй выход формирователя тактовых импульсов подключен к входу первой линии задержки, а первый выход формирователя тактовых импульсов подключен к второму входу регистра сдвига. Выход первой линии задержки подключен к третьему входу регистра сдвига. Выход второй линии задержки подключен к четвертому входу регистра сдвига, а выход третьей линии задержки подключен к считывающему входу параллельного регистра. L выходов регистра сдвига подключены к соответствующим L информационным входам параллельного регистра, L выходов которого являются L выходами блока управления скоростью передачи. Первый вход регистра сдвига подключен к первому входу формирователя тактовых импульсов и является информационным входом блока управления скоростью передачи. Второй вход формирователя тактовых импульсов является управляющим входом блока управления скоростью передачи.

Каждый блок управления скоростью приема состоит из формирователя импульсов синхронизации, распределителя импульсов, дешифратора. L считывающих входов дешифратора подключены к соответствующим L выходам распределителя импульсов. Первый выход формирователя импульсов синхронизации подключен к входу гашения дешифратора и к входу распределителя импульсов, а второй выход - к установочному входу распределителя импульсов. L информационных входов дешифратора являются соответствующими L информационными входами блока управления скоростью приема. Вход формирователя импульсов синхронизации является управляющим входом блока управления скоростью приема, а выход дешифратора является выходом блока управления скоростью приема.

Благодаря новой совокупности существенных признаков за счет введения блоков управления скоростью передачи и приема, блоков управления, передающего и приемного коммутаторов обеспечивается максимальное использование пропускной способности группового тракта при оперативном управлении скоростью передачи источников дискретных сообщений.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественными всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного изобретения условию патентоспособности "новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

Заявляемое устройство поясняется чертежами, на которых:

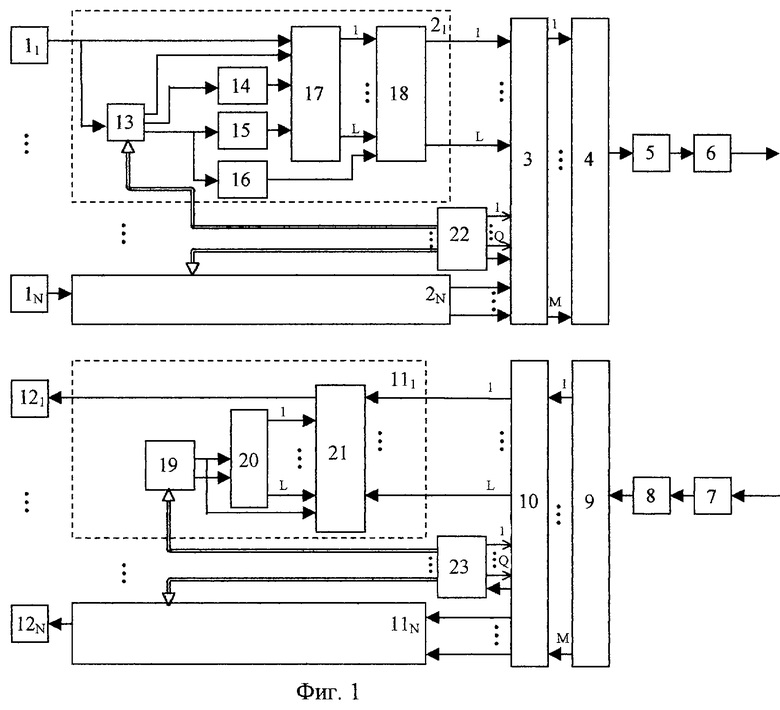

на фиг.1 показана функциональная схема многоканальной системы передачи и приема дискретной информации;

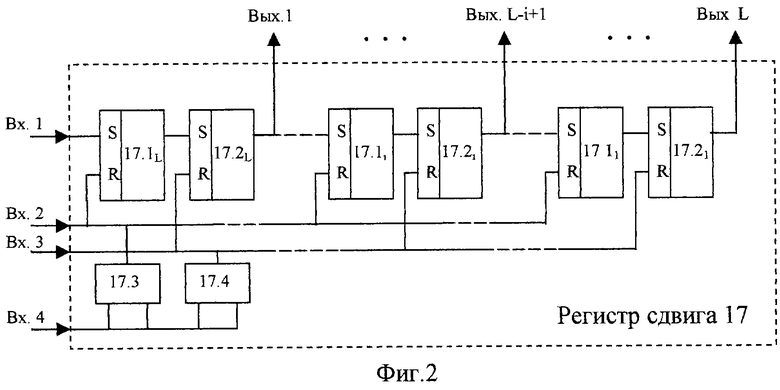

на фиг.2 - схема регистра сдвига 17;

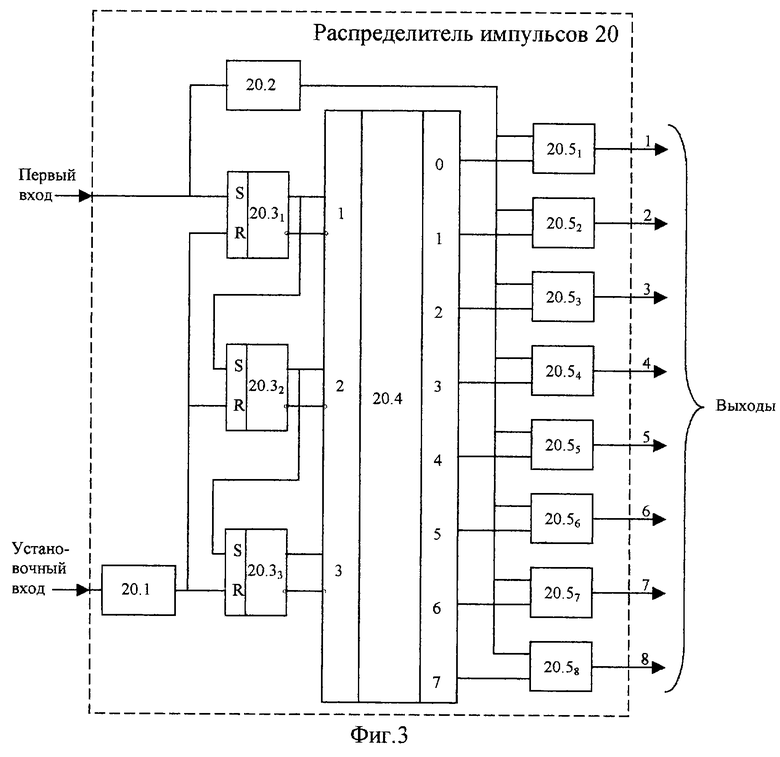

на фиг.3 - схема распределителя 20;

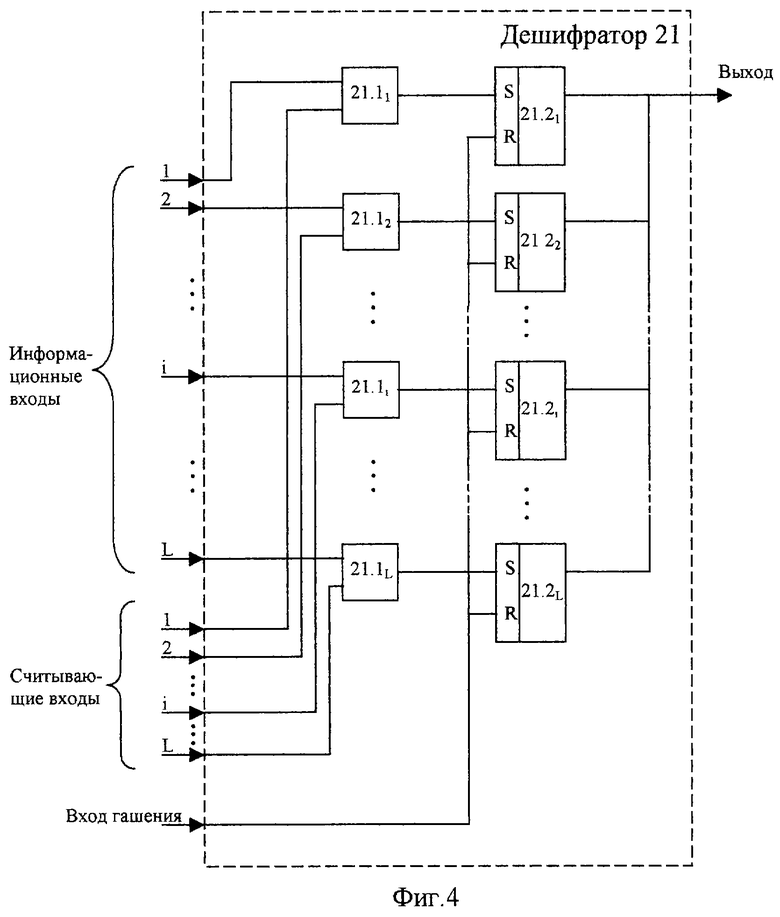

на фиг.4 - схема дешифратора 21;

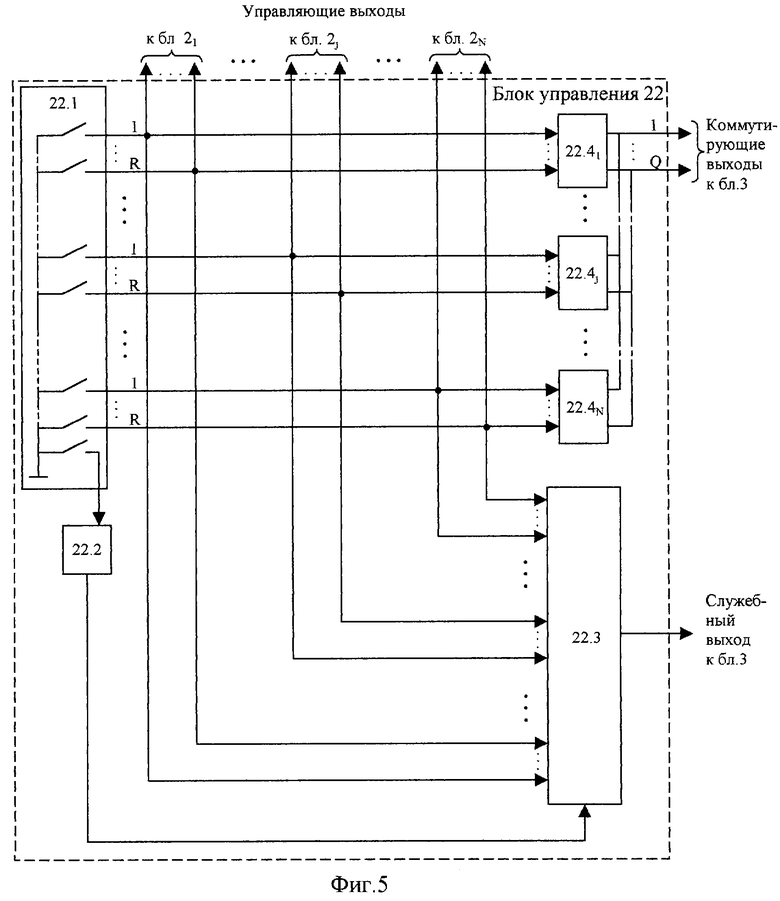

на фиг.5 - схема блока управления 22;

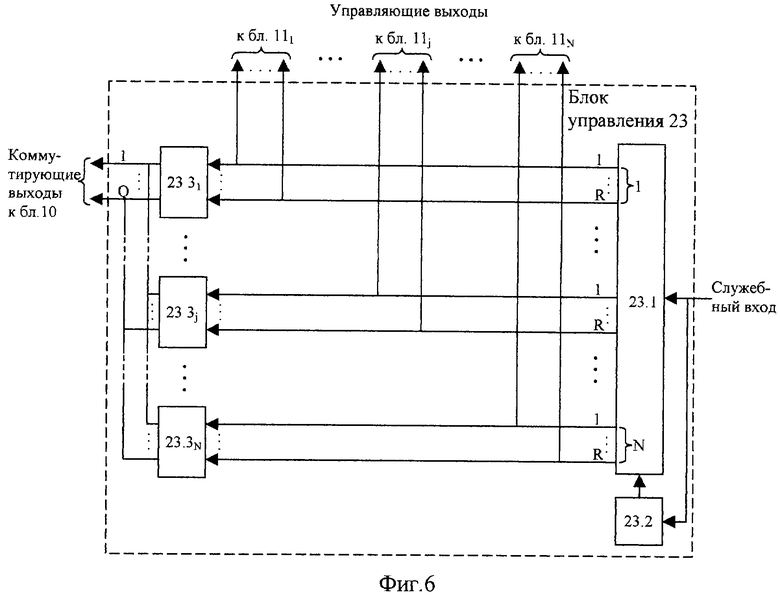

на фиг.6 - схема блока управления 23;

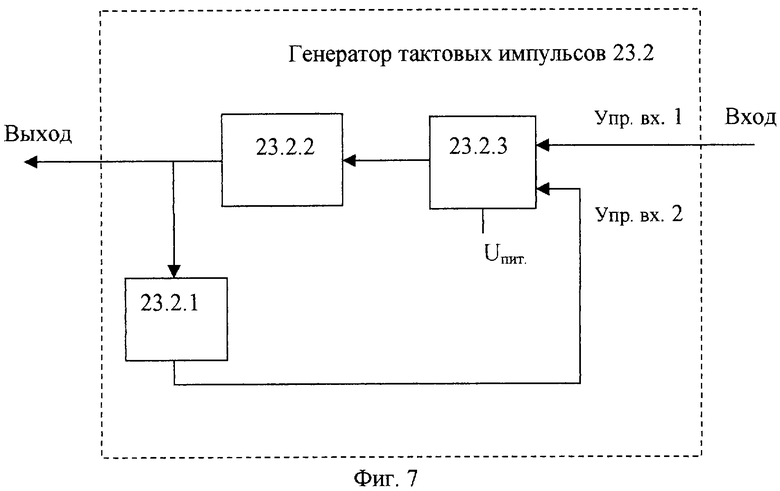

на фиг.7 - схема генератора тактовых импульсов 23.2;

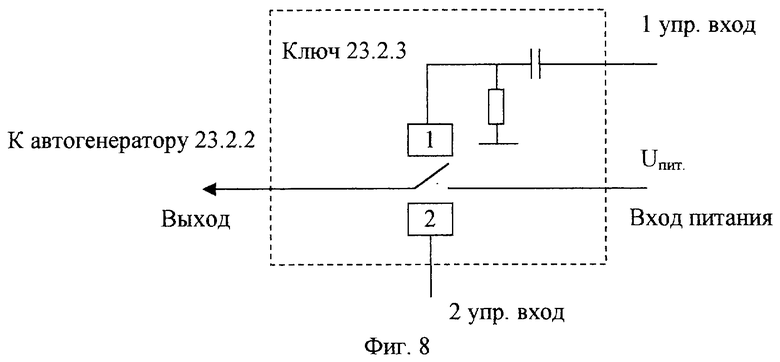

на фиг.8 - схема ключа;

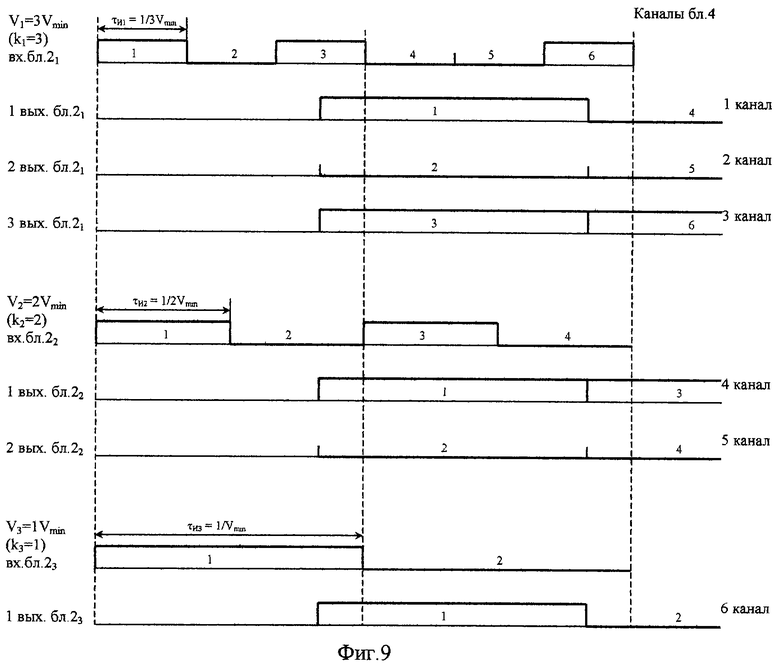

на фиг.9 - диаграммы, поясняющие принцип обработки сигналов при передаче информации от трех источников дискретных сообщений;

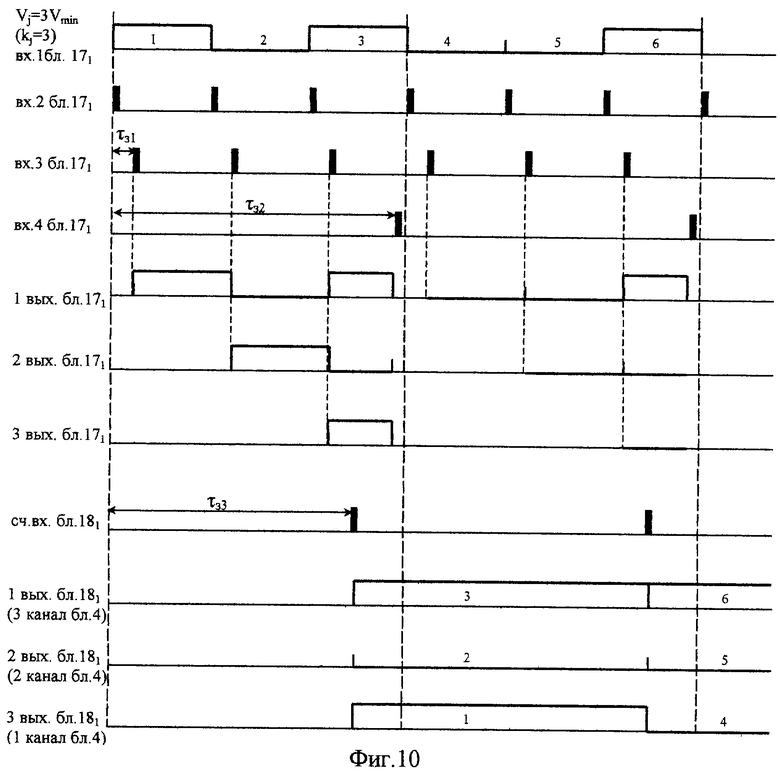

на фиг.10 - диаграммы, поясняющие работу регистра сдвига 17 и параллельного регистра 18;

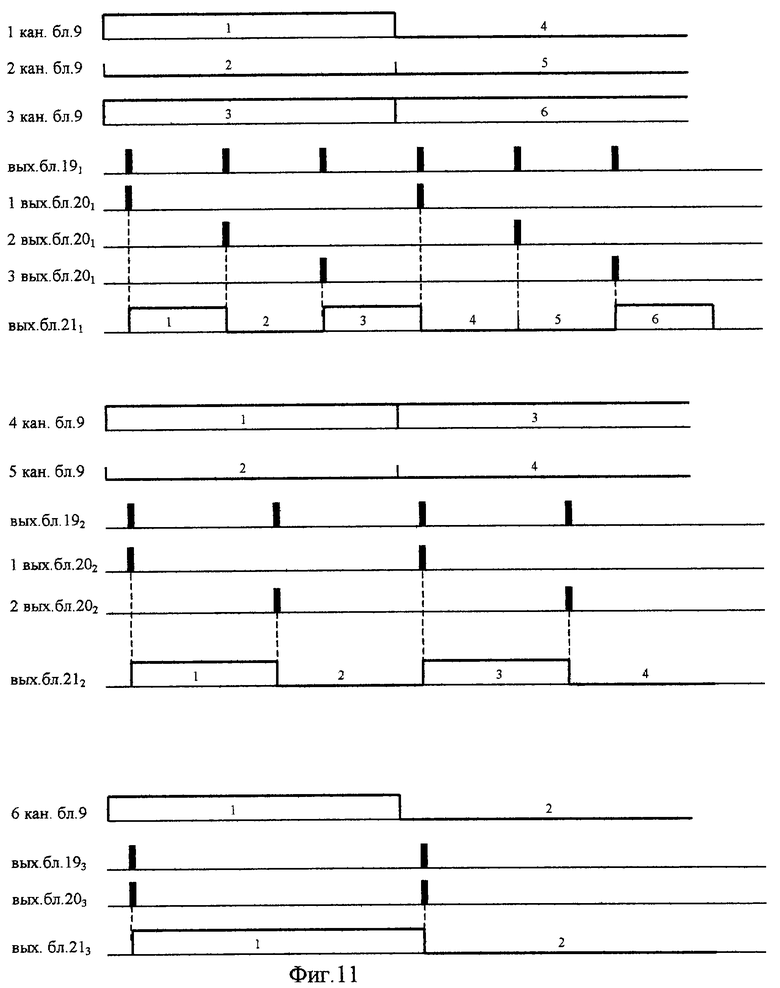

на фиг.11 - диаграммы, поясняющие принцип обработки сигналов при приеме информации тремя приемниками дискретной информации.

Заявляемое устройство, показанное на фиг.1, на передающей стороне состоит из: N источников дискретных сигналов 11...1N, N блоков управления скоростью передачи 21. ..2N, передающего коммутатора 3, мультиплексора 4, блока защиты от ошибок 5, блока преобразования сигналов 6 и блока управления 22, а на приемной стороне - из N приемников дискретной информации 121...12N, N блоков управления скоростью приема 111...11N, приемного коммутатора 10, мультиплексора 9, блока защиты от ошибок 8, блока преобразования сигналов 7 и блока управления 23.

На передающей стороне выход j-го источника дискретных сообщений 1j, где j= 1, 2, . ..N подключен к информационному входу j-го блока управления скоростью передачи 2j. L выходов j-го блока управления скоростью передачи 2j, где L≥N подключены к соответствующим L информационным входам j-ой группы входов передающего коммутатора 3, а М выходов передающего коммутатора 3, где M≥L≥N, подключены к соответствующим М входам мультиплексора 4. Выход мультиплексора 4 подключен к входу блока защиты от ошибок 5. Выход блока защиты от ошибок 5 подключен к входу блока преобразования сигналов 6, выход которого является выходом передающей части системы, j-ый управляющий выход блока управления 22 подключен к управляющему входу j-го блока управления скоростью передачи 2j, a Q коммутирующих выходов блока управления 22 подключены к соответствующим Q управляющим входам передающего коммутатора 3. Служебный вход передающего коммутатора 3 подключен к служебному выходу блока управления 22.

На приемной стороне выход блока преобразования сигналов 7, вход которого является входом приемной части системы, подключен к входу блока защиты от ошибок 8. Выход блока защиты от ошибок 8 подключен к входу мультиплексора 9. М выходов мультиплексора 9 подключены к соответствующим М входам приемного коммутатора 10. L информационных выходов j-ой группы выходов приемного коммутатора 10 подключены к соответствующим L информационным входам j-блока управления скоростью приема 11j. Вход j-го приемника дискретных сообщений 12j подключен к выходу j-го блока управления скоростью приема 11j. j-ый управляющий выход блока управления 23 подключен к управляющему входу j-го блока управления скоростью приема 11j, a Q коммутирующих выходов блока управления 23 подключены к соответствующим Q управляющим входам приемного коммутатора 10. Служебный выход приемного коммутатора 10 подключен к служебному входу блока управления 23.

Каждый блок управления скоростью передачи 21...2N состоит из формирователя тактовых импульсов 13, первой 14, второй 15 и третьей 16 линий задержки, регистра сдвига 17 и параллельного регистра 18. Третий выход формирователя тактовых импульсов 13 подключен к входам второй 15 и третьей 16 линий задержки. Второй выход формирователя тактовых импульсов 13 подключен к входу первой линии задержки 14, а первый выход формирователя тактовых импульсов 13 подключен ко второму входу регистра сдвига 17. Выход первой линии задержки 14 подключен к третьему входу регистра сдвига 17. Выход второй линии задержки 15 подключен к четвертому входу регистра сдвига 17, а выход третьей линии задержки 16 подключен к считывающему входу параллельного регистра 18. L выходов регистра сдвига 17 подключены к соответствующим L информационным входам параллельного регистра 18, L выходов которого являются L выходами блока управления скоростью передачи 2. Первый вход регистра сдвига 17 подключен к первому входу формирователя тактовых импульсов 13 и является информационным входом блока управления скоростью передачи 2. Второй вход формирователя тактовых импульсов 13 является управляющим входом блока управления скоростью передачи 2.

Каждый блок управления скоростью приема 111...11N состоит из формирователя импульсов синхронизации 19, распределителя импульсов 20, дешифратора 21. L считывающих входов дешифратора 21 подключены к соответствующим L выходам распределителя импульсов 20. Первый выход формирователя импульсов синхронизации 19 подключен к входу гашения дешифратора 21 и к входу распределителя импульсов 20, а второй выход формирователя импульсов синхронизации 19 подключен к установочному входу распределителя импульсов 20. L информационных входов дешифратора 21 являются соответствующими L информационными входами блока управления скоростью приема 11. Вход формирователя импульсов синхронизации 19 является управляющим входом блока управления скоростью приема 11, а выход дешифратора 21 является выходом блока управления скоростью приема 11.

Передающий коммутатор 3 предназначен для подключения требуемых выходов L блоков управления скоростью передачи 21...2L к М входам (каналам) мультиплексора 4 под действием управляющих сигналов, а также подключения служебного выхода блока управления 22 к одному из каналов мультиплексора 4. Приемный коммутатор 10 предназначен для подключения М выходов (каналов) мультиплексора 9 к требуемым входам L блоков управления скоростью приема 111...11L под действием управляющих сигналов, а также подключения канала мультиплексора 9, по которому передается служебная информация, к служебному входу блока управления 23. Как передающий коммутатор 3, так и приемный коммутатор 10 могут быть реализованы на интегральных схемах матричных коммутаторов, известных и описанных - Вениаминов В.Н. и др. Микросхемы и их применение. Справочное пособие. - М: Радио и связь, 1983, с. 109... 110. Например, передающий коммутатор 3 может быть реализован на ИС К1509КП1, а приемный коммутатор 10 - на ИС К561КП1. При этом Q коммутирующими выходами коммутаторов являются их управляющие входы, т. е. Q - число разрядов для управления передающим коммутатором 3 (например, для ИС К1509КП1 их 12).

Формирователь тактовых импульсов 13 предназначен для формирования тактовых импульсов на третьем выходе с частотой следования соответствующей минимальной скорости передачи информационных сообщений Vmin, а на первом и втором выходах - тактовых импульсов с регулируемой частотой следования, которая определяется в соответствии со значением коэффициента скорости kj, устанавливаемом через второй вход. Формирователь тактовых импульсов 13 можно построить на основе многочастотного генератора импульсов, описанного в известной литературе (см. Вениаминов В.Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1983, с. 136... 138, рис.4.29). При этом выход 6 элемента D9 является первым и вторым выходом формирователя тактовых импульсов, а выход 11 одного из делителей D2...D8 - третьим выходом формирователя тактовых импульсов. Управляющие сигналы v1, v2, v3 (S3,, *104,,, S2, , *102,,, S1, ,*101,,) поступают на второй вход формирователя тактовых импульсов 13 из блока управления 22 по шине, содержащей R=3 провода, а на первый вход формирователя тактовых импульсов поступает команда на запуск задающего генератора на К155ЛА3 (т.е. подается питание на схему через ключ, аналогичный изображенному на фиг.8).

Первая линия задержки 14 предназначена для задержки тактовых импульсов на время τз1, вторая линия задержки 15 - на время τз2, а третья линия задержки 16 - на время τз3. Эти элементы известны и могут быть реализованы на элементах временной задержки К523БР1 или цифровых линиях задержки КР186ИР5, описанных - Интегральные микросхемы: Справочник. Под ред. Б.В. Тарабрина. - М.: Радио и связь, 1984, с.288, с. 177.

Регистр сдвига 17 предназначен для распределения информационной последовательности импульсов, поступающей на первый вход, по L выходам с необходимыми сдвигами, определяемыми тактовыми импульсами, поступающими на его второй, третий и четвертый входы. Регистр сдвига 17 может быть построен на основе двухтактного сдвигающего регистра на триггерах, описанного в известной литературе (см. Гусев В.В. и др. Основы импульсной и цифровой техники. Учебное пособие для вузов. - М.: Сов. радио, 1975, с. 383...384, рис. 14.25). Схема регистра сдвига 17 показана на фиг.2. Регистр сдвига 17 состоит из элементов "И" 17.3 и 17.4 и RS-триггеров 17.11... 17.1L и 17.21... 17.2L. Общее число последовательно соединенных через прямые выходы и S-входы триггеров 17.1 и 17.2 равно 2L. При этом выход i-го триггера 17.1i подключен к S входу i-го триггера 17.2i, a S вход i-го триггера 17.1i подключен к выходу i+1-го триггера 17.2i, где i=1, 2...L. Выход i-го триггера 17.2i является L-i+1-ым выходом регистра сдвига 17. S-вход L-го триггера 17.1L является первым входом регистра сдвига 17, а выход первого триггера 17.21 является L-ым выходом регистра сдвига 17. R-входы триггеров 17.11... 17.1L и 17.21. .. 17.2L объединены и являются соответственно вторым и третьим входом регистра сдвига 17. Четвертый вход регистра сдвига 17 подключен через элементы "И" 17.3 и 17.4 соответственно к второму и третьему входам регистра сдвига 17. RS-триггеры 17.1, 17.2 известны и описаны - Вениаминов В.Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1983, с. 121. . . 123. Могут быть реализованы на ИМС К555ТР2. Элементы "И" 17.3, 17.4 известны и описаны - Интегральные микросхемы: Справочник. Под ред. Б.В. Тарабрина. - М.: Радио и связь, 1984, с.60, с.485. Могут быть реализованы на ИМС К155ЛИ5. Последовательный регистр сдвига может быть реализован на ИМС К161ИР7 (Интегральные микросхемы: Справочник. Под ред. Б.В. Тарабрина. - М.: Радио и связь, 1984, с.102,с.490).

Параллельный регистр 18 предназначен для считывания информации, поступающей на его L входов с L выходов регистра сдвига 17 только в моменты поступления тактовых импульсов на его считывающий вход. Параллельные регистры известны и описаны - Вениаминов В. Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1983, с. 124... 125. Могут быть реализованы на микросхемах К155ТМ8.

Формирователь импульсов синхронизации 19 предназначен для формирования тактовых импульсов на первом выходе с регулируемой частотой следования в соответствии со значением коэффициента скорости kj, устанавливаемом через вход, а на втором выходе - с частотой следования соответствующей минимальной скорости передачи информационных сообщений Vmin. Формирователь импульсов синхронизации 19 можно построить на основе многочастотного генератора импульсов, описанного - Вениаминов В.Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1983, с. 136... 138, рис.4.29. При этом выход 6 элемента D9 является первым выходом формирователя импульсов синхронизации 19, а выход 11 одного из делителей D2...D8 - вторым выходом формирователя импульсов синхронизации. Управляющие сигналы v1, v2, v3 (S3,,*104", S2, ,*102", S1,,*101") поступают на вход формирователя тактовых импульсов 13 из блока управления 23 по шине, содержащей R=3 провода.

Распределитель импульсов 20 предназначен для распределения поступающих на вход импульсов последовательно по L выходам до поступления импульса сброса на установочный вход (с его поступлением распределение импульсов снова начинается с первого выхода). Распределитель импульсов 20 можно построить на базе распределителя импульсов, описанного - Гусев В.В. и др. Основы импульсной и цифровой техники. Учебное пособие для вузов. - М.: Сов. радио, 1975, c. 404...406, рис. 14.50. Пример реализации распределителя импульсов 20 показан на фиг.3. Для упрощения описания в приведенной схеме значение L принято равным 8. Таким образом, для данного случая распределитель импульсов 20 состоит из первой и второй линий задержки 20.1, 20.2, трех RS-триггеров 20.31, 20.32, 20.33, дешифратора 20.4, восьми (L=8) элементов "И" 20.51... 20.58. S-вход первого триггера 20.31 подключен к входу второй линии задержки 20.2 и является первым входом распределителя импульсов 20. Прямой выход первого триггера 20.31 подключен к первому прямому входу дешифратора 20.4 и S-входу второго триггера 20.32, прямой выход которого подключен к второму прямому входу дешифратора 20.4 и S-входу третьего триггера 20.33. Прямой выход третьего триггера 20.33 подключен к третьему прямому входу дешифратора 20.4. Инверсные выходы всех триггеров подключены к соответствующим инверсным входам дешифратора 20.4. Вход первой линии задержки 20.1 является установочным входом распределителя импульсов 20, а ее выход подключен к R-входам всех триггеров 20.31...20.33. Выход второй линии задержки 20.2 подключен к первым входам всех элементов "И" 20.51...20.58. Каждый i-ый выход дешифратора 20.4, где i=1, 2,...8 подключен к второму входу соответствующего i-го элемента "И" 20.51. ..20.58. Выход каждого i-го элемента "И" 20.51...20.58 является соответствующим i-ым выходом распределителя импульсов 20.

Первая линия задержки 20.1 идентична второй линии задержки 15 блока управления скоростью приема 2, вторая линия задержки 20.2 идентична первой линии задержки 14 блока управления скоростью приема 2. Триггер 20.3 идентичен триггеру 17.1, а элемент "И" 20.5 - элементу "И" 17.3 регистра сдвига 17. Дешифратор 20.4 известен и описан - Вениаминов В.Н. и др. Микросхемы и их применение. Справочное пособие. -М.: Радио и связь, 1983, с. 102... 104. Может быть реализован на микросхеме К555ИД7.

Дешифратор 21 предназначен для преобразования информации, поступающей в параллельном виде на его k из L входов, где k=1, 2,...L, со скоростью Vmin в информацию на выходе в последовательном виде со скоростью kVmin. Дешифратор 21 может быть построен на основе параллельного регистра на триггерах, описанного в известной литературе (см. Гусев В.В. и др. Основы импульсной и цифровой техники. Учебное пособие для вузов. - М.: Сов. радио, 1975, c. 382... 383, рис. 14.24). Схема дешифратора 21 показана на фиг.4. Дешифратор 21 состоит из L элементов "И" 21.11...21.1L и L RS-триггеров 21.21...21.2L. Первый и второй входы i-го элемента "И" 21-1i являются соответственно i-ым информационным и i-ым считывающим входом дешифратора 21 соответственно. Выход i-го элемента "И" 21.1i подключен к S-входу i-го RS-триггера 21.2i. R-входы всех RS-триггеров 21.21...21.2L объединены и являются входом гашения дешифратора 21. Выходы всех RS-триггеров 21.21...21.2L также объединены и являются выходом дешифратора 21. RS-триггеры 21.21...21.2L известны и описаны - Вениаминов В.Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1983, с. 121... 123. Могут быть реализованы на ИМС К555ТР2. Элементы "И" 21.11...21.1L известны и описаны - Интегральные микросхемы: Справочник. Под ред. Б.В. Тарабрина. - М.: Радио и связь, 1984, с.60, с.485. Могут быть реализованы на ИМС К155ЛИ5.

Блок управления 22 предназначен для установки коэффициентов скорости передачи k1...kL на блоках управления скоростью передачи 21... 2L и режима передающего коммутатора 3, а также передачи управляющей информации на приемную сторону. Схема блока управления 22 показана на фиг.5. Блок управления 22 состоит из кнопочного табло 22.1, генератора тактовых импульсов 22.2, преобразователя 22.3 и N кодопреобразователей 22.41...22.4N. R выходов j-ой группы выходов кнопочного табло 22.1 подключены к соответствующим R входам j-го кодопреобразователя 22.4j, а также к соответствующим R-входам j-ой группы входов преобразователя 22.3 и представляют собой одну шину, которая является j-ым управляющим выходом блока управления 22.. Запускающий выход кнопочного табло 22.1 подключен к входу генератора тактовых импульсов 22.2, выход которого подключен к тактовому входу преобразователя 22.3. Выход преобразователя 22.3 является служебным выходом блока 22. q-ые выходы кодопреобразователей 22.41. . .22.4N, где q=1, 2,...Q, a Q - число разрядов для управления передающим коммутатором 3, объединены и являются q-ым коммутирующим выходом блока управления 22. Генератор тактовых импульсов 22.2 известен и описан - Вениаминов В.Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1983, с.210, рис.7. 10г). Может быть реализован на микросхеме К555АГ3. Кодопреобразователь 22.4 известен и описан - Вениаминов В.Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1983, с. 104... 106. Может быть реализован на микросхеме К155ПР7. Преобразователь 22.3 предназначен для преобразования RN управляющих сигналов на его входах из параллельного в последовательный вид на выходе. В качестве преобразователя 22.3 можно использовать передающее устройство, описанное - Шляпоберский В.И. Основы техники передачи дискретных сообщений. - М.: Связь, 1973, с. 141. . . 142, рис.3.31. Триггеры и элементы "И", используемые в преобразователе 22.3, идентичны триггерам 21.2 и элементам "И" 21.1 дешифратора 21.

Блок управления 23 предназначен для установки коэффициентов скорости приема k1. . . kL на блоках управления скоростью приема 111... 11L и режима приемного коммутатора 10 в соответствии с информацией, принятой по служебному входу. Схема блока управления 23 показана на фиг.6. Блок управления 23 состоит из регистра сдвига 23.1, генератора тактовых импульсов 23.2 и N кодопреобразователей 23.31. .. 23.3N. Информационный вход регистра сдвига 23.1 подключен в входу генератора тактовых импульсов 23.2 и является служебным входом блока управления 23. Выход генератора тактовых импульсов 23.2 подключен к тактовому входу регистра сдвига 23.1. R выходов j-ой группы выходов регистра сдвига 23.1 подключены к соответствующим входам j-го кодопреобразователя 23.3j, представляют собой одну шину, которая является j-ым управляющим выходом блока управления 23. q-ые выходы кодопреобразователей 23.31... 23.3N объединены и являются q-ым коммутирующим выходом блока управления 23. Регистр сдвига 23.1 представляет собой регистр сдвига последовательно-параллельного типа, известен и описан - Вениаминов В.Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1983, с. 127... 128, рис. 4.21. Может быть реализован на D-триггерах К570ТМ1. Кодопреобразователь 23.3 идентичен кодопреобразователю 22.4 блока управления 22.

Генератор тактовых импульсов 23.2 предназначен для формирования тактовых импульсов с приходом служебной команды, число которых соответствует числу информационных посылок в этой команде. Генератор тактовых импульсов 23.2 состоит из (фиг. 7) ключа 23.2.3, автогенератора 23.2.2, делителя 23.2.1. Первый управляющий вход ключа 23.2.3 является входом генератора 23.2, второй управляющий вход ключа соединен с выходом делителя 23.2.1. Выход ключа 23.2.3 подключен к входу автогенератора 23.2.2. Выход автогенератора 23.2.2 подключен к входу делителя 23.2.1 и является выходом генератора тактовых импульсов 23.2. В качестве автогенератора 23.2.2 может быть использован генератор на интегральных импульсных усилителях, который описан - Шило В.Л. Популярные цифровые микросхемы, Челябинск: Металлургия, 1989 г., стр. 51, рис. 1.31 а. Может быть реализован на ИМС К155ЛН1. В качестве ключа 23.2.3 может быть использован диодный ключ, который описан - Булычев А.Л. и др. Аналоговые интегральные микросхемы - Минск, Беларусь, 1994 г., стр. 328, рис. 2.57 а, б. Ключ может быть реализован на ИМС 228КН1. При этом выводы 1, 2 ИМС 228КН1 являются соответственно управляющим входами 1 и 2 ключа 23.2.3 (фиг. 8), а к выводу 4 ИМС 228КН1 (входу питания ключа 23.2.3) подключается напряжение питания Uпит и с вывода 14 ИМС 228КН1 (выхода ключа 23.2.3) подается на автогенератор. Делитель 23.2.1 известен и описан - Вениаминов В.Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1983, стр.137, рис.4.28 б и может быть реализован на ИМС К 561ИЕ8.

Многоканальная система передачи и приема дискретной информации работает следующим образом. Предположим, что на передающей стороне с выходов N источников дискретной информации 11... 1N на информационные входы соответствующих N блоков управления скоростью передачи поступают однополярные посылки с различной скоростью Vj=kj•Vmin. При этом, их общая скорость  не может быть больше максимальной Vmax=М•Vmin, где Vmin - минимальная скорость, т.е. скорость, которую обеспечивает каждый канал на входе мультиплексора 4, а М - число каналов мультиплексора 4, где М≥N•kj. В соответствии с коэффициентом изменения скорости передачи kj на каждом из kj выходах соответствующего j-го блока управления скоростью передачи 2j появляются информационные посылки со скоростью Vmin. Так как скорость передачи от j-го источника дискретных сообщений lj в kj раз больше скорости, обеспечиваемой одним каналом мультиплексора 4 Vmin, то поток информационных посылок разбивается на группы по kj посылок в каждой, при этом первая посылка появляется на первом выходе блока управления скоростью передачи, вторая - на втором и т.д., a k-ая на k-ом выходе. Диаграммы, характеризующие работу, например, трех источников дискретных сообщений со скоростями 3Vmin, 2Vmin, 1Vmin при общем количестве каналов мультиплексора 4 М=6 показаны на фиг.9. Блок управления 22 с помощью коммутатора 3 подключает соответствующие выходы каждого j-го блока управления скоростью передачи, на которых появились информационные посылки, к каналам мультиплексора 4. В мультиплексоре 4 они объединяются и через блок защиты от ошибок 5 и блок преобразования сигналов 6 передаются на приемную сторону. Служебная информация о количестве kj каналов мультиплексора 4, выделяемых каждому j-му источнику дискретных сообщений (начиная с 1-го по N-ый), передается со служебного выхода блока управления 22 на передающей стороне в блок управления 23 на приемной стороне по специально выделенному каналу в групповом тракте перед началом передачи.

не может быть больше максимальной Vmax=М•Vmin, где Vmin - минимальная скорость, т.е. скорость, которую обеспечивает каждый канал на входе мультиплексора 4, а М - число каналов мультиплексора 4, где М≥N•kj. В соответствии с коэффициентом изменения скорости передачи kj на каждом из kj выходах соответствующего j-го блока управления скоростью передачи 2j появляются информационные посылки со скоростью Vmin. Так как скорость передачи от j-го источника дискретных сообщений lj в kj раз больше скорости, обеспечиваемой одним каналом мультиплексора 4 Vmin, то поток информационных посылок разбивается на группы по kj посылок в каждой, при этом первая посылка появляется на первом выходе блока управления скоростью передачи, вторая - на втором и т.д., a k-ая на k-ом выходе. Диаграммы, характеризующие работу, например, трех источников дискретных сообщений со скоростями 3Vmin, 2Vmin, 1Vmin при общем количестве каналов мультиплексора 4 М=6 показаны на фиг.9. Блок управления 22 с помощью коммутатора 3 подключает соответствующие выходы каждого j-го блока управления скоростью передачи, на которых появились информационные посылки, к каналам мультиплексора 4. В мультиплексоре 4 они объединяются и через блок защиты от ошибок 5 и блок преобразования сигналов 6 передаются на приемную сторону. Служебная информация о количестве kj каналов мультиплексора 4, выделяемых каждому j-му источнику дискретных сообщений (начиная с 1-го по N-ый), передается со служебного выхода блока управления 22 на передающей стороне в блок управления 23 на приемной стороне по специально выделенному каналу в групповом тракте перед началом передачи.

На приемной стороне, пройдя через блоки преобразования сигналов и защиты от ошибок, сигналы разделяются (разгруппировываются) в мультиплексоре 9 и поступают на коммутатор 10. Блок управления 23 в соответствии с принятой служебной информацией выдает команды на приемный коммутатор 10 для подключения выходных каналов мультиплексора 9 к необходимому количеству выделенных каждому блоку управления скоростью приема 11j каналов kj. Коммутатор 10 осуществляет подключение. В каждом j-ом блоке управления скоростью приема 11j происходит обратное преобразование числа каналов kj в число посылок на временном интервале, соответствующем минимальной скорости передачи τ = 1/Vmin Далее с выходов блоков управления скоростью приема 111... 11N информационные посылки с соответствующими скоростями передачи Vj поступают на входы соответствующих приемников дискретных сообщений 121...12N. Диаграммы, поясняющие принцип обработки сигналов при приеме информации от трех источников дискретных сообщений со скоростями 3Vmin, 2Vmin, 1Vmin при общем количестве каналов мультиплексора 4 М=6 показаны на фиг.11.

Блок управления скоростью передачи 2 работает следующим образом. С поступлением информационных посылок на первый вход формирователя тактовых импульсов 13 подается питание на его задающий генератор. Он запускается, и на третьем выходе формирователя тактовых импульсов 13 появляются тактовые импульсы с частотой следования, соответствующей минимальной скорости передачи сообщений Vmin, а на первом и втором выходах формирователя тактовых импульсов 13 появляются импульсы с частотой следования в kj раз большей. При этом коэффициент kj устанавливается по команде с блока управления 22 через второй вход формирователя тактовых импульсов 13. С первого выхода формирователя тактовых импульсов 13 тактовые импульсы поступают на второй вход регистра сдвига 17, со второго выхода эти же импульсы, но уже с задержкой на τз1 в первой линии задержки 14, поступают на третий вход регистра сдвига 17, а с третьего выхода тактовые импульсы с частотой следования, соответствующей минимальной скорости передачи информационных посылок Vmin, поступают на четвертый вход регистра сдвига 17 с задержкой τз2 во второй линии задержки 15. Диаграммы, поясняющие принцип работы регистра сдвига 17 и параллельного регистра 18 первого блока 2, при поступлении на его вход информационных посылок, например, со скоростью в 3 раза превышающую минимальную (k1=3), показаны на фиг. 10. Таким образом, в регистре сдвига 17 информационные посылки, поступающие на первый вход, продвигаются под действием двух последовательностей тактовых импульсов, сдвинутых друг относительно друга на τз1. Информационные посылки появляются не одновременно на L выходах регистра сдвига 17, а с нарастающим сдвигом. При этом сдвиг информации между соседними выходами равен длительности информационной посылки. Сброс (гашение) информации в триггерах регистра сдвига 17 осуществляется при подаче тактовых импульсов на четвертый вход регистра сдвига 17. Интервал между гасящими импульсами равен длительности информационной посылки при минимальной скорости передачи Vmin. Сдвинутые во времени информационные посылки с L выходов регистра сдвига 17 поступают на L входов параллельного регистра 18. На считывающий вход параллельного регистра 18 поступают считывающие импульсы с временем задержки τз3, меньшим времени задержки гасящих импульсов τз2, поступающих на четвертый вход регистра сдвига 17 (τз3<τз2). На L выходах параллельного регистра 18 появляются только те посылки, которые в момент действия считывающего импульса были на соответствующих L входах. Длительность их на L выходах параллельного регистра 18 равна длительности информационных посылок при минимальной скорости передачи Vmin.

Блок управления скоростью приема 11 работает следующим образом. В соответствии с управляющими сигналами, поступающими на второй вход по шине от блока управления 23 формирователь импульсов синхронизации 19, вырабатывает последовательность тактовых импульсов на первом выходе с частотой следования, пропорциональной коэффициенту скорости kj для данного блока управления скоростью приема 11j. Эти импульсы поступают на первый вход распределителя импульсов 20, где последовательно распределяются по k из L выходов до поступления импульса сброса на установочный вход. Импульсы сброса с частотой, соответствующей минимальной скорости приема (передачи), вырабатывает на своем втором выходе формирователь импульсов синхронизации 19. С приходом импульса сброса распределение импульсов, поступающих на первый вход распределителя импульсов 20, начинается снова с первого выхода. Далее эти импульсы поступают на соответствующие считывающие входы дешифратора 21. На информационные входы дешифратора 21 (см. фиг.4) и далее через элементы "И" 21.11... 21.1L на триггеры 21.21...21.2L поступают информационные посылки с информационных выходов приемного коммутатора 10. Запись в соответствующий i-ый триггер 21.2i производится при наличии импульса считывания на втором входе i-го элемента "И" 21.1i. По его команде триггер 21.2i устанавливается в соответствующее информационному импульсу состояние. В это же время поступает считывающий импульс на следующий i+1-ый элемент "И" 21.1i+1 и по его команде производится запись в следующий i+1-ый триггер 21.2i+1. Сброс осуществляется тактовыми импульсами, поступающими на вход гашения дешифратора 21. Таким образом, на выходе дешифратора 21 последовательно появляются импульсы с выходов сначала первого, затем второго и так по k-ый триггер 21.21... 21.2k.

Установка скоростей передачи и приема осуществляется с помощью блоков управления 22 и 23 следующим образом. Управляющие сигналы формируются последовательно кнопочными переключателями, начиная с первого, на табло 22.1 (см. фиг. 5). По управляющим шинам, содержащим R проводов, где R - число управляющих входов формирователя тактовых импульсов 13 (для элемента D9 на ИС К155КП5 их три), они устанавливают свой коэффициент скорости передачи kj (коэффициент деления формирователя тактовых импульсов 13) для j-го блока управления скоростью передачи 2j. Также эти сигналы поступают на соответствующие кодопреобразователи 22.41... 22.4N, где они преобразуются в управляющие сигналы на Q выходах (для ИС К1509КП1 - пять управляющих сигналов), используемые для установки режима передающего коммутатора 3. Таким образом, кроме определения коэффициента деления формирователя тактовых импульсов 13 коэффициент kj определяет число выходов блока управления скоростью передачи 2j, которые необходимо подключить к выходам передающего коммутатора 3. Например, в случае, когда k1= 3, k2=2, k3=1 (см. фиг.9) третий, второй и первый выходы первого блока управления скоростью передачи 21 необходимо подключить соответственно к первому, второму и третьему выходам передающего коммутатора, (т. е. к первому, второму и третьему каналам мультиплексора 4) второй и первый выход второго блока управления скоростью передачи 22 - к четвертому и пятому выходам, а первый выход третьего блока управления скоростью передачи 23 - к шестому выходу. Кроме того, управляющие сигналы после приведения к последовательному виду в преобразователе 22.3 поступают на служебный выход и далее передаются на приемную сторону. Генератор тактовых импульсов 22.2 запускается с кнопочного табло 22.1 отдельной кнопкой после установки коэффициентов скоростей на всех блоках и обеспечивает работу преобразователя 22.3.

На приемной стороне в блоке управления 23 (см. фиг.6) с первым импульсом запускается генератор тактовых импульсов 23.2, который вырабатывает определенное число тактовых импульсов (2*N*R), поступающих на тактовый вход регистра сдвига 23.1. Информация снимается последовательно во времени и с последними тактовыми импульсами на выходах регистра сдвига 23.1 устанавливается окончательная кодовая комбинация, соответствующая управляющим сигналам на передающей стороне. Генератор тактовых импульсов 23.2 работает следующим образом. Последовательность служебных символов поступает первоначально на первый управляющий вход ключа 23.2.3 (фиг.8) через интегрирующую RC-цепь, создает на выводе 1 ИМС 228КН1 напряжение высокого уровня и тем самым включает цепь питания автогенератора 23.2.2. Делитель 23.2.1 с коэффициентом деления 2*N*R после получения с выхода генератора 23.2.2 2*N*R импульсов вырабатывает на своем выходе напряжение высокого уровня, которое подается на второй управляющий вход ключа 23.2.3 и выключает питание автогенератора.

В ходе ведения связи может возникнуть необходимость изменить скорость передачи отдельных источников дискретных сообщений 11...1N или перераспределить пропускную способность между ними. В этом случае с помощью блока управления 22 снова устанавливаются коэффициенты скорости передачи (коэффициенты деления) kj, перераспределяются каналы в передающем коммутаторе 3 и служебная информация об этих изменениях передается на приемную сторону в блок управления 23, который также осуществляет необходимые переключения.

Таким образом, в предложенном устройстве имеется возможность оперативно перераспределять пропускную способность общего тракта между отдельными источниками дискретных сообщений при изменении количества работающих источников и их скорости передачи.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПРИЕМА И ОБРАБОТКИ ИНФОРМАЦИИ | 2002 |

|

RU2213424C1 |

| УСТРОЙСТВО ДЕЦЕНТРАЛИЗОВАННОГО УПРАВЛЕНИЯ РАСПРЕДЕЛЕНИЕМ ПАКЕТОВ СООБЩЕНИЙ В СЕТИ ПЕРЕДАЧИ ДАННЫХ | 2002 |

|

RU2213427C1 |

| РАДИОЛИНИЯ С АМПЛИТУДНО-ФАЗОМАНИПУЛИРОВАННЫМИ ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1999 |

|

RU2163746C1 |

| УСТРОЙСТВО АДАПТИВНОГО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2001 |

|

RU2194366C2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2001 |

|

RU2199148C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2000 |

|

RU2179334C1 |

| УСТРОЙСТВО ДИСКРЕТНО-ВЕСОВОГО СЛОЖЕНИЯ РАЗНЕСЕННЫХ СИГНАЛОВ | 2002 |

|

RU2220504C1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ (ВАРИАНТЫ) | 1999 |

|

RU2163027C2 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2185029C1 |

| РАДИОЛИНИЯ С АМПЛИТУДНО-ФАЗОМАНИПУЛИРОВАННЫМИ ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1999 |

|

RU2144272C1 |

Изобретение относится к технике связи и может быть использовано при многоканальной передаче дискретных сообщений. Техническим результатом является разработка системы, обеспечивающей максимальное использование пропускной способности группового тракта при оперативном управлении скоростью передачи источников дискретных сообщений. Технический результат достигается тем, что на передающей стороне информационные посылки, поступающие на вход блока управления скоростью передачи со скоростью Vj=kj•Vmin, где j=1, 2, ... N, а k= 1, 2, ... М, преобразуются в информационные посылки со скоростью Vmin на kj выходах блока, при условии, что

Распределение различного числа низкоскоростных каналов связи (Vmin) на входе мультиплексора между источниками дискретных сообщений, работающих с различными скоростями в процессе обмена сообщениями, осуществляется с помощью передающего коммутатора и блока управления. В передаче информации, а также группировании и разгруппировании каналов принимают участие блоки защиты от ошибок, блоки преобразования сигналов, мультиплексоры. На приемной стороне производят обратное преобразование М низкоскоростных каналов в N каналов приема информации с требуемой скоростью с помощью приемного коммутаторами и блока управления. 11 ил.

Многоканальная система передачи и приема дискретной информации, содержащая на передающей стороне - N источников дискретной информации, где N≥2, мультиплексор, выход которого подключен к входу блока защиты от ошибок, выход которого подключен к входу блока преобразования сигналов, выход которого является выходом передающей части системы, и на приемной стороне - блок преобразования сигналов, вход которого является входом приемной части системы, а выход подключен к входу блока защиты от ошибок, выход которого подключен к входу мультиплексора, и N приемников дискретной информации, отличающаяся тем, что на передающей стороне дополнительно введены N блоков управления скоростью передачи, блок управления коэффициентами скорости передачи, передающий коммутатор, причем выход j-го источника дискретной информации, где j=1,2,...N, подключен к информационному входу j-го блока управления скоростью передачи, L выходов j-го блока управления скоростью передачи, где L≥N, подключены к соответствующим L информационным входам j-й группы входов передающего коммутатора, а М выходов передающего коммутатора, где M≥L≥N, подключены к соответствующим М входам мультиплексора, j-й управляющий выход блока управления подключен к управляющему входу j-го блока управления скоростью передачи, Q коммутирующих выходов блока управления подключены к соответствующим Q управляющим входам передающего коммутатора, служебный вход которого подключен к служебному выходу блока управления, а на приемной стороне дополнительно введены N блоков управления скоростью приема, блок управления коэффициентами скорости приема, приемный коммутатор, причем вход j-го приемника дискретной информации подключен к выходу j-го блока управления скоростью приема, М выходов мультиплексора подключены к соответствующим М входам приемного коммутатора, L информационных выходов j-й группы выходов которого подключены к соответствующим L информационным входам j-го блока управления скоростью приема, j-й управляющий выход блока управления подключен к управляющему входу j-го блока управления скоростью приема, Q коммутирующих выходов блока управления подключены к соответствующим Q управляющим входам приемного коммутатора, служебный выход которого подключен к служебному входу блока управления.

| МАЛИНОВСКИЙ С.Т | |||

| Сети и системы передачи дискретной информации и АСУ | |||

| - М.: Связь, 1979 | |||

| МНОГОКАНАЛЬНАЯ ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1990 |

|

RU2013012C1 |

| ДОБАВКА ДЛЯ МАТЕРИ, ПРЕДНАЗНАЧЕННАЯ ДЛЯ УКРЕПЛЕНИЯ ИММУННОЙ СИСТЕМЫ РЕБЕНКА | 2012 |

|

RU2586150C2 |

| US 5303237 А, 12.04.1994 | |||

| Устройство для уплотнения свежесформованного волокнистого изделия | 1973 |

|

SU444656A1 |

Авторы

Даты

2003-06-27—Публикация

2001-07-20—Подача