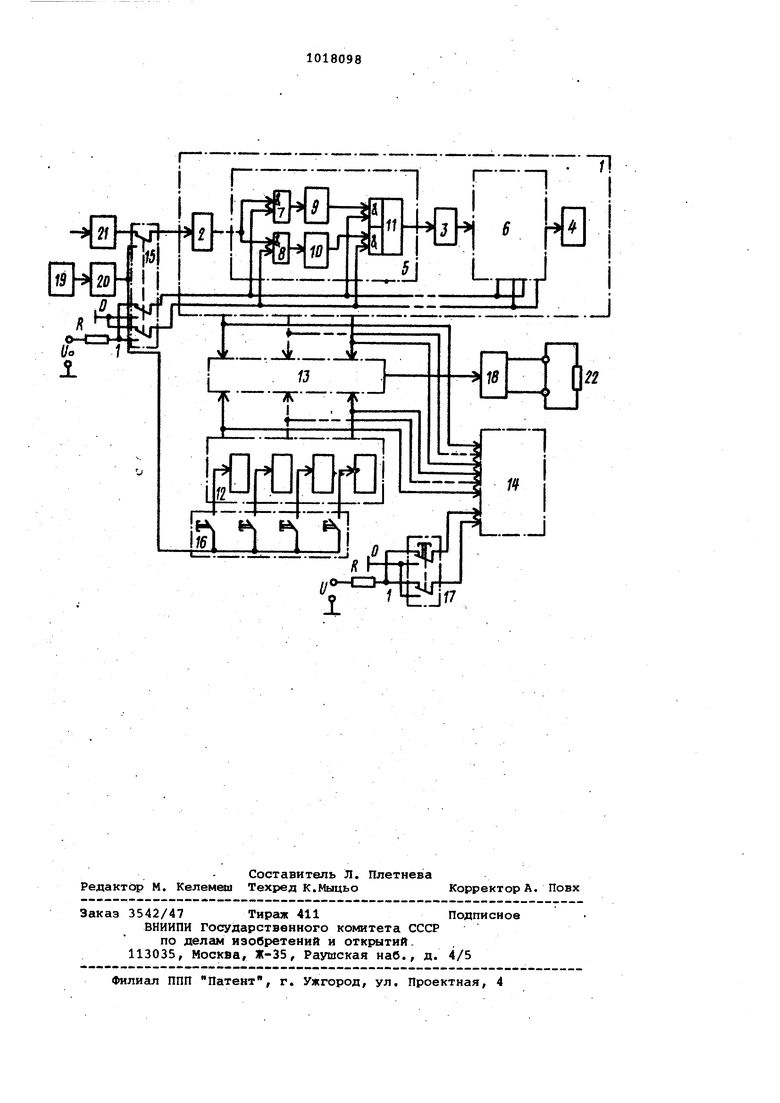

Изобретение относится к импуль .рной технике и может быть использовано в программных системах автоматического управления. Известно устройство для сигнализсщии времени, содержащее ге нератор импульсов синхронизации, три счетчика импульсов, прибор Установки времени, предназначенный для хранения значения времени, о котором сигнализируем, и для формирования кодиг рЬванного выходного сигнала, представляющего это время, схему совпаде ния, предназначенную для сравнения кодированных выходных сигналов счета второго и третьего счетчиков с кодированньв4 выходным сигналом прибора установки времени для всех двоичных разрядов одновременно и формирования сигнала совпадения при наступлении совпадения между ними, причем каскад управления нагрузкой возбуждается этим сигналом совпадения и управляет прибором-потребителем Clj, Недостаткалм известного устройств являются: отсутствие входа для ввода внешних импульсов синхронизации, невозможность программированного под счету количества внешних импульсов синхронизации, отсутствие визуальной индикации состояния счетчиков времени и прибора установки времени; Цель изобретения - расширение фун кциональных возможностей устройства. Поставленная цель достигается тем что в комбинированное цифровое устройство для измерения интервала времени, содержащее последовательно соединенные генератор тактовых импульсов и д елитель частоты, блок счета, выходы котсфого соединены с первой группой входов блока элементов совпа дения, вторая группа входов которого соединена с выходами блока памяти, выход блока элементов совпадения под ключен Kj входу блока управления нагруэкой, введены два коммутатора, формирователь импульсов и ключ, причем вход формирователя импульсов соединен с.входной шиной, а его выход с первым входом первого коммутатора, второй вход которого подключен к выходу делителя частоты и входу второго коммутатора, выходы которого соединены с соответствующими входами блока памяти, выходы которого подклю чены к первой группе блока индикации вторая группа входов которой соединена с выходами счетного блока, первый, второй и третий входы которого соединены соответственно с nepBtBvi, вторым и третьим выходами первого коммутатора, третий и четвертый входы которого объединены и соединены с шиной уровня логической 1 и первым и вторым входами ключа, пятый и шестой входы первого коммутатора объединены и соединены с шиной уровня логического О и третьим и четвертым входами ключа, выходы которого соединены о управляющими входами блока индикации. Кроме того, блок счета содержит три делителя частоты и два блока коммутации, причем первый вход блока счета срединен через первый делитель частоты с первым входом первого блока коммутации, выход которого через второй делитель частоты подключен к первому входу второго блока коммутации, выход которого подключен к входу третьего делителя частоты, вторые входы коммутаторов объединены и соединены с вторым входом счетного блока, третий вход которого подключен к объединенным третьим входам коммутаторов, выходы делителей частоты являются выходами блока. При этом кажддай блок коммутации содержит два элемента И, два делителя частоты и элемент 2 И-ИЛИ, выход которого является выходом блока, Первый вход блока коммутации соединен с первыми входами элементов И, второй вход первого из которых соединен с первым входом элемента 2 И-ИЛИ и с вторым входом блока, а выход - через первый делитель частоты с вторым входом элемента 2 И-ИЛИ, второй вход второго элемента И подключен к третьему входу элемента 2 И-ИЛИ и третьему входу блока, а выход через второй делитель частоты - к четвертому входу элемента 2 И-ИЛИ. На чертеже изображена структурная электрическая схема предложенного устройства. Устройство содержит блок 1 счета, в состав которого входят делители 2-4 частоты, блоки 5 и б коммутации, в состав каждого из входят элементы 7 и 8 И, делители 9 и 10 частоты соответственно на десять и на шесть и элемент 11 2И-ИЛИ, блок 12 памяти, блок 13 элементов совпадения, блок 14 индикации, коммутаторы 15 и 16, ключ 17, блок 18 управления нагрузкой, генератор 19 тактовых импульсов, делитель 20 частоты, формирователь 21 импульсов и нагрузку 22. Блок 5 (6) коммутации обеспечивает работу блока 1 счета и устройства в целом в режиме подсчета количества поступивших на вход нагрузки 22 и формирователя 21 импульсов(первый режим) и в режиме подсчета времени работы нагрузки (второй режим). Форкйрователь 21 импульсов предназначен для преобразования-входных импульсов отрицательной или положительной полярности к виду,удобному для работы блока 1. Коммутатор 15 предназначен для выбора режима работы устройства. Ключ 17 предназначен для подачи в соответствующие цепи блока 14 индикации уровней-логического О и логической 1 при визуальной индикации состояний блока 1 счета и состояния счетчиков, входящих в состав блока 12 памяти.

На чертеже, в части блока 5 коммутации для простоты объяснения принципа его работы показаны два делителя, которые могут ейзть выполнены на базе двоично-десятичных декадных счетчиков, причем один из них работает в режиме деления частоты на десять, другой - на шесть. В реальной принципиальнЪй схеме возможно использование только одного двоично-десятичного счетчика с предустановкой.

Устройство |работает следующим образом.

На чертеже коммутатор 15 показан в положении, при котором устройство подготовлено к первому режиму работы При этом на один из входов злемента 7 и соответствующий вход элемента 11 подан уровень логической 1. Блок 5 коммутации и блок 1 счета в целом подготовлены к суммированию импульсов. .

Работу устройства можно условно разбить, на два этапа.

Первый этап - подготовительный. При этом ключ 17 устанавливается в положение, соответствующее режиму индикации состояния счетчиков блока 12 памяти. От. делителя 20 частоты, имеющего на выходе частоту 1 Гц, путем последовательного подключения с помр1 Ц ю коммутатора 16 входа каждого счетчика блока 12 вводится в блок 12 памяти програмктруемое число импульсов, которое необходимо подать в нагрузку 22. Соответствующий вход отключается в тот момент, когда в выбранном декадном счетчике зафиксирована необходимая информация. Ключ 17 устанавливается в исходное состояние. При этом блок 14 индикации подключается к блоку 1. На этом подготовительный этап работы устройства заканчивается.

Второй этап - собственно .измерения. Устройство начинает работать одновременно с работой нагрузки 22. .В момент равенства числа импульсов, поступивших в нагрузку 22 и на вход блока 1 счета с информацией,, заложенной в блок 12 памяти, срабатывает блок,13 элементов совпадения, в котором вырабатывается сигнал совпадения поступающий далее в блок 18 управления нагрузкой. Блок 18 воздействует соответствующим образом на нагрузку

Согласно BTOpewiy режиму работы устройства коквлутатор 15 устанавливается в другое устойчивое состояние При этом на один из входов элемента 8 и соответствующий вход элемента 11 подается уровень логической 1, блок 5 комк тации и блок 1 счета в целом подготовлены к работе в каНестве электронных часов. Во втором режиме этапы работы устройства те же, что и в первом режиме. При этом в блок 12 памяти закладывается информация о времени работы нагрузки 22.

Конструкция предложенного устройства по сравнению с известным дает возможность применить данное устройство к технологическим процессам с чередующимся контролируемом импульсным или периодическим режимом работы нагрузки. Кроме того, в процессе длительности работы нагрузки возможно проконтролировать или даже изменить программу работы нагрузки без ее выключения путем внесения корректив в блок памяти. И, наконец, можно изменить временной диапазон работы устройства, что достигается путем изменения объема памяти блока памяти и соответствующего изменения числа разрядов блока счета при незначительном внесении изменений в блок элементов совпадения и в блок индикации .

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор экстремумов | 1984 |

|

SU1196810A1 |

| Устройство для контроля центрировки линз | 1983 |

|

SU1196715A1 |

| Устройство для автоматической центрировки линз | 1982 |

|

SU1118882A1 |

| Устройство для управления преобразователем | 1983 |

|

SU1096748A1 |

| Устройство для измерения девиации частоты линейно-частотно-модулированного колебания | 1989 |

|

SU1711087A1 |

| Устройство для отображения информации | 1985 |

|

SU1285525A1 |

| Устройство для контроля высоковольтного тиристорного вентиля | 1983 |

|

SU1153374A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2009 |

|

RU2417537C1 |

| АВТОМАТИЧЕСКИЙ СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ПЕРИОДОВ ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2105410C1 |

| Устройство для определения содержания связующего в стеклопластиках | 1984 |

|

SU1265538A1 |

1. КОМБИНИРОВАННОЕ ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ИНТЕРВАЛА ВРЕМЕНИ, содержгипее последовательно соединенные генератор тактовых импульсов и делитель частоты, блок счета, выходы которого соединены с первой группой входов блока элементов совпадения, вторая группа входов которого соединена с выходами блока памяти, выход блока элементов совпадения подключен к входу блока управления нагрузкой, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены два кокмутатс а, ф мирователь импульсов и ключ, щжчем вход формирователя импульсов соединен с входной шиной, а его выход - с первым входом первого коммутатора, второй вход которого подключен к выходу делителя частоты и входу второго коммутатора, выходы которого соединены с соответствующими входами блока пшляти, выходы которого подключены к первой группе входов блока индикации, вторая группа входов которой соединена с выходами счетного блока, первый, второй и третий входы которого соединены соответственно с первым, вторым и третьим выходами первого коммутатора, третий и.четвертый входы которого объединены и соединены с шиной уровня логической 1 и первым и вторым входами ключа, пятый и шестой входы первого коммутатора .объединены и соединены с шиной уровня логического О и третьим и четвертым входами .ключа, выходы которого соединены с .управляющими входами блока индикации. 2.Устройство по п. 1, отличающееся тем, что блок счета содержит три делителя частоты и два блока коммутации, причем первый вход блока счета соединен через первый делитель частоты с первым входом первого блока коммутации, выход которого через второй делитель частоты под ключен к первому входу второго блока Коммутации, выход которого подключен , k входу третьего делителя частоты, 9 входы коммутаторов объединены и соединены с вторым входом счетноТо блока,третий вход которого подключен к объединенным третьи: входам комУ1Утатора,выходы делителей частоты являются выходами блока. 3.Устройство по пп. 1 и 2, о т -i ;i и чающееся тем, что Каждьй бпок коммутации содержит два элемента И , два делителя частоты и элемент 2И-ИЛИ, выход которого является выходом блока, первый вход блока коммутации соединен с первыми входами 00 I элементов И, второй вход первого о о из которых соединен с первым входом элемента 2И-шга и с вторым входом блока, а выход - через первый дели00 тель частоты с вторым входом элемента 2И-ИЛИ, второй вход второго элемента И подключен к третьему йхолУ элемента 2И-ИЛИ и третьему входу блока, а выход через второй делитель частоты - к четвертому входу элемента 2И-ИЛИ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент ОНА №4131855, .кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-05-15—Публикация

1981-07-16—Подача