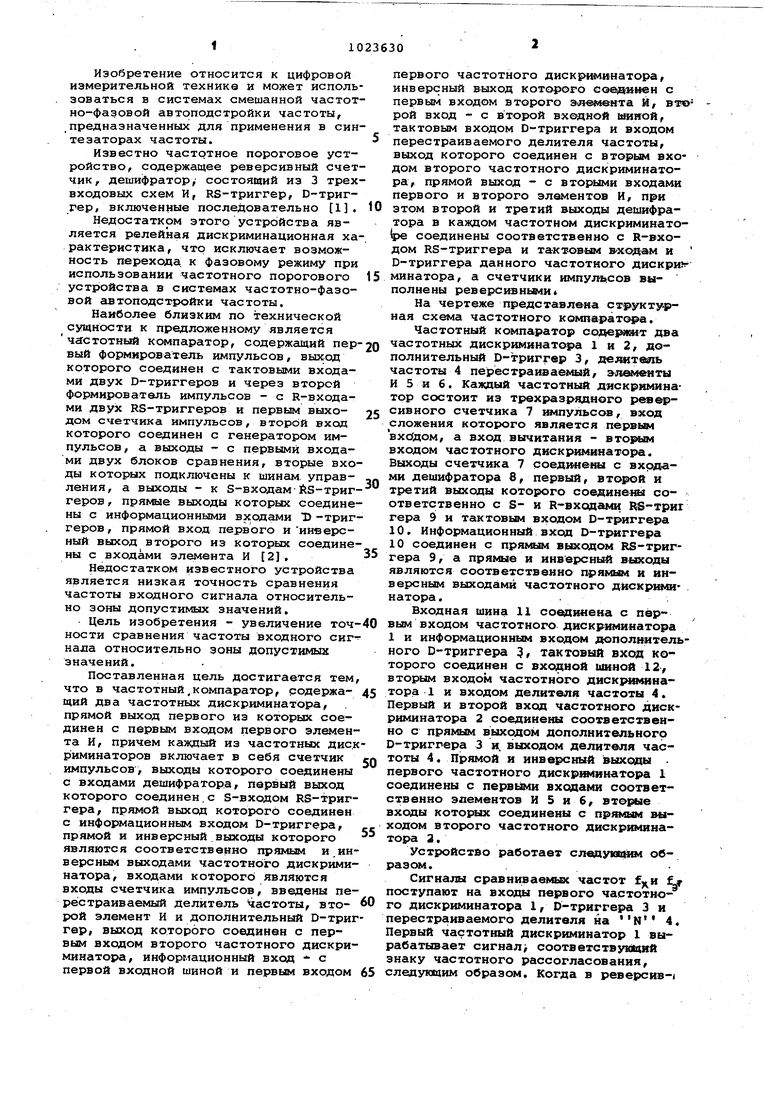

Изобретение относится к цифровой измерительной технике и может использоваться в системах смешанной частотно-фазовой автоподстройки частоты, предназначенных для применения в синтезаторах частоты. Известно частотное пороговое устройство, содержащее реверсивный счетчик, дешифратор, состоящий из 3 трехвходовых схем И, RS-триггер, D-триггер, включенные последовательно 1. Недостатком этого устройства является релейная дискриминационная характеристика, что исключает возможность перехода; к фазовому режиму при использовании частотного порогового устройства в системах частотно-фазовой сштопод с тройки частоты. Наиболее близким по технической сущности к предложенному является частотный компаратор, содержащий первый формирователь импульсов, выход которого соединен с тактовыми входами двух D-триггеров и через второй формирователь импульсов - с R-входами двух RS-триггеров и первым выходом счетчика импульсов, второй вход которого соединен с генератором импульсов , а выходы - с первыми входами двух блоков сравнения, вторые входы которых подключены к шинам управления, а выходы - к S-входам ftS-триггеров, прямые выходы которых соединены с информационными входами U-триг геров , прямой вход первого иинверсный выход второго из которых соединены с входами элемента И 2. Недостатком известного устройства является низкая точность сравнения частоты входного сигнала относительно зоны допустимых значений. Цель изобретения - увеличение точности сравнения частоты входного сигнала относительно зоны допустимых значений. Поставленная цель достигается тем что в частотный,компаратор, родерзкащий два частотных дискриминатора, прямой выход первого из которых соединен с первым входом первого элемента И, причем каждый из частотных дис.к риминаторов включает в себя счетчик импульсов, выходы которого соединены с входами дешифратора, первый выход которого соединен.с S-входом RS-триггера, прямой выход которого соединен с информационным входом D-триггера, прямой и инверсный выходы которого являются соответственно прямым и ин версным выходами частотного дискриминатора, входами которого являются входы счетчика импульсов, введены перестраиваемый делитель Частоты, второй элемент И и дополнительный D-триг гер, выход которого соединен с первым входом второго частотного дискриминатора, информационный вход с первой входной шиной и первым входом первого частотного дискр-иминатора, инверсный выход которого соедагмен с первым входом второго элеллента И, вто рой вход - с второй входной шиной, тактовым входом D-триггера и входом перестраиваемого делителя частоты, выход которого соединен с вторым входом второго частотного дискриминатора, прямой выход - с вторыми входами первого и второго элементов И, при этом второй и третий выходы дешифратора в каждом частотном дискриминато(ре соединены соответственно с R-BXOдом RS-триггера и тактов-ым выходам и D-триггера данного частотного дискри минатора, а счетчики 1шпуль.сов выполнены реверсивнь№4И« На чертеже представлена структу рная схема частотного компаратора. Частотный компаратор два частотных дискриминатора 1 и 2, дополнительный D-триггер 3, деяитеяь частоты 4 перестраиваемый, элементы И 5 и 6. Каждый частотный дискриминатор состоит из трехразрядного реверсивного счетчика 7 импульсов, вход сложения которого является первым вхс(цом, а вход вычитания - вторым входом частотного дискриминатора. Выходы счетчика 7 соединены с входами дешифратора 8, первый, второй и третий выходы которого соедине1а1 соответственно с S- и R-вхсдами RS-триг гера 9 и тактовым входом D-триггера 10. Информационный D-триггера 10 соединен с прямым в|ьвсодом RS-триггера 9, а прямые и инверсный В1:всоды являются соответственно прямым и ииверсным выходами частотного дискриминатора. Входная шина 11 соединена с первым входом частотного дискриминатора 1 и информационным входом дополнительного о-триггера 3 тактовый вход которого соединен с входной шиной 12, вторым входом частотного дискриминатора 1 и входом делителя частоты 4. Первый и второй вход частотного дискриминатора 2 соединены соответственно с прямым выходом дополнительного D-триггера 3 и. выходом делителя частоты 4. Прямой и инверсный выходы первого частотного дискрш 1инатора 1 соединены с первыми входами соответственно элементов И 5 и б, вторые входы которых соединены с прямым выходом второго частотного дискршлинатора 2. Устройство работает следуивоно образе. Сигналы сравниваемьк частот f поступают на входы первого частотного дискриминатора 1, D-триггера 3 и N 4, перестраиваемого делителя на Первый частотный дискриминатор 1 вырабатывает сигналу соответству1ацкй знаку частотного рассогласования, следующим образом. Когда в реверсив-i ном счетчике 7 записи код 000/ ЕЗ-триггер 9 сигналом с второго, выхода дешифратора 8 устанавливается в ноль, а при коде 001 сигнсшом с первого выхода - в единицу. При коде реверсивного счетчика 7 Oil сигналом с третьего выхода дешифратора 8 состояние триггера 9 переписывается в D-триггер 10. ПРИ остальных значениях кода реверсивного счетчика состояние RS-триггера 9 и D-триггера 10 не изменяется. Таким.образом состояние D-триггера 10 определяется направлег нием счета реверсивного счётчика 7-. При выполнении условия fx f старите разряды реверсивного счетчика 7 работают в режиме вычитания и D-триггер 10 установится в нулевое состояние. При выполнении условия 7 старшие разряда реверсивного счетчика 7 рабоtaiOT в режиме сложения, а D-триггер 10 перейдет в единичное состояние. D-триггер 3 выполняет функции цифрового смесителяi Частота сигнала на вьоссде D-триггера 3 при выполнении условия 0,,5 равна . Этот сигнал разностной частоты поступает на вход сложения реверсивного счетчика 7 второго частотного дискриминатора 2. На вход вычитания, реверсивного счетчика 7 поступает сигнал с частотой fsT/N с выхода перестраиваемого делителя частоты 4. Второй частотный дискриминатор 2 работает аналогично первому и осуществляет сравнение частот ( %1/N. При выполнении условия () D-триггер 10 находится в еди- нйчном состоянии, а при условии (ff,-f) fgr/N в нулевом. Сигналы с выходов первого и второго частотных дискриминаторов поступа-. ют на элементы И 5,6. На выходах элементов И 5,6 ( Q соответственно) и на инверсном выходе (Qj) D-триггера 10 формируется трехразрядный двоичный код, соответствующий трем уровням передаточной характеристики частотного комгшратора. Соотношение частот c-f соответствует код 010 (Qf , Qnf Q) , соотношению y7:fg-j - 100 и соотнокод-О-оТГ - хх..,.Ч -о--Ует шеншо дт М Изменяя значение коэффициента деления М перестраиваемого делителя частоты 4, можно дискретно регулировать зоны не чувствительности частотного компаратора. Преиму1цеством частотного Компаратора является большая точность сравнения частоты входного сигнала относительно границ зоны допустимых значений за счет устранения ошибки дискретности сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный компаратор | 1983 |

|

SU1167719A2 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Самонастраивающийся генератор опережающих импульсов | 1989 |

|

SU1700533A1 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 2002 |

|

RU2252450C2 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2174705C2 |

| Электропривод постоянного тока | 1986 |

|

SU1661951A1 |

| Преобразователь временных параметров импульсных последовательностей | 1980 |

|

SU900445A1 |

| Устройство для измерения перемещений | 1986 |

|

SU1357695A1 |

| МНОГОКАНАЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2177637C2 |

| Устройство измерения времени ограничения тока транзисторными коммутаторами систем зажигания | 1989 |

|

SU1758279A1 |

ЧАСТОТНЫЙ КОМПАРАТОР, содержадий два частотных дискриминатора, Гпрямой выход первого кз которых сое- . дйнен с первым входом первого sneMeH та И, причем каждый из частотных дискриминаторов включает в себя счетчик импульсов, выходы которого соединены с входами дешифратора, первый выход которого соединен с S-входом RS-триггера, прямой выход которого.соединен с информационным входом D-триггёра, прямой и инверсный выходы которого являются соответственно прямым и инBepcHbsiyi выходами частотного дискриминатора, входами которого являются входы счетчика импульсов, о т л и f, 11 ч а ю щ и и с я тем, что, с целью увеличения точности сравнения частоты входного сигнала относительно зоны допустимых значений, в него введены перестраиваемый делитель частоты, второй элемент И и дополнительный D-триггер, выход которого соединен с первьал входом второго частотного дискриминатора, информационный вход - с первой входной шиной и первым входом первого частотного дискриминатора, инверсный выход которого соединен с первым входом второго элемента И, второй вход - с второй входной шиной, тактовым входом D-тригге ра и входом перестраиваемого делителя частоты, выход которого соединен с § вторым входом второго частотного диск (Л риминатора, :прямой вьзход - с вторыми входами первого и второго элементов И, при Зтом второй и третий выходы девшфратора в каждом частотном дискриминаторе соединены соответственно с Е-входомЕ8-триггера и тактовьюв входом D-триггера, данного частотного дискриминатора, а счетчики импуль сов выполнены реверсивными.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Частотное пороговое устройство | 1976 |

|

SU629511A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Частотный компаратор | 1975 |

|

SU570193A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-06-15—Публикация

1981-01-23—Подача