Фиг.1

Изобретение относится к цифровой измерительной технике и может быть использовано в системах частотно-фазовой автоподстройки частот, в частности в синтезаторах частот.

По основному авт. св. № 1023630 известен частотный компаратор, содержащий первый частотный дискриминатор, первый вход которого подключен к информационному входу D-триггера и первой входной шине, второй вход, - к тактовому входу D-триггера, входу перестраиваемого делителя частоты и второй входной шине, прямой и инверсный выходы - к первым входам соответственно первого и второго элементов И, выходы которых подключены соответственно к первой и второй выходным шинам, и второй частотный дискриминатор, первый и второй входы которого подключены к выходам D-триггера и перестраиваемого делителя частоты, прямой выход - к вторым входам элементов- И, инверсный выход - к третьей выходной шине, при этом каждый частотный дискриминатор состоит из трехразрядного реверсивного счетчика импульсов, выходы разрядов которого соединены с входами дешифратора, первый, второй и третий выходы которого соединены соответственно с S-, R-входами RS-триггера и тактовым входом D-триггера, информационный вход которого соединен с прямым выходом RS-триггера, а прямой и инверсный выходы D-триггера являются, соответственно, прямым и инверсным выходами частотного дискриминатора, первым и вторым входами которого являются соответственно входы сложения и вычитания трехразрядного реверсивного счетчика импульсов 1.

Недостатком данного устройства является ограниченный диапазон изменения частоты измеряемого сигнала относительно частоты эталонного сигнала far. Это ограничение определяется принципом работы D-триггера в качестве разностного смесителя частот

и равно 0,,5. При частоте изметэг

ряемого сигнала ,5Гэт и {х.-С.О,5Гэт частота выходного сигнала D-триггера будет равна абсолютной величине разности частот измеряемого сигнала и ближайшей гармоники эталонного сигнала т. е. /nfsr -L/, где п 1,2,3... - номер гармоники. В этом случае при некоторых значениях частоты fx частота сигнала на выходе D-триггера окажется меньше величины зоны допустимых значений и будет произведена ложная оценка соотношения частот измеряемого и эталонного сигналов.

Цель изобретения - увеличение допустимого диапазона изменения частоты измеряемого сигнала относительно частоты эталонного сигнала.

Поставленная цель достигается тем, что в частотный компаратор введены два делителя частоты на два, два делителя частоты на три, третий и четвертый частотные дискриминатора, первый вход последнего из которых соединен с вторым входом первого частотного дискриминатора и выходом первого делителя частоты на три, второй вход - с первым входом третьего частотного дискриминатора, входом первого делителя частоты на два, выход которого подключен к первому входу

0 первого частотного дискриминатора, и выходом второго делителя частоты на три, вход которого подключен к первой входной шине, и элемент ИЛИ, выход которого соединен с третьим входом второго частотного дискриминатора, первый и второй входы - с прямыми выходами соответственно третьего и четвертого частотных дискриминаторов, второй вход первого из которых соединен с входом первого делителя частоты на три и выходом второго делителя частоты на два,

0 вход которого подключен к второй входной шине.

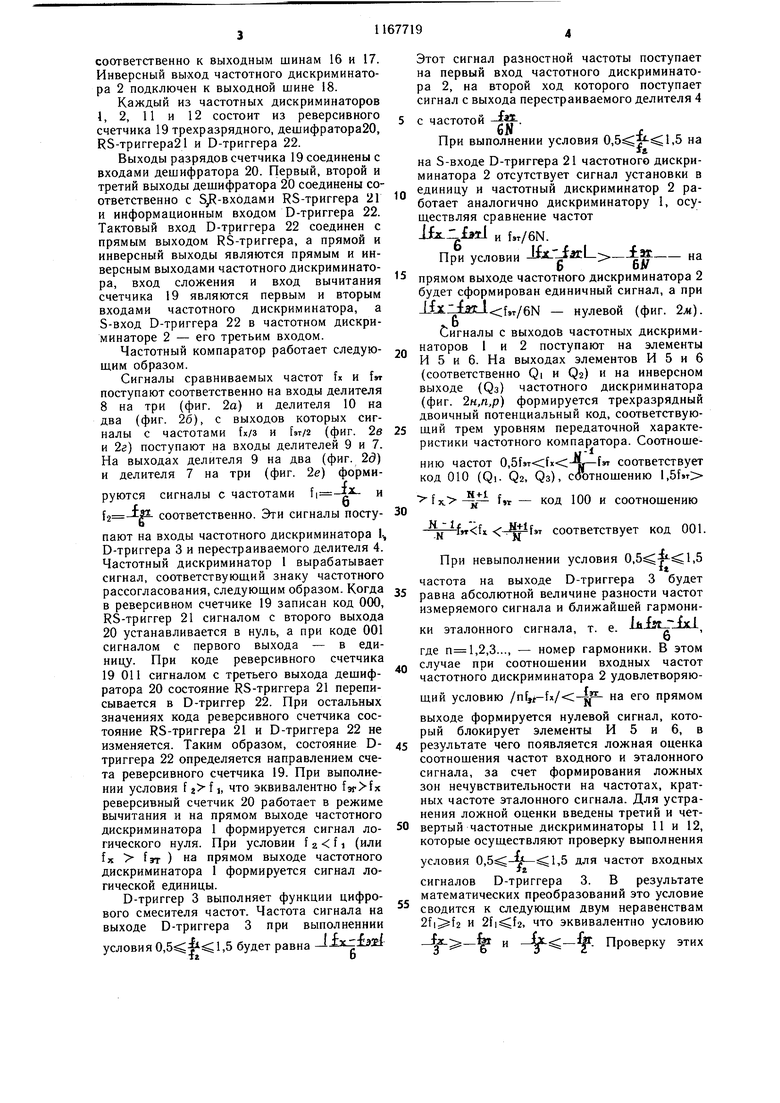

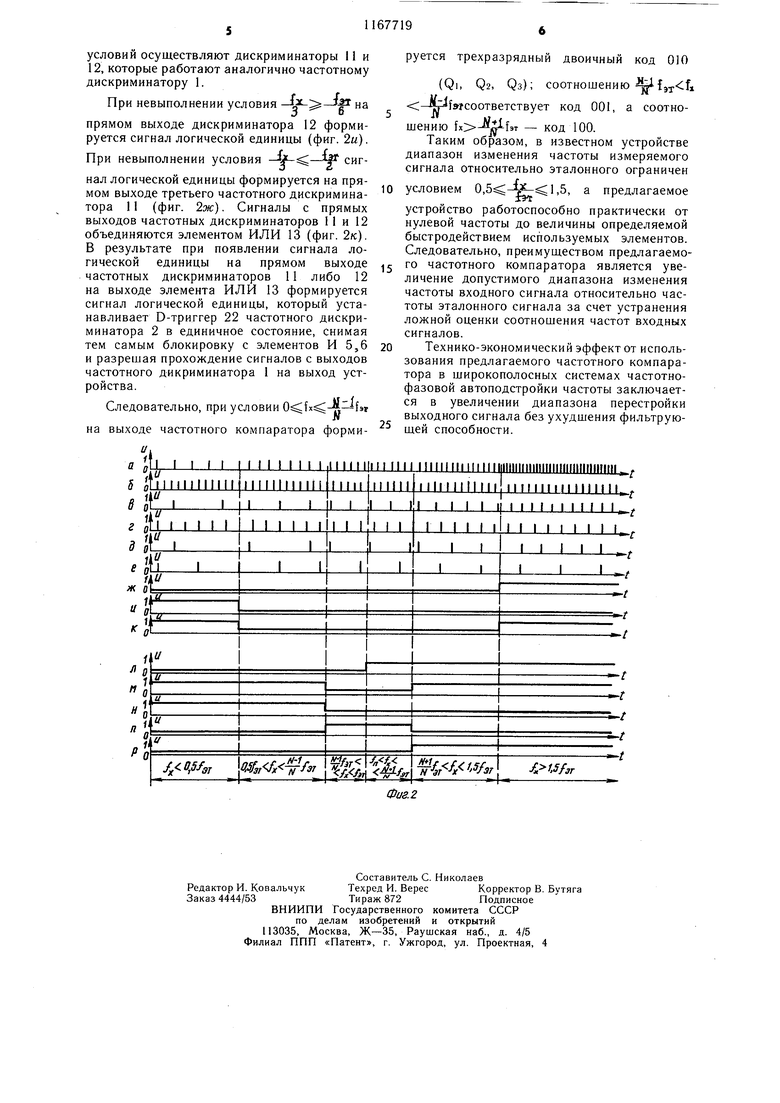

На фиг. 1 приведена функциональная схема частотного компаратора; на фиг. 2 - временные диаграммы, поясняющие его работу.

5 Частотный компаратор содержит первый и второй частотные дискриминаторы 1 и 2, D-триггер 3, перестраиваемый делитель 4 частоты (на N), первый и второй элементы И 5 и 6, первый и второй делители 7 и 8 частоты на три, первый

0 и второй делители 9 и 10 частоты на два, третий и четвертый частотные дискриминаторы 11 и 12, элемент ИЛИ 13, первую и вторую входные шины 14 и 15, первую, вторую и третью выходные шины 16-18. Первый вход частотного дискриминатора

1 соединен с информационным входом D-триггера 3 и выходом делителя 9, второй вход - с выходом делителя 7, тактовым входом Dтpиггepa 3, входом перестраиваемого делителя 4 и первым входом

Q частотного дискриминатора 12. Первый вход частотного дискриминатора 2 соединен с выходом D-триггера 3, вгорой вход - с выходом перестраиваемого делителя 4. Первый вход частотного дискриминатора 11 соединен с вторым входом частотного дискриминатора 12, входом делителя 9 и выходом делителя 8, второй вход - с входом делителя 7 и выходом делителя 10. Вход делителя 8 подкелючен к входной шине 15. Первый вход элемента ИЛИ 13 соединен с прямым выходом частотного дискриминатора 11, второй вход - с прямым выходом частотного дискриминатора 12, выходс третьим входом частотного дискриминатора 2. Прямой и инверсный выходы частотного дискриминатора 1 соединены с первыми

j входами соответственно элементов И 5 и 6. Прямой выход частотного дискриминатора 2 соединен с вторыми входами элементов И 5 и 6, выходы которых подключены соответственно к выходным шинам 16 и 17. Инверсный выход частотного дискриминатора 2 подключен к выходной шине 18. Каждый из частотных дискриминаторов 1, 2, 11 и 12 состоит из реверсивного счетчика 19 трехразрядного, деи1ифратора20, Н5-триггера21 и D-триггера 22. Выходы разрядов счетчика 19 соединены с входами дешифратора 20. Первый, второй и третий выходы дешифратора 20 соединены соответственно с S -входами RS-триггера 21 и информационным входом D-триггера 22. Тактовый вход D-триггера 22 соединен с прямым выходом RS-триггера, а прямой и инверсный выходы являются прямым и инверсным выходами частотного дискриминатора, вход сложения и вход вычитания счетчика 19 являются первым и вторым входами частотного дискриминатора, а S-вход D-триггера 22 в частотном дискриминаторе 2 - его третьим входом. Частотный компаратор работает следуюшим образом. Сигналы сравниваемых частот fx и Гэт поступают соответственно на входы делителя 8 на три (фиг. 2а) и делителя 10 на два (фиг. 26), с выходов которых сигналы с частотами fx/з и fsr/z (фиг. 2в и 2г) поступают на входы делителей 9 и 7. На выходах делителя 9 на два (фиг. 2(3) и делителя 7 на три (фиг. 2е) формируются сигналы с частотами и JO .;,- 12. соответственно. Эти сигналы поступают на входы частотного дискриминатора Ь, D-триггера 3 и перестраиваемого делителя 4. Частотный дискриминатор 1 вырабатывает сигнал, соответствуюш.ий знаку частотного рассогласования, следуюшим образом. Когда в реверсивном счетчике 19 записан код 000, RS-триггер 21 сигналом с второго выхода 20 устанавливается в нуль, а при коде 001 сигналом с первого выхода - в единицу. При коде реверсивного счетчика 19 011 сигналом с третьего выхода дешифратора 20 состояние RS-триггера 21 переписывается в D-триггер 22. При остальных значениях кода реверсивного счетчика состояние RS-триггера 21 и D-триггера 22 не изменяется. Таким образом, состояние Dтриггера 22 определяется направлением счета реверсивного счетчика 19. При выполнении условия f г , что эквивалентно реверсивный счетчик 20 работает в режиме вычитания и на прямом выходе частотного дискриминатора I формируется сигнал логического нуля. При условии f а f i (или fx fyr ) нз прямом выходе частотного дискриминатора 1 формируется сигнал логической единицы. D-триггер 3 выполняет функции цифрового смесителя частот. Частота сигнала на выходе D-триггера 3 при выполненнии условия 0, 1,5 будет равна -1-Ьсг±521 тгD Этот сигнал разностной частоты поступает на первый вход частотного дискриминатора 2, на второй ход которого поступает сигнал с выхода перестраиваемого делителя 4 с частотой -. 6Nе При выполнении условия 0,,5 на на S-входе D-триггера 21 частотного дискриминатора 2 отсутствует сигнал установки в единицу и частотный дискриминатор 2 работает аналогично дискриминатору 1, осуществляя сравнение частот -ibsL-btl и bT/6N. При условии оОа прямом выходе частотного дискриминатора 2 будет сформирован единичный сигнал, а при ± х: Ш г„/6Ы - нулевой (фиг. 2л). Сигналы с выходов частотных дискриминаторов 1 и 2 поступают на элементы И 5 и 6. На выходах элементов И 5 и 6 (соответственно Qi и Qa) и на инверсном выходе (Qa) частотного дискриминатора (фиг. 2н,п,р) формируется трехразрядный двоичный потенциальный код, соответствующий трем уровням передаточной характеристики частотного компаратора. Соотношению частот 0,5f9T cfx ;-4;.-f соответствует код 010 (Qi. Q2, Qs), соотношению l, -5,f f код 100 и соотношению I Х -ir- Ьт соответствует код 001. При невыполнении условия 0,,5 частота на выходе D-триггера 3 будет равна абсолютной величине разности частот измеряемого сигнала и ближайшей гармоники эталонного сигнала, т. е. ib-lit -ixi где п 1,2,3..., - номер гармоники. В этом случае при соотношении входных частот частотного дискриминатора 2 удовлетворяющий условию /nfjt-fx/ -4p- на его прямом выходе формируется нулевой сигнал, который блокирует элементы И 5 и 6, в результате чего появляется ложная оценка соотношения частот входного и эталонного сигнала, за счет формирования ложных зон нечувствительности на частотах, кратных частоте эталонного сигнала. Для устранения ложной оценки введены третий и четвертый частотные дискриминаторы 11 и 12, которые осуществляют проверку выполнения условия 0,,5 для частот входных сигналов D-триггера 3. В результате математических преобразований это условие сводится к следующим двум неравенствам и , что эквивалентно условию и Проверку этих

условий осуществляют дискриминаторы 11 и 12, которые работают аналогично частотному дискриминатору 1.

При невыполнении условия -q д

прямом выходе дискриминатора 12 формируется сигнал логической единицы (фиг. 2и).

При невыполнении условия сигнал логической единицы формируется на прямом выходе третьего частотного дискриминатора 11 (фиг. 2ж). Сигналы с прямых выходов частотных дискриминаторов 1 1 и 12 объединяются элементом ИЛИ 13 (фиг. 2/с). В результате при появлении сигнала логической единицы на прямом выходе частотных дискриминаторов 11 либо 12 на выходе элемента ИЛИ 13 формируется сигнал логической единицы, который устанавливает D-триггер 22 частотного дискриминатора 2 в единичное состояние, снимая тем самым блокировку с элементов И 5,6 и разрешая прохождение сигналов с выходов частотного дикриминатора 1 на выход устройства.

Следовательно, при условии O fx - -lifsr

li

на выходе частотного компаратора формируется трехразрядный двоичный код 010

(Qi, Q2, Qs); соотношению {33.fi -«р Гмсоответствует код 001, а соотношению - код 100.

Таким образом, в известном устройстве диапазон изменения частоты измеряемого сигнала относительно эталонного ограничен

условием 0,5 Д 1,5, а предлагаемое

устройство работоспособно практически от нулевой частоты до величины определяемой быстродействием используемых элементов. Следовательно, преимуш.еством предлагаемого частотного компаратора является увеличение допустимого диапазона изменения частоты входного сигнала относительно частоты эталонного сигнала за счет устранения ложной оценки соотношения частот входных сигналов.

Технико-экономический эффект от использования предлагаемого частотного компаратора в широкополосных системах частотнофазовой автоподстройки частоты заключается в увеличении диапазона перестройки выходного сигнала без ухудшения фильтрующей способности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный компаратор | 1981 |

|

SU1023630A1 |

| Самонастраивающийся генератор опережающих импульсов | 1989 |

|

SU1700533A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Преобразователь частота-код | 1987 |

|

SU1427571A2 |

| Электропривод постоянного тока | 1986 |

|

SU1661951A1 |

| Устройство для определения первой разности частотно-импульсного сигнала | 1982 |

|

SU1043675A1 |

| Устройство измерения времени ограничения тока транзисторными коммутаторами систем зажигания | 1989 |

|

SU1758279A1 |

| Устройство для измерения частоты и периода | 1991 |

|

SU1824592A1 |

| Цифровой дискриминатор средней частоты | 1985 |

|

SU1293835A1 |

| Преобразователь частота-код | 1981 |

|

SU970681A1 |

ЧАСТОТНЫЙ КОМПАРАТОР по авт. св. № 1023630, отличающийся тем, что с целью увеличения допустимого изменения частоты измеряемого сигнала относительно частоты эталонного сигнала, в него введены два делителя частоты на два, два делителя частоты на три, третий и четвертый частотные дискриминаторы, первый вход последнего из которых соединен h. 1 с вторым входом первого частотного дискриминатора и выходом первого делителя частоты на три, второй вход - с первым входом третьего частотного дискриминатора, входом первого делителя частоты на два, выход которого подключен к первому входу первого частотного дискриминатора, и выходом второго делителя частоты на три, вход которого подключен к первой входной шине, и элемент ИЛИ, выход которого соединен с третьим входом второго частотного дискриминатора, первый и второй входы - с прямыми выходами соответственно третьего и четвертого частотных дискриминаторов, второй вход первого из которых соединен с входом первого делителя частоты на три и выходом второго делителя частоты на два, вход которого подключен к второй входной шине.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Частотный компаратор | 1981 |

|

SU1023630A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-07-15—Публикация

1983-11-01—Подача