(Л

Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1981 |

|

SU1273831A1 |

| Устройство временной привязки к экстремальным значениям гармонического сигнала | 1978 |

|

SU789855A1 |

| Цифровой фазометр | 1983 |

|

SU1155957A1 |

| Цифровой корреляционный фазометр | 1981 |

|

SU1056077A1 |

| Измеритель разности фаз | 1990 |

|

SU1800382A1 |

| Цифровой фазометр | 1976 |

|

SU573772A1 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

| Цифровой фазометр | 1980 |

|

SU938197A1 |

| Цифровой фазометр | 1982 |

|

SU1075187A1 |

| Цифровой фазометр с постоянным измерительным временем | 1981 |

|

SU1269035A1 |

1. ЦИФРОВОЙ ФАЗОТ1ЕТР НО авт. св. 573772, о т л и ч а ю и и и с я тем, что, с целью повышения точности измерения, в каждый качал ф&зсметра введен блок коррекции, соединенный первь входом с выходом младшего разряда счетчика, вторым входом.- с входом Запись регистра памяти, третьим входом - с выходом блока сравнения кодов, четвертым входом - с выходом генератора счетных импульсов и пятым входом .- с входом Пуск триггера, первый и второй выходы блока коррекции соединены с дополнительными входамиэлектронного ключа. .

to

а: оо 00

Изобретение относится к радиоизмерительной технике.

По .основному авт. св. № 573772 известен цифровой фазометр, содержащий в каждом канале регистр памяти и последовательно соединенные формирующее устройство, счетчик, блок сравнения кодов и триггер, второй вход которого соединен с выходом формирующего устройства, а выход с входом записи регистра памяти, выходы разрядов которого подключены к блоку сравнения кодов, а вхсэды к выходам разрядов счетчика, общие для обоих каналов и последовательно соединенные генератор счетных импульсов, связанныйСО счетньп 1и входами счетчиков, времязадающий блок, подключенный выходом к-входам Пуск триггеров, электронныйключ, связанный входами с генератором счетных импульсов, времязадающим блоком и выходами блоков сравнения кодов, и «регистрирующий счетчик.

пятым входом блока коррек-ции., а вьГходом - с входом Сброс одноразрядг ного регистра , информационный вход и вход записи которого соответствуют первому и вт.орому входам блока коррекции.

3« Фазометр по п. 1, отлич аю щ и и с я тем, что блок коррекции содержит элемент задержки, элемент ИЛИ, элемент совпадений, эЛемент переноса, триггер-и одноразрядный регистр памяти, информационный вход и вход записи которого соответствует первому и второму входам блока коррекции, а-его инверсный выход является первым выходом бло.ка коррекции, вход Сброс одноразрядного регистра памяти соединен с выходом элемента ИЛИ, а его прямой выход г с первым входом элемента совпадений, второй и третий входы которого являются соответственно третьим и четвертым входами блока коррекции, выход элемента совпадений подключен к первым входам триггера и элемента ИЛИ, второй вход которого является пятым входом блока коррекции-, выход триггера соединен с первым входсм элемента переноса, выход которого является вторым выходом блока коррекции, а вторые входы триггера и элемента переноса подключены к выходу элемента задержки, вход которого соединен с третьим входом элемента совпадений.

В данном фазометре преобразование сдвига фаз в эквивалентные интервалы времени осуществляется по переходам гармонического сигнала через максимальные (минимальные) значения, что определяет повышенную помехоустойчивость фазометра к воздействию внутренних и внешних широкополосных шумов. Моменты перехода фиксируются путем временной привязки к серединам соответствующих полуволн сформированного пигнала. этом в каждом периоде сигнала текущий код счетчика сравнивается с помощью элемента сравнения коДов с кодом, хранимым в регистре

Т1амяти и .соответствующим,половине длительности полуволны сигнала в предыдущем периоде 1 .

Однако при записи в регистр памяти нечетных значений выходного кода

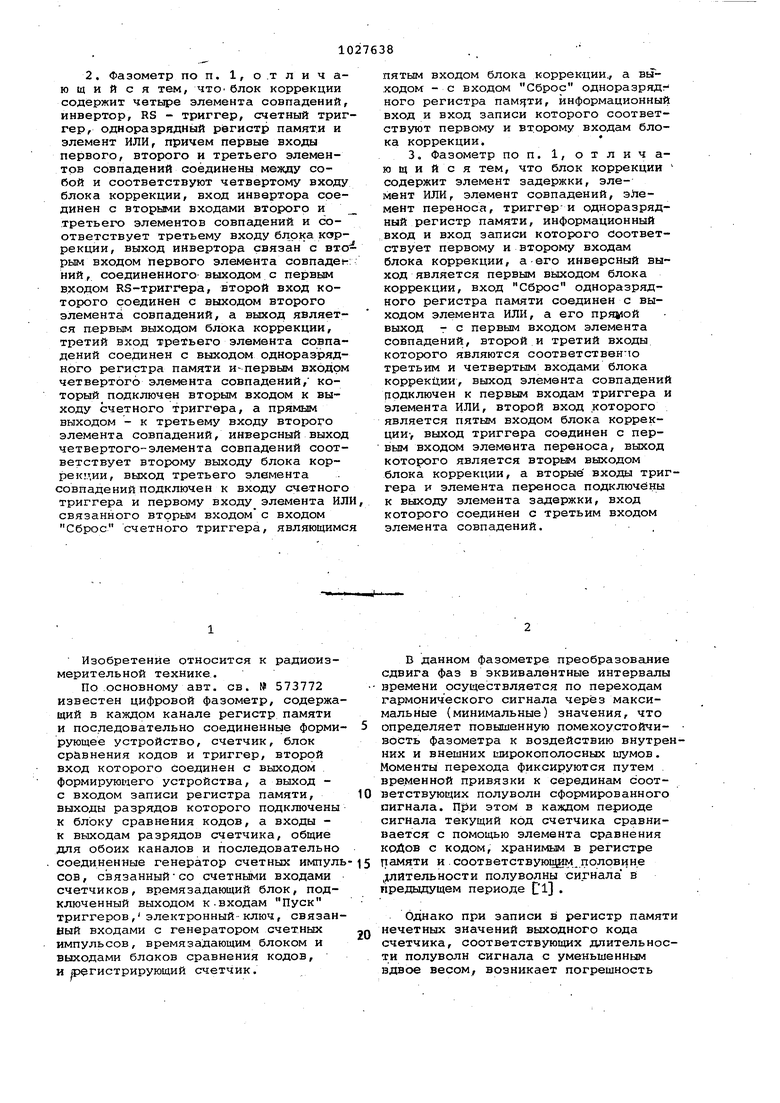

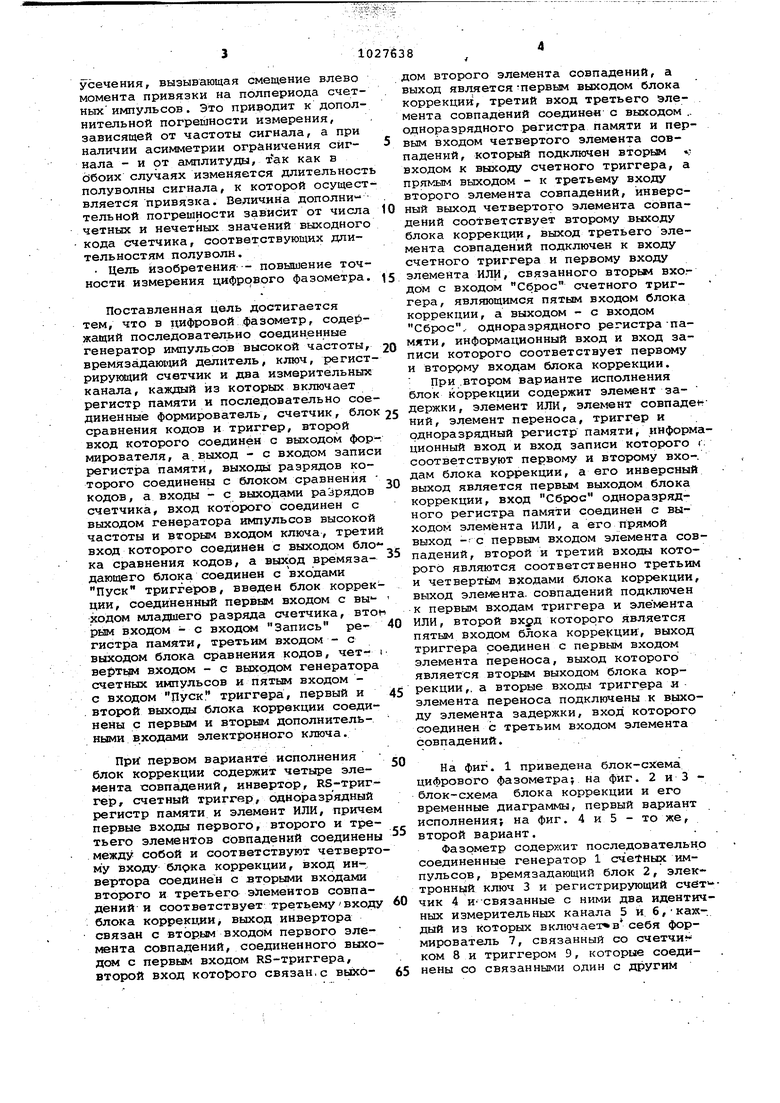

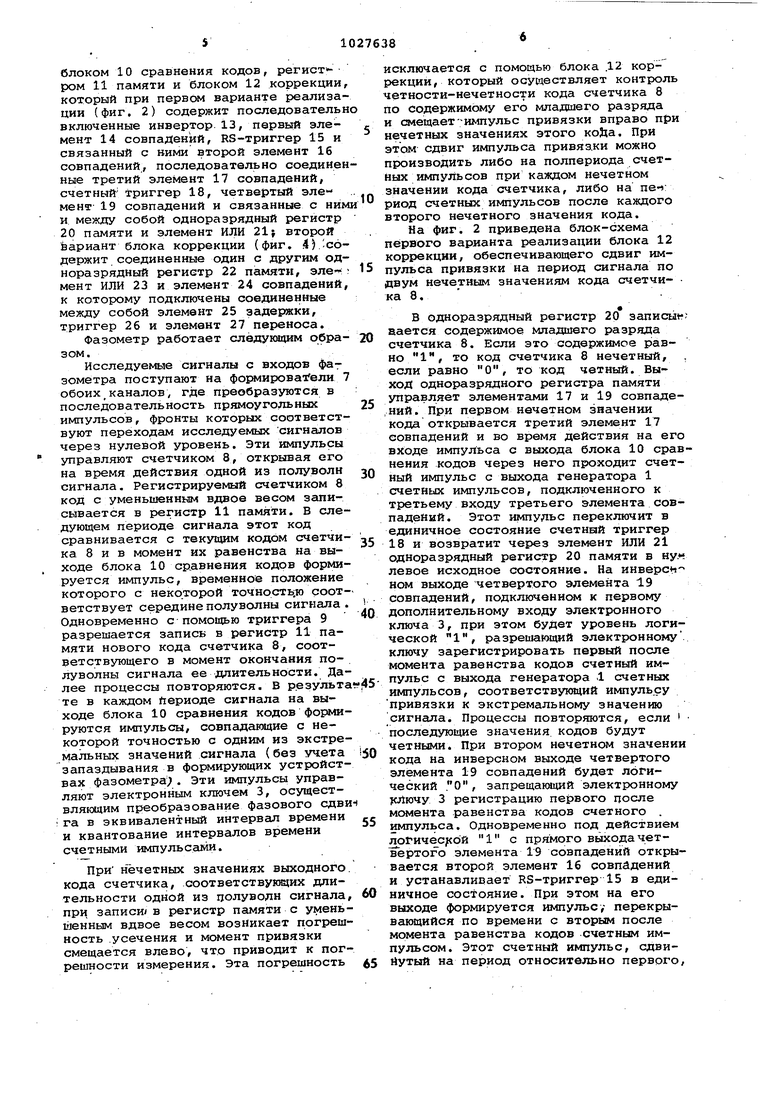

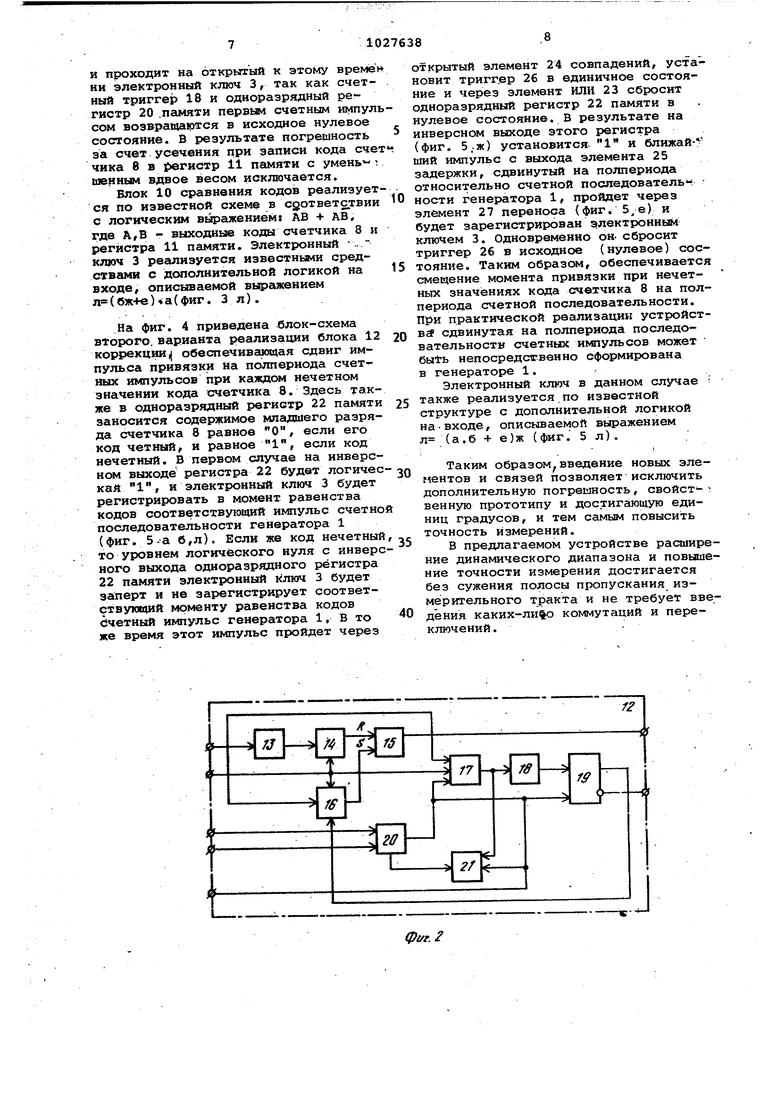

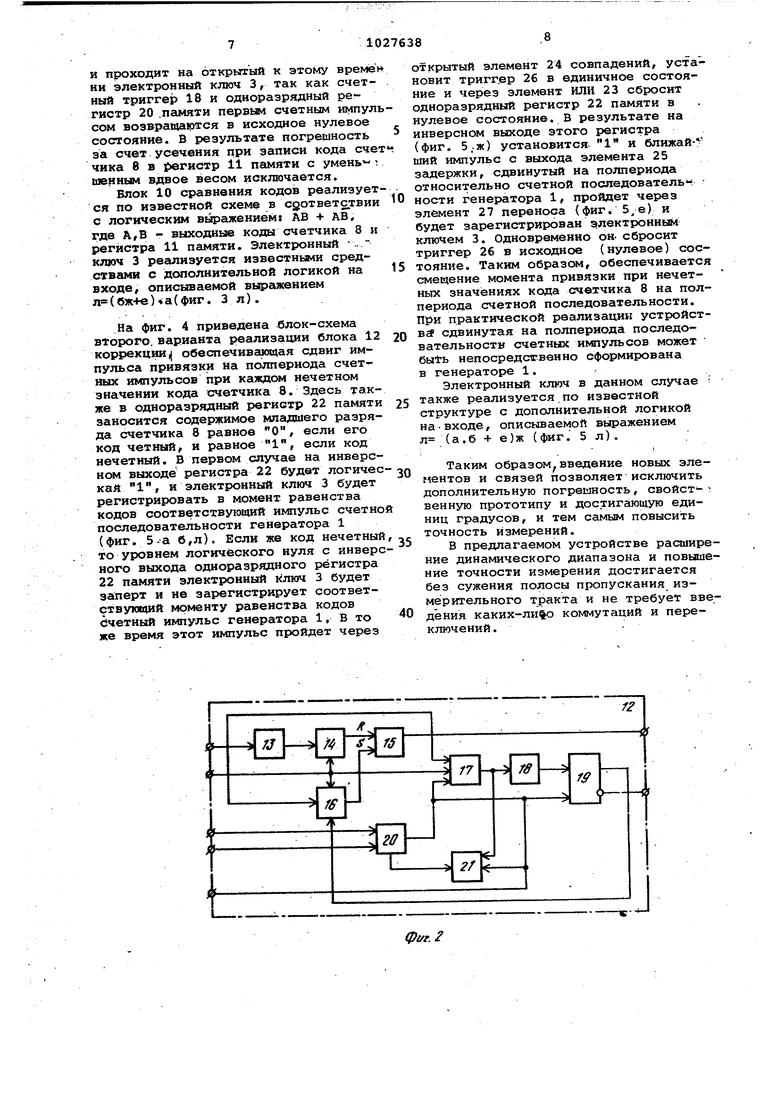

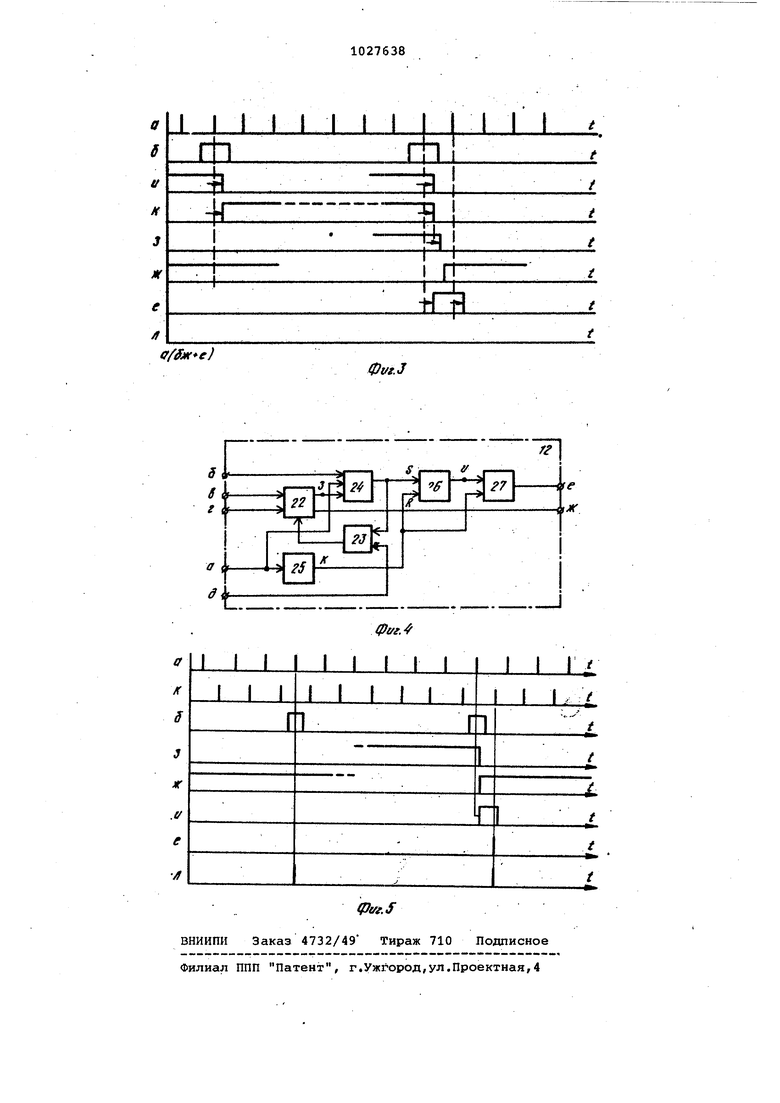

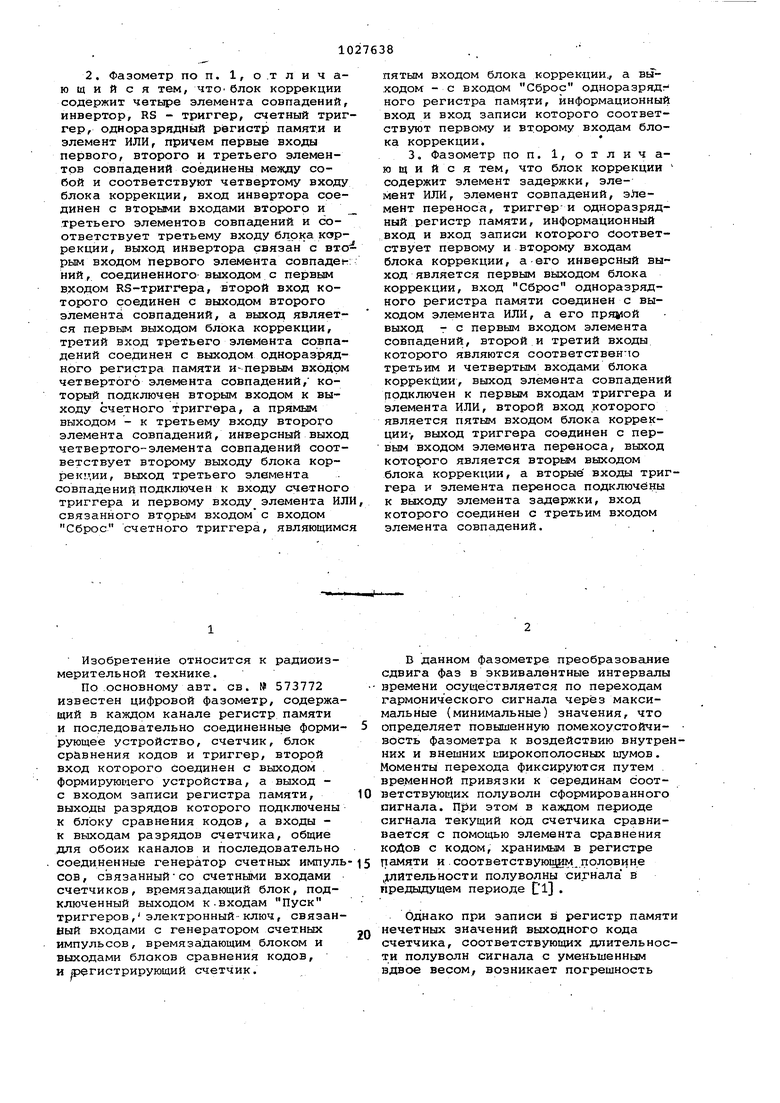

счетчика, соответствующих длительности полуволн сигнала с уменьшенным вдвое весом, возникает погрешность усечения, вызывающая смещение влево момента привязки на полпериода счетных импульсов . Это приводит к дополнительной погрешности измерения, зависящей от частоты сигнала, а при наличии асимметрии ограничения сигнала - и от амплитуды, как в дбоих случаях изменяется длительност полуволны сигнала, к которой осущест вляется привязка. Величина дополни- тельной погрешности зависит от числа четных и нечетных значений выходного кода счетчика, соответствующих длительностям полуволн. Цель изобретения-- повышение точности измерения цифрового фазометра. Поставленная цель достигается тем, что в цифровой;фазометр, содержащий последовательно соединенные генератор импульсов высокой частоты, времязадаюрлий делитель, ключ, регист рирующий счетчик и два измерительных канала, каждый из которых включает регистр памяти и последовательно сое диненные формирователь, счетчик, бло сравнения кодов и триггер, второй вход которого соединен с выходом фор мирователя, а.выход - с входом запис регистра памяти, выходы разрядов которого соединены с блоком сравнения кодов, а входы - с выходами разрядов счетчика, вход которого соединен с выходом генератора импульсов высокой частоты и вторым входом ключа, трети вход которого соединен с выходом бло ка сравнения кодов, а выход времязадающего блока соединен с входами Пуск триггеров, введен блок коррек ции, соединенный первым входом с выходетл младшего разряда счетчика, BTo рым входом - с ВХОДСЖ4 Запись регистра памяти, третьим входом - с выходом блока сравнения кодов, четBe TtJM входом - с выходом генератора счетных импульсов и пятым входом с входом Пуск триггера, первый и второй выходы блока коррекции соединены с первым и вторыгл дополнительными входами электронного ключа. nprf первом варианте исполнения блок коррекции содержит четыре элемента совпадений, инвертор, RS-триггер, счетный триггер, одноразрядный регистр памяти и элемент ИЛИ, причем первые входы первого, второго и третьего элементов совпадений соединены между собой и соответствуют четверто му входу блрка коррекции, вход инвертора соединен с вторыми входами второго и третьего элементов совпадений- и соответствует третьемуВХОДУ блока коррекции, выход инвертора связан с вторым входом первого элемента совпадений, соединенного выходом с первым входом RS-триггера, второй вход которого связан, с вьйсодом второго элемента совпадений, а выход является-первым выходом блока коррекций, третий вход третьего элемента совпадений соединен с выходом .. одноразрядного регистра памяти и первым входом четвертого элемента совпадений, который подключен вторым «: входом к выходу счетного триггера, а прямым выходом - к третьему входу второго элемента совпадений, инверсный выход четвертого элемента совпадений соответствует второму выходу блока коррекции, выход третьего элемента совпадений подключен к входу счетного триггера и первому входу элемента ИЛИ, связанного вторьм вхо,дом с входом Сброс счетного триггера, являющимся пятым входом блока коррекции, а выходом - с входом Сброс, одноразрядного регистра памяти, информационный вход и вход записи которого соответствует первсму и второму входам блока коррекции. - При .втором варианте исполнения блок коррекции содержит элемент задержки, элемент ИЛИ, элемент совпаде тНИИ, элемент переноса, триггер и одноразрядный регистр памяти, информационный вход и вход записи которого с соответствуют первому и второму вхо-. дам блока коррекции, а его инверсный выход является первым выходом блока коррекции, вход Сброс одноразрядного регистра памяти соединен с выходом элемента ИЛИ, а его прямой выход --с первым входом элемента совпадений, второй и третий входы которого являются соответственно третьим и четвертым входами блока коррекции, выход элег« нта. совпадений подключен к первым входам триггера и элемента ИЛИ, второй ВХ2Д которого является пятым входом блока коррекции, выход триггера соединен с первым входом элемента переноса, выход которого является вторым выходом блока коррекции,, а вторые входы триггера и элемента переноса подключены к выходу элемента задержки, вход которого соединен с третьим входом элемента совпадений. На фиг. 1 приведена блок-схема цифрового фазометра; на фиг. 2 и 3 блок-схема блока коррекции и его временные диаграммы, первый вариант исполнения; на фиг. 4 и 5 - то же, второй вариант. . Фазометр содержит последовательно соединенные генератор 1 счетных импульсов, времязадающий блок 2, электронный ключ 3 и регистрирующий счбт -чик 4 И-связанные с ними два идентичных измерительных канала 5 и. 6,каж-. дый из которых включает в себя формирователь 7, связанный со счетчи« ком 8 и триггером 9, которые соединены со связанными один с другим блоком 10 сравнения кодов, регист ром 11 памяти и блоком 12 коррекции который при первом варианте реализа ции (фиг. 2) содержит последователь включенные инвертор 13, первый элемент 14 совпадений, RS-триггер 15 и связанный с ними второй элемент 16 совпадений, последовательно соедине ные третий элемент 17 совпадений, счетный триггер 18, четвертый мент 19 совпадений и связанные с ним и между собой одноразрядный регистр 20 памяти и элемент ИЛИ 21j второй вариант блока коррекции (фиг. 4).со держит соединенные один с другим од норазрядный регистр 22 памяти, эле мент ИЛИ 23 и элемент 24 совпадений к которому подключены соединенные между собой элемент 25 задержки, триггер 26 и элемент 27 переноса. Фазометр работает следующим образом. Исследуемые сигналы с входов фат зометра поступают на формирователи 7 обоих каналов, где преобразуются в последовательность прямоугольных импульсов, фронты которых соответствуют переходам исследуемых сигналов через нулевой уровень. Эти импульсы 5травляют счетчиком 8, открывая его на время действия одной из полуволн сигнала. Регистрируемый счетчиком 8 код с уменьшенным вдвое весом записывается в регистр 11 памяти. В следующем периоде сигнала этот код сравнивается с текущим кодом счетчика 8 и в момент их равенства на выходе блока 10 сравнения кодов формируется импульс, временное положение которого с некоторой точность;ю соответствует середине полуволны сигнала. Одновременно с-помощью триггера 9 разрешается запись в регистр 11 памяти нового кода счетчика 8, соответствующего в момент окончания полуволны сигнала ее длительности. Далее процессы повторяются. В результа те в каждом йериоде сигнала на выходе блока 10 сравнения кодов фоЕлетруются импульсы, совпадакядие с некоторой точностью с одним из экстремальных значений сигнала (без учета запаздывания в формирующих устройствах фазометра. Эти импульсы управляют электронным ключем 3, осуществляющим преобразование фазового cдви га в эквивалентный интервал времени и квантование интервалов времени счетными импульсгдаи. При нёчетных значениях выходного кода счетчика, соответствующих длительности одной из полуволн сигнала, при, записи в регистр памяти с уменьшенным вдвое весом возникает погрешность усечения и момент привязки смещается влево, что приводит к погрешности измерения. Эта погрешность исключается с помощью блока .12 коррекции, который осуществляет контроль четности-нечетности кода счетчика 8 по содержимому его младшего разряда и смещает-импульс привязки вправо при нечетных значениях этого . При этом сдвиг импульса привязки можно производить либо на полпериода счетных импульсов при каждом нечетном значении кода счетчика, либо на печ: риод счетных импульсов после каждого второго нечетного значения кода. На фиг. 2 приведена блок-схема первого варианта реализации блока 12 коррекции, обеспечивающего сдвиг импульса привязки на период сигнала по двум нечетным значениям кода счетчи- ка 8. В одноразрядный регистр 20 записы - аается содержимое младшего разряда счетчика 8. Если это содержимое равно 1, то код счетчика 8 нечетный, если равно О, то код четный. Выход одноразрядного регистра памяти управляет элементами 17 и 19 совпаде,ний. При первом нечетном значении кода открывается третий элемент 17 совпадений и во время действия на его входе импульса с выхода блока 10 сравнения кодов через него проходит счетный импульс с выхода генератора 1 счетных импульсов, подключенного к третьему входу третьего элемента совпадений. Этот импудьс переключит в единичное состояние счетный триггер 18 и возвратит через элемент ИЛИ 21 одноразрядный регистр 20 памяти в нул левое исходное состояние. На инверсн ном выходе четвертого элемента 19 совпадений, подключенном к первому дополнительному входу электронного ключа 3, при этом будет уровень логической 1, разрешающий электронному ключу зарегистрировать первый после момента равенства кодов счетный импульс с выхода генератора 1 счетных импульсов, соответствующий импульсу привязки к экстремальному значению сигнала. Процессы повторяются, если i последующие значения, кодов будут четными. При втором нечетном значении кода на инверсном выходе четвертого элемента 19 совпадений будет логический О, запрещающий электронному ключу 3 регистрацию первого после момента равенства кодов счетного импульса. Одновременно под действием лрГичес)кой 1 с прямого выхода четвертого элемента 19 совпадений открывается второй элемент 16 совпадений и устанавливает RS-триггер 15 в единичное состояние. При этом на его выходе формируется импульс,- перекрывающийся по времени с вторым после момента равенства кодов счетным импульсом. Этот счетный импульс, сдвийутый на период относительно первого, И проходит на открьггый к этому време ни электронный ключ 3, так как счетный триггер 18 и одноразрядный регистр 20 .памяти первьам счетным импул сом возвраща ртся в исходное нулевое состояние. В результате погрешность за счет усечения при записи кода сче чика в в регистр 11 памяти с умень -1 шейным вдвое весом исключается. Блок 10 сравнения кодов реализует ся по известной схеме в сдответствии с логическим выражением АВ + АВ, где А,В - выходные коды счетчика 8 и регистра 11 памяти. Электронный .. ключ 3 реализуется известными средствами с дополнительной логикой на входе, описываемой выражением л(бж+е)а(фиг. 3л). На фиг. 4 приведена блок-схема второго, варианта реализации блока 12 коррекции обеспечивающая сдвиг импульса привязки на полпериода счетных импульсов при каждом нечетном значении кода счетчика 8, Здесь также в одноразрядный регистр 22 памяти заносится содержимое младшего разряда счетчика 8 равное О, если его код четный, и равное 1, если код нечетный. В первом случае на инверсном выходе регистра 22 будет логичес кай 1, и электронный ключ 3 Судет регистрировать в момент равенства кодов соответствующий импульс счетно последовательности генератора 1 (фиг. 5-а б,л). Если же код нечетный то уровнем логического нуля с инверс ного выхода одноразрядного регистра 22 памяти электронный 3 будет заперт и не зарегистрирует соответствушций моменту равенства кодов Учетный импульс генератора 1, В то же время этот импульс пройдет через открытый элемент 24 совпадений, установит триггер 26 в единичное состояние и через элемент ИЛИ 23 сбросит одноразрядный регистр 22 памяти в нулевое состояние. В результате на инверсном выходе этого регистра (фиг. 5,-ж) установится- 1 и ближай- ший импульс с выхода элемента 25 задержки, сдвинутый на прлпериода относительно счетной последователь - ности генератора 1, пройдет через элемент 27 переноса (фиг. 5,е) и будет зарегистрирован электронным ключем 3. Одновременно он. сбросит триггер 26 в исходное (нулевое) состояние. Таким образом, обеспечивается смещение момента привязки при нечетных значениях кода счетчика 8 на полпериода счетной последовательности. При практической реализации устройстBcf сдвинутая на полпериода последовательность счетных икетульсов может бы1ь непосредственно сформирована в генераторе 1. Электронный ключ в данном случае также реализуется по известной структуре с дополнительной логикой на-входе, описываемой выражением л (а.б + е)ж (фиг. 5л), Таким образом,введение новых элементов и связей позволяет исключить дополнительную погрешность, свойственную прототипу и достигающую единиц градусов, и тем самым повысить точность измерений. В предлагаемом устройстве расширение динамического диапазона и повышение точности измерения достигается без сужения полосы пропускания измерительного тракта и не требует введения каких- ли%о коммутаций и переключений.

CffffjK e)

фуг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой фазометр | 1976 |

|

SU573772A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-07-07—Публикация

1982-03-12—Подача