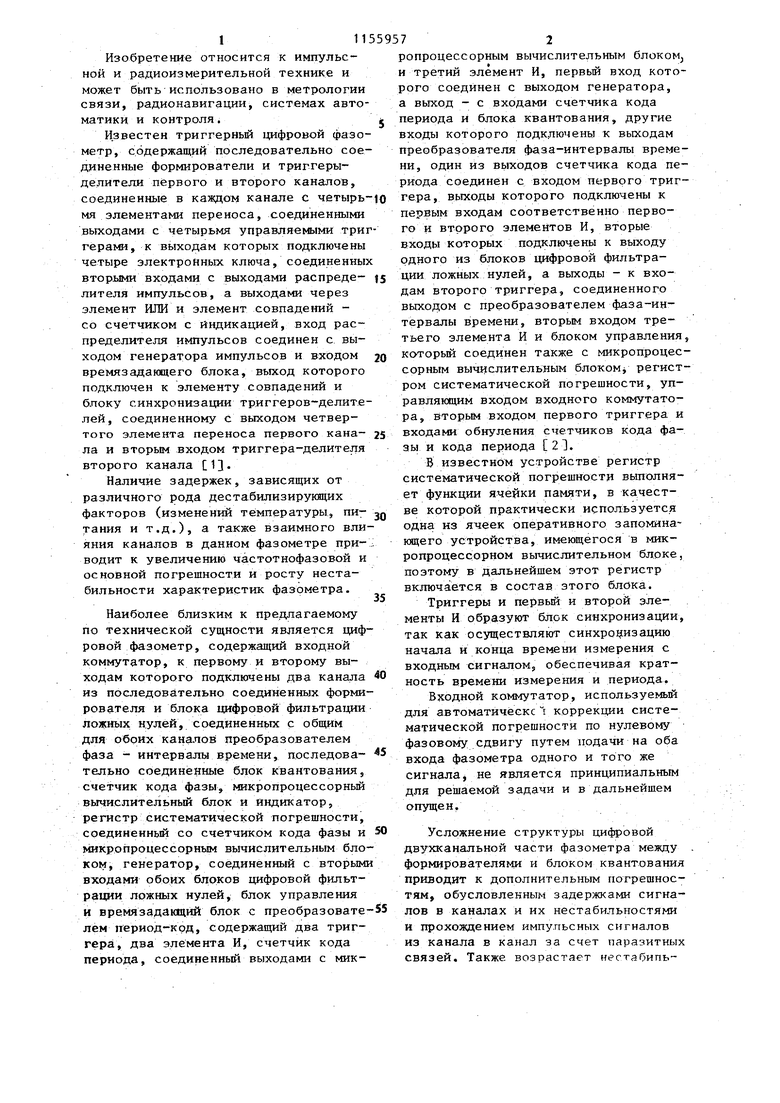

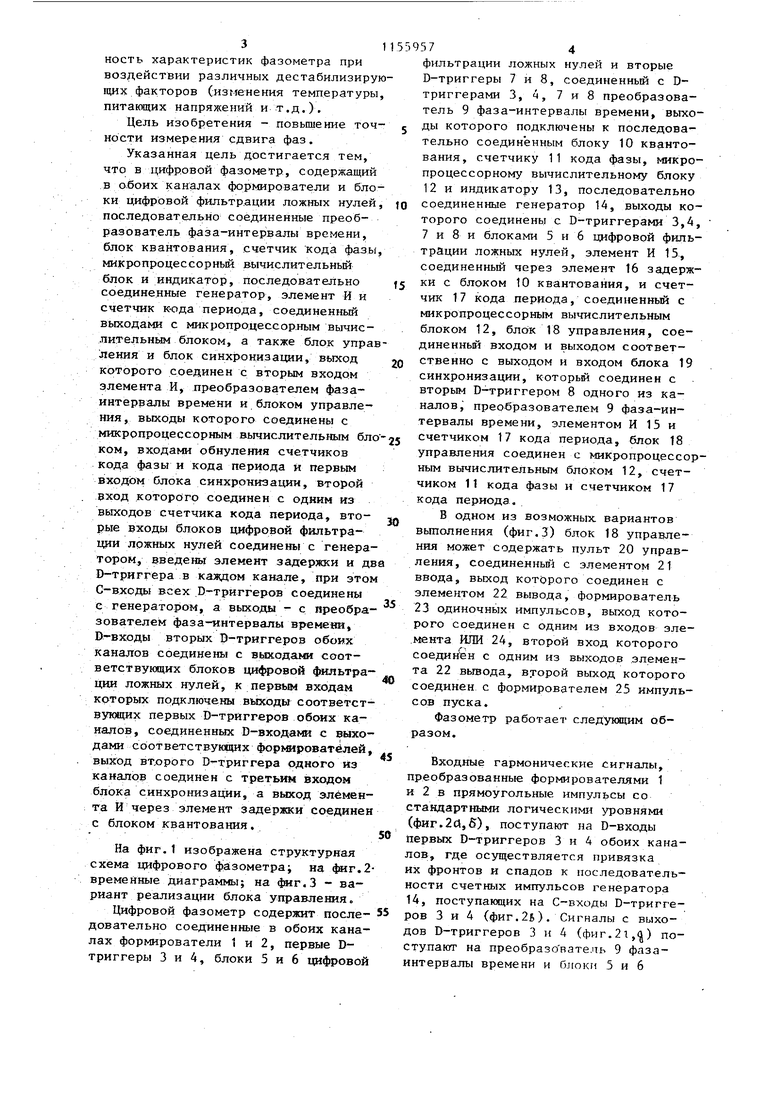

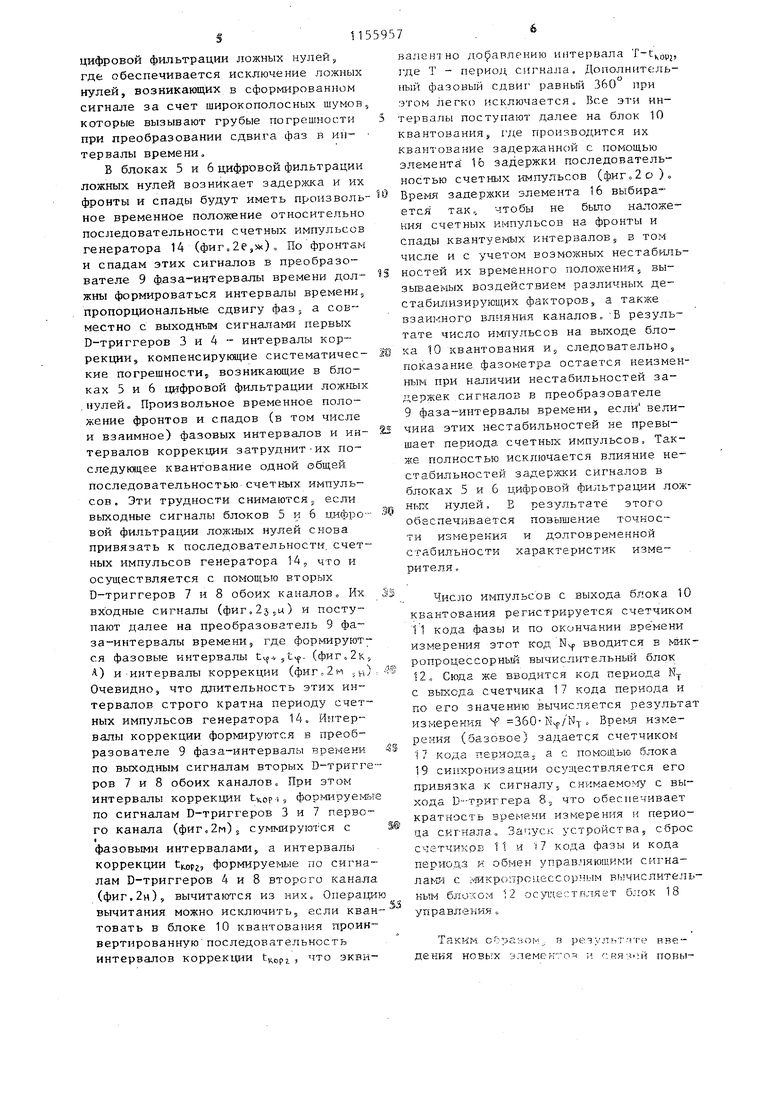

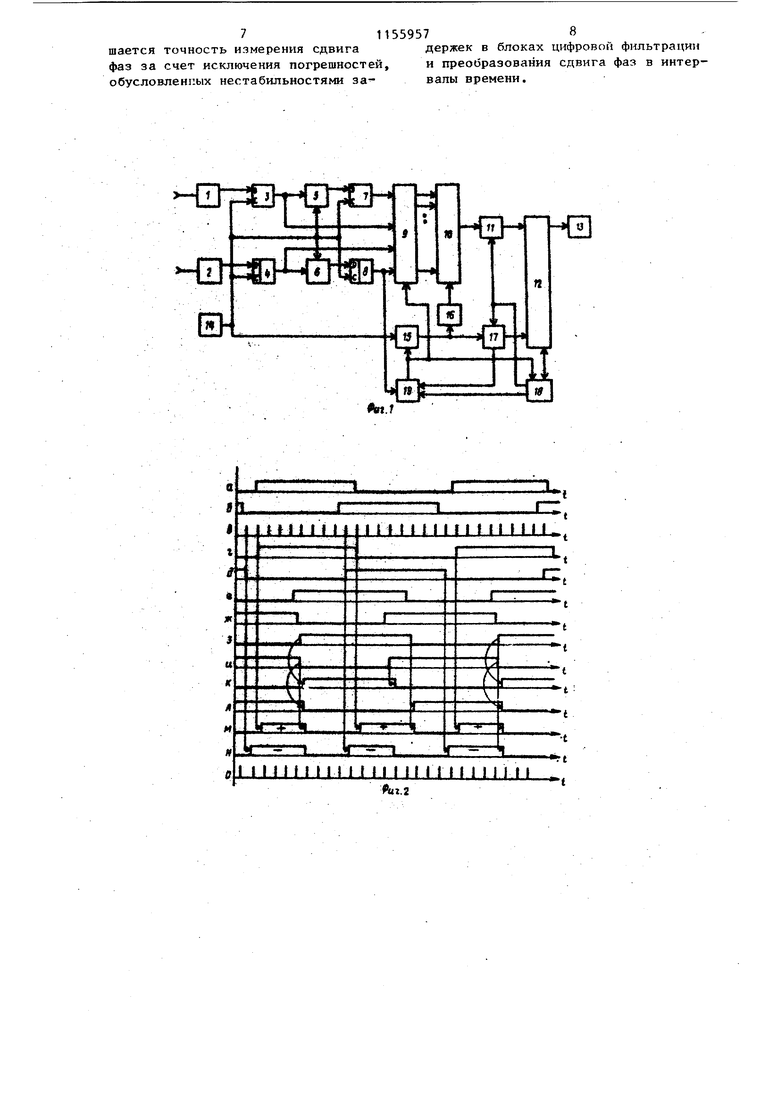

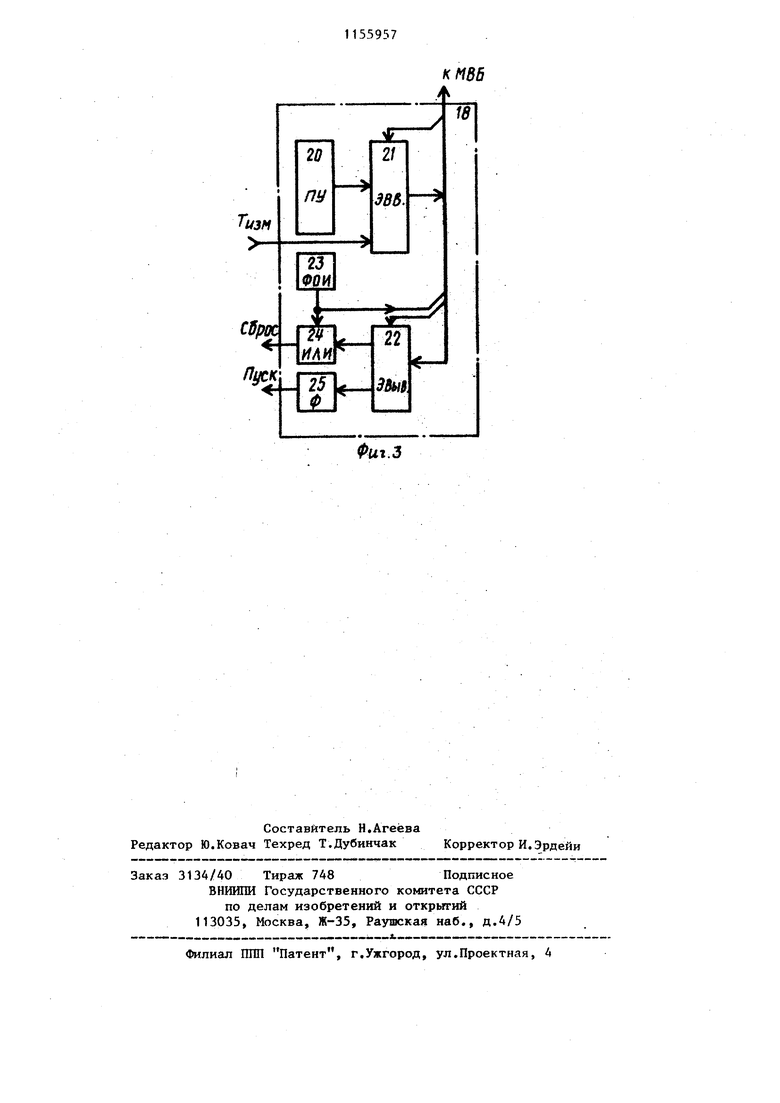

Изобретение относится к импульсной и радиоизмерительной технике и может быть использовано в метрологии связи, радионавигации, системах авто матики и контроля. Известен триггерньй цифровой фазо метр, содержащий последовательно сое диненные формирователи и триггерыделители первого и второго каналов, соединенные в каждом канале с четырь мя элементами переноса, соединенными выходами с четырьмя управляемыми три герами, к выходам которых подключены четыре электронных ключа, соединенны вторыми входами с выходами распределителя импульсов, а выходами через элемент ИЛИ и элемент совпадений со счетчиком с индикацией, вход распределителя импульсов соединен с выходом генератора импульсов и входом времязаданяцего блока, выход которого подключен к элементу совпадений и блоку синхронизации триггеров-делите лей, соединенному с выходом четвертого элемента переноса первого канала и вторым входом триггера-делителя второго канала 1. Наличие задержек, зависящих от различного рода дестабилизирукщих факторов (изменений те:мпературы, питания и т.д.), а также взаимного вли яния каналов в данном фазометре приводит к увеличению частотнофазовой и основной погрешности и росту нестабильности характеристик фазометра. Наиболее близким к предлагаемому по технической сущности является цифровой фазометр, содержащий входной коммутатор, к первому и второму выходам которого подключены два канала из последовательно соединенных формирователя и блока цифровой фильтрации ложных нулей, соеднненньтх с общим для обоих каналов преобразователем фаза - интервалы времени, поеледовательно соединенные блок квантования, счетчик кода фазы, микропроцессорньй вычислительный блок и индикатор, регистр систематической погрешности, срединенньй со счетчиком кода фазы и микропроцессорнш вычислительным блоком, генератор, соединенный с вторыми входами обоих блрков цифровой фильтрации ложных нулей, блок управления и времязадакщий блок с преобразователём период-код, содержащий два триггера, два элемента И, счетчик кода периода, соединенный выходами с микропроцессорным вычислительным блоком и третий элемент И, первый вход которого соединен с выходом генератора, а выход - с входами счетчика кода периода и блока квантования, другие входы которого подключены к выходам преобразователя фаза-интервалы времени, один из выходов счетчика кода периода соединен с входом первого триггера, выходы которого подключены к первым входам соответственно первого и второго элементов И, вторые входы которых подключены к выходу одного из блоков цифровой фильтрации ложных нулей, а выходы - к входам второго триггера, соединенного выходом с преобразователем фаза-интервалы времени, вторым входом третьего элемента И и блоком управления, который соединен также с микропроцессорным вычислительным блоком регистром систематической погрешности, управляющим входом входного коммутатора, BTOpbtM входом первого триггера и входами обнуления счетчиков кода фазы и кода периода 21. В известном устройстве регистр систематической погрешности выполняет функции ячейки памяти, в качестве которой практически используется одна из ячеек оперативного запомина кщего устройства, имеющегося в микропроцессорном вычислительном блоке, поэтому в дальнейшем этот регистр включается в состав этого блока. Триггеры и первый и второй элементы И образуют блок синхронизации, так как осуществляют синхронизацию начала и конца времени измерения с входным сигналом, обеспечивая кратность времени измерения и периода. Входной коммутатор, используемьй для автоматичёскс : коррекции систематической погрешности по нулевоь фазовому сдвигу путем подачи на оба входа фазометра одного и того же сигналаi не является принципиальным для решаемой задачи и в дальнейшем опущен. Усложнение структуры цифровой двухканальной части фазометра между . формирователями и блоком квантования приводит к дополнительным погрешностям, обусловленным задержками сигналов в каналах и их нестабильностями и прохождением импульсных сигналов из канала в канал за счет паразитных связей. Также возрастает нестабипь3ность характеристик фазометра при воздействии различных дестабилизиру 1ЦИХ факторов (изгтенения температуры питающих напряжений и т.д.). Цель изобретения - повышение точ ности измерения сдвига фаз. Указанная цель достигается тем, что в цифровой фазометр, содержащий в обоих каналах формирователи и бло ки цифровой фильтрации ложных нулей последовательно соединенные преобразователь фаза-интервалы времени, блок квантования, счетчик кода фазы микропроцессорньй вычислительньй блок и индикатор, последовательно соединенные генератор, элемент И и счетчик к-ода периода, соединенный выходагда с микропроцессор.ным вычислительным блоком, а также блок упра ления и блок синх1юнизации, вьпсод которого соединен с вторым входом элемента И, преобразователем фазаинтервалы времени и блоком управления, выходы которого соединены с микропроцессорным вычислительным бл ком, входами обнуления счетчиков кода фазы и кода периода и первым входом блока синхронизации, второй 9ХОД KOTopdro соединен с одним из выходов счетчика кода периода, вторые входы блоков цифровой фильтрации ложных нулей соединены с генера тором, введень элемент задержки и д D-триггера в каяадом канале, при это С-входы всех D-триггеров соединены с генератором, а выходы - с преобра зователем фаза-интервалы времеин, D-входы вторых В-триггеров обоих каналов соединены с выходами соответствующих блоков цифровой фильтра ции ложных нулей, к первьм входам которых подключены выходы соответст вующих первых D-триггеров обоих каналов, соединенных D-входами с выхо дами соответствующих форьмроватёлей выход второго D-триггера одного из каналов соединен с третьим входом блока синхронизации, а выход элемен та И через элемент задержки соедине с блоком квантования, На фиг,1 изображена структурная схема цифрового фа зометра; на (|мг.2 временные диаграммы; на фкг.З - вариант реализации блока управления. Цифровой фазометр содержит последовательно соединенные в обоих каналах формирователи 1 и 2, первые Dтриггеры 3 и 4, блоки 5 и 6 цифровой 574 фильтрации ложных нулей и вторые D-триггеры 7 и 8, соединенный с Dтриггерами 3, ч, 7 и 8 преобразователь 9 фаза-интервалы времени, выходы которого подключены к последовательно соединенным блоку 10 квантования, счетчику 11 кода фазы, микропроцессорному вычислительному блоку 12 и индикатору 13, последовательно соединенные генератор 14, выходы которого соединены с D-триггерами 3,4, 7 и 8 и блоками 5 и 6 цифровой фильтрации ложных нулей, элемент И 15, соединенный через элемент 16 задержки с блоком 10 квантования, и счетчик 17 кода периода, соединенньш с микропроцессорным вычислительным блоком 12, блок 18 управления, соединенньй входом и выходом соответственно с выходом и входом блока 19 синхронизации, который соединен с вторым D-триггеррм 8 одного из каналов, преобразователем 9 фаза-интервалы времени, элементом И 15 и счетчиком 17 кода периода, блок 18 управления соединен с микропроцессорным вычислительным блоком 12, счетчиком 11 кода фазы и счетчиком 17 кода периода, В одном из возможных, вариантов вьтолнения (фиг.З) блок 18 управления может содержать пульт 20 управления, соединенна с элементом 21 ввода, выход которого соединен с элементом 22 вывода, формирователь 23 одиночных импульсов, выход которого соединен с одним из входов эле.мента Или 24, второй вход которого Соединен с одним из выходов элемента 22 вьшода, второй выход которого соединен с формирователем 25 импульсов пуска. Фазометр работает следующим образом. Входные гармонические сигналы, реобразованные формирователями 1 2 в прямоугольные импульсы со тандартными логическими уровнями (фиг.2с1,5), поступают на D-входы ервых D-триггеров 3 и 4 обоих канаов, где осуществляется привязка х фронтов и спадов к последовательости счетных импульсов генератора 4, поступающих на С-входы D-триггеов 3 и 4 {фиг.2ь). Сигналы с выхоов D-триггеров 3 и 4 (фиг.21 ,J) потупают на преобразователь 9 фазантерналы времени и блоки 5 и 6

цифровой фильтрации ложных нулей, где обеспечивается исключение ложных нулей, возникающих в сформированном сигнале за счет широкополосных шумов которые вызывают грубые погрешности при преобразовании сдвига фаз в интервалы времени

В блоках 5 и 6 цифровой фильтрации ложных нулей возникает задержка и их фронты и спады будут иметь произволь ное временное положение относительно последовательности счетных импульсов генератора 14 (фиг.), По фронтам и спадам этих сигналов в преобразователе 9 ф.аза-интервалы времени должны формироваться интервалы времени, пропорциональные сдвигу фаз j а совместно с выходным сигналами первых D-триггеров 3 и 4 - интервалы коррекции, компенсирукяцие систематические погрешности, возникающие в блоках 5 и 6 цифровой фильтрации ложных .нулей Произвольное временное положение фронтов и спадов (в том числе и взаимное) фазовых интервалов и ийтервалов коррекции затруднит-их последующее квантование одной общей последовательностью счетных импульсов . Эти трудности снимаютсЯз если

выходные сигналы блоков 5 и 6 цифро

вой фильтрации ложных нулей снова привязать к последовательности, счетных импульсов генератора 14, что и осуществляется с помощью вторых D-триггеров 7 и 8 обоих каналов. Их входные сигналы (фиго2з5и) и поступают далее на преобразователь 9 фаза-интервалы времени, где фop шpyются фазовые интервалы (фиг.2к5 А) и интервалы коррекции (фиг, 2м ,, L,) Очевидно, что длительность этих интервалов строго кратна периоду счетных импульсов генератора 14. Интервалы коррекции формируются в преобразователе 9 фаза-интервалы времени по выходным сигналам вторых В-тригге ров 7 и 8 обоих каналов с При этом интервалы коррекции tKopi, форг- ируемы по сигналам D-триггеров 3 и 7 первого канала (фиг,2м) суммирую1ся с I

фазовыми интервалами5 а интервалы коррекции tn,of23 формируемые по сигналам D-триггеров 4 и 8 второго канала (фиг,2и)5. вычитаются из них, Операц 1 вычитания можно исключить, если квантовать в блоке 10 квантования проинвертированную последовательность интервалов коррекции ,p2. 0 эквнвален1но добавлению интервала , где Т - период сигнала. Дополнительный фазовый сдвиг равньп ЗбО при этом легксз исключается. Все эти интервалы поступают далее на блок 10 квантования, где производится lix квантование задержанной с помощью элемента 16 задержки последовательностью счетных им.пульсов (фиго2о ) Время задержки элемента 16 выбирается так., чтобы не было наложения счетных импульсов на фронты и спады квантуемых интерваловj в том числе и с учетом возможных нестабильностей их временного пололсения5 вызьюаемых воздействием различных дестабилизирующих факторов, а также взаимного каналов, В результате число импульсов на выходе блока 10 квантования и, следовательно, показание фазометра остается неизменным при наличии нестабильностей задержек сигналов в преобразователе 9 фаза-интервалы времени, если величина этих нестабильностей не превышает периода, счетных импульсов. Также полностью исключается влияние нестабильностей задержки сигналов в блоках 5 и б цифровой фильтрации ложньпс нулей. В результате этого обеспечивается повышение точности измерения и долговременной стабильности характеристик измерителя.

Число импульсов с выхода блока ТО квантования регистрируется счетчиком 11 кода фазы и по окончании времени измерения этот код Nvp вводится в микропроцессорньй вычислительный блок 12, Сюда же вводится код периода N-,с выхода счетчика 17 кода периода и по его значению вычисляется результа измерения f 360-М / Ну. Времл измерения (базовое) за.дается счетчиком 17 кода периода, а с помощью блока 19 синхронизации осуществляется его привязка к сигналу, снимаемо гу с выхода D-триггера 83 что обеспечивает кратность времени измерения и периода сигнала. Зачуск устройства, сброс счетчиков 11 и 17 кода фазы и кода перио.дз к обмен управляющими сигналам: с гф кропроиессорным вычислительным блоком 2 осуществляет блок 18 управления.

Такг-;м of:pi;iioi4 в результ.чге введения новых элемеь:-:-оч и связок повы711359578

шается точность измерения сдвига держек в блоках цифровой фильтрации фаз за счет исключения погрешностей, и преобразования сдвига фаз в интеробусловленпых нестабильностями за валы времени.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения фазы | 1983 |

|

SU1265640A1 |

| Измеритель разности фаз | 1990 |

|

SU1800382A1 |

| Измеритель группового времени запаздывания | 1990 |

|

SU1725180A2 |

| Измерительное устройство для измерителя группового времени запаздывания | 1989 |

|

SU1620986A1 |

| Цифровой фазометр | 1981 |

|

SU1273831A1 |

| Цифровой фазометр | 1984 |

|

SU1213436A1 |

| Цифровой фазометр | 1985 |

|

SU1298688A2 |

| Цифровой фазометр с постоянным измерительным временем | 1981 |

|

SU1269035A1 |

| Цифровой фазометр | 1981 |

|

SU970258A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ КОЭФФИЦИЕНТА КОМАНДЫ ОДНОКАНАЛЬНЫХ ВРАЩАЮЩИХСЯ РАКЕТ И СНАРЯДОВ С РЕЛЕЙНЫМ РУЛЕВЫМ ПРИВОДОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2574500C2 |

ЦИФРОВОЙ ФАЗОМЕТР содержащий в обоих каналах формирователи и блоки цифровой фильтрации ложных нулей, последовательно соединенные преобразователь фаза-интервалы времени, блок квантования, счетчик кода фазы, микропроцессорНЬ1Й вычислительный блок и индикаторJ последовательно соединенные генератор, элемент И и счетчик кода периода; соединенный выходами с микропроцессорным вычислительным блоко®, а также блок управления и блок синхронизации, выход которого соединен с вторым входом элемента И, преобразователем фаза-интервалы времени и блоком- управления, выходы которого соединены с микропроцессорным вычислительным блоком, входами обнуления счетчиков кода фазы и кода периода и первым входом блока синхронизации, второй вход которого соединен с одним из выходов счетчика кода периода, вторые входы блоков цифровой фильтрации ложных нулей соединены с генератором, отличающийс я тем, что, с целью повьппения точности измерения, в него введены элемент задержки и два D-триггера в каждом канале при этом С-входы всех D-триггеров соединены с генератором, а выходы - с преобразователем фазаинтервалы времени, D-входы вторых D-трнггеров обоих каналов соединены с выходами соответствующих блоков цифровой фильтрации ложных нулей, к первым входам которых подключены выходы соответствующих первых D-триггеров обоих канадов, соединенных D-входами с выходами соответствующих формирователей, выход второго сл D-триггера одного из каналов соедиD1 нен с третьим входом блока синхро низации а выход элемента И через (У1 элемент задержки соединен с блоком квантования.

KM 86

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПРИБОР ДЛЯ СВЕРЛЕНИЯ ОТВЕРСТИЙ В ОБСАДНЫХ ТРУБАХ | 1933 |

|

SU68284A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Способ запрессовки не выдержавших гидравлической пробы отливок | 1923 |

|

SU51A1 |

Авторы

Даты

1985-05-15—Публикация

1983-11-03—Подача