Изобретение относится к измерительной технике и может быть использовано для измерения фазового сдвига непрерывных радиосигналов.

Наиболее близким к предлагаемому является цифровой фазометр, содержащий два формирователя, первьзй и второй триггеры, первый и второй элементы совпадений, генератор квантующих импульсов, счетчик импульсов и делитель частоты, причем входал формирователей соединены с входами фазометра, а их выходы - с соответствующими управляющими входами первого триггера, выход которого подключен к входу первого элемента совпадeнийj выход второго элемента совпадений соединен с входом делителя частоты и с вторым входом первого элемента совпадений, выход которого подключен к входу счетчика импульсов, выход генератора квантующих импульсов соединен с первым входом второго элемента совпадений, второй вход которого подключен к выходу второго триггера, выход делителя частоты соединен с первым входом второго триггера, второй вход которого подключен к входу запуска фазометра и к входу установки в О счетчика импульсов l .

Недостатком известного цифрового фазометра является недостаточно высокая точность измерения фазовых сдвигов сигналов. Это обусловлено тем, что он имеет большое значение систематической погрешности от шумоввызванной разрывностью фазовой характеристики - соответствием нулевого фазового сдвига фазовому сдвигу, равному 360. Систематическая погрешность от шумов, вызванная разрывностью фазовой характеристики, возникает в результате усреднения значений отсчетов фазового сдвига, лежащих в области разрыва фазовой характеристики. При этом среднее значение измеряемого фазового сдвига определяемое, например, по двум близким значениям, равным 359 и l, оказывается равным

со - , ср- 2 180 .

Составляющая погрешности измерения фазового сдвига, обусловленная разрывностью фазовой характеристики в данном случае составлйет 180.

Цель изобретения - повышение точности измерения фазовых сдвигов сигналов.

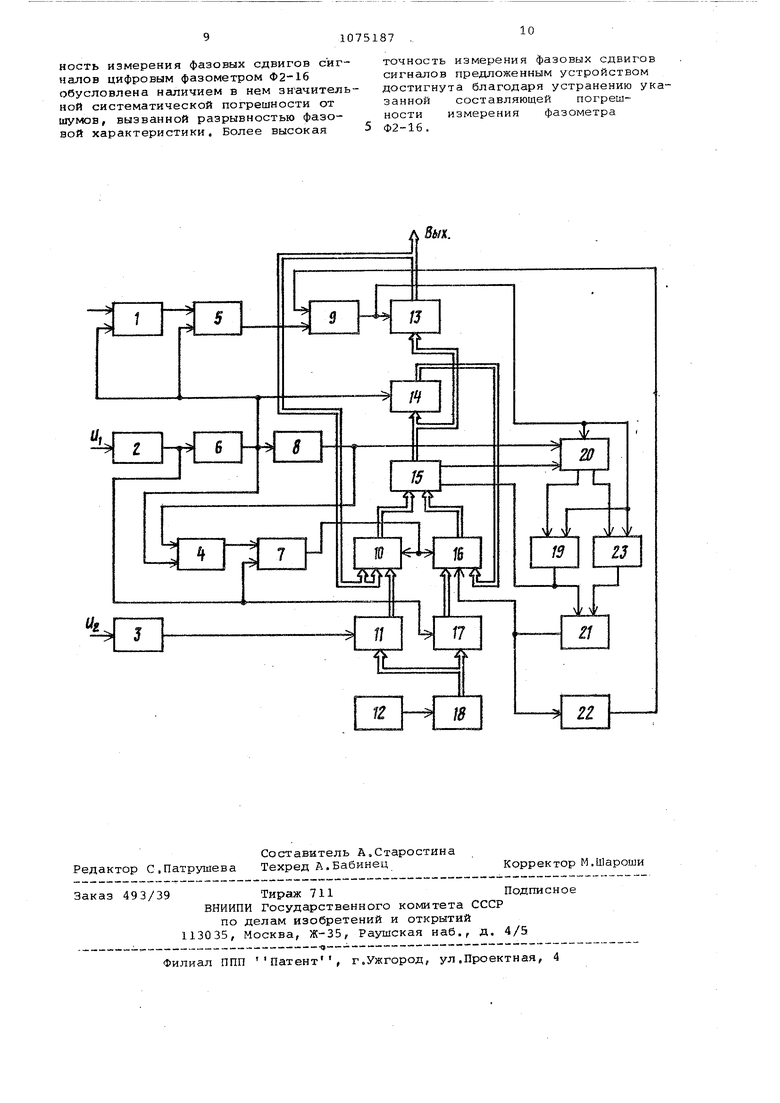

Поставленная цель достигается тем, что в цифровой фазометр, содержащий два формирователя, входы которых соединены с соответствующими входами цифрового фазометра, элемент совпадений, генератор квантуюгдих импульсов, делитель частоты и первый триггер, вход которого подключен к входу запуска фазометра, а выход к первому входу элемента совпадений, введены арифметический блок, первый, второй, третий и четвертый запоминающие регистры, первый и второй коммутаторы, выходы которых соединены соответственно с первым и вторым входами арифметического блока, реверсивный счетчик, второй делитель частоты, первый, второй и третий элемент ИЛИ, второй и третий триггеры, первый, второй и третий элементы задержки, причем выход генератора квантующих импульсов соединен с входом делителя частоты, выходы разрядов которого подключены к сигнальным входам первого и второго запоминающего регистров, выход первого формирователя соединен с управляющим входом первого запоминающего регистра, выход второго формирователя подключен к управляющему входу второго запоминающего регистра, к входу

О

второго делителя

установки в

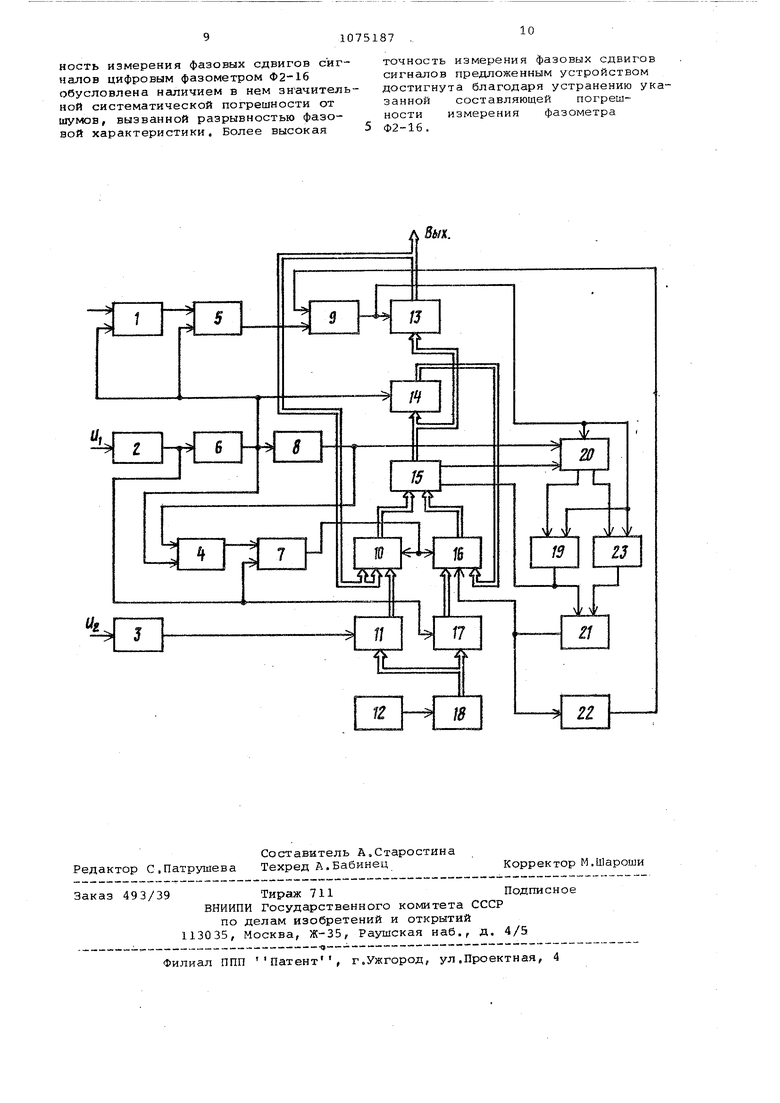

частоты и к входу первого элемента задержки, ЁЫХОД которого соединен с входом установки в О первого триггера, вторым входом элемента совпадений, входом второго элемента задержки, управляющим входом третьего запоминающего регистра и первым входом первого элемента ИЛИ, выход которого подключен к входу второго делителя частоты, выходы которого соединены с управляющими входами первого и второго коммутаторов, первые входы которых подключены к выходам первого и второго запоминающих регистров, при этом второй и третий входы первого коммутатора соединены с выходом четвертого запоминающего регистра и выходом цифрового фазометра, второй вход второго комг утатора подключен к выходу третьего запоминающего регистра, вход которого соединен с первым выходом арифметического блока и входом четвертого запоминающего регистра, второй выход арифметического блока подключен к уцрс1вляющему входу реверсивного счетчика, счетный вход которого соединен с выходом второго элемента задержки и вторым входом первого элемента ИЛИ, вход предустановки реверсивного счетчика подключен к выходу второго элемента ИЛИ, к управляющему входу четвертого запоминающего регистра и к входам установки в О второго и третьего триггеров, входы которых соединены с выходами соответственно переноса и заема реверсивного счетчика, выход третьего триггера .подключен к одному входу третьего элемента ИЛИ, другой вход которого сое,цинен с выходом второго триггера и выходом арифметического блока, а выход - с третьим входом второго ком мутатора и входом третьего элемента задержки, выход третьего элемента задержки подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом элемента совпадений. Первое значение фазового свдига заносят в выходной запоминающий регистр. Последующие .отсчеты фазового сдвига сравнивают со значением, хранящимся в выходном регистре, и накап ливают информацию о разности количеств отклонений разных знаков после дующих значений фазовых сдвигов относите51ьно значения, хранящегося в выходном регистре. При превышении значением указанной разности некоторого заданного числа значение, хранящиеся в выходном регистре, коррек тируют в сторону уменьшения разности сравниваемых значений фазовых сдвигов , Таким образом, в предлагаемом цифровом фазометре среднее значение измеряемого фазового сдвига сигнало П9лучают путем запоминания одного из текущих значений фазового сдвига и коррекции его до получения значения, при котором знаки отклонений от него последующих значений фазовых сдвигов станут равновероятными, При этом для определения среднего значения измеряемого фазового сдвига сигналов не используют суммирова ние значений фазовых сдвигов, приво дящее в противопоставляемом цифрово фазометре к систематической погрешности от шумов, обусловленной разрывностью фазовой характеристики. Поэтому указанная составляющая погр ности измерения в предложенном устройстве отсутствует, что обуславливает его более высокую точность. На чертеже приведена структурная схема устройства, Цифровой фазометр содержит первы триггер 1, формирователи 2 и 3, пер вый элемент ИЛИ 4, элемент 5 совпадений, первый элемент б задержки, второй делитель 7 частоты, второй элемент 8 задержки, второй элемент ИЛИ 9, первый коглмутатор 10, первый запоминающий регистр 11, генератор 12 квантующих импульсов, четвертый запоминающий регистр 13, третий запоминающий регистр 14, арифметический блок 15, второй коммутатор 16, второй запоминающий регистр 17, пер вый делитель 18 частоты, второй три гер 19, реверсивный счетчик 20, третий элемент 21 ИЛИ, третий элемент 22 задержки и третий триггер 2 причем входы цифрового фазометра подключены к входам соответственно первого и второго формирователей, выход первого формирователя 3 соеди нен с управляющим входом первого запоминающего регистра И, выход ге-. нератора 12 квантующих импульсов подключен к входу делителя 18 частоты, выходы разрядов которого соединены с сигнальным входами первого и второго запоминающих регистров 11 и 17, выход второго формирователя 2 подключен к входу установки в О делителя 7 частоты, управляющему входу второго запоьщнающего регистра 17 и входу первого элемента 6 задержки, выход которого соединен со входом установки в О первого триггера 1, вторым входом элемента 5 совпадений, управляющим входом третьего запоминающего регистра 14, входом второго элемента- 8 задержки и первым входом первого элемента 4 ИЛИ, выход второго элемента 8 задержки подключен к счетному входу реверсивного счетчика 20 и второму входу первого элемента 4 ИЛИ, выход которого соединен с входом делителя 7 частоты, выходы первого и второго запоминающего регистров 11 и 17 подключены к первым входам соответственно первого и второго коммутаторов 10 и 16, управляющие входы которых соединены с выходами делителя 7 частоты, выходы первого и второго коммутаторов 10 и 16 подключены соответственно к первому и второму входам арифметического блока 15, первый выход которого соединен с входами четверторого и второго запоминающих регистров 13 и 17, выход третьего запоминающего регистра 14 подключен к второму входу второго коммутатора 16, выход четвертого запоминающего регистра 13, являющийся выходом цифрового фазометра, соединен с вторым и третьим входами первого коммутатора 10, вход запуска цифрового фазометра подключен к входу первого триггера 1, выход которого соединен с первым входом элемента 5 совпадений, выход которого подключен к второму входу второго элемента 9 ИЛИ, выход которого соединен с управляющим входом четвертого запоминающего регистра 13, входом предустановки реверсивного счетчика 20 и входами установки в О второго и третьего триггеров 19 и 23, второй выход арифметического блока подключен к управляющему входу реверсивного счетчика 20, выходы переноса и заема которого соединены с входами соответственно второго и третьего триггеров 19 и 23, выход второго триггера 13 подключен к управляющему входу арифметического блока 15 и к одному входу третьего элемента 21 ИЛИ, другой вход которого соединен с выходом третьего триггера 23, выход третьего элемента 21 ИЛИ подключен к третьему входу второго коммутатоpa 16 и к входу третьего элемента 22 задержки, выход которого соедине с первым входом второго элемента 9 ИЛИ. Устройство работает следующим образом. Формирователи 2 и 3 производят короткие импульсы в моменты переход исследуемых сигналов через нулевое значение, например, из области отри цательных значений в область положи тельных значений,Полученные короткие импульсы поступают на управляющие входы первого и второго запоминающих регистров 11 и 17 и осуществ ляют перепись в них значений кодов делителя 18 частоты, заполняемого импульсами генератора 12, Период за полнения делителя 18 частоты устана ливают равным периоду исследуемых сигналов, поэтому каждому мгновенно му значению фазы исследуемого сигна ла соответствует определенное значе ние кода делителя 18 частоты. Корот кий импульс с выхода второго формирователя 2 устанавливает в нулевое состояние делитель 7 частоты, выход ной код которого поступает на управ ляющие входы первого и второго коммутаторов 10 и 16 и подключает к их выходам первые входы. При этом запо ненные первым и вторым запоминающими регистрами 11 и 17 значения кодов поступает через первый и второй коммутаторы 10 и 16 на входы арифметического блока 15, вычисляющего их разность, соответствующую измеря емому фазовому сдвигу. Цифровой фазометр предназначен для измерения фазовых сдвигов сигналов фиксированной частоты, равной частоте заполнения делителя 18 частоты. Работа в широком диапазоне частот может быть обеспечена известными методами, например переносом измеряемого фазового сдвига сигнало с любой частоты диапазона на фиксиро ванную частоту с помощью преобразования частоты. Поддержание равенства частоты преобразованных сигналов частоте заполнения делителя частоты может быть достигнуто при помощи частотной и фазовой автоподстройки частоты сигнала гетеродина. Внешним сигналом Запуск ьйрвый триггер устанавливают в состояние логической единицы. Короткий выходной импульс эторого формирователя 2 задерживается первым элементом 6 задержки на время, рав ное времени прохождения сигналов от входов коммутаторов до выходов арифм€ тического блока 15, проходит через открытый выходным сигналом перво го триггера 1 элемент 5 совпадений и через второй элемент 9 ИЛИ на управляющий вход четвертого запо№1нающего регистра и осуществляет перепись в него выходного кода арифметического блока 15, соответствующего значению измеряемого фазового сдвига, а также установку в нулевое со- . .стояние второго и третьего триггеров и установку в реверсивном счетчике 20 кода N/2, соответствующего половине его емкости, Короткий импульс с выхода первого элемента задержки осуществляет также установку в исходное нулевое состояние первого триггера, перепись кода арифметичезского блока 15 в третий запоминающий регистр, а также проходит через первый элемент 4 ИЛИ на вход второго делителя 7 частоты. Изменившийся при этом код второго делителя частоты подключает выходы коммутаторов к их вторым входам. При этом арифметический .блок 15 вычисляет разность значений кодов, поступающих на его входы с выходов третьего и четвертого запоминающих регистров через второй и первый коммутаторы соответственно. В данном такте работы арифметический блок 15 используют как устройство сравнения значения фазового сдвига С| g,, , записанного в четвертом (выходном) запоминающем регистре 13с последующим (текущим) значением фазового сдвига Qi|-, вычисленным арифметическим блоком 15 и записанным в третьем запоминающем регистре 13, При значении разности сравниваемых фазовых сдвигов Л( Чвы х ii с второго выхода арифметического блока 15 на управляющий вход реверсивного счетчика поступает потенциал, при котором реверсивный счетчик работает в режиме суммирования. Если значение йС|) rCf gj,-Cf т iи i на втором выходе арифметического блока 15 формируется инверсный сигнал, переключающий реверсивный счетчик в режим вычитания. Содержащиеся во входных сигналах шумы, а также собственные аппаратурные шумы цифрового фазометра приводят к флуктуадиям переходов исследуемых сигналов через нулевое значение. Поэтому при неизменном значении измеряемого фазового сдвига измеренные в каждом периоде исследуемых сигналов значения фазового сдвига соответствуют случайным числам, распределенным, как правило, по нормальному закону и характеризующимся средним значениям и дисперсией, Если значение кода, записанного в четвертый запоминающий регистр 1, окажется равным среднему значению измеряемого фазового сдвига, то отклонения последующих значений фазовых сдвигов в сторону больших или меньших значений относительно среднего

значения будут иметь равную вероятность. При этом разность значений кодовf Записанных в третий и четвертый запоминающие регистры 14, 13, также с равной вероятностью будут иметь значения ii или itf « Так, если значения фазовых сдвигов, записываемых в третий запоминаю1дий регистр 14, равны ( -Aqi или Ц + it|i , где itj) сi, то значение разности кодо четвертого и третьего регистров 13 и 14 составит соответственно Цl-()и иц)-(ци-лч1 -ь -0-441 2и-йс п так как емкость арифметического блока 15 соответствует 2i.

В рассмотренном случае равноверо ятных отклонений значений фазовых сдвигов, записываемых в третий запоминающий регистр 14, от значения, записанного четвертый запо1чинающий регистр 13 со второго выхода арифметического блока 15 на Управляющий вход реверсивного счетчика 20, с равной вероятностью будут поступать сигналы лопгческого О и логической ,

Короткий импульс с выхода первого элемента б задержки, задержанный вторым элементом 8 задержки на время, равное времени прохождения сигналов от входов коммутаторов до выходов арифметического блока 15, поступает на счетный вход реверсивного счетчика 20 и через первый элемен 4 ИЛИ на вход делителя 7 частоты. Изменившийся при этом код делителя 7 частоты подключает выходы первого и второго коммутаторов 10 и 16 к их третьим входам. Количества импульсов, сосчитанных реверсивным счетчиком 20 в режимах суммирования и вычитания будут равны при выборе доста . точно -большого значения емкости реверсивного счетчика. Поэтому сигналы на выходах переноса и заема реверсивного счетчика будут отсутствовать .

Если значение фазового сдвига, записанное в четвертом запоминающем регистре 13, не равно его среднему значению, то количества импульсов, .сосчитанных реверсивным счетчиком 20 в режимах суммирования и вычитания ,будут неравномерны, что приведет к появлению импульсов на выходе переноса или заема и опрокидыванию соответственно второго или третьего триггера.

Сигнал логической i с выхода второго или третьего триггера 19 или 23 проходит через третий элемент 21 ИЛИ и поступает на третий вход второго коммутатора 16. Указанный сигнал обеспечивает появление на выходе коммутатора 16 кода, соответствующего значению приращения фазового сдвига, на которое предусмотрено производить коррекцию результата,

хранящегося в четвертом регистре 13. Знак коррекции определяется состоянием триггера 19, выходной сигнал которого поступает на управляющий вход блока 15 и задает операцию суммирования или вычитания. Блок 15 вычисляет при этом сумму или разность значения выходного кода зaпo инaющeгo регистра 13 и значения корректирующего кода. Сигнал с выхода третьего элемента 21 ИЛИ задерживается элементом 22 задержки на время, равное времени прохождения сигналов от входов коммутатора до выхода арифметического блока, проходит через второй элемент 9 ИЛИ и осуществляет перепись выходного сигнала блока 15 в запоминающий регистр 13, а также установку в счетчике 20 кода предустановки W/2 и установку в нулевое состояние триггеров 19 и 23.

И в дальнейшем в течение каждого периода исследуемых сигналов определяют текущее значение их фазового сдвига, находят знак его отклонения от значения, хранящегося в выходном регистре, и накапливают при помощи реверсивного счетчика информацию о разности количеств указанных отклонений разных знаков. При превышении значением разности количеств отклонений разных знаков числа Я/2 значение результата, хранящееся в четвертом регистре, корректируют при помощи арифметического блока на определе ное значение в сторону уменьшения разности сравниваемых значений фазовых сдвигов. Таким образом, значение кода в четвертом регистре отслеживает среднее значение измеряемого фазового сдвига.

Таким образом, благодаря применению в предложенном фазометре схемы отслеживания среднего значения фазового сдвига, включающей арифметический блок 15, третий и четвертый запоминающие регистры 13, 14 и первый и второй комм таторы 10 и 16, реверсивный счетчик 20, второй и третий триггеры 19 и 23, делитель 7 частоты первый, второй и третий элементы 4, ,9 и 21 ИЛИ, исклЕочена присущая противоставляемому фазометру систематическая составляющая погрешности от шумов, обусловленная разрывностью фа фазовой характеристики. Этим обусловлено значительное повышение точности измерения предложенным фазометром фазовых сдвигов сигналов в диапазоне значений 0-2 it .

Техническим преимуществом предлагаемого цифрового фазометра перед базовым образцом, в качестве которого принят серийный цифровой фазометр Ф2-16, является более высокая точность измерения фазовых сдвигов сигналов. Недостаточно высокая точность измерения фазовых сдвигов сигналов цифровым фазометром Ф2-16 обусловлена наличием в нем зн ачительной систематической погрешности от шумов, вызванной разрывностью фазовой характеристики. Более высокая

точность измерения фазовых сдвигов сигналов предложенным устройством достигнута благодаря устранению указанной составляющей погрешности измерения фазометра Ф2-16.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой компенсатор | 1972 |

|

SU439915A1 |

| Цифровой фазометр | 1986 |

|

SU1348744A1 |

| Цифровой корреляционный фазометр | 1981 |

|

SU1056077A1 |

| Ультразвуковой расходомер | 1991 |

|

SU1831655A3 |

| Способ измерения фазового сдвига между двумя гармоническими сигналами и устройство для его осуществления | 1988 |

|

SU1596272A1 |

| Цифровой фазометр | 1981 |

|

SU1026077A1 |

| Фазометр | 1978 |

|

SU765750A1 |

| Следящий фазометр | 1980 |

|

SU894595A1 |

| Цифровой корреляционный фазометр | 1980 |

|

SU943598A1 |

| Цифровой фазометр | 1983 |

|

SU1128187A1 |

ЦИФРОВОЙ ФАЗОМЕТР, содержащий два формирователя,входы которых соединеныс первым и вторым входами цифрового фазометра, элемент совпадений, генератор квантующих импульсов, делитель частоты и первый триггер, вход которого подключен к входу запуска фазометра, а выход к первому входу элемента совпадений, отличающийся тем, что, с целью повышения точности измерения фазовых сдвигов сигналов, в него введены арифметический блок, первый, второй, третий и четвертый запоминающие регистры, первый и второй коммутаторы, выходы которых соединены соответственно с первым и вторым входами арифметического блока, реверсный счетчик, второй делитель частоты, первый, второй и третий элементы ИЛИ, второй и третий триггеры, первый, второй и третий элементы задержки, причем выход генератора квантующих импульсов соединен с входом делителя частоты, выходы разрядов которого подключены к сигнальным входам первого и второго запоминающих регистров, выход первого формирователя соединен с управляющим входом первого запоминающего регистра, выход второго формирователя подключен к управляющему входу второго запоминающего регистра, к .входу установки в О второго де;лителя частоты и к входу первого элемента задержки, выходом соединенного с входом установки в О первого триггера, вторым входом элемента совпадений, входом второго элемента задержки, управляющим входом третьего запоминающего регистра и первым входом первого элемента ИЛИ, выход которого подключен к входу второго делителя частоты, соединенного выходом с управляющими входами первого и второго коммутаторов, первые входы которых подключены к выходам первого и второго запоминающих регистров, при этом второй и третий входы первого кЬммутатора соединены с выходом четвертого запоминающего регистра и выходом цифрового фазометра, второй вход второго ком(Л мутатора подключен к выходу третьего запоминающего регистра, вход которого соединен с первым выходом арифметического блока и входом чет вертого запоминающего регистра, второй -выход арифметического блока подключен к управляющему входу реверсивного счетчика, счетный вход которого сЪединен с выходом второго элемента задержки и вторым дом первого элемента ИЛИ, вход предустановки реверсивного счетчика подСП ключен к выходу второго элемента ИЛИ; к управляющему входу четвертого за-,, поминающего регистра и к входам ус00 тановки в О второго и третьего триггеров, входы которых соединены с выходами соответственно переноса и заема реверсивного счетчика, выход третьего триггера подключен к одному входу третьего элемента ИЛИ, другой вход которого соединен с выходом второго триггера и выходом арифметического блока, а выход - с третьим входом второго коммутатора и входом третьего элемента задержки, выход третьего элемента задержки подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом элемента совпадений.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Смирнов П.Т | |||

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1984-02-23—Публикация

1982-08-31—Подача