со

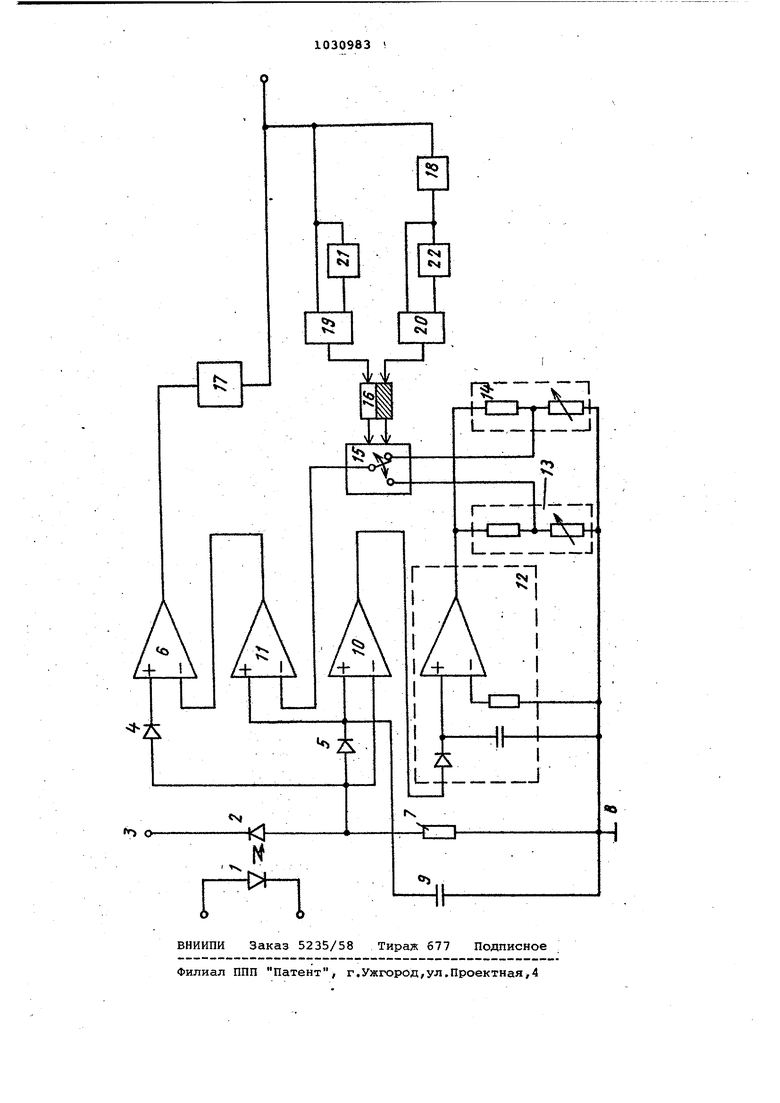

00 00 Изобретение относится к вычислительной и телеграфной технике и мо- жет быть использовано в устройствах/ предназначенных для регистрации длительности однополярных импульсов тока. По основному авт. св. № 898625 известно оптоэлектронное входное устройство, содержащее светодиод, оптически связанный с фотодиодом,который включен в обратном направлении между ши ной питания и инвертируквдим входом первого дополнительного операционного усилителя, анодом первого диода, анодом второго диода, вторым выводом резистора, первый вьавод которого под ключей к общей шине, к первому входу делителя напряжения и к одному выво|цу конденсатора, другой вывод которого соединен с катодом второго диода, с неинвертирунхдим входом первого дополнительного операционного усилителя и с неинвертирукяцим входом второго дополнительного операционного усилителя, выход которого подключен к инвертирующему входу основного операционного усилителя, причем выход первого дополнительного операционного усилителя соединен с входом аналогового блока памяти, выход которого под ключен к второму входу делителя напряжения, выход которого соединен с инвертирующим входом второго дополнительного операционного усилителя, а катод первого диода подключен к неинвертирунхдему входу основного операционного усилителя 1, Однако это устройство обладает низкой помехоустойчивостью. Цель изобретения - повышение помехоустойчивости. Для-этого в оптоэлектронное устройство, содержащее светодиод оптически связанный с фотодиодом, который включен в обратном направлении между шиной питания и инвертирующим входом первого дополнительного операционного усилителя, анодом первого диода, анодом второго диода, вторым выводом резистора, первый вывод которого подключен к общей шине, к первому входу делителя напряжения и к одному выводу конденсатора, другой вывод которого соединен с катодом второго диода, с неинвертирующим входом первого дополнительного операционного усилителя и с неинвертируняцим входом второго дополнительного операционного усилителя, выход которого подключен к инвертирующему входу основного операционного усилителя, причем выход первого дополнительного операционного усилителя соединен с входом аналогового блока памяти, выход которого подключен к второму входу делителя напряжения, выход которого соедине с инвертирующим входом второго дополнит ельного операционного усилителя,а катол первого диода подключен к неинвертирующему входу основного операционного усилителя, дополнительный делитель напряжения, коммутатор, триг гер, два элемента И, два элемента задержки, инвертор и буферный усилитель, выход которого соединен с входом первого элемента задержки, с первым входом первого элемента И и с входом инвертора, выход которого соединен с первым входом второго элемента И и с входом второго элемента задержки, выход которого соединен с вторым входом второго элемента И, выход которого соединен с первым входом триггера, второй вход которого соединен с выходом первого элемента И, второй вход которого соединен с выходом первого элемента задержки, причем выходы триггера подключены к управляю им входам коммутатора, первый вход которого соединен с выходом делителя напряжения,. первый и второй входы которого подключены соответственно к первому и второму входам дополнительного делителя напряжения, выход которого соединен с вторым входом коммутатора, выход которого соединен с инвертирующим входом второго дополнительного операционного усилителя, а выход основного операционного усилителя подключен к входу буферного усилителя. На чертеже приведена структурная электрическая схема предложенного устройства. Оптоэлектронное входное устройство содержит светодиод 1, оптически связанный с фотодиодом 2, включенным в обратном направлении между шиной 3 питания и анодом .первого диода 4, второй диод 5, основной операционный усилитель б, резистор 7, общую .шину 8, конденсатор 9, первый дополнительный операционный усилитель 10, второй дополнительный операционный усилитель J. 1, аналоговый блок 12 памяти, делитель 13 напряжения, дополнительный делитель 14 напряжения, коКшутатор 15, триггер 16, буферный усилитель 17, инвертор 18, элементы И 19 и 20, элементы 21 и 22.задержки. Устройство работает следуквдим образом. При отсутствии сигнала на входе {бестоковая посылка), ток через светодиод 1 и оптически связанный с ним фотодиод 2 не протекает, поэтому на резисторе 7 отсутствует напряжение. Конденсатор 9 не заряжен, и на обоих входах первого дополнительного операционного усилителя 10 также отсутствует напряжение, в результате чего на его выходе, а, соответственно, на выходах аналогового блока 12 памяти и делителей 13 и 14 напряжения - нулевые потенциалы. Ввиду отсутствия напряжения на обоих входах второго дополнительного операционного усилителя 11, на его выходе - нулевой потенциал. Нулевые потенциалы поступают на оба входа основного операционного усилителя 6, в результате чего на его выходе низкий уровень напряже ния, который обеспечивает нулевой потенциал на выходе буферного усилителя 17, При этом с выхода инвертора 18 на оба входа элемента И 20 поступает высокий потенциал, поэтому на выходе элемента И 20 также высокий . потенциал который устанавливает триггер 16 в единичное состояние. Единичное состояние триггера 16 обес печивает подачу: на управляющие входы коммутатора 15 такого кода, при кото ром обеспечивается передача через коммутатор 15 сигнала на инвертирующий вход второго дополнительного опе рационйого усилителя 11 с выхода дополнительногЬ делителя 14 напряжения При отсутствии на вход сигнала (токовой посылки)/ через светодиод 1 а, соответственно, и фотодиод 2 начи нает протекать ток, в результате чего на резисторе 7 Ha4HifaeT- развивать ся напряжение, пропорциональное амплитуде входного сигнала. Когда ток через светодиод 1 достигает значения при котором напряжение на резисторе 7 превысит порог включения основного операционного усилителя 6, определяе мого в этом случае напряжением отсечКи диода 4 и пороговой чувствительностью основного операционного усилителя б, на выходе устройства по является высокий .уровень напряжения, ,а на выходе инвертора 18 - низкий по тенциал. Это приводит к тому, что на выходе элемента И 20 сразу устанавли вается низкий потенциал, а на выходе элемента И 19 низкий потенциал сохра няется (так как элемент 21 задержки . задерживает подачу высокого потенциала на второй вход элемента И 19), состояние триггера 16 при этом не иэменяется (триггер 16 изменяет свое состояние при воздействии на его входы высоких потенциалов), В процессе увеличения амплитуды входного сигнала увеличивается напряжение на резисторе 7 и конденсаторе 9, который заряжается фототоком через диод 5. При этом напряжение на обоих входах первого дополнительного операционного усилителя 10 изменяются по одинаковому закону, в результате чего на его выходе сохраняется нулевой потенциал, состояние аналогового блока 12 памяти не изменяется и на выходах обоих делителей 13 и 14 напряжения нулевые потенциалы. При достижении входным сигналом максимального (установившего) значения, заканчивается заряд конденсатора 9, После этого элемент 21 задержки обеспечивает подачу высокого потенциала и на второй вход элемента И 19. При одновременном наличии высо1 их потенциалов на обоих входах элемента И 19 на его выходе вырабатывается высокий потенциал, который изменяет состояние триггера 16 и устанавливает его в другое состояние (нулевое), Время задержки элемента 21 выбирается таким, чтобы оно превышало максимальную длительность положительного фронта регистрируемого сигнала (но не должно превышать длительности токовой посылки), Нулевое состояние триггера 16 обеспечивает подачу на управляющие входы коммутатора 15 такого кода, при котором обеспечивается передача через коммутатор 15 сигнала на инвертирующий вход второго дополнительного операционного у силителя 11 теперь уже свыхода делителя 13 напряжения. Напряжение на конденсатора 9 воздействует на неинвертирующий вх.од второго дополнительного операционного усилителя 11, в результате чего на его выходе устанавливается потенциал, пропорциональный амплитуде входного сигнала. Потенциал на выкоде второго дополнительного опера даонного усилителя 11 определяет порог срабатывания основного операционного усилителя, а, следовательно, и уровень регистрации входного сигнала. . При уменьшении амплитуды входного сигнала уменьшается ток через светодиод 1, а, следовательно, и через фотодиод 2. Это приводит к уменьшению напряжения на резисторе 7, однако, напряжение на конденсаторе 9 не изменяется, так как диод 5 запирается и исключает разряд конденсатора 9 через резистор 7. Напряжение на выходе второго дополнительного операционного усилителя 11 не изменяет своей величины. При достижении входным сигналом значения, соответствующего установившемуся порогу переключения, основной операционный усилитель 6 вьжлючается и на выходе устройства устанавливается низкий уровень напряжения, а на выходе инвертора 18 - высокий потенциал. Это приводит к тому, что на выходе элемента и 19 сразу устанавливается низкий потенциал, а на выходе элемента И 20 низкий потен- циал сохраняется (так как элемент 22 задержки задерживает подачу высокого потенциала на второй вход элемента И 20), состояние триггера 16 при этом не изменяется. В процессе уменьшения амплитуды ходного сигнала уменьшается напряжеие и на инвертирующем входе первого ополнительного операционного усилителя 10, поэтому на его выходе напряение увеличивается пропорционально разности между амплитудным значением входного сигнала (напряжение на конденсаторе 9) и его уменьшакидимся зна чением (напряжение на резисторе 7), Если амплитуда бестоковой посылки не равна нулю (имеет место утечка) , то на вход аналогового блока 12 памяти с выхода первого дополнительного, опе рационного усилителя 10 поступает на пряжение, максимальное значение которого пропорционально разности меж ду амплитудами токовой и бестоковой посылок. С выхода аналогового блока 12 памяти это напряжение поступает на делители 13 и 14 напряжения. После достижения входным сигналом минимальногь значения (амплитуда, бес токовой посылки) элемент 22 задерж.ки обеспечивает подачу высокого-потенциала и на второй вход элемента И 20. При одновременном наличии высоких потенциалов на обоих входах элемента И 20, на его выходе выраба-тывается высокий потенциал, который изменяет состояние триггера 16 и устанавливает его в единичное состояние,- которое с помощью коммутатора 15 обеспечивает подключение к инвертирующему входу второго дополнительного операционного усилителя 11, выход дополнительного делителя 14 напряжения. При этом состояние основно го операционного усилителя б не йзме няется, так как вновь установленный уровень превышает амплитуду бестоковой посылки на некоторую величину. Время задержки элемента 22 задерж ки выбираетсятаким, чтобы оно превы шало максимальную длительность отрицательного фронта регистрируемого сигнала (но не должно превьлшать длительности бестоковой посылки). Для обеспечения нормального функционирования устройства необходимо, чтобы напряжение на выходе дополнительного делителя 14 напряжения всегда было больше напряжения на выходе делителя 13 напряжения, что обеспечивается при выполнении условия , где коэффициент деления дополнительного делителя 14 напряжения; , - ко эффициент деления делителя 13 напряжения . Наличие в устройства двух уровней регистрации, каядаый из которых располагается в началах фронтов регистри руемого сигнала, их автоматическое переключение, позволяет повысить помехоустойчивость регистрации сигналов с переменными длительностям фронтов, так как в этом случае практически исключается влияние длительности фронтов передаваемого сигнала на величину искажений зарегистрированного сигнала (уровни регистрации располагаются в таких зонах сигнала, которые наименее подвержены искажениям при изменении длительности фронтов сигнала). Поскольку оба уровня регистрации определяются только коэффициентами деления делит елей 13 и 14 напряжения, то иэменени я в широких пределах коэффициента передачи тока оптоэлектронной пары сэетодиод 1 - фотодиод 2 при воздействии дестабилизирунвдих ; факторов не влияют на стабильность уровней регистрации. Абсолютные значения уровней устанавливаются автоматически, в зависимости от амплитуд токовых и бестоковых посылок, а относительное положение уровней регистрации может быть задано с помощью простых регулировок коэффициентов деления делителей напряжения и сохраняется при изменении амплитудных пара-, метров применяемых сигналов. Применение оптоэлектронного входного тройства в приемниках электроннных телеграфныхаппаратов, в переходных и преобразующих телеграфных устройствах, на необслуживаемых телеграфных ретрансляторах, в автоматических телеграфных станциях позволит существенно повысить точность регистрации сигналов, передаваемьах по длинным физическим линиям, в условиях, . когда изменяются не только амплитудные параметры сигналов, но и временные параметры. При этом вообще может быть исключена регулировка входного устройства в условиях эксплуатации ,(при регистрации сигналов с перемен;ными амплитудными и временными параметрами и при действии дестабилизирукадих факторов окружакяцей среды) ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Оптоэлектронное устройство для регистрации телеграфных сигналов | 1985 |

|

SU1246393A1 |

| Оптоэлектронное входное устройство | 1980 |

|

SU898625A1 |

| Оптоэлектронный переключатель | 1982 |

|

SU1103354A2 |

| Устройство для формирования двухполярных сигналов | 1985 |

|

SU1290553A1 |

| Двухуровневый оптоэлектронный переключатель | 1982 |

|

SU1069166A2 |

| Оптоэлектронное устройство для контроля линейного тракта электронного телеграфного аппарата | 1983 |

|

SU1128403A2 |

| Устройство для регистрации импульсов тока | 1980 |

|

SU938422A1 |

| ОПТОЭЛЕКТРОННОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНЫХ СИГНАЛОВ В ЛИНИЮ СВЯЗИ | 2006 |

|

RU2313914C1 |

| Оптоэлектронное входное устройство | 1978 |

|

SU738170A1 |

| Триггер Шмитта | 1987 |

|

SU1422368A1 |

ОПФОЭЛЕКТРОННОЕ ВХОДНОЕ УСЭУ РОЙС7ВО по авт. св. 898625, отличающееся тем, что, .с целью повьщгения помехоустойчивости, в него введены дополнительный делитель напряжения, коммутатор, триггер, два элемента И, два элемента задержки, инвертор и буферный усилитель, выход которого Соединен с входом первого элемента задержки, с первым входом первого элемента И и с входом инвер тора, выход которого соединен с первым входом второго элемента И и с входом второго элемента задержки, выход которого соединен с вторит входом второго элемента И, выхрд которого соединен с первым входом триггера, второй вход которого соединен с выходом первого элемента И, второй вход которого соединен с выходом первого элетлента задержки, причем выходы триггера подкдшчены к управляицим входам коммутатора, первый вход которого соединен с выходом делителя напряжения, первый и второй входы которого подключены соответственно к первсму и вторсолу входам дополнительного делителя напряжения, выход которого соединен с втохшм входом комму татора, выход которого соединен с ийвер гирующим входом второго Дополнительного операционного усилителя, а tf выход основного операционного усилителя подключен к входу буферного уси лителя.- 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Оптоэлектронное входное устройство | 1980 |

|

SU898625A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-07-23—Публикация

1981-06-12—Подача