Изобретение относится к электросвязи и может найти применение в электронных телеграфных аппаратах.

Цель изобретения - повышение точности формирования.

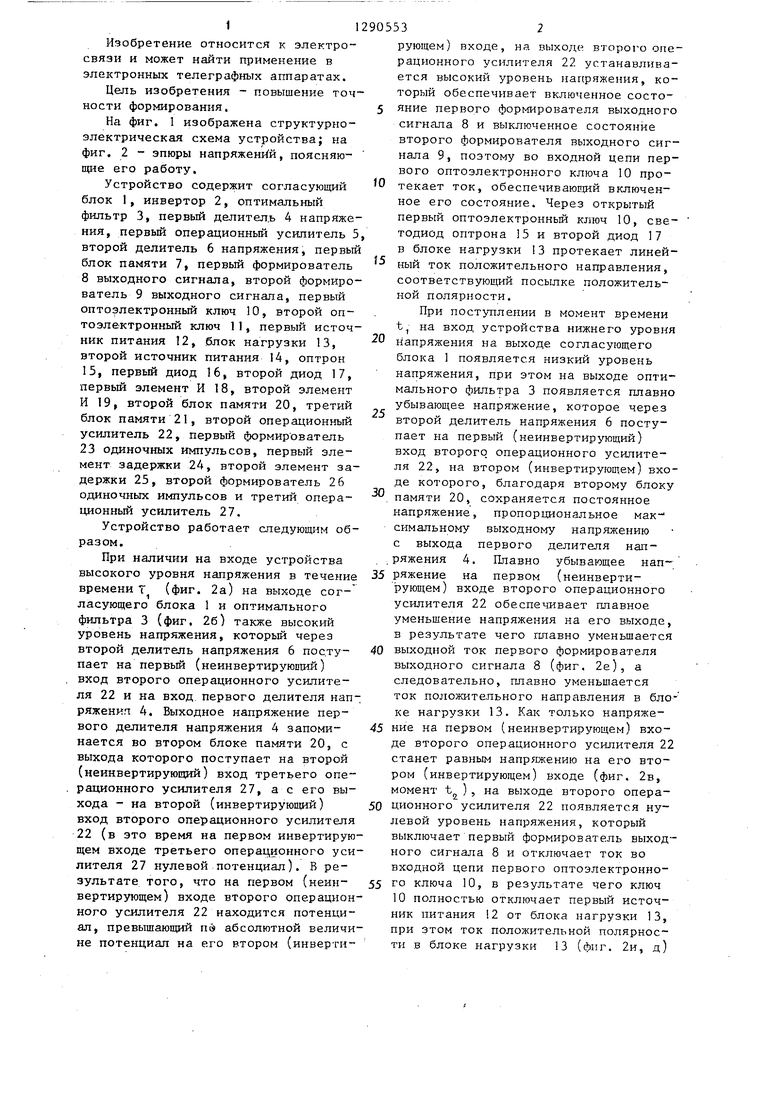

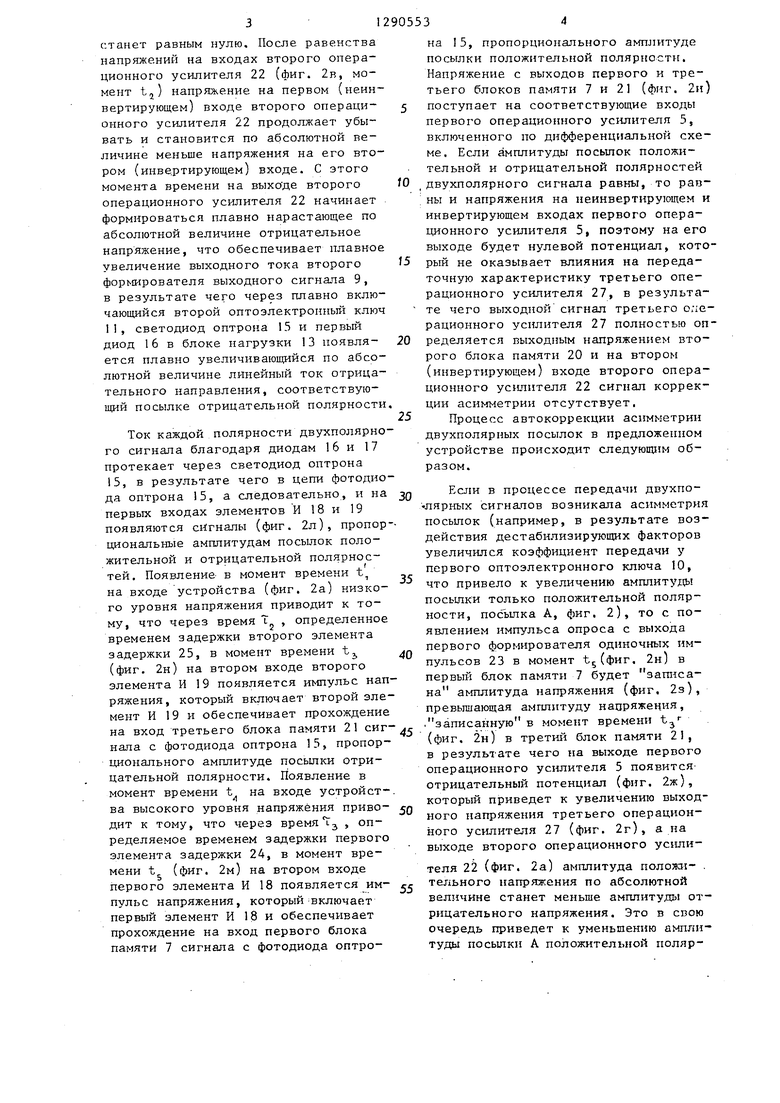

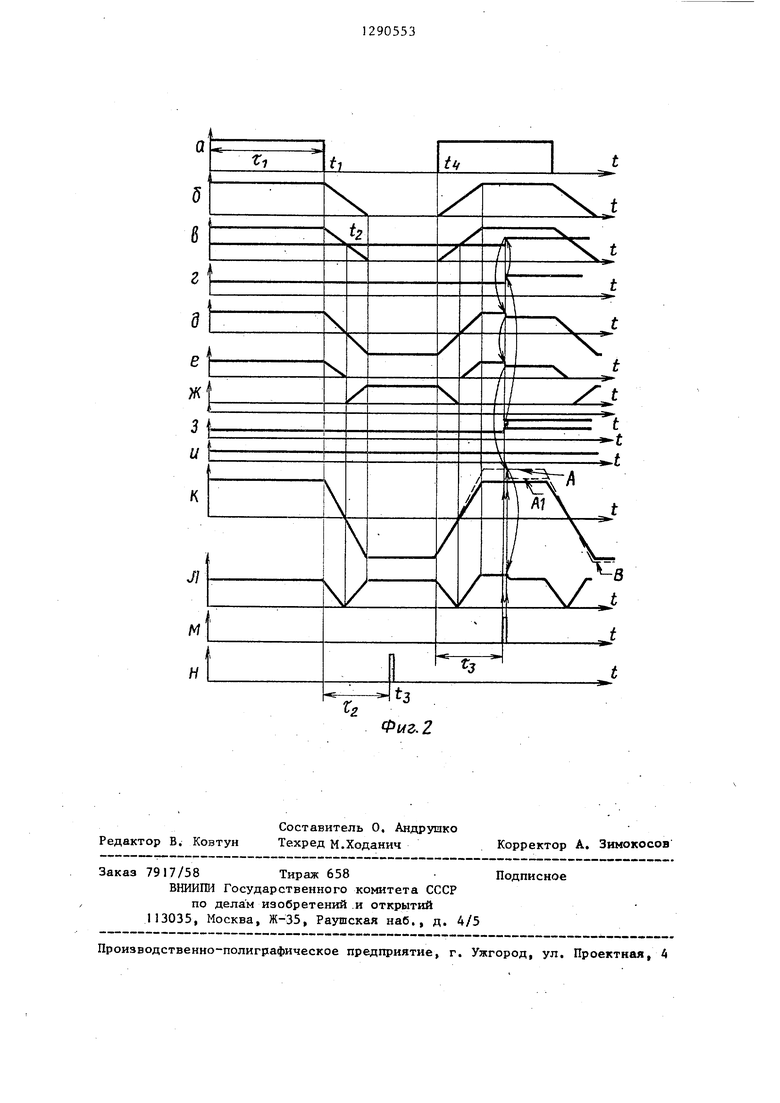

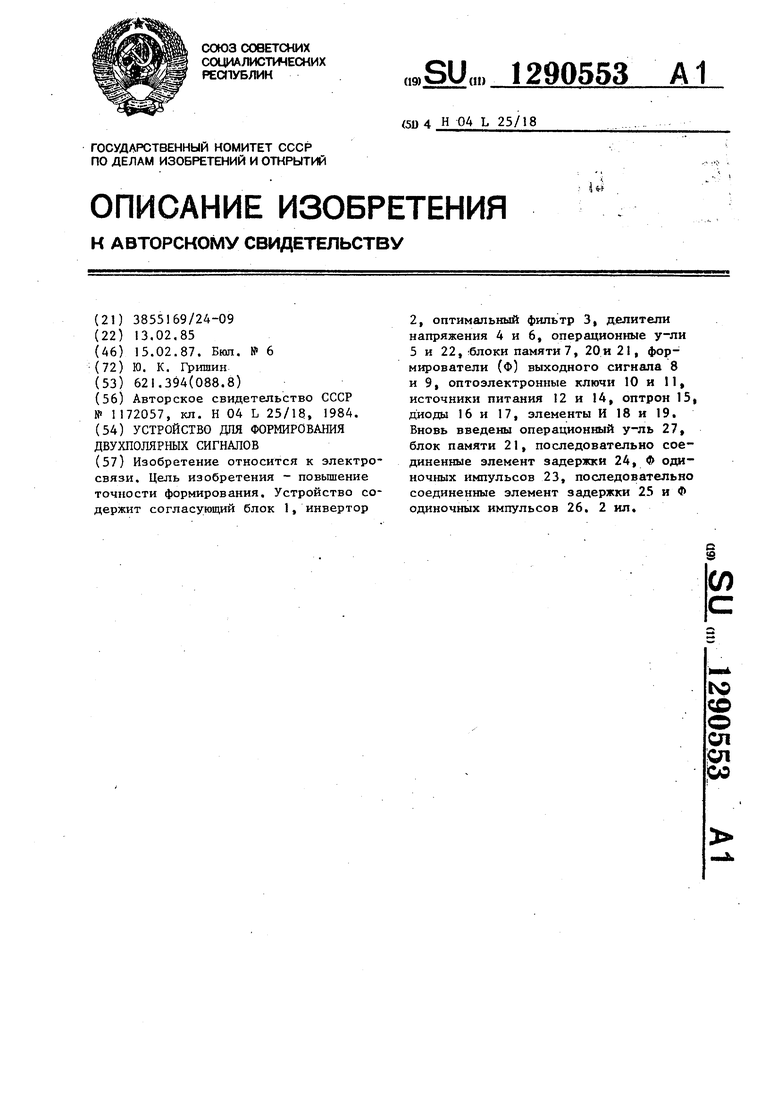

На фиг, 1 изображена структурно- электрическая схема устройства; на фиг. 2 - эпюры напряжений, поясняющие его работу.

Устройство содержит согласующий блок I, инвертор 2, оптимальный фильтр 3, первый делител.ь 4 напряжения, первьй операционный усилитель 5 второй делитель 6 напряжения, первый блок памяти 7, первый формирователь 8 выходного сигнала, второй формирователь 9 выходного сигнала, первый оптоэлектронный ключ 10, второй оп- тоэлектронный ключ 11, первый источник питания 12, блок нагрузки 13, второй источник питания 14, оптрон 15, первый диод 16, второй диод 17, первьш элемент И 18, второй элемент И 19, второй блок памяти 20, третий блок памяти 21, второй операционный усилитель 22, первый формир ователь 23 одиночных импульсов, первый элемент задержки 24, второй элемент задержки 25, второй формирователь 26 одиночных импульсов и третий операционный усилитель 27.

Устройство работает следующим образом.

При наличии на входе устройства высокого уровня напряжения в течение времени Т (фиг. 2а) на выходе сог

ласуювдего блока 1 и оптимального фильтра 3 (фиг. 26) также высокий уровень напряжения, который через второй делитель напряжения 6 поступает на первый (неинвертируюп1ий) вход второго операционного усилителя 22 и на вход первого делителя напряжении 4. Выходное напряжение первого делителя напряжения 4 запоминается во втором блоке памяти 20, с выхода которого поступает на второй (неинвертирующий) вход третьего операционного усилителя 27, ас его выхода - на второй (инвертирующий) вход второго операционного усилителя 22 (в это время на первом инвертирующем входе третьего операционного усилителя 27 нулевой потенциал). В результате того, что на первом (неин- вертирующем) входе второго операционного усилителя 22 находится потенциал, превышающий п абсолютной величине потенциал на его втором (инверти

рующем; входе, на выходе второго операционного усилителя 22 устанавливается высокий уровень напряжения, который обеспечивает включенное состояние первого формирователя выходного сигнала 8 и выключенное состояние второго формирователя выходного сигнала 9, поэтому во входной цепи первого оптоэлектронного ключа 10 протекает ток, обеспечиваюпщй включенное его состояние. Через открытый первый оптоэлектронньш ключ 10, све- тодиод оптрона 15 и второй диод 17 в блоке нагрузки 13 протекает линейный ток положительного направления, соответствующий посылке положительной полярности.

При поступлении в момент времени t, на вход устройства нижнего уровня напряжения на выходе согласующего блока 1 появляется низкий уровень напряжения, при этом на выходе оптимального фильтра 3 появляется плавно убывающее напряжение, которое через второй делитель напряжения 6 поступает на первый (неинвертирующий) вход второго операционного усилителя 22, на втором (инвертирующем) входе которого, благодаря второму блоку памяти 20, сохраняется постоянное напряжение, пропорциональное мак- симальному выxoднo ry напряжению с выхода первого делителя нап- ряжения 4. Плавно убывающее напряжение на первом (неинвертирующем) входе второго операционного усилителя 22 обеспечивает плавное уменьшение напряжения на его выходе, в результате чего плавно уменьшается

выходной ток первого формирователя выходного сигнала 8 (фиг. 2е), а следовательно, плавно уменьшается ток положительного направления в бло ке нагрузки 13. Как только напряжение на первом (неинвертирующем) входе второго операционного усилителя 22 станет равным напряжению на его втором (инвертирующем) входе (фиг. 2в,

момент t ) , на выходе второго операционного усилителя 22 появляется нулевой уровень напряжения, который выключает первый формирователь выходного сигнала 8 и отключает ток во входной цепи первого оптоэлектронного ключа 10, в результате чего ключ 10 полностью отключает первый источник питания 12 от блока нагрузки 13, при этом ток положительной полярности в блоке нагрузки 13 (фиг. 2и, д)

31

станет равным нулю. После равенства напряжений на входах второго операционного усилителя 22 (фиг. 2в, момент tj) напряжение на первом (неинвертирующем) входе второго операци- онного усилителя 22 продолжает убывать и становится по абсолютной величине меньше напряжения на его втором (инвертирующем) входе. С этого момента времени на выходе второго операционного усилителя 22 начинает формироваться плавно нарастающее по абсолютной величине отрицательное напряжение, что обеспечивает плавное увеличение выходного тока второго формирователя выходного сигнала 9, в результате чего через плавно включающийся второй оптоэлектронный ключ II, светодиод оптрона 15 и первый диод 16 в блоке нагрузки 13 появля- ется плавно увеличивающийся по абсолютной величине линейный ток отрицательного направления, соответствующий посылке отрицательной полярности

Ток каждой полярности двухполярно го сигнала благодаря диодам 16 и 17 протекает через светодиод оптрона 15, в результате чего в цепи фотодиода оптрона 15, а следовательно, и на первых входах элементов И 18 и 19 появляются сигналы (фиг. 2л), пропор ционапьные амплитудам посылок положительной и отрицательной полярнос

тей. Появление в момент времени t на входе устройства (фиг. 2а) низкого уровня напряжения приводит к тому, что через время Т, , определенное временем задержки второго элемента задержки 25, в момент времени t (фиг. 2н) на втором входе второго элемента И 19 появляется импульс напряжения, который включает второй элемент И 19 и обеспечивает прохождение на вход третьего блока памяти 21 сигнала с фотодиода оптрона 15, пропорционального амплитуде посьтки отрицательной полярности. Появление в момент времени t на входе устройства высокого уровня напряжения приво- дит к тому, что через время t. , определяемое временем задержки первого элемента задержки 24, в момент времени t (фиг. 2м) на втором входе первого элемента И 18 появляется им

пульс напряжения, который-включает первый элемент И 13 и обеспечивает прохождение на вход первого блока памяти 7 сигнала с фотодиода оптро5JO 0

15

5

о

5

0

Q

5

на 15, пропорционального амплитуде посылки положительной полярности. Напряжение с выходов первого и третьего блоков памяти 7 и 21 (фиг. 2и) поступает на соответствующие входы первого операционного усилителя 5, включенного по дифференциальной схеме. Если амплитуды посьток положительной и отрицательной полярностей ,двухполярного сигнала равны, то равны и напряжения на неинвертирующем и инвертирующем входах первого операционного усилителя 5, поэтому на его выходе будет нулевой потенциал, который не оказывает влияния на передаточную характеристику третьего операционного усилителя 27, в результате чего выходной сигнал третьего оле- рационного усилителя 27 полностью определяется выходным напряжением второго блока памяти 20 и на втором (инвертирующем) входе второго операционного усилителя 22 сигнал коррекции асимметрии отсутствует,

Процесс автокоррекции асимметрии двухполярных посылок в предложенном устройстве происходит следующим образом.

Если в процессе передачи двухпо- -лярных сигна-пов возникала асимметрия посылок (например, в результате воздействия дестабилизирующих факторов увеличился коэффициент передачи у первого оптоэлектронного ключа 10, что привело к увеличению амплитуды посылки только положительной полярности, посьшка А, фиг, 2), то с появлением импульса опроса с выхода первого формирователя одиночных импульсов 23 в момент 15(фиг. 2н) в первый блок памяти 7 будет записана амплитуда напряжения (фиг. 2з), превьшающая амплитуду напряжения, .записанную в момент времени t (фиг. 2н) в трет1Ш блок памяти 21, в результате чего на выходе первого операционного усилителя 5 появится- отрицательный потенциал (фиг. 2ж), который приведет к увеличению выходного напряжения третьего операционного усилителя 27 (фиг. 2г), а на выходе второго операционного ycimHтеля 22 (фиг. 2а) амплитуда положи- . тельного напряжения по абсолютной величине станет меньше амплитуды отрицательного напряжения. Это в свою очередь приведет к уменьшению амплитуды посылки А положительной полярности и увеличению амплитуды посылки отрицательной полярности в блоке нагрузки 13 (фиг. 2к, посьшки А1 , В), т.е. будет осуществлена автокоррек- ция возникшей асимметрии посылок.

Формула изобретения

Устройство для формирования двух- полярных сигналов, содержащее первый операционньй усилитель, первый блок памяти, инвертор, первый и второй элементы И, первые входы которых объединены, последовательно соединен- ные первый делитель напряжения и второй блок памяти, последовательно соединенные согласукяций блок, оптимальный фильтр, второй делитель напряжения и второй операционный усилитель, выход которого подключен к входам первого и второго формирователей выходного сигнала, выходы которых подключены к первым выводам соответственно первого и второго оптоэлектронных ключей, вторые выводы которых соединены соответственно с положительным выводом первого источника питания и отрицательным выводом второго источника питания, положительный вывод которого соединен с отри- дательным выводом первого источника питания и с первым выводом блока нагрузки, второй вывод которого соединен с анодом первого диода и катодом второго диода, анод которого соединен с третьим выводом второго опто- электронного ключа и с катодом свё

ю 15 20 5

0

5

тодиода оптрона, анод которого соединен с третьим выводом первого опто- электронного ключа и с катодом первого диода, катод фотодиода оптроиа соединен с. общей тиной, вход согласующего Злока соединен с входом инвертора, а выход второго делителя напряжения подключен к входу первого делителя напряжения, отличающееся тем, что, с целью повышения точности формирования, введены третий операционный усилитель, третий блок памяти, последовательно соединенные первый элемент задержки и первый формирователь одиночных импульсов, последовательно соединенные второй элемент задержки и второй формирователь одиночных импульсов, выход которого и выход первого формирователя одиночных импульсов подключены к вторым входам соответственно первого и второго элементов И, выходы которых через соответственно первый и третий блоки памяти подключены к входам первого операционного усилителя, выход которого подключен к первому входу третьего операционного усилителя, второй вход и выход которого соединены соответственно с выходом второго блока памяти и с вторым входом второго операционного усилителя, вход согласующего блока соединен с входом первого элемента задержки, выход инвертора подключен к входу второго элемента задержки, а первый вход первого элемента И соединен с анодом фотодиода оптрона.

L HlKfHi

l-&

а

б б

г 1

ж

3

и к

J/

м н

Редактор В. Ковтун

Составитель О, Андрушко Техред М.Ходанич

Заказ 7917/58 Тираж 658

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг. 2

Корректор А, Зимокосов

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Выходное телеграфное устройство | 1984 |

|

SU1172057A1 |

| Оптоэлектронное входное устройство | 1980 |

|

SU898625A1 |

| Оптоэлектронное входное устройство | 1981 |

|

SU1030983A2 |

| Устройство для регистрации импульсов тока | 1980 |

|

SU938422A1 |

| Устройство согласования | 1983 |

|

SU1188900A2 |

| Источник питания электроразрядных импульсных лазеров | 1983 |

|

SU1277358A1 |

| Способ преобразования перемещения в длительность импульсов и устройство для его осуществления (его варианты) | 1984 |

|

SU1227939A1 |

| Двухуровневый оптоэлектронный переключатель | 1982 |

|

SU1069166A2 |

| ОПТОЭЛЕКТРОННОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНЫХ СИГНАЛОВ В ЛИНИЮ СВЯЗИ | 2006 |

|

RU2313914C1 |

| Выходное телеграфное устройство | 1981 |

|

SU1019658A1 |

Изобретение относится к электросвязи. Цель изобретения - повьшение точности формирования. Устройство содержит согласующий блок 1, инвертор 2, оптимальный фильтр 3, Д|елители напряжения 4 и 6, операционные у-ли 5 и 22, :блоки памяти 7, 20и21, формирователи (Ф) выходного сигнала В и 9, оптоэлектронные ключи 10 и П, источники питания 12 и 14, оптрон 15, диоды 16 и 17, элементы И 18 и 19. Вновь введены операционный у-ль 27, блок памяти 21, последовательно соединенные элемент задержки 24, Ф одиночных импульсов 23, последовательно соединенные элемент задержки 25 и Ф одиночных импульсов 26. 2 ил. Isp UD СЛ сд ОО

| Выходное телеграфное устройство | 1984 |

|

SU1172057A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-02-15—Публикация

1985-02-13—Подача