тий информационный входы которого подключены соответственно к выходу элементов ИЛИ группы и к выходу блока формирования адреса, информационный вход которого подключен к выхо:ду второго счетчика, причем управляющие выходы аналого-цифровых преобразователей всех каналов объединены и подключены- к первому входу блока управления, третий выход которого соединен с управляющими входами регистров сомножителей всех каналов, выход блока задания кода единицы соединен с первым входом блока умножения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

| Многоканальный многомерный цифровой коррелометр | 1985 |

|

SU1305714A1 |

| Цифровой коррелометр | 1979 |

|

SU783797A1 |

| Многоканальный многомерный цифровой коррелометр | 1984 |

|

SU1187177A1 |

| Многоканальный цифровой коррелометр | 1985 |

|

SU1262523A1 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Многофункциональный цифровой коррелометр | 1979 |

|

SU826361A1 |

| Цифровой коррелометр | 1985 |

|

SU1298767A1 |

| Цифровой коррелометр | 1983 |

|

SU1113806A1 |

| Многоканальный цифровой коррелометр | 1985 |

|

SU1297075A1 |

МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ КОРРЕЛОМЕТР, содержащий блок памяти , информационный вход и информационный выход 1«оторого соединены соответственно с -выходом и первым информационным входом арифметического блока, второй информационный вход которого соединен с выходом блока умножения, регистр адреса, аналого-цифровые преобразователи по числу каналов, информационный выход каждого из которых подключен к информационным входам первого и второго регистров сомножителей своегоканала, а входы являются соответствуюадимй входами коррелометра, одноименные выходы регистров сомножителей - всех каналов объединены и подключены соответственно к.первому и второму входам блока умножения, о т л ичающийся тем, что, с целью . расширения его функциональных возможностей, за счет одновременного - вычисления комплекса статистических характеристик по одной реализации 7 случайного процесса, введены регистр данных, блок задания кода единицы, компаратор, первый и второй коммутаторы, груп.па элементов ИЛИ, первый и второй преобразователи кодов, блок задания начальных условий, пер-, вый и второй счетчики, блок формирования адреса и блок постоянной памяти, выход которого соединен со вторым информационным входом арифметического блока, а вход блока постоян ной памяти объединен с первым информационным входом первого коммутатора и подключен к выходу арифметического блока, выход первого коммутатора соединен с адресным входом блока памяти, информационный выход которого соединен с первым входом блока управления, первый и второй выходы которого соединены соответственно с первым и вторым управляющими входами арифметического блока, второй (Л вход блока управления объединен с управляющим входом блока формирова1НИЯ адреса и подключен к первому выходу регистра данных, второй выход которого объединен с первым информационным входом второго коммутатора и подключен к первому входу компаратора, выход которого соединен с уп. равляющим входом второго коммутатора, второй информационный вход которого объединен с вторым входом компаратора, входом блока задания начальных со условий и подключен к выходу первого преобразователя кодов вход которого соединен с третьим выходом регистра IsD данных, выход второго коммутатора соединен с входом второго преобразователя кодов, первый и второй выходы которого соединены соответственно с первым и вторым входами элементов ИЛИ- группы, третий вход которых подключен к выходу первого счетчика, вход которого соединен с выходом блока задания начальных условий, четвертый вход элементов ИЛИ группы соединен с первым выходом регистра адреса, второй выход которого подключен к второму ин Ьормационному входу первого коммутатора, управлякяцнй и тре

Изобретение относится к цифровой электроизмерительной технике и предназначено для определения в реальном масштабе времени одновременно по одной реализации комплекса статистических характеристик случайного процесса: матрицы корреляционных функций, автокорреляционных функций взаимно корреляционных функций, дифференциальных законов распределения а также для определения по корреляционным функциям спектральной плотност.и мощности. Изобретение может быть использовано в системах автоматического управления, технологического контроля, обработки информации и т.д. , .

Известно устройство, содержащее аналого-цифровой преобразователь, блок памяти, блок оценки характеристик распределения вероятностей слу чайных величин, первый вход которого подключен к выходу аналого-цифрового преобразователя, а выход - к блоку памяти, второй вход соединен с первым выходом блока управления, первый вьгход которого подключен к управляющему входу аналого-цифрового преобразователя. Кроме того, устройство содержит блок суммирования Cl

Недостатком является то, что устройство не позволяет одновременно определять комплекс статистических характеристик по одной реализации случайного процесса.

Наиболее близким по технической сущности к предлагаемому является многоканальный цифровой коррелометр, содержащий блок управления, выход которого через дешифратор подключен к блоку памяти, выходом соединенным с сумматором, вход которого подключен к выходу блока умножения, выход сумматора соединен с входом блока памяти, аналого-цифровые преобразователи по числу каналов, выход каждого из которых подключен к входам регистров сомножителей своего канала, блок выбора сомножителей, ВХОДЫ которого соединены с выходами младших разрядов адресного счетчика, а выходы подклю;чены соответственно к первым входам элемен2

тов и каждого канала, вторые входы которых подключены к выходам соответствующих регистров сомножителей своего канала, а третьи входы объединены и подключены к выходам блока управления, выходы элементов И объединены и подключены к входам блока умножения.

Блоки элементов И и блок выбора сомножителей можно рассматривать как управляемый коммутатор, который в свою очередь, можно реализовать на регистрах с тремя состояниями на выходе, объединив их выходы в группы и подключив к входам блока умножения. Функции сумматора могут быть выполнены арифметическим блоком.

Коррелометр позволяет в реальном масштабе в.ремени одновременно по одной реализации случайного процесса вычислять п корреляционных функций ( матрицу корреляционных функций ), где п - число обрабатываемых случайных процессов. Блок памяти при этом с помощью младших разрядов 5 адресного счетчика делится на (секций) по количеству вычисляемых кривых, а старшие разряды адресного счетчика делят, каждую зону на m адресов по количеству вычисляемых в каждой кривой ординат 2 и tsj.

Однако указанное устройство не позволяет определять распределение плотности вероятностей и спектральную плотность мощности, т.е. обла- . дает о раниченными функциональными возможностями. Кроме того, жесткое деление блока памяти на п секций по m ячеек в каждой секции не позволяет при изменении числа обрабатываемых процессов оперативно Менять число секций и ординат в секции, а также уменьшать число ординат, что часто необходимо при оперативном анализе...

Цель изобретения - расширение функциональных возможностей многоканального коррелометра за счет одновременного вычисления кс5мплекса статистических характеристик по одной реализации случайного процесса.

Поставленная цель достигаетЬя тем, что в многоканальный цифровой

коррелометр, содержащий блок памяти информационный вход и информаци6н- ный выход которого соединены соответственно с выходом и первым информационным входом арифметического блока, второй информационный вход которого соединен с выходом блока умножения, регистр адреса, аналогоцифровые преобразователи по числу . каналов, информационный выход каждого из которых подключен к информационным входам первого и второго регистров сомножителей своего канала, а входы являются соответствующими входами коррелометра, одноимённые выходы регистров сомножителей всех каналов объединены и подключены соответственно к первому и второму входам блока умножения, введены регистр данных, блок задания кода единицы компаратор, первый и второй о коммутаторы. Группа элементов ИЛИ, первый и второй преобразователи кодов, блок задания начальных условий первый и второй счетчики, блок форт мирования адреса и блок постоянной . памяти, выход которого соединен со вторым информационным входом арифметического блока, а вход блока постоянной памяти объединен с первым информационным входом первого коммутатора и подключен к выходу арифметического блока, выход первого коммутатора соединен с адресным входом блока памяти, информационный выход которого соединен с первым входом блока управления, первый и второй выходы которого соединены соответственно с первым и вторым управляющими входами арифметического блока, второй вход блока управления объединен с управляющим входом блока формирования адреса и подключен к первому выходу регистра данных, второй выход которого объединен с первым информационным входом второго коммутатора и подключен к первому входу компаратора, выход которого соединен с управляющим входом второго коммутатора, второй информационный вход которого объединен с вторым входбм компаратора, входом блока задания начальных условий и подключен к выходу первого преобразователя кодов, вход которого Соединен с третьим выходом регистра данных, выход второго коммутатора соединен с входом второго преобразователя кодов, первый и второй выхО ды которого сбединены соответственно с первым и вторым входаи н элементов ИЛИ группы, третий вход которых подключен к выходу первого счетчика, вход которого соединен с выхоДсм .Л5лока эгшания начёшьных условий, четвертый вход элементов ИЛИ группы Соединен с -первым выходом регистра адреса, второй выход которого подключей к- второму информационному входу первого коммутатора, управляющий и третий информационный входы которого подключены соответственно . к выходу элементов ИЛИ группы и к выходу блока формирования адреса, информационный вход которого подключен к выходу второго счетчика, причем управляющие выходы аналого-цифровых преобразователей всех каналов

0 объединены и подключены к первому входу блока управления, третий выход которого соединен с, управляющими входами регистров сомножителей всех каналов, выход блока задания кода

5 единицы соединены с первым входом блока умножения.

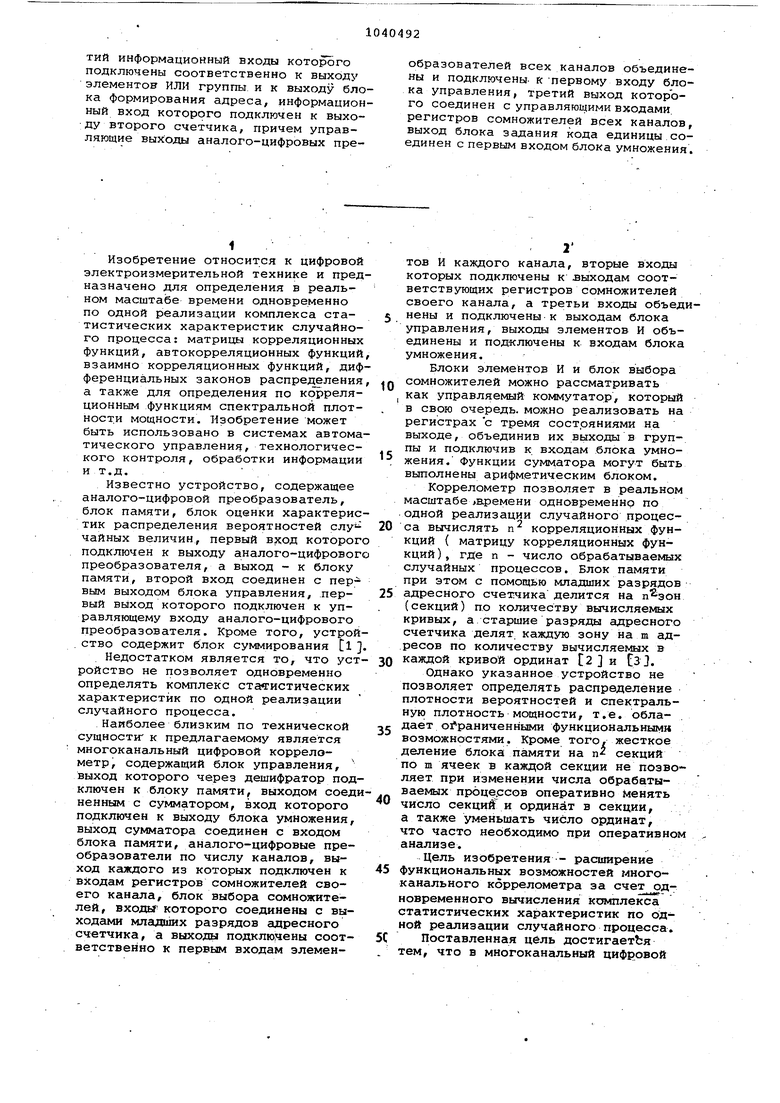

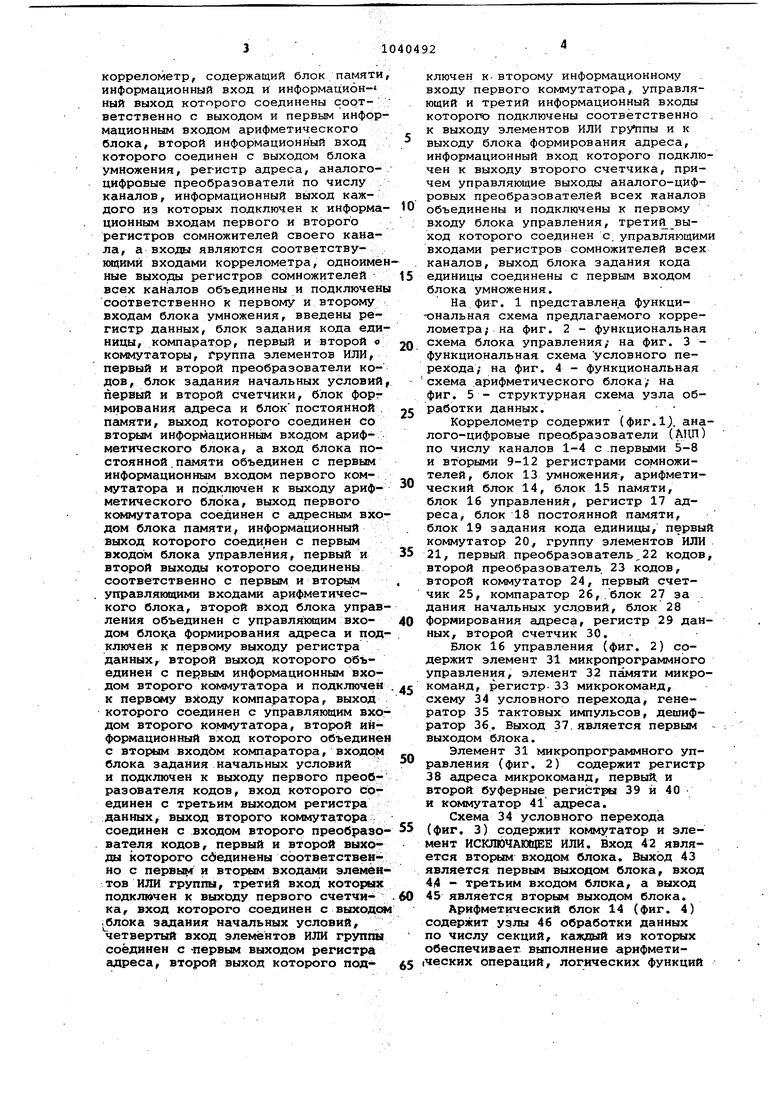

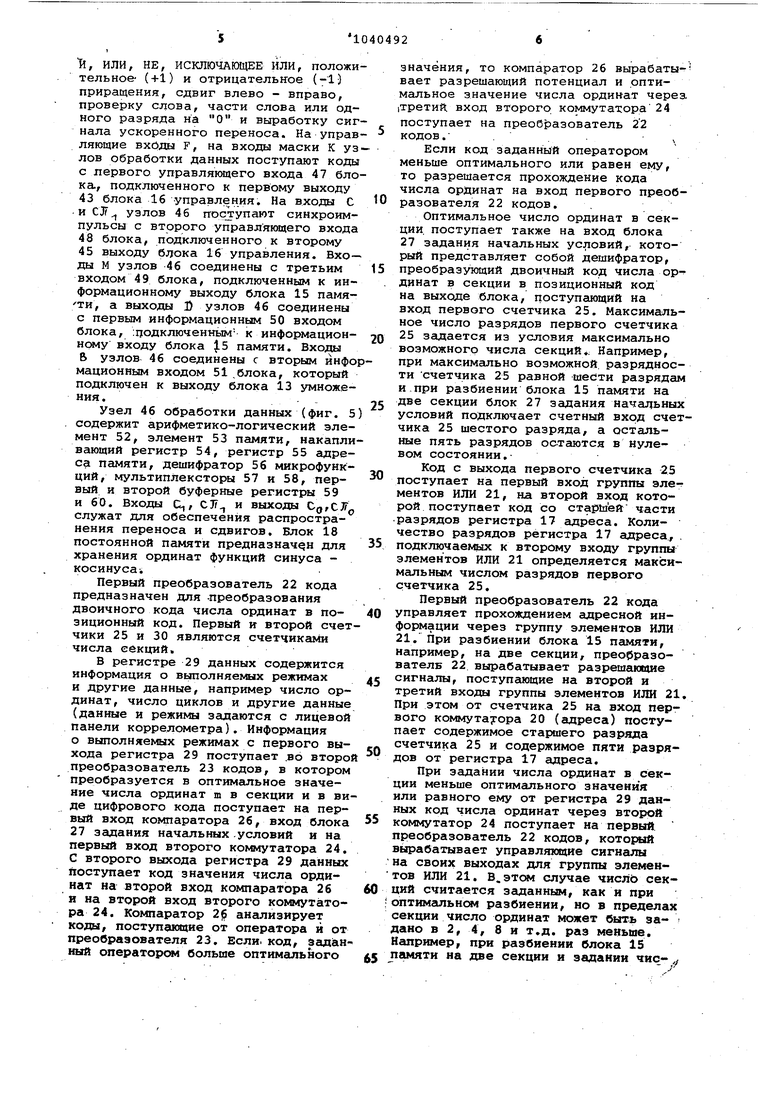

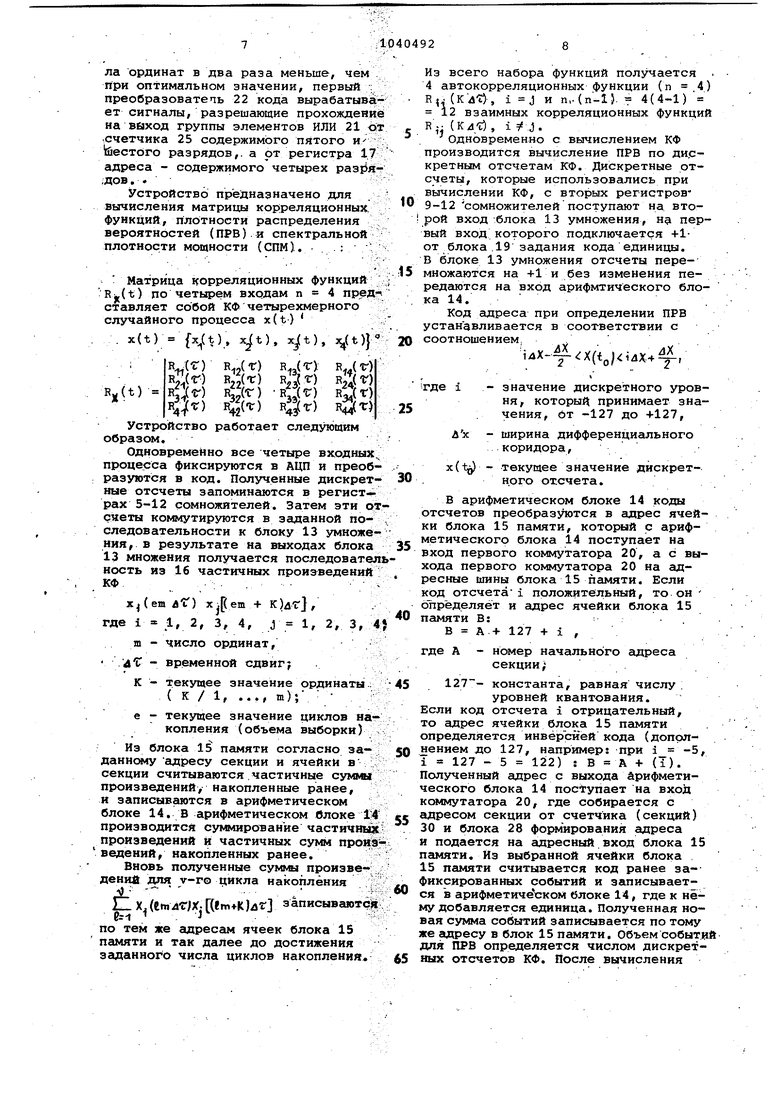

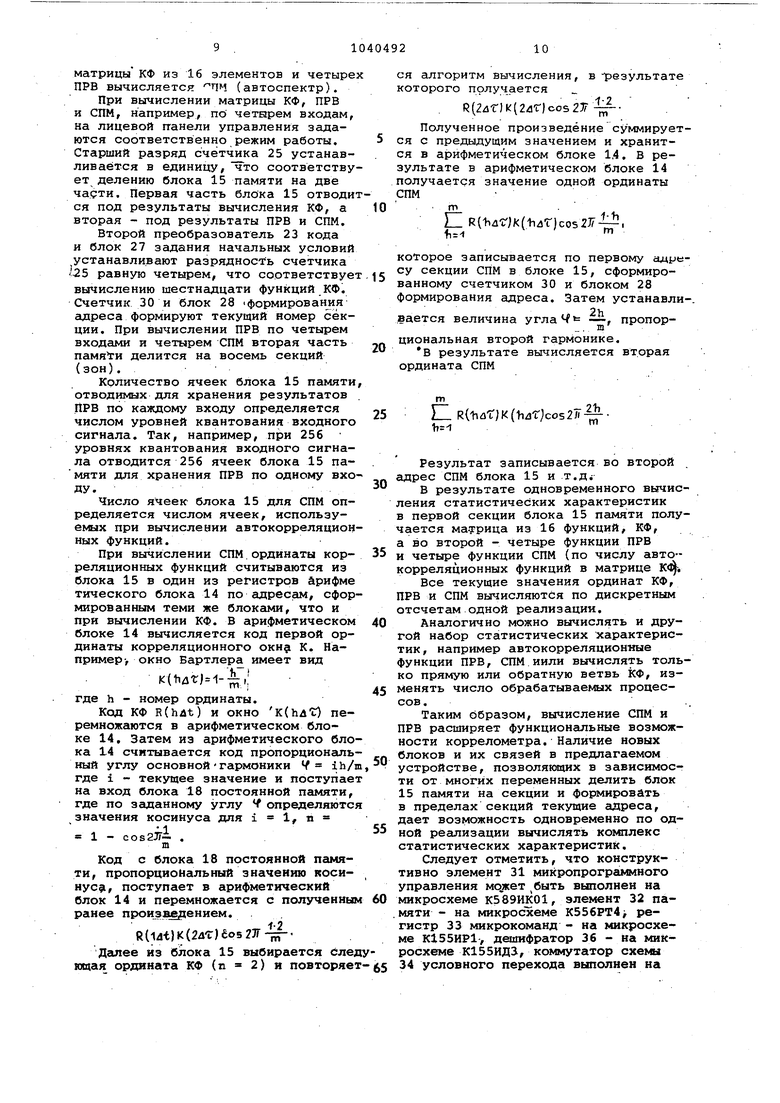

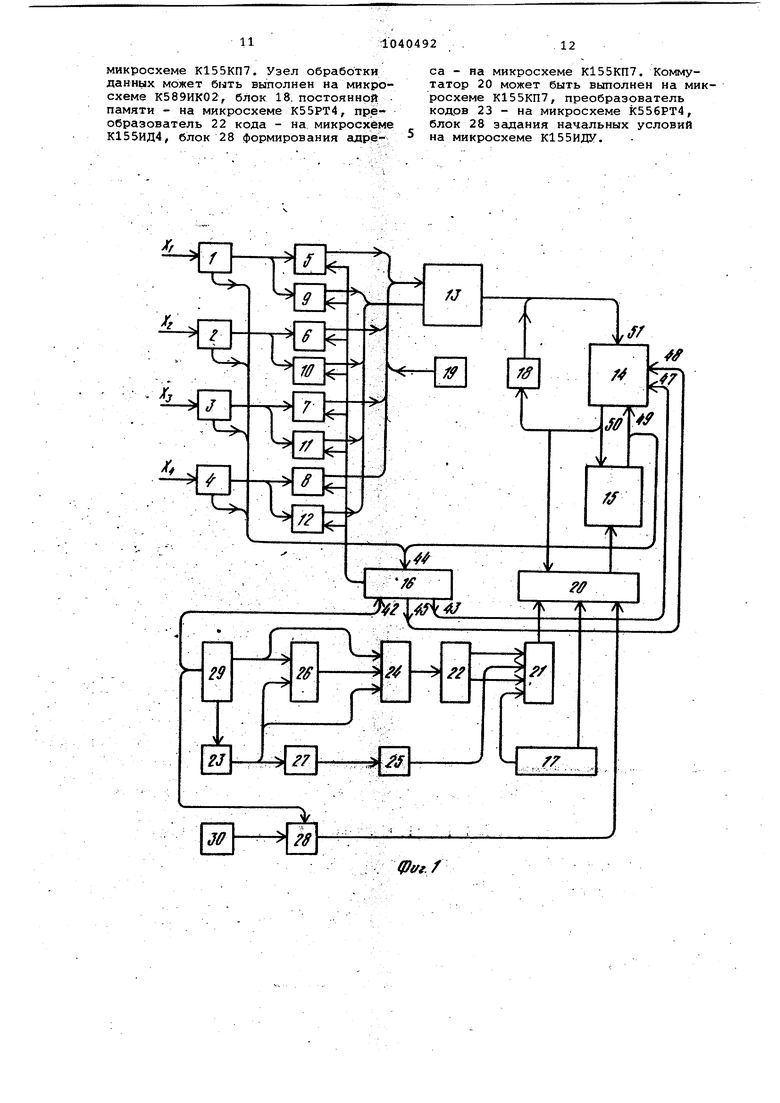

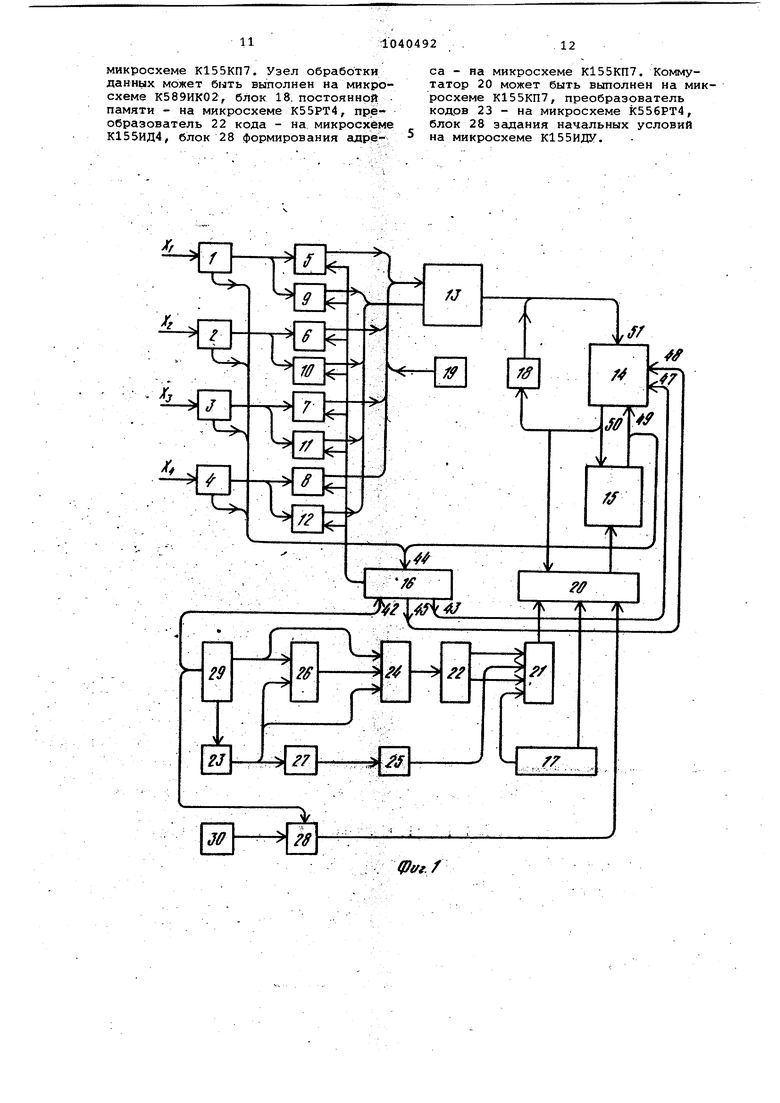

На.фиг. 1 представлена функци-ональная схема предлагаемого коррелометра; на фиг. 2 - функциональная схема блока управления; на фиг. 3 0функциональная схема условного перехода; на фиг. 4 - функциональная схема арифметического блока; на фиг. 5 - структурная схема узла обработки данных. 5

Коррелометр содержит (фиг.1), аналого-цифровые преобразователи (АДП) по числу каналов 1-4 с .первыми 5-8 и вторыми 9-12 регистрами сомножителей, блок 13 умножения-, арифмети0ческий блок 14, блок 15 памяти, блок 16 управлений, регистр 17 адреса, блок 18 постоянной памяти, блок 19 задания кода единицы, первый коммутатор 20, группу элементов ИЛИ

5 21, первый преобразователь,22 кодов, второй преобразователь 23 кодов, второй коммутатор 24, первый счетчик 25, компаратор 26,.блок 27 за . Дания начальных усл.овий, блок 28 формирования адреса, регистр 29 дан0ных, второй Счетчик 30.

Блок 16 управления (фиг. 2) содержит элемент 31 микропрограммного управления, элемент 32 памяти микрокоманд, регистр-33 микрокоманд,

5 схему 34 условного перехода, генератор 3 5 тактовых импульсов, дешифратор 36. Выход 37. является первым выходом блока.

Элемент 31 микропрограммного уп0равления (фиг. 2) содержит регистр 38 адреса микрокоманд, первый, и второй буферные регистры 39 и 40 и коммутатор 41 адреса.

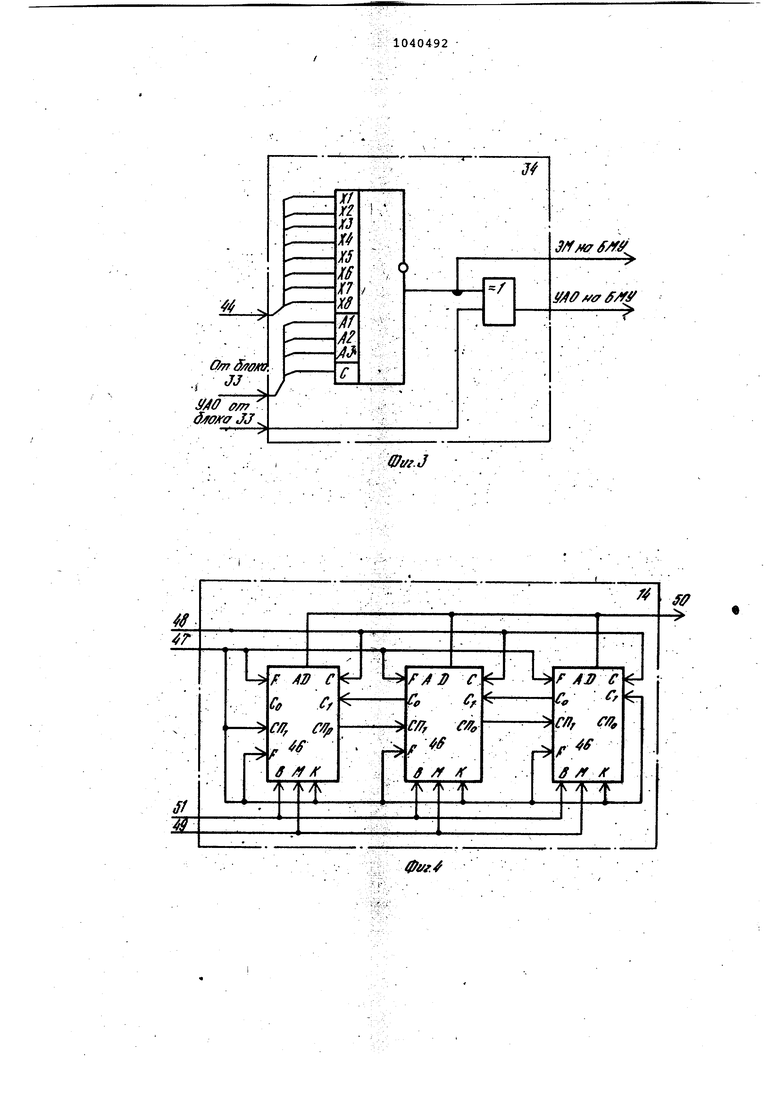

Схема 34 условного перехода

5 (фиг. 3) содержит коммутатор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. Вход 42 является вторым входом блока. Выход 43 является первым выходом блока, вход

44- третьим входом блока, а выход

45является вторым выходом блока.

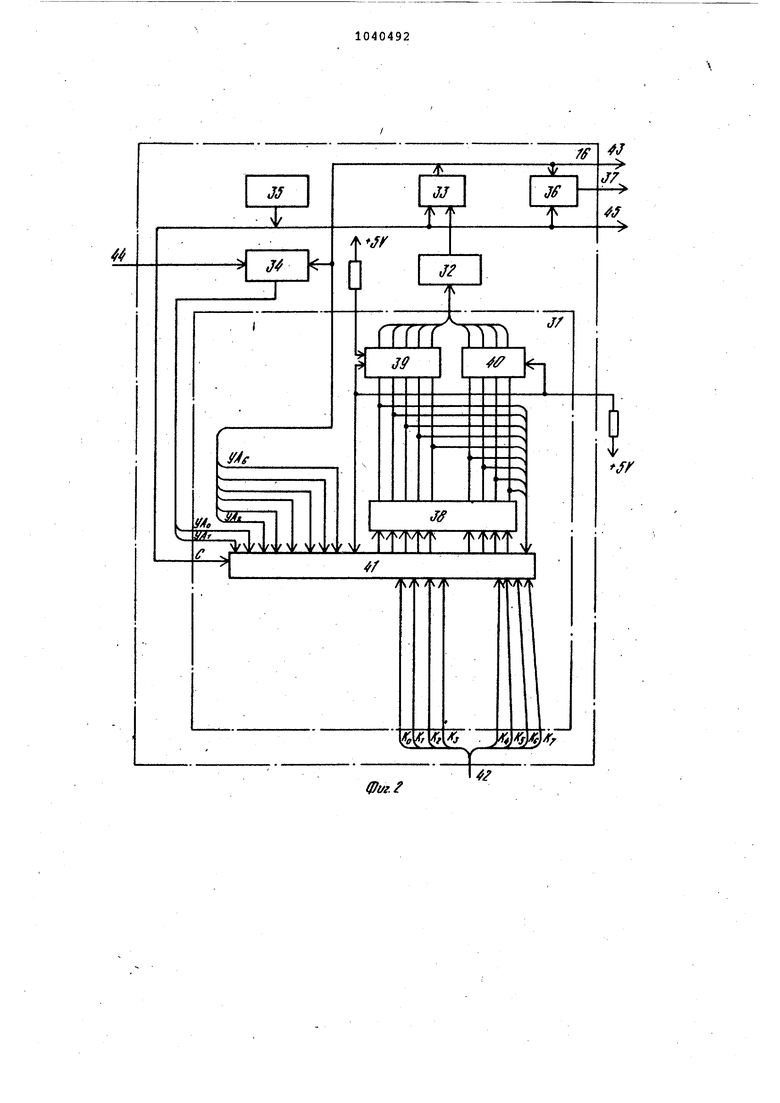

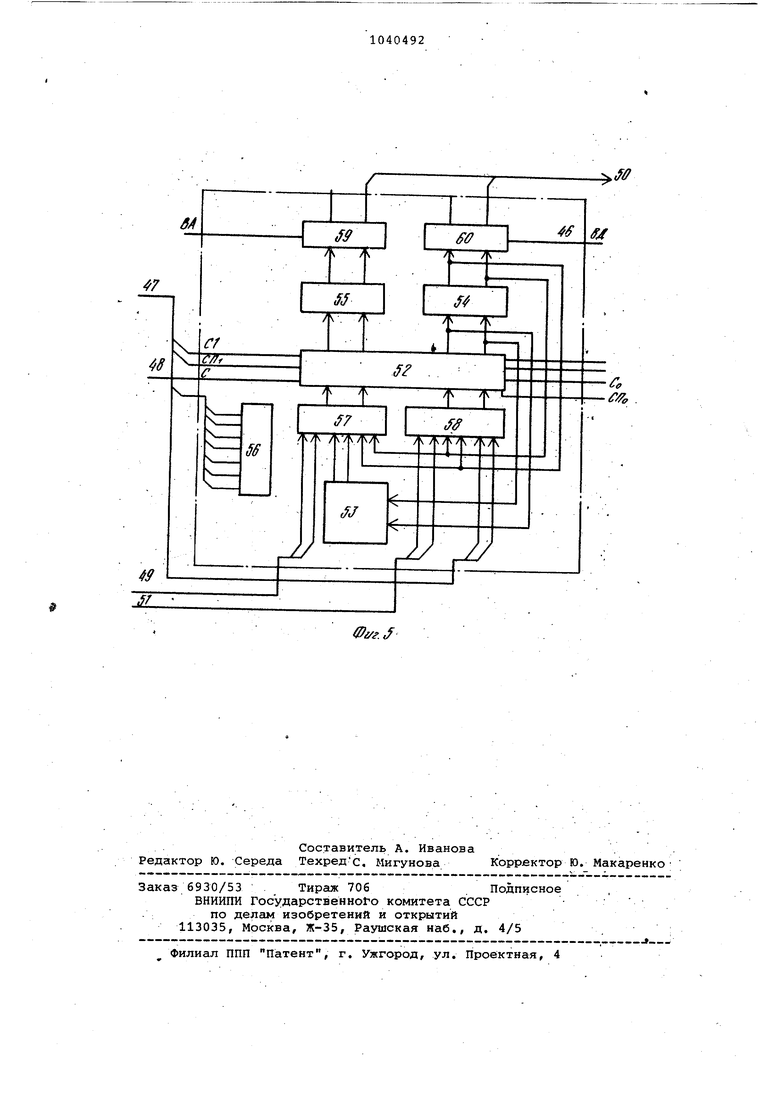

0 Арифметический блок 14 (фиг. 4)

содержит узлы 46 обработки данных по числу секций, каждый из которых обеспечивает выполнение арифмети|Ческих операций, логических функций

5

Tl, ИЛИ, HE, ИСКЛЮЧАЮЩЕЕ ИЛИ, положительное- (+1) и отрицательное (-1-1 приращения, сдвиг влево - вправо, проверку слова, части слова или одного разряда на О и ВБгработку сигнала ускоренного переноса. На управляющие входы F, на входы маски К узлов обработки данных поступают коды с первого управлякадего входа 47 блока, подключенного к первому выходу 43 блока 16 управления. На входы С

И СЛ узлов 46 поступают синхроимпульсы с второго управляющего входа 48 блока, подключенного к второму 45 выходу блока 16 управления. Входы М узлов 46 соединены с третьим входом 49 блока, подключенным к информационному выходу блока 15 памяти, а выходы D узлов 46 соединены с первым информационным 50 входом блока, :подключеннь1м- к информационному входу блока J.5 памяти. Входы В узлов 46 соединены с вторым инфомационным входом 51 .блока, который подключен к выходу блока 13 умножения.

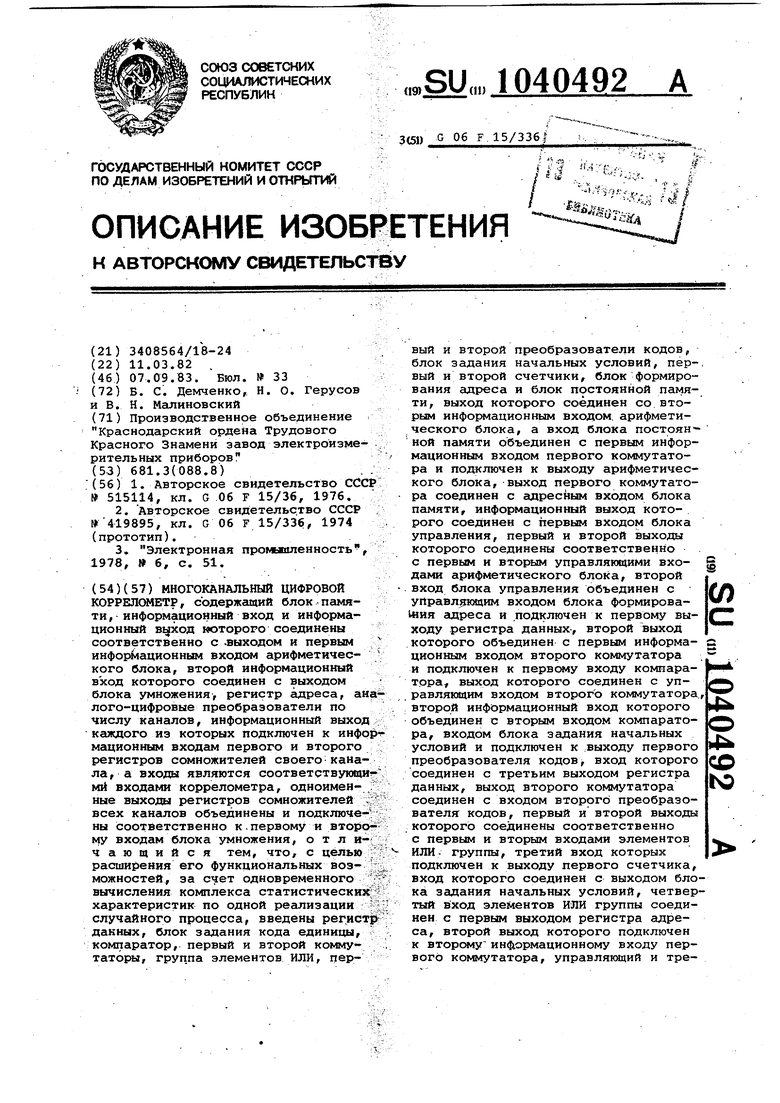

Узел 46 обработки данных (фиг. 5 содержит арифметико-логический элемент 52, элемент 53 памяти, накапливающий регистр 54, регистр 55 гщреса памяти, дешифратор 56 микрофункций, мультиплексторы 57 и 58, первый и второй буферные регистры 59 и 60. Входы СЦ, CJf и выходы C-fffCJif, служат для обеспечения распространения переноса и сдвигов. Блок 18 постоянной памяти предназначен для хранения ординат функций синуса косинуса.

Первый преобразователь 22 кода предназначен для -преобразования двоичного кода числа ординат в позиционный код. Первый к второй счетчики 25 и 30 являются счетчиками числа секций.

В регистре 29 данных содержится информация о выполняемых режимах и другие данные, например число ординат, число циклов и другие данные (данные и режимы задаются с лицевой панели коррелометра). Информация о выполняемых режимах с первого выхода регистра 29 поступает .во второ преобразователь 23 кодов, в котором преобразуется в оптимальное значение числа ординат m в секции и в виде цифрового кода поступает на первый вход коштаратора 26, вход блока 27 задания начальных .условий и на первый вход второго коммутатора 24. С второго выхода регистра 29 данных поступает код значения числа ординат на второй вход компаратора 26 и на второй вход второго коммутатора 24. Компаратор 2$ ангшизнрует коды, поступаклцие от оператора и от преобразователя 23. Бсли код, заданный оператор ж больше оптимального

начения, то компаратор 26 вырабатыает разрешающий потенциал и оптиальное значение числа ординат через рети{1 вход второго коммутатора 24 оступает на преобразователь 22 кодов. . .ч

Если код заданный оператором еньше оптимального или равен ему, то разрешается прохождение кода исла ординат на вход первого преобазователя 22 кодов.

Оптимальное число ординат в секции, поступает также на вход блока 27 задания начальных условий, который представляет собой дешифратор, преобразующий двоичный код числа ординат в секции в позиционный код на выходе блока, поступающий на вход первого счетчика 25. Максимальное число разрядов первого счетчика 25 задается из условия максимально возможного числа секций. Например, при максимально возможной разрядности счетчика 25 равной шейти разрядам и.при разбиении блока 15 памяти на две секции блок 27 задания начальных условий подключает счетный вход счетчика 25 шестого разряда, а остальные пять разрядов остаются в нулевом состоянии.

Код с выхода первого счетчика 25 поступает на первый вход группы эле-г ментов ИЛИ 21, на второй вход которой поступает код со старшей части разрядов регистра 17 адреса. Коли- чество разрядов регистра 17 адреса, . подключаемь1х к второму входу группы элементов ИЛИ 21 определяется максимальным числом разрядов первого счетчика 25.

Первый преобразователь 22 кода управляет прохождением адресной информации через группу элементов ИЛИ 21. При разбиений блока 15 пг1мяти, например, на две секции, преобразователБ 22 вырабатывает разрешающие сигналы, поступающие на второй и третий входы группы элементов ИЛИ 21. При этом от счетчика 25 на вход первого коммутатора 20 (адреса) поступает содержимое старшего разряда счетчика 25 и содержимое пяти разря дов от регистра 17 адреса.

При задании числа ординат в секции меньше оптимального значения или равного ему от регистра 29 данных код числа ординат через второй коммутатор 24 поступает на первый преобразователь 22 кодов, который вырабатывает управляющие сигналы на своих выходах для группы элементов ИЛИ 21. В.этсж случае числь секций считается зсланным, как и при оптимальнс || разбиении, но в пределах секции число ординат может быть заано в 2, 4, В и т.д. раз меньше. Например, при разбиении блока 15 памяти иа две секции и задаиии чис-,/

ла ординат в два раза меньше, чем при оптимальном значении, первый преобразоватепь 22 кода вырабатывает сигналы, разрешающие прохождение на вйход группы элементов ИЛИ 21 от счетчика 25 содержимого питого и toecTdro разрядов,, а от регистра 17 адреса - содержимого четырех ,дов. .

Устройство прёйназначено для вычисления матрицы корреляционных, функций, плотности распределения вероятностей (ПРВ) и спектраль ной плотности мощности (СПМ).. ;

Матрица корреляционных функций Rjj(t) по четырем входам п 4 представляет собой КФ четырехмерного случайного процесса x(t}

. x(t) fx(t), ), ),(t)} Устройство работает следующим образом. Одновременно все четыре входных процесса фиксируются в АЦП и преоб разуются в код. Полученные дискрет ные отсчеты запоминаются в регистрах 5-12 сомножителей. Затем эти о счеты коммутируются в заданной последовательности к блоку 13 умноже НИН, в результате на выходах блока 13 множения получается последовате ность из 16 частичных проиэ ведений КФ. K)ArJ/ х ( em Л) X jpem + где i 1, 2, 3, 4, J 1, 2, 3, m - число ординат, аТ - временной сдвиг; К - текущее значение ординаты ( К / 1, ..., т); - е - текущее значение циклов на копления (объема выборки) Из блока 15 памяти согласно заданно адресу секции и ячейки в секции считываются.частичные сугты произведений/ накопленные ранее, и записываются в арифметическом блоке 14. В арифметическом влоке 1 производится суммирование частичны произведений и частичных сумм прои ведений, накопленных ранее. Вновь полученные сумквл произведений для v-ro цикла накопления X(em-ar/Xj ( записываются по тем же адресам ячеек блока 15 памяти и так далее до достижения заданного числа циклов накопления.

Из всего набора функций получается . 4 автокорреляционных функции (п 4) К ИКЛ-с), и п,.(п-1). - 4(4-1) 12 взаимных корреляционных функций R.- (К 40, i J.

Одновременно с вычислением КФ производится вычисление ПРВ по дискретным отсчетам КФ. Дискретные отсчеты, которые использовались при вычислении КФ, с вторых регистров

9-12 сомножителей поступгиот на второй вход блока 13 умножения, н первый вход которого подключается +1от блока.19 задания кода единицы. В блоке 13 умножения отсчеты перемножаются на +1 и без изменения передаются на вход арифмтического блока 14.,

Код адреса при определении ПРБ устанавливается в соответствии с

соотношением, ,

i4X-f- X( где 1 - значение дискретного уровня, который принимает значения, 6т -127 до +127, Лх - ширина дифференциального коридораf x(tQ) - текущее значение дискретного отсчета. В арифметическом блоке 14 коды отсчетов преобразуются в адрес ячейки блока 15 памяти, который с арифметического блока 14 поступает на вход первого коммутатора 20, ас выхода первого коммутатора 20 на адресные шины блока 15 памяти. Если код отсчета положительный, то он оТтределяёт и адрес ячейки блока 15 памяти В: : . В А + 127 + i , где А - номер начального адреса секции; константа, равная числу : уровней квантования. Если код отсчета i отрицательный, то адрес ячейки блока 15 памяти определяется инвёрсйей кода (дополнением до 127, например: при 1 -5, i 127 - 5 122) : В А + (i). Полученный адрес с выхода арифметического блока 14 поступает на вход коммутатора 20, где собирается с адресом секции от счетчика (секций) 30 и блока 28 формирования адреса и подается на адресный.вход блока 15 памяти. Из выбранной ячейки блока 15 памяти считывается код ранее зафиксированных событий и записывается в арифметическом блоке 14, где к нему добавляется единица. Полученная новая сумма событий записывается по тому же адресу в блок 15 памяти. Объем событий для ПРВ определяется числом дискретных отсчетов КФ. После вычисления матрицы КФ из 16 элементов и четыре ПРВ вычисляется (автоспектр). При вычислении матрицы КФ, ПРВ и СПМ, например, nd четнрем входам, на лицевой п-анели управления задаются соответственно режим работы. Старший разряд счётчика 25 устанавливается в единицу, что соответству ет делению блока 15 памяти на две части. Первая часть блока 15 отводи ся под результаты вычисления КФ, а вторая - под результаты ПРВ и СПМ. Второй преобразователь 23 кода и блок 27 задания начальных условий .устанавливают разрядность счетчика 25 равную четырем, что соответствуе вычислению шестнадцати функций КФ. Счетчик 30 и блок 28 формирования адреса формируют текущий номер секции. При вычислении ПРВ по четырем входами и четырем СПМ вторая часть памяги делится на восемь секций (зон). Количество ячеек блока 15 памяти отводимых для хранения результатов ПРВ по каждому входу определяется числом уровней квантования входного сигнала. Так, например, при 256 уровнях квантования входного сигнала отводится 256 ячеек блока 15 памяти для хранения ПРВ по одному вхо ду. Число ячеек блока 15 для СПМ определяется числом ячеек, используемых при вычислении автокорреляцион ных функций. При вычислении СПМ ординаты корреляционных функций считываются из блока 15 в один из регистров арифме тического блока 14 по адресам, сфор мированным теми же блокг1ми, что и при вычислении Кф. В арифметическом блоке 14 вычисляется код первой ординаты корреляционного окн§1 К. Например окно Бартлера имеет вид K(hdtr)i-,: где h - номер ординаты. Код КФ R(h/jt) и окно к(ьлс) перемножаются в арифметическом блоке 14, Затем из арифметического бло ка 14 считывается код пропорциональ ный углу основнойгармоники V ih/ где i - текущее значение и поступае на вход блока 18 постоянной пг1мяти, где по заданному углу f определяютс значения косинуса для i 1, п 1 - cossiri . Код с блока 18 постоянной пгиняти, пропорциональный значению косинус51, поступает в арифметический блок 14 и перемножается с полученны ранее произведением. Я(Ш)К(2дТ)ео523Г. Далее из блока 15 выбирается сле ющая ордината КФ (п 2) и повторяе ся алгоритм вычисления, в результате которого получается R(24r)K(2dr)cos2J- Полученное произведение суммируется с предыдущим значением и хранится в арифметическом блоке 1,4. В результате в арифметическом блоке 14 получается значение одной ординаты СПМ С Р(11ЛС;к(114Г)со52, которое записывается по первому адресу секции СПМ в блоке 15, сформированному счетчиком 30 и блоком 28 формирования адреса. Затем устанавливается величина углаЧ -, пропор.. ш циональная второй гармонике. В результате вычисляется вторая ордината СПМ . Е1 R{har;K(tijr;cos2ir Ъ -1Результат записывается во второй . адрес СПМ блока 15 и т.д В результате одновременного вычисления статистических характеристик в первой секции блока 15 памяти получается матрица из 16 функций, КФ, а во второй - четыре функции ПРВ и четыре функции СПМ (по числу авто-корреляционных функций в матрице кф Все текущие значения ординат КФ, ПРВ и СПМ вычисляются по дискретным отсчетам одной реализации. Аналогично можно вычислять и другой набор статистических характеристик, например автокорреляционные функции ПРВ, СПМ иили вычислять только прямую или обратную ветвь КФ, изменять число обрабатываемых процессов. Таким образом, вычисление СПМ и ПРВ расширяет функциональные возможности коррелометра. Наличие новых блоков и их связей в предлагаемом устройстве, позволяющих в зависимости от многих переменных делить блок 15 памяти на секции и формировать в пределах секций текущие адреса, дает возможность одновременно по одной реализации вычислять комплекс статистических характеристик. Следует отметить, что конструктивно элемент 31 микропрограммного управления мржет быть выполнен на микросхеме К589ИК01, элемент 32 памяти - на микросхеме К556РТ4 регистр 33 микрокоманд - на микросхеме К155ИР1, дешифратор 36 - на микросхеме К155ИДЗ, коммутатор схемы 34 условного перехода выполнен на

микросхеме К155КП7. Узел обработкиса - на микросхеме К155КП7. Коммуданных может бить выполнен на микро-татор 20 может быть выполнен на миксхеме К589ИК02, блок 18. постоянно росхеме К155КП7, преобразрватель

памяти - на микросхеме К55РТ4, пре-кодрв 23 - на микросхеме К55бРТ4,

образователь 22 кода - на микросхемеблок 28 задания начальных условий

К155ИД4, блок 28 формирования адре- на микросхеме К155ИДУ.

(Pf/f.f

гтпттт

, ттттт Trrr Ф

/V/s/v/V7

Ш:/

Фуг

Ф1/г. J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Статистический анализатор | 1975 |

|

SU515114A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Электронная промышленность, 1978, 6, с | |||

| Способ запрессовки не выдержавших гидравлической пробы отливок | 1923 |

|

SU51A1 |

Авторы

Даты

1983-09-07—Публикация

1982-03-11—Подача