1

Изобретение относится к цифровой электроизмерительной технике и предназначено для одновременного определения в реальном масштабе времени обеих ветвей корреляционной функции 5 высокочастотнЕлх случайных процессов аппаратурой ограниченного быстродействия и может использоваться в системах автоматического управления технологического контроля, диагности- Ю ки, обработки информации и т.д.

Известны коррелометры для одновременного вычисления обеих ветвей кор- . реляционной функции (КФ) стационарных случайных процессов ll 15

Этот коррелометр содержит две цепочки, состоящие из последовательно соединенных аналого-цифрового преобразователя и регистра сомножителя, . 20 выходы регистров через блок умножения подключены к сумматору произведения, соединенному с входом и выходом запоминаквдего устройства, причем в каждую цепочку дополнительно введен 25 регистр сомножителя, вход которого соединен с выходом соответствующего аналого-цифрового Лреобразователя, а выход подключен к соответствукнцему входу блока умножения.30

Коррелометр дает возможность вычислять в реальном масштабе времени по одной реализации ординаты обеих ветвей КФ, однако он не позволяет обрабатывать входные сигналы с частотой больше, чем f l/ut l/T(j, что существенно ограничивает частотные свойства коррелометра и снижает эффективность работы.

Наиболее близким техническим ре-шением является коррелометр, содержащий квантователи сигналов (эквивалентные аналого-цифровым преобразователям) , расширители импульсов (эквивалентные промежуточньм регистрам) , блок умножения, блок суммирования и накопления, блок памяти, счетчик и генератор тактовых импульсоп 2.

Такой коррелометр имеет недостаточный диапазон частот при использовании цифровых элементов.

Цель изобретения - повьлшение частотного диапазона входных сигналов при сохранении ограничений на быстродействие элементной базы.

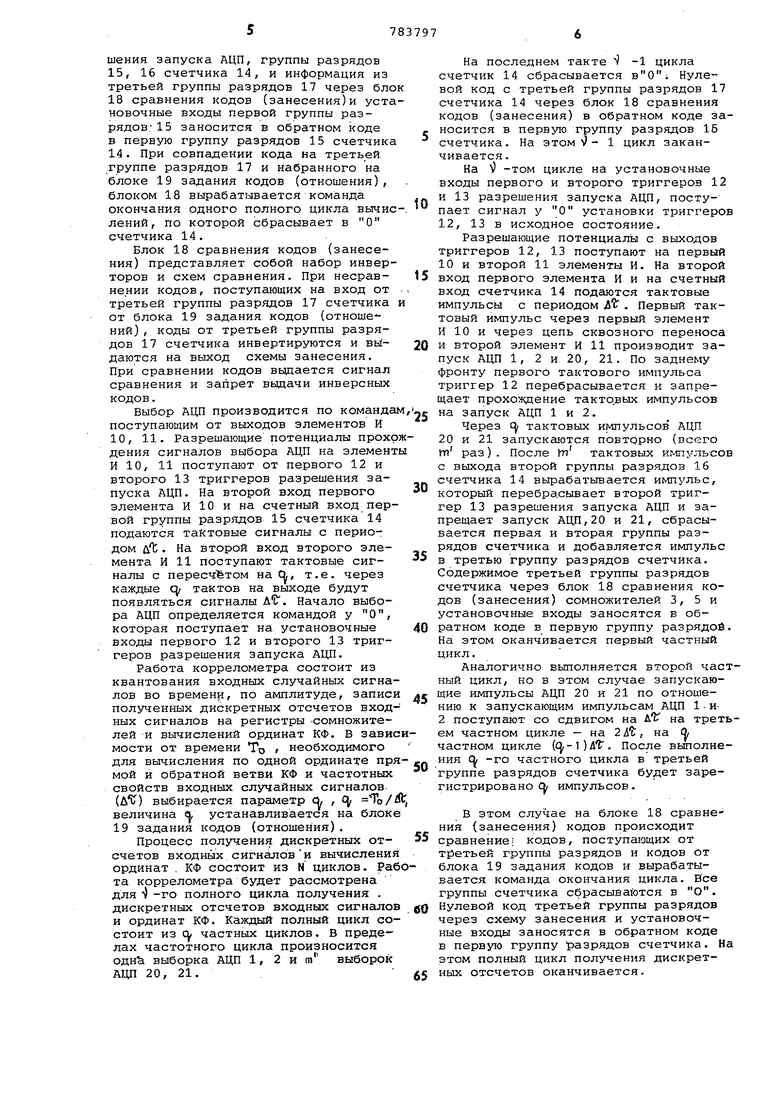

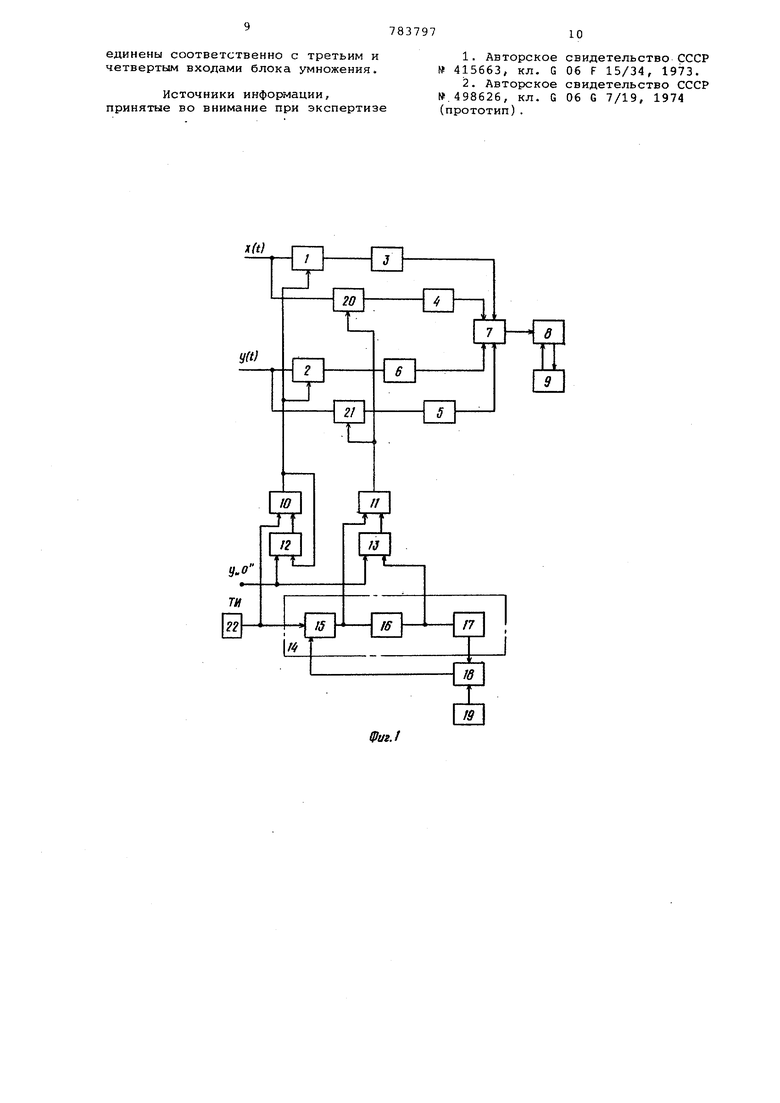

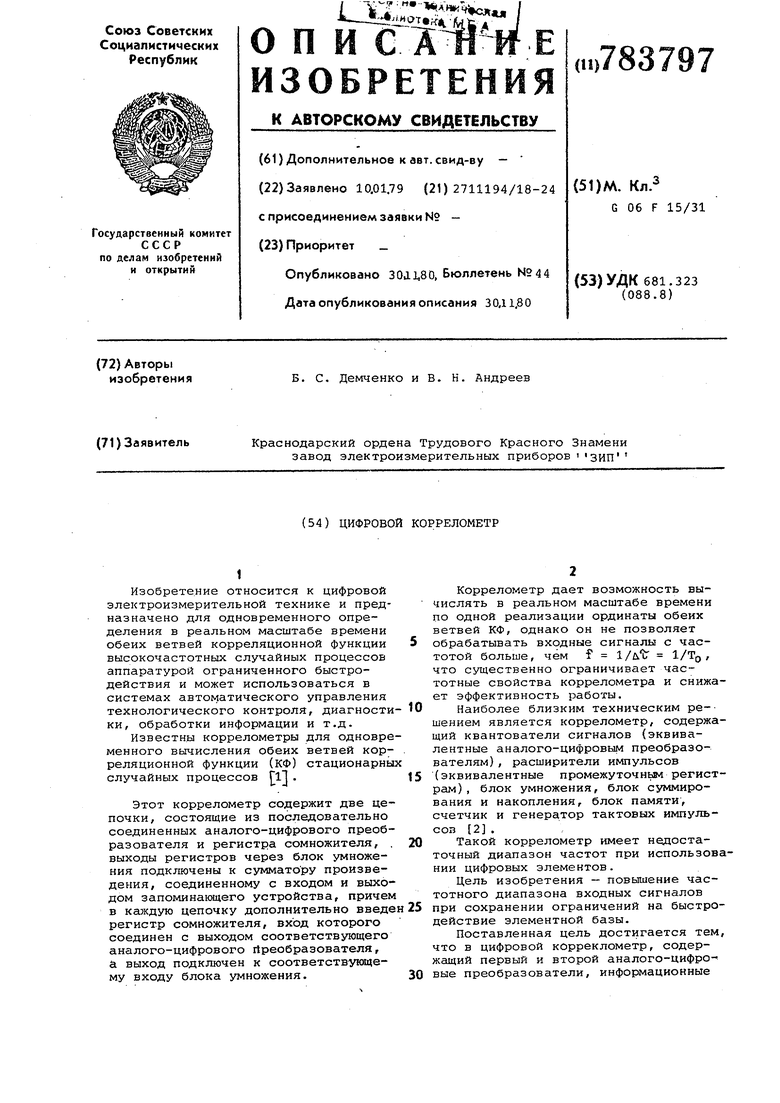

Поставленная цель достигается тем, что в цифровой корреклометр, содержащий первый и второй аналого-цифро- вые преобразователи, информационные входы которых являются соответствен первым и вторым входами коррелометр а выходы через первый и второй регистры сом 1ожителя соответственно подключены к первому и второму входам блока умножения, выход которого соединен с первым входом сумматора произведения, второй вход которого подключен к выходу блока памяти, вх которогоподключен к выходу сумматора произведений, генератора импульсов, выход которого соеЯинен с входом счетчика введены третий и четвертый аналого-цифровые преобразователи , третий и Четвертый регистры сомножителя, два Элемента И, два триггера, блок срав нения кодов и блок задания кодов, выход которого подключен к первому входу блока сравнения кодов, второй вход которого соединен с выходом группы старших разрядов счетчика, первые входы.элементов И подключены соответственно к выходу генератора импульсов и к выходу переполнения группы младших разрядов счетчика, вторые входы элементов И соединены с выходами соответствующих триггеров , первые входы, которых объединены и подключены к входу установки нуля коррелометра, выход первого эл мента И соединен с управляющими вхо первого и второго аналого-циф ;1Овых преобразователей и с вторым Зходом первого триггера, второй вхо второго триггера подключен к выходу переполнения группы средних разрядов счетчика, выход второго элемент И соединен с управляющими входами третьего и четвертого аналого-цифровых преобразователей, информацион ные входы которых подключены соотве ственно к первому и второму входам коррелометра, а выходы - через третий и четвертый регистры сомножителя соединены соответвтенно с третьим и четвертым входами блока yMf;oжения.. На фиг. 1 изображена функциональная схема предлагаемого коррелометра . Коррелометр -содержит аналого-циф ровые преобразователи (АЦП) 1, 2, регистры сомножителей 3, 4, 5, б, блок 7 умножения, сумматор 8 произведений, блок 9 памяти, первый и вт рой элементы И 10, 11, первый и вто рой триггеры 12, 13 запуска аналого цифровых преобразователей, счетчик 14 запуска АЦП, состоящий кз трех групп разрядов 15, 16, 17, блок 18 Сравления кодов, блок 19 задания ко дов, аналого-цифровые преобразователи 20,21. Цепь переполнения перво группы разрядов счетчика 14 предста ляет собой соединение между выходом первой группы разрядов 15 и входом второй группы разрядов 16 счетчика а цепь переполнения второй .группы разрядов представляет соединение между выходом второй группы разрядов 16 и входом третьей группы разрядов 17. Первая цепочка, состоящая из последовательно соединенных аналого-цифрового преобразователя 1 и регистра сомножителя 3, вторая цепочка из АЦП 2 и регистра сомножителя 6, первая дополнительная цепочка АЦП 20 и регистра сомножителя 4, вторая дополнительная цепочка из АЦП 21 и регистра сомножителя 5 через выходы регистров сомножителя 5 через выходы регистров сомножителей 3-6 соединены с входами блока 7 умножения, выход которого соединен с входом сумматора 8 произведений, соединенного с входами и выхода.Ми запом.нающего устройства 9. Устройство содержит .генератор иг лульсов 22. Выход первого элемента И 10 соединен с одним из установочных входов первого триггера 12 разрешения запуска АЦП и с управляющими входами АЦП 1 и 2. Первые входы первого 10 и второго 11 элемента И соединены соотЕвтственно с, выходами первого 12 и второго 13триггеров разрешения запуска АЦП. Выход второго элеме1.1та И 11 соединен с управляющими входами дополнительных АЦП 20 и 21 первой и второй цепочек. Второй вход второго элемента И соединен с цепью переполнения первой группы разрядов 15 счетчика 14, цепь переполнения второй группы разрядов 16 связан с одним из установочных входов второго триггера 13 разрешений запуска АЦП, другие входы д-риггеров 12, 13 соединены вместе. Второй вход первого элемента М 10 и счетный вход счетчика запуска АЦП соединены вместе и подключены к выходу генератора 22. Счетчик запуска АЦП состоит из последовательно соединенных трех групп разрядов 15, 16f 17. Установочный вход первой группы разрядов 15 счетчика 14соединен с выходом блока 18 сравнения кодов, один вход которого соединен с выходом блока 19 задания кодов (отношения), а другой вход соединен с выходом третьей группы разрядов 17 счетчика 14, Первая группа разрядов 15 производит пересчет тактовых сигнало з на величину с , определяемую отношением времени Т обработки сомножителей к шагу задержки выбора АЦП At . Вторая группа разрядов 16 осуществляет пересчет тактовых импульсов на Cj/w Ш, где 1TI -- число вычисляемых ординат КФ, гп - число вычисляемых ор,цинат в частном цикле. Третья группа разрядов 17 производит пересчет тактовых импульсов на JDCV Перенос сигнала из второй группы разрядов -16 счетчика в третью означает конец частного цикла, по которому сбрасывается в О второй триггер 13 разрешения запуска АЦП, группы разрядов 15, 16 счетчика 14, и информация из третьей группы разрядов 17 через бло 18 сравнения кодов (занесения)и уста новочные входы первой группы разрядов,- 15 заносится в обратном коде в первую группу разрядов 15 счетчика 14. При совпадении кода на третьей группе разрядов 17 и набранного на блоке 19 задания кодов (отношения), блоком 18 вырабатывается команда окончания одного полного цикла вычис лений, по которой сбрасывает в О счетчика 14. Блок 18 сравнения кодов (занесения) представляет собой набор инверторов и схем сравнения. При несравнении кодов, поступающих на вход от третьей группы разрядов 17 счетчика от блока 19 задания кодов (отношений), коды от третьей группы разрядов 17 счетчика инвертируются и выдаются на выход схемы занесения. При сравнении кодов выдается сигнал сравнения и запрет вьздачи инверсных кодов. Выбор АЦП производится по команда поступающим от выходов элементов И 10, 11. Разрешающие потенциалы прохо дения сигналов выбора АЦП на элемент И 10, 11 поступают от первого 12 и второго 13 триггеров разрешения запуска АЦП. На второй вход первого элемента И 10 и на счетный вход пер вой группы разрядов 15 счетчика 14 подаются тактовые сигналы с периодом u.t. На второй вход второго элемента И 11 поступают тактовые сигналы с пересчетом на tt, т.е. через каждые q/ тактов на выходе будут появляться сигналы Л С . Начало выбора АЦП определяется командой у О, которая поступает на установочные входы первого 12 и второго 13 триггеров разрешения запуска АЦП. Работа коррелометра состоит из квантования входных случайных сигна лов во времени, по амплитуде, запис полученных дискретных отсчетов вход ных сигналов на регистры сомножителей и вычислений ординат КФ. В зави мости от времени То г необходимого для вычисления по одной ординате пр мой и обратной ветви КФ и частотных свойств входных случайных сигналов () выбирается параметр сз. , С %/ величина а, устанавливается на блок 19 задания кодов (отношения). Процесс получения дискретных отсчетов входных сигналови вычисления ординат . КФ сострит из N циклов. Ра та коррелометра будет рассмотрена для -то полного цикла получения . дискретных отсчетов входных сигнало и ординат КФ. Каждый полный цикл со стоит из су частных циклов. В пределах частотного цикла произносится одн выборка АЦП 1, 2 и т выборок АЦП 20, 21. На последнем такте J -1 цикла счетчик 14 сбрасывается Нулевой код с третьей группы разрядов 17 счетчика 14 через блок 18 сравнения кодов (занесения) в обратном коде заносится в первую группу разрядов 16 счетчика. На этом - 1 цикл заканчивается. На V -том цикле на установочные входы первого и второго триггеров 12 и 13 разрешения запуска АЦП, поступает сигнал у О установки триггеров 12, 13 в исходное состояние. Разрешающие потенциалы с выходов триггеров 12, 13 поступают на первый 10 и второй 11 элементы И. На второй вход первого элемента И и на счетный вход счетчика 14 подаются тактовые импульсы с периодом jSt . Первый тактовый импульс через первый элемент И 10 и через цепь сквозного переноса и второй элемент и 11 производит запуск АЦП 1, 2 и 20, 21. По заднему фронту первого тактового импульса триггер 12 перебрасывается и запрещает прохождение тактовых импульсов на запуск АЦП 1 и 2. Через с тактовых импульсов АЦП 20 и 21 запускаются повторно (всего т раз). После ID тактовых импульсов с выхода второй группы разрядов 16 счетчика 14 вырабатывается импульс, который перебрасывает второй триггер 13 разрешения запуска АЦП и запрещает запуск АЦП,20 и 21, сбрасывается первая и вторая группы разрядов счетчика и добавляется импульс в третью группу разрядов счетчика. Содержимое третьей группы разрядов счетчика через блок 18 сравнения кодов (занесения) сомножителей 3, 5 и установочные входы заносятся в обратном коде в первую группу разрядов. На этом оканчивается первый частный цикл. Аналогично выполняется второй частный цикл, но в этом случае запускающие импульсы АЦП 20 и 21 по отношению к запускающим импульсам АЦП 1.и2 поступают со сдвигом на Д на третьем частном цикле - на 2it, на С частном цикле ((-)ift. После выполнения с -го частного цикла в третьей группе разрядов счетчика будет зарегистрировано с импульсов. В этом случае на блоке 18 сравнения (занесения) кодов происходит сравнение: кодов, поступающих от третьей группы разрядов и кодов от блока 19 задания кодов и вырабатывается команда окончания цикла. Все группы счетчика сбрасывайтся в О. Нулевой код третьей группы разрядов через схему занесения и установочные входы заносятся в обратном коде в первую группу разрядов счетчика. На этом полный цикл получения дискретных отсчетов оканчивается. На фиг. 2 изображена и последовательность выборок АЦИ для At -To -Ma№; Параллельно получению дискретных отсчетов производится вычисление оценок ординат прямой и обратной вет ви КФ. Ординаты КФ , вычисляются до К/ О, 1,- ...,С|,-1, Ki О, 1, ...,т . Рассмотрим вычисление по одной ординате прямой и обратной ветви КФ для 1частного цикла i ординаты. : Для вычисления Rx iLCi-- - )й J к входным цепям блока умножения подкЬночаются выходы регистров сомиожит|елей , Pi2.r 3,5. i На выходе блока умножения получаем произведение XtG- d At -iU 0)l: В сумматоре 8 из блока 9 памяти С:читается частичная cyMNsa произведений -- 1 циклон . ,)u:r netHc ;il 4 2--(-t:1 в сумматоре 8 производится сум1 1ироваиие полученного произведения в -том цикле с частичной сумг-Юй проиэведенин полученшлх в 1 циютах. В результа-те получаем -Jv(.-1-я.1)Чг1 Л. хл, - г-1 ; Далее к выходным цепям блока 7 умр ажония тюдключаются входы регистров сомиолиггелей 4, 6. Аналогично щолучаем оп.енку ординаты второй ветв КФ ,-;лч V --|о 7,ис.па. ; Таким образом, за Ы циклов вычисЛени; ;1О. по-чниИ набор ординат КФ прямой : обратной ветви vL.к,я,lc,,, С:,(.,г) ( 0,1,m Обработка высококачествеггных сиг налов для o Mqk;ii производится ана логично при использовании параллель но-последователь юго метода ний. При этом в течение частного цикла работы производится вычислени одной ордин 1ты (для - мсткс производится вычлсление гп ординат) Onm;:;iHfiJ ; коррелометр иай;дет шир кое п .;и(. и науке, технике-, на родном хо;- Гйсгве д.пп обработки случайных iTpou.eccoB в UJHPOKOM диапазоь частот . Частотный диапазон обрабаты ваемых cHiM-iajiOB в предлагаемом кор ;pcj)(5McTpc не зависит от времени об:работки сомножителей ( То) и определ ;ется величиной f - 1/ut, где ut мо .жет быть взята во много раз меньше То ( ,) . Наименьшая величина ьТ iкоторую можно установить при опреде ;лении КФ, определяется погрешностью фиксации входного сигнала аналогоцифровь.. преобразователем. Для обычных коррелометров минимальная величина, которую можно получить, учитывая погрешность фиксации АЦП в пределах О Д-0 , , TQ-составляет 10-30 МКС. Ориентировочное увеличение частоты обрабатываемого процесса в 20 раз по сравнению с прототипом расширяет область применения коррелометра, увеличивает эффективность работы коррелометра. Формула изобретения Цифровой коррелометр, содержащий первый и второй аналого-цифровые преобразователи, информационные входы которых являются соответственно nepBFiiM 1 вторым входами коррелометра, а выходы через первый и второй регистры сомножителя соответственно подключены к первому и второму входам, блока умножения, выход которого соедиНен с первым входом сумматора произведений, второй вход которого подключен к выходу блока памяти, вход которого подключен к выходу сумматора произведений, генератор и мпульсов , выход которого соединен с входом счетчика, отличающийся тем, что, с целью расширения частотного диапазона входных сигналов, в коррелометр введены третий и четверт} 1й аналогоцифровые преобразователи, третий и четвертый регистры сомножителя, два элемента И, два триггера, блок сравнения кодов и блок- задания кодов,выход которого подключен к первому входу блока сравнения кодов, второй вход которого соединен с выходом группы старших разрядов счетчика, первые входы элементов И подключены соответственно к выходу генератора импульсов и к выходу переполнения группы младших разрядов счетчика-, вторые входы элементов И соединены с выходами соответствующих триггеровj первые входы которых объединены и подключены к входу установки нуля коррелометра, выход первого элемента И соединен с управляющими входаг- и первого и второго аналого-цифровых преобразователей и с вторым входом первого триггера, второй вход второго триггера подключен к выходу переполнения группы средних разрядов счетчика, выход второго элемента И соединен с управля ощими входами третьего и четвертого аналого-цифровьх преобразователей, информационные входы которых подк/шчены соответственно ,к первому и второму входам корреломе,тра, а выходы через третий и четвертый регистры сомножителя соединены соответственно с третьим и четвертым входами блока умножения. Источники информации, принятые во внимание при экспертизе 78379 710 1.Авторское свидетельство СССР № 415663, кл, G 06 F 15/34, 1973. 2.Авторское свидетельство СССР №.498626, кл. G 06 G 7/19, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелометр | 1983 |

|

SU1113806A1 |

| Многоканальный многомерный цифровой коррелометр | 1984 |

|

SU1187177A1 |

| Многоканальный цифровой коррелометр | 1985 |

|

SU1262523A1 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

| Многоканальный многомерный цифровой коррелометр | 1985 |

|

SU1305714A1 |

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

| Цифровой коррелометр | 1979 |

|

SU788113A1 |

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ КОРРЕЛОМЕТР | 1972 |

|

SU419895A1 |

ьй.-ЙЙ.Й;/

. ,- , V

Гл( ,

Т„-т.То.ЩЛ.лГ

Фиг. 2

хШ1)Тш1

fffffffC f

Авторы

Даты

1980-11-30—Публикация

1979-01-10—Подача