Изобретение относится к цифровой электроизмерительной технике и предназначено для из|уюрения в реальном масштабе врекени автокорреляционной функции кмогомерного случайного процесса, имеющего п случайных составляющих и представляквдего собой матрицу размера плп корреляционньсс функций. При этом все элементы матрицы вычисляются одновременно. ИзобЕЮтение может быть использова но в системах автоматического управления, обработки измерительной информации , технологического контроля, технической диагностики и т.д. В настоящее время известны и полу чили широкое распространение цифровы коррелометры параллельно-последовательного действия, которые вычисляют в реальном масштабе времени m ордииа автокорреляционной функции случайного процесса одного канала измерения или m ординат взаимной корреляцион ной функции случайных процессов двух каналов измерений. Известен коррелометр, который можно назвать двухканальным (по числу обрабатываемых случайных процессов) , содержащий два аналого-цифровы преобразователя (АЦП), два регистра сомножителя, в которые из АЦП поступают дискретные отсчеты входных сигналов, множительное устройство,сум- матор произведений,входное sanoNSHHSuoщее устройство (ЗУ) для хранения дискретных отсчетов входных сигналов и выходное запоминающее устройство для хранения частичных сумм произведений отсчетов в процессе вычисления и после их завершения. Количество запоминаекмЯ ординат . во входном ЗУ для некоррелированной выборки входных сигналов,частично коррелированной и сильно коррелированной различно и зависит от степени коррелированности отсчетов. При сильно коррелированной выборке требуется входное ЗУ на m чисел. При некоррелированной выборке требуется входное ЗУ на одно число, при этом обрабатываются входные сигнгшы с наибольшим значением верхней частоты по сравнению с другими способами выборки, однако при некоррелированной выборке входных сигналов требуется значительное увеличение длительности обрабатываемой реализации по сравнению с сильно коррелированной выборкой.

На практике увеличение длины реализации не всегда возможно,так как длина реализации может быть ограничена условиями эксперимента или стационарности процесса. Особенно часто встречаются задачи с ограниченными услови-ями стационарности в управлении технологическими про-цессами.

Во многих задачах технологического контроля, автоматического управления, технической диагностики, самонастройки и т.д. необходимо вычислять в реальном масштабе времени взаимные и автокорреляционные функци нескольких случайных процессов (авто-КФ многомерного процесса). Такие задачи можно решать, используя необходимое количество (по числу вычисляемых корреляционных функций) описанных двухканальных коррелометро параллель но-последов ательного действия fl .

Однако подобная вычислительная система дорога, сложна по количеству используемого оборудования и ее применение не всегда оправдано.

Наиболее близким к предлагаемому является многоканальный цифровой коррелометр, содержащий блок управления , выход которого подключен ко входу адресного счетчика, выходы адресного счетчика через дешифратор подключены к запоминающему устройств выход которого соединен с сул№1атором подключенным к блоку умножения, выхс сумматора соединен с запоминакндим устройством, аналого-цифровые преобразователи по числу каналов, выход каждого из которых подключен ко входам регистра сомножителя своего канала, блок выбора сомножителей,входы которого соединены с выходами младши разрядов адресного счетчика, а выходы подключены,соответственно,к первы входам введенных в каждый канал блоков схем И, вторые входы которых подключены ко входам соответствующих регистров сомножителей, а третьи входы объединены и подключены ко входам блока управления, выходы блоков схем И объединены и подключены ко входам блока умножения t2} .

Недостатком такого устройства является возрастание статистической погрешности при обработке реализаций ограниченной длительности или стационарности, а также возможность появления дополнительной погрешности погрешности синхронности.

При решении многих задач технологического контроля автоматического управления, технической диагностики, например при ферментации белкововитаминных концентратов из нормальных парафинов нефти, требуется работа коррелятора с ограниченными по длительности реализациями случайного процесса или с ограниченными услоВИЯМИ стационарности в управлении процессом, а следовательно, необходимость введения алгоритмов частично и сильно коррелированных выборок, которые совместно с некоррелированной выборкой перекрывают весь диапазон возможных реализаций .случайного процесса.

Работа описанного прототипа только с относительно длинными и стационарными реализациями случайного (Процесса при наличии в нем широкого набора функциональных узлов сужает его функциональные возможности,увеличивает статистическую погрешность вычислений и, сл едовательно, неприемлема для разрабатываемого коррелометра .

Цель изобретения - повьииение точности вычислений.

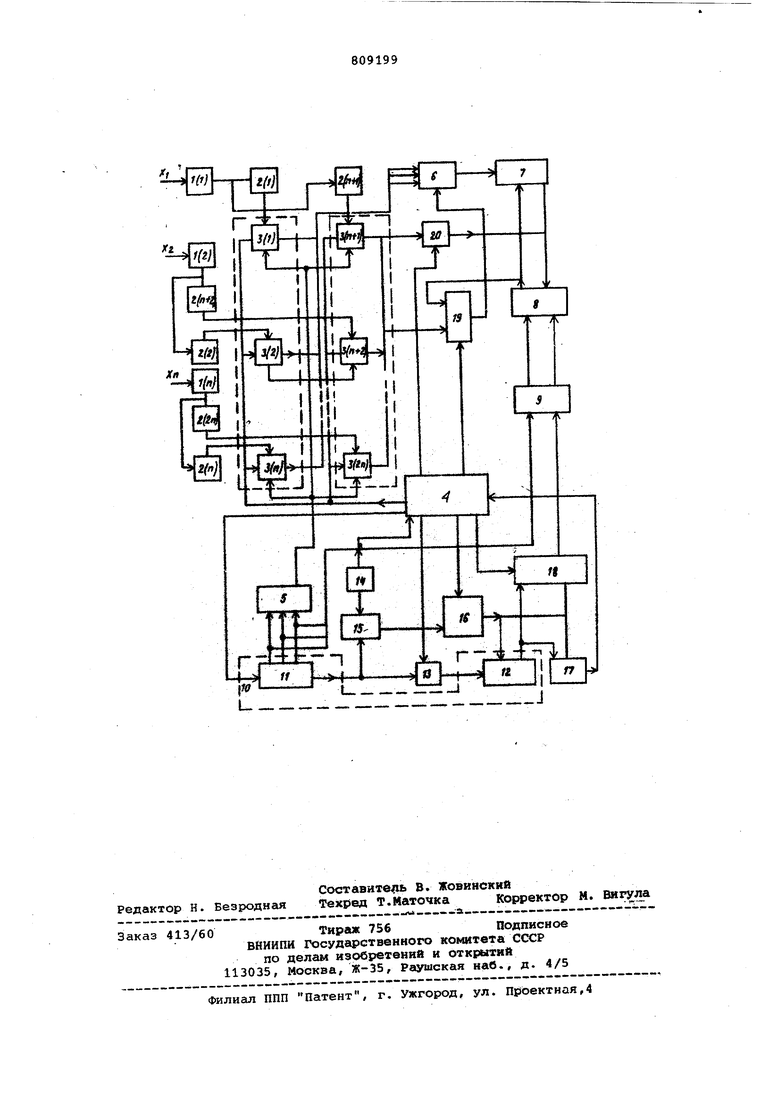

Поставленная цель достигается тем, что в многоканальный многомерный цифровой коррелометр, содержгидий адресный счетчик СТВЕЙНИХ разрядов, аналого-цифровые преобразователи,входы которых являются соответствуквдиьм входами коррелометра, а выход каждог аналого-цифрового преобразователя подключен ко входам первого и второго регистров сомножителей, выходы каяодого из которых соединены с первыми входами соответствующих блоков элементов И первой и второй группы, вторые входуа блоков элементов И подключены к первому выходу блока синхронизации, третьи входы блоков элементов И соединены с выходом блока выбора сомножителей, входы которого подключены к разрядным выходам адресного счетчика ь4падших разрядов, выходы блоков элементов И первой группы подключены к соответствующим входам первой группы блока у лножения, выход которюго соединен с первы входом сумматора, второй вход которого подключен к выходу блока памяти, адресный вход которого соединен с выходом дешифратора, первая группа входов которого подключена к разрядным выходам адресного счетчика младших разрядов, информационный вход блока памяти подключен к выходу сумматора, введены два коммутатора,третий блок элементов И, блок сравнения адресов, элемент 2И-ИЛИ, блок задани коррелированности выборки, счетчик коррелированности выборки и счетчик адреса входных отсчетов, информационный вход которого соединен с выходом счетчика коррелированноути выборки, управляющий вход - со вторым выходом блока синхронизации, третий, четвертый, пятый и шестой выходы которого подключены.соответственно,к управляющим входам первого и второго коммутаторов, к первым входам элемента 2 И-ИЛИ и третьего блока элементов И, выходы элементов И второй группы подключены, соответственно, ко второй группе входов третьего блока элементов И и первой группе входов второго коммутатора, выход которого сое динен со второй группой входов блока умножения, выход третьего блока элементов И соединен с информационным входом блока памяти, выход которого соединен со вторым входом второго коммутатора, первый вход счетчика коррелированности выборки и второй вход элемента 2 И-ИЛИ подключены к выходу адресного счетчика младших разрядов, вход которого соединен с седьмым выходом блока синхро низации, первый вход которого соединен с выходом блока сравнения адресов, выхода блока задания коррелированности выборки соединены,соответственно, со вторым входом счетчика коррелированности выборки и со вторы входом блока синхронизации, выходы счетчика адреса входных отсчетов под ключе ны. соответственно к первым вхоДсЛ1 первого коммутатора, блока сравн ния адресов и адресного счетчика старших разрядов, второй вход которо го соединен с выходом элемента 2 И-ИЛИ, а выход адресного счетчика старших разрядов подключен ко вторым входам блока сравнения ещресов и первого коммутатора, выход которого соединен со вторым входом дешифратора. Предлагаемый коррелометр включает в себя п аналого-цифровых преобразователей - АЦП 1, выходы которых соединены со входами регистров сомножителей 2, поразрядные выходы регистров 2 соединены со входами блоков элементов И 3, количество элементов И в блоке равно числу разрядов в регистре . Каждый, из разрядных выходов регистра соединен с одним входом одного элемента И, второй вход элег«1ента И всех блоков - с блоком синхронизации 4; третий вход схем совпадения с соответствующим выходом блока 5 выбора сомножителей (пар сомножителей) . выходы первой группы элементов И подключены к первой группе входов блока умножения б, выход которого подключен ко входу сумматора 7 произведений, являгадегося регистром числа выходного блока пгцляти 8 (БП). Выбор адреса БП.производится с помощью дешифратора 9,соединенного с адресным счетчиком 10, точнее, с разрядными выходами адресного счет чика младших разрядов 11. Вход адресного счетчика 12 старших разрядов подключен к выходу элемента 2 И-ИЛИ 13, первый вход которого соединен с выходом адресного счетчика младших разрядов, второй вход - с третьим выходом блока 4. Первый выход блока задания коррелированности выборки 14 соединен со входом блока 4, второй выход - со входе счетчика корр лированности выборки 15, второй вход которого подключен к выходу адресного счетчика 11 младших разрядов, а выход - ко входу счетчика 16 адреса входных отсчетов. Выход счетчика 12 соединен со входом блока сравнения адресов 17 и со входом коммутатора 18, выход которого связан со входом дешифратора 9, второй вход счетчика адреса входных отсчетов - с четвертым выходом блока 4, а выход - со вторым входом счетчика 12, а также со вторым входом блока сравнения 17 и с дешифратором 9 через коммутатор 18, третий вход которого соединен с пятым выходом блока 4. Выход блока срав,неНИН 17 адресов связан со вторым входом блока 4, седьмой выход которого соединен со входом коммутатора 19, второй и третий вход которого подключены, соответственно, к выходам второй группы элементов И 3 и к выходу ВП 8, а выход кокмутатора 19 соединен со второй группой входов блока умножения 6. Шестой выход блока синхронизации 4 соединен со входом третьего блока элементов И 20, вторые входы которого связаны с выходами второй группы первых элементов И 3, а выходы - со входом БП 8. На коммутатор 19. MOt-yT поступать значения входных отсчетов, записанные в ВП 8, и далее ко вторым входам блока умножения. Управление прохождением информации через блок 20, а также выбор направления на коммутаторе 19 осуществляется блоком 4. албор направления адреса производится коммутатором 18, при этом для записи (считывания) в (из) ВП8 частичных сумм произведений корреляционных функций используется адресный счетчик 10, а запись (считывание) в (из) БП8 входных отсчетов производится по адресу из счетчика.11 младших разрядов и счетчика адреса входных отсчетов 16, Управление коммутатором 18 осуществляется от блока синхронизации. 4. Счетчик 16 реверсивный, управление сложением-вычитанием осуществляется от четвертого выхода блока синхронизации. Перенос на счетчик 12 от счетчика 11 может быть эаблоки- рован по команде, поступаквдей от третьего выхода блока 4 на второй вход элемента 2 И-ИЛИ 13. На блоке 14 задания коррелированности выборки в зависимости от степени коррелированности выборок устанавливается число, которое поступает на первый вход блока 4 для выбора соответствующего гшгоритма вы- f числений (программ работы коррелометра) , а со второго блока задания через установочные вход счетчика 15 коррелированности ьыборок записывается коэффициент пересчета q в счетчик 15, Существует цепь из счетчика 16 адреса входных отсчетов на установо ные входы счетчика 12 для переписи адресной информации при коррелированных выборках. Выходы счетчиков 12 и 16 поступают на блок схемы сра .нения адресов 17, результат сравнения с выхода которого поступает на второй вход блока синхронизации 4 и является признаком окончания пересчета адресов. Выходы адресного счетчика 11 поступают на блок выбор сомножителей 5/, выход с которого управляет выбором соответствующих сомножителей (входных отсчетов). В счетчике 11 производится пересчет тактовых импульсов блока 4 на п где число обрабатываемых процессов (входов). Счетчик 15 коррелированности выборок производит пер счет переносов счетчика 11 при неко релированных выборках на т, сильнокоррелированных - на 1, частично ко релированных - на q (). Счетчик 1Ь производит пересчет н S. При некоррелированных выборках , частично коррелированных 1- S т, сильнокоррелированных остальные т/2 ячеек сохраняются для вычисления корреляционных функций. Счетчик 12 производит пересчет на m при некоррелированных и на m-S при коррелированных выборках. Все дополнительно введенные блок состоят из известных элементов/например задатчик коррелированности 14 представляет собой переключатель с определенной коммутацией его контактов, а счетчик корредированности 15 - двоичный счетчик с переменным коэффициентом передачи. Предлагаемый коррелятор работает при некоррелированной (НКВ), сильнокоррелированной (СКВ) и частично коррелированной (4KB) выборках вхо ных сигналов. Математическая модель алгоритма при 4KB .S (v-).|ciV.K )atj, ( где R -оценка ординат коррелированной функции; -шаг задержки; -объем выборки (число циклов накопления); -коэффициент пересчета;-количество запоминаемых ординат (степень коррелированности); 0,1. .(S-1) ; К,. 0,1... (q-1) - коэффициенты i 1,2...п; j 1,2...п; V - текущий цикл накоплеX,, xi - значения дискретных отсчетов. При СКВ () формула (1) видоизменяется в соответствии с К ,j О и МАКС К т-1. При НКВ () формула (1) видоизменяется в соответствии с q-m: К,,0, К К 0,1. ..... ,т-1. Алгоритм НКВ, описанный в характеристике известного устройства, выполняется в предлагаемом коррелометре таким же образом, для чего блок синхронизации 4 по сигналу блока 14 блокирует прохождение информации через блок 20, запрещает работу счетчика 16 и блока сравнения 17, разрешает прохождение переносов от счетчика 11 к счетчику 12 и разрешает прохождение информации от элементов И 3 через коммутатор 19 на блок 6, а также от счетчика 12 через коммутатор 18 на дешифратор 9. Для вновь введенных гшгоритмов СКВ и 4KB,-также как и для НКВ, отводится m ячеек ЗУ для вычисления корреляционных функций. Часть отведенных ячеек т используется для хранения частичных сумм произведений в ходе обработки, а после нее для хранения ординат (точек) КФ. Другая часть ячеек S используется для хранения входных отсчетов. При сильнокоррелированной выборке СКВ , m m-rS Перед обработкой случайных процессов сильно коррелированной выборки (СКВ) производится предварительная записьвходных отсчетов по адресам ячеек S для всех КФ. Процедура обработки случайных процессов, также как и при некоррелированной выборке, состоит из N полных циклов вычислений. Каждый полный цикл вычислений состоит из трех подциклов. В течение первого подцикла вычислений определяются i произведений по одному для каждого временного сдвига К дТ (К 0,1.., ffl-l). Каждый первый подцикл состоит из тчастных циклов первого подцикла, в течение каждого из которых вычисляется по одному произведению для одного значения временного сдвига. Каждый частный цикл первого подцикла состоит из п- тактов. В течение такта вычисляется произведение одной из пар сомнож телей. Во втором подцикле вычислений производится параллельный сдвиг входных отсчетов по адресам S на один адрес так, что отсчеты с максимальным сдвигом стираются, а первые адреса ячеек 5 всех КФ освобождаются для записи вновь поступагацих отсчетов . Каждый второй подиикл состоит из S частных пиклов второго подцикла, в течение которого производится сдвиг на один адрес для одного временного сдвига входящих отсчетов. Каждый частный цикл второго подцикла состоит из п тактов. В течение такта производится сдвиг отсчета на один адрес. В течение третьего подцикла производится запись вновь поступивших входных отсчетов в первые адреса ячеек S. Третий подцикл состоит из п тактов. В течение каждого такта производится запись одного отсчета. Предварительная запись входных отсчетов состоит из S частных циклов записи., в течение которых записываются все входные отсчеты для всех КФ для каждого временного сдвига. В течение частного цикла записываются все отсчеты с одним сдвигом КдТ. Частный цикл состоит из п тактов. -В течение такта записы|вается один отсчет. Рассмотрим работу коррелометра при предварительной записи входных отсчетов и для V -того полного цик ла вычислений СКВ. В исходном состоянии от блока 14 в блок синхронизации 4 поступает сигнал, указывающий иа сильно коррелированную выборку, и одновременно в счетчик 15 коррелированности выборок по установленным входам заносится код, поэволякадий производит пересчет переноса из счетчика 11 на 1. Счетчик 16 устанавливается а единичное состояние, а на управ ляющий вход поступает команда на разрешение вычитания. Сигналы адре са со счетчика 16 через коммутатор 18 поступают на вход дешифратора 9 прохождение гщреса осуществляется по команде от блока 4. Одновременн блок 4 вырабатывает разрешающий по тенциал на прохождение кодов, вход ных отсчетов на вход БП 8 от элеме тов И 3 через третий блок элемен-. тов И 20. Иэ блока 4 вызывается под программа предварительной записи входных отсчетов по адресам S.Выбо пар отсчетов (сомножителей) аналог чен выбору при некоррелированной в борке, но при этом для записи в БП используются отсчеты, находящиеся регистрах 2(n+j). В результате выполнения п первых тактов в послед ние адреса ячеек S записываются от счеты с самым большим временным сд гом. - Х.тЧ)Л-С, j i,2...n Первый частный цикл записи вход ных отсчетов заканчивается. На вто ром частном цикле из счетчика 16 вычитается единица, а в счетчик 12 добавляется 1 (перед записью сче чик 12 установлен в О).В результате выполнения второго частного цикла в предпоследние адреса ячеек S запишутся входные отсчеты. ,1 Xjgm-2)t:j На S-OM частном цикле по первому адресу 3 записываются отсчеты с минимальным сдвигом , (.р.лг на счетчиках 16 и 12 после S частных циклов фиксируются одинаковые коды. Момент совпадения кодов адресов фиксируется блоком сравнения адресов 17, сигнал с которого поступает на блок 4, на этом предварительная запись входных отсчетов заканчиваетсяПри работе коррелятора на i) -ом полном цикле вычислений блок управления вырабатывает вначале подпрограмму первого подцикла. На регистрах сомножителей 2() находятся-занесенные входные отсчеты на последнем такте (i)-l)-го цикла. Входные отсчеты с минимальным сдвигом записываются с регистров 2(n+j) в ВП 8 по первым адресам ячеек. Эти отсчеты ,используются для вычислений на -i) -ом полном цикле. Подпрограмма вычислений ансшогична nporpawvie V -го полного цикла при некоррелированной выборке. Отличие состоит в том,.что вторые сомножители для получения произведения считывания из ВП и через коммутатор 19 по команде от блока 4 поступают на вторые входы блока умнояения б, блокируется прохождение информации на вход ВП 8 через йторой блок схем И 20 и прохождение информации от элементов И 3 на вход блока умножения 6. Считывание входных отсчетов из ВП 8 производится по адресу счетчиков 11 и 16, запись частичных сумм произведений - по адресу счетчиков 11 и 12. Счетчик 12 сброшен в О, в счетчике 16 установлен первый адрес ячеек 5. В течение первого подцикла вычислений получают набор произведений, которые суммируются с частичными суммами произведений -1 подцикла и получают (e-K)ui: к 0,i...m-l i,,2,..,n Сумма произведений с нулевым сдвигом записывается в ячейки т БП 8 по первому адресу, со сдвигом дТ - по второму адресу, со сдвигом (m-l)AT - по последнему адресу ячеек m БН 8, , При достижении единичного состояния 16 блок синхронизации 4 переходит на подпрограмму второго подцикла и вырабатывает команду

на вычитание переносов счетчика 16 и запрет прохождения переносов из счетчика 11 на счетчик 12. Счетчик 16 остается в единичном состоянии, счетчик 12 сбрасывается в О. Адрес из счетчика 16 по установочным входам переписывается в счетчик 12 «(считанная информация из БП 8 до перезаписи хранится на регистре И 8). Считывание входных отсчетов производится по адресам счетчиков 11 и 16, запись - по адресам счетчиков 11,12.

Для первых h тактов первого частного цикла входные отсчеты считываются из последних адресов ячеек S БП 8 и записываются по тем же адресам. В конце последнего такта первого частного цикла счетчик 12 сбрасывается в О, затем в него по установленным входам переписывается содержимое счетчика 16. По первому такту второго частного цикла второго подцикла перенос из счетчика 11 поступает в счетчик 16, где из содержимого вычитается 1. Для всех h. тактов второго частного цикла входные отсчеты-считываются по предпоследнему адресу ячеек, а записываются по последнему и т.д. Йа S-OM частном цикле входные отсчеты из первых ячеек S БП 8 пере писываются во вторые ячейки, освободив первые ячейки для з.аписи новых отсчетов. На этом второй подцикл заканчивается.

Блок 4 вырабатывает подпрограмму третьего подцикла, в результате которой на регистре 2 (i) 2 (n-fj) записываются отсчеты для вычисления на (i-fl) полном цикле. Отсчеты на регистрах 2(i) заполняются на +1 полный цикл вычислений, а отсчеты с 2() регистров записываются в БП 8 по первым адресам ячеек S. Вырабатываются команды для прохождения входных отсчетов на вход БП 8 от выходов элементов И 3 второй группы через второй блок 20 и адреса на дешифратор от счетчика 16 через коммутатор 18.

На этом полный цикл вычислений оканчивается. Через N полных циклов вычисления прекрамаются и в БП 8 оказываются оценки п корреляционных функций по т ординат (точек) каждая при сильнокоррелированной выборке входных сигналов.

Работа коррелометра при частично коррелированной выборке (4KB) входны сигналов аналогична работе при СКВ.

Для 4KB m S (m m-fS) . Количество ячеек S, отводимых для записи в ЗУ входных отсчетов (или степень коррелированности) определяется из соотношения , где q - коэффициент пересчета счетчика 15.

В исходном состоянии от задатчика коррелированности 14 в блок синхронизации 4 поступает сигнал, указывгиощий на частнокоррелированную выборку, и одновременно в счетчик коррелированности заносится код, позволякйдий производить пересчет в счетчике на

q m/S .

В результате предварительной записи входных отсчетов в ячейках будут зафиксированы отсчеты

X.CV(V-KM-C

к 0,1...S-1 j 1,2. . .п В течение пецвого подцикла вычисляется произведений по одному для каждого временного сдвига

(qK +KjUt; к:, 0,1...S-1;

0,l...q-l.

О.

Первый поддикл состоит из m S частных циклов. В пределах одного частного цикла вычисляется п произведений для одного временного сдвига ()AT, Частный цикл состоит из тактов. В течение одного такта первых п тактов из числа вычисляется одно произведение.

4.

,2.

m q. частного цикла вычисляются произведения, которые суммируются с частичными суммами произведений т)-1 полного цикла, находящимся по первым адресам ячеек т и результаты записываются по тем же адресам.

i,jni---«

в течение первых п- тактов т частного цикла вычисляются произведения, которые суммируются с частичными суммами произведений V-l полного цикла, находящимися по q адресам счетчика 12, и результаты Записываются по тем же адресам. V+5+1,

Е х..,(я{еЧ2-)дг}

На mq частном цикле получаем SX.t(.,- e4S-i)ATj ,

и результаты записываются по m-q адресам счетчика 12. На последнем такте mg частного цикла на регистры 2{i) заносятся отсчеты (q,Ati)At.

На первом такте т час -ного цикла счетчики 12 и 16 сбрасываются в О в счетчике 16 устанавливается первый адрес ячеек, сигнал от блока 4 через схему 2 И-ИЛИ устанавливает в счетчике 12 второй адрес. На

частичных циклах процесс

11

ЗД

вычислений аналогичен т частным циклам, только результат вычислений записывается в ячейки m начиная со второго адреса и далее через q адресов. Частичная су ма произведений т., частного цикла -0+5 Е Х.(с}1)нМТ Хз 1 еЧ5-) 2-S и записывается по т -(q-1) адресам счетчика 12. Результат, полученный на m частном цикле, записывается по т адресам БП 8. В течение второго и третьего подцикла вычислений производится параллельный сдвиг входных отсчетов по адресам S и запись в БП 8 по первым адресам ячеек S всех вновь поступающих отсчетов. Второй и третий подциклы выполняются так же как и при СКВ. На этом полный V -ый цикл заканчивается. Через N полных циклов вычисления прекращаются. В ЗУ фиксируются КФ по т ординат при 4KB входных сигналов. Предлагаелий коррелометр определяет в реальном масштабе времени полный набор авто и взаимных корре ляционных функций п случайных процессов при некоррелированной, частичнокоррелированной и сильнокоррелированной выборке входных сигналов и может использоваться во многих областях науки, техники и народном хозяйстве. Наличие 4KB и СКВ входных сигна лов позволяет использовать данный коррелометр в управлении технологи ческими процессами в большом диапазоне частот с ограниченной длительностью и стационарностью,уменьш статическую погрешность вычислений. Нсшичие 4KB расширяет частотный диапазон обрабатываемых процессов сравнительно с СКВ почти на порядок пр том же быстродействии элементов схем Формула изобретения Многоканальный многомерный дифровой коррелометр, содержащий адрес ный счетчик старших разрядов, аналого-цифровые преобразователи, вход которых являются соответствующими входами коррелометра, а выход каждо го аналого-цифрового преобразовател подключен ко входам первого и второ го регистров сомножителей, выходы из которых соединены с первыми входами соответствующих блоков элементов И первой и второй группы соответственно, вторые входы блоков элементов И подключены к первому выходу блока синхронизации, третьи входы блоков элементов И соединены с выходом блока выбора сомножителей входы которого подключены к разряд ным выходам адресного счетчика мла ших разрядов, выходы блоков элемен тов И первой группы подключены к соответствующим входам первой груп : блока умножения, выход которого соединен с первым входом сумматора, второй вход которого подключен к выходу блока памяти, адресный вход которого соединен с выходом дешифратора, первая группа входов которого подключена к разрядным выходам адресного счетчика младших разрядов, информационный вход блока памяти подключен к выходу сумматора, отличающийся тем, что, с целью повышения точности, в коррелометр введены два кс «мутатора, третий блок элементов И, блок сравнения адресов, элемент 2 И-ИЛИ, блок задания коррелированности выборки, счетчик коррелированности выборки и счетчик адреса входных отсчетов, информационный вход которого соединен с выходом счетчика коррелированности выборки, управляющий вход - со вторим выходом блока синхронизации, третий, четвертый, пятый и шестой выходы которого подключены, соответственно к управляющим входам первого и второго коммутаторов, к первым входам элемента 2 И-ИЛИ и третьего блока элементов И, выходы блоков элементов И второй группы подключены,соответственно, ко второй группе входов третьего блока элементов И и первой группе входов второго коммутатора, выход которого соединен со второй группой входов блока умножения, выход третьего блока элементов И соединен с информационным входом блока памяти, выход которого соединен со вторым входом второго коммутатора,первый вход счетчика коррелированности выборки и второй вход элемента 2 И-ИЛИ подключены к выходу адресного счетчика младших разрядов, вход которого соединен с седьмлм выходом блока синхронизации, первый вход которого соединен с выходом блока ср.авнения адресов, выходы блока эадания коррелированности выборки соединены, соответственно со вторым входом счетчика коррелированности выборки и со вторым входом блока синхронизации, выходы счетчика адреса входных отсчетов подключены,соответственно, к первым входам первого коммутатора, блока сравнения адресов и адресного счетчика старших разрядов, второй вход которого соединен с выходом элемента 2 И-ИЛИ, а выход адресного счетчика старших разрядов подключен ко вторым входам блока сравнения адресов и первого коммутатора, выход которого соединен со вторым входом дешифратора. Источники информации, принятые во внимание при экспертизе 1.Грибанов Ю.И.,и др. Автоматические цифровые корреляторы.М., Энергия, 1971, С. 152. 2.Авторское свидетельство СССР № 419895, кл. G Об F 15/34, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелометр | 1983 |

|

SU1113806A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ КОРРЕЛОМЕТР | 1972 |

|

SU419895A1 |

| Многоканальный многомерный цифровой коррелометр | 1984 |

|

SU1187177A1 |

| Многоканальный цифровой коррелометр | 1985 |

|

SU1262523A1 |

| Цифровой коррелометр | 1979 |

|

SU788113A1 |

| Многоканальный многомерный цифровой коррелометр | 1985 |

|

SU1305714A1 |

| Усреднитель-анализатор спектра Фурье | 1980 |

|

SU955086A1 |

| Однородный спектро-коррелометр | 1980 |

|

SU892339A1 |

Авторы

Даты

1981-02-28—Публикация

1978-12-13—Подача