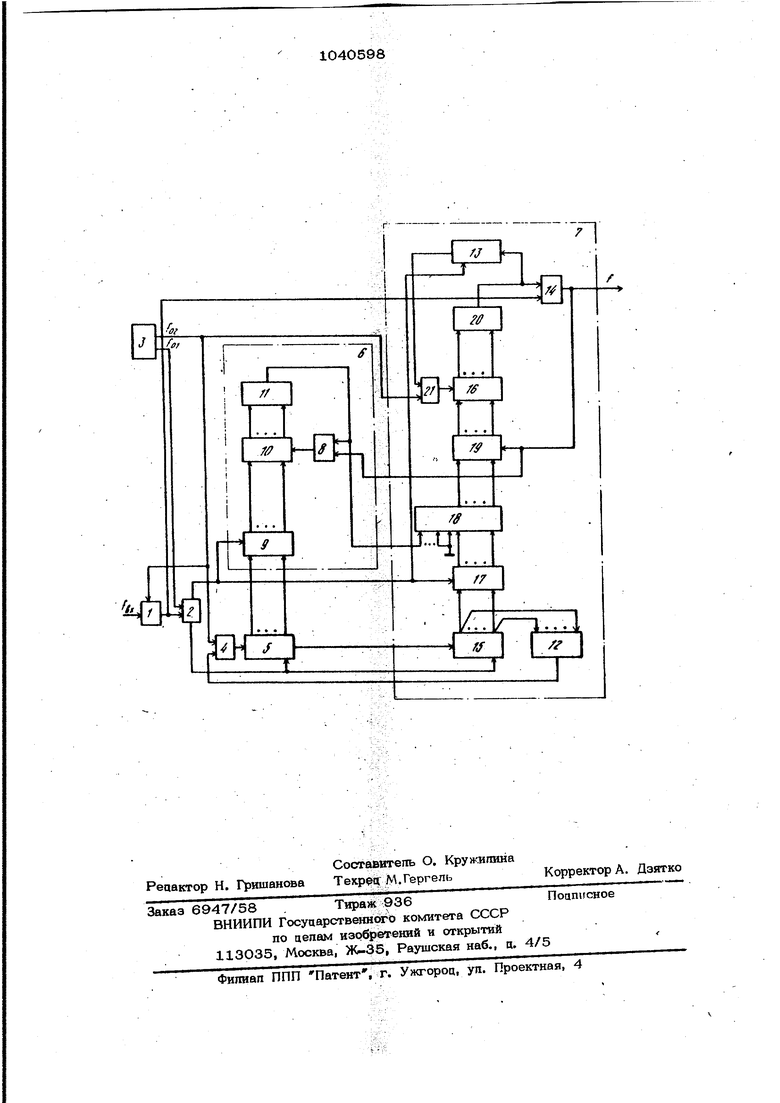

I 3j6peTeHHe относится к измерительной технике, автоматике и может быть испопьзовано в измерителях частоты, в сисугемах регулирования с частотными оатчиками и цругик устройствах для умножения частоты. Известно устройство для умножения частоты слецования импульсов, соцержащее управляющий блок, вкоачой формиро ватель импульсов, генератор опорной частоты, делитель частоты, блок умножения и блок коррекции , Оцнако устройство характеризуется недостаточно высокой точностью умножения. Наиболее близким по технической сущности к предлагаемому является ус ойство цля умножения частоты следования импульсов, содержащее управляющий блок, первый выход которого соединен с установочным входом делителя частоты, генератор опорной частоты выход которого подключен к входу делителя частоты, бпок умножения, cooros 11шй из элемента ИЛИ, первого счетчика ра ядные выходы которого соединены с входами запоминающего регистра и посл довательно соесиненных элемента перено са, второго счетчика и элемента И, выход которого соединен спервым входом элемента ИЛИ, второй вход которого объединен с установочным входом перво го счетчика импульсов и подключен к первому выходу управляющего блока, а выход - к управЛ5пощему входу блока переноса, лри этом вход первого счетчика импульсов соепинен с выходом делителя частоты, управляющий вход запоминающего регистра - с вторым выходом управляющего блока, и блок коррекции, состоящий из элемента И и последовательно соединенных элемента переноса, счетчика и элемента ИЛИ, выход которого подключен к первому входу элемента И, причем вход счетчика импульсов блока коррекции соединен с выходом элемента И, а разрядные выходы делителя частоты подключены к входам элемента переноса блока KOI рекиии, упрбшпяющий вход которого соединен с вторым выходом, управляющего блока, сумматор, первые входы которого соединены с разрядньши выходами запоминающего регистра, вторые входы генератора опорной частоты, а выход подключен к входу управляющего блока, причем выход генератора опорной частоты соединен со счетным входом второго подключены к щине логического нуля, кроме младщего,разряда, соединенного с выходом элемента умножения и синхронизатор, входы которого соединены с щиной частоты и с выходом счетчика, а второй вход элемента И блока коррекции подключен к выходу эл&мента ИЛИ блока умножения 2 . Однако устройство характеризуется недостаточно высокой точностью умножения из-за возникновения динамической оимбки умножения при увеличении умножаемой частоты, выраженной в изменении коэффициента умножения за счет пропусков импульсов выходной последователь. ности. Это связано с тем, что (V.+ 1)-я последовательность выходных импульсов формируется из У. -го периода входной частоты и при увеличении входной частоты (К + 1)-й период будет меньщеК-го периода умножаемой частоты. Кроме того, ограниченные функциональ: ные возможности, так как. известное устройство для умножения частоты рабо тоспособно в ограниченном диапазоне входных частот от,. j - aoipx.tnax и неработоспособйо в диапазоне входных частот о-iax.min. Цель изобретения - повыщение точности умножения и расщирение функциональных возможностей за счет .обеспечения возможности умножения частоты следования импульсов в области низких частот. Поставленная цель достигается тем, что в устройство для умножения частоты следования импульсов, содержащее блок коррекции, состоящий из последовательно соединенных элемента переноса, счетчика импульсов, элемента ИЛИ и элемента И, выход которого подключен к счетному входу счетчика импульсов, блок умножения, состоящий из последовательно соединенных первого (иетчика импульсов, запоминающего регистра, сумматора, элемента переноса, второго счетчика импульсов, элемента И и элемента ИЛИ, выход которого подключен к управляющему входу элемента переноса и к второму входу элемента И, блока коррекции, первый вход которого соединен с входом младшего разряда сумматора, блока умножения, вторая группа входов которого соединена с шиной логического нуля, синхронизатор, первый вход которого 3 10 поцкпючен к вхоцной шине, второйвхоц к первому выхоцу генератора опорной частоты, а выхоц - к первому вхоцу бпока управления, первый выхоц которо. го с установочными вкоцами цепитепя частоты и первого счетчика импутгъсов бпока умножения, счетный .вхоа которог соединен с выхоцом целитепя частоты, разряаные выхоцы которого соединены с разрядными входами элемента переноса блока коррекции, управляющий вход которого поцкпючен к второму выходу бпока управления и управляющему входу запоминающего регистра бпока умножения , введены элемент совпадения и в блок умножения дополнительный элемент И, элемент запрета и делитель частоты, установочный вход которо- . го подключен к второму выходу бпока управления, вход - к первому вхоцу элемента ИЛИ блока умножения, второй вход которого соединен с первым входом бп ка управления,второй вход которого соедин с вторым выходом генератора опорной част ты,а выкод целителя частоты лока умноже ния соединен с первым входом .допопнитепьного элемента И этого бпок второй вхоц которого соединен с вторым входом синхронизатора и первым входом элемента совпадения, второй вхоц ко. торогосоединен с выходом элемента запрета, блока умножения, разрядные входы которого соединены с выходами . первого счетчика импульсов этого же бпока. На чертеже представлена структурная схема устройства. Устройство содержит синхронизатор блок 2 управления, генератор 3 опорной частоты, целитель 5 частоты, элемент 4 совпадения, блок 6 коррекци и бпок 7 умножения. Блок 6 коррекции состоит из элемента И 8, элемента 9 переноса,, счетчика 10 импульсов, эпе- мента ИЛИ 11. Бпок 7 умножения состоит из элемента 12 запрета, делителя 13 частоты, элемента ИЛИ L4, счетчиков 15 и 16 импульсов, запоминающего регистра 17, сумматора 18, эпемента 1 переноса, элемента И 20 и дополнитеш кого элемента И 21. Делитель 5, делитель 13 и счетчик являются двоичными суммирующими cчeтчикa tи, счетчик 10 и счетчик 16 явпякл-ся вычитающими двоичными cqei 8 Устройство работает следующим образом. Импульсы умножаемой частоты поступают на вход синхронизатора 1. При этом, , каждым входным импульсом со сдвигом на интервал времени О появляется импульс, совпадающий во времени с одним из импульсов эталонной частоты i, . д2 поступающей на вхоц блока 2. Блок 2 на каждый импульс синхронизатора формирует два импульса, разн&сГенных во времени. Длительность этик импульсов -, определяется частотой ioi (2-4)io2 Импульсы Q от генератора 3 через элемент 4 поступают на вход делите, ля 5, коэффициент деления которого равен заданному коэффициенту К умноже.ния. Импульсы, с выхода делителя 5, частота следова1 ия которых равна Ig /К, поступают на вход счетчика 15. Первым импульсом с блока 2 переписывается полученное значение кодов из делителя 5 через блок 9 в счетчик 10 и из счетчика 15 в регистр 17. Этим же импульсом делитель 13 сбрасывает ся в нуль, образуя на инверсном вы- . ходе последнего единичный уровень, обеспечивающий прохождение импульсов 1ог(ч8рез элемент 21 на счетчик 16. При этом, к моменту прихода . первого импульса с блока 2 на вход делителя 5 поступит 14 - импульсов. В счетчике 15 зафиксируется число импульсов Ni , равное целой части от целения N /К, а в делителе 5 зафиксируется остаток импульсов & N - N - N Второй импульс с блока 2 сбрасывает в ноль делитель 5 и счетчик 15, подготавливая их к новому заполнению в следующий период TgxИмпульсы с элемента 2О появляют ся каждый раз, как топько счетчик 16, переходит в нулевое состояние, н вычитаюший вход которого через элемент 21 подаются импупьсы io2 от генератора 3. При этом, (К - 1)-й импульс с эпемента 20 устанавливает на инверсном выхоце цешггеля 13 нулевой потенциал, который перекрывает доступ импупьсов частоты IQ на вычитающий счетчик 16. Kf-u импульс входной посп&цоватепьности поступает через эпемеит 14 с выхода синхронизатора 1. Каждым выходным импульсом устройства умножения значение выходного 5 ijotfe сумматора 18,равное копу NI , при & N О и N, U} при 4N : О перепис вается через эпемент 19 в счетнянк и процесс вычитания повторяется. Очевидно, что выходные импупьсы будут расставлены равномерно щщ N 1фатном К, т. е. при &N 0 При д N О блок коррекшш 6 осуществляет коррекцию расстановки вы-гходных импульсов по времени внутри периода Т вх. Коррекция производится ,спе дующим образом, . При d N О , значение которого накопится в счетчике 10, на выходе элемент 11, соединенного с входом мл шего сумматора 18, присутствует едшоршьтй уровень. Каждый выход ной импульс устройства переписывает выхооиой код сумматора 18, значение котсфото будет равно Н + 1 в счетЧ1ТК 16. В этом случае появление следующего выходного импульса будет позже на время Кроме того, импульсы с выхода элемента 14 через элемент 8 подаются на вычитающи вход счетчика 10 и из числа Л N вычитается единица. За время Tg эта операция производится AN раз пока счетчик 1О не установится в ноль. При этом, на выходе элемента 11 установится нулевой -уровень, запрещаю ишй прохождение импульсов на вычитак ишй вход счетчика 10 и исключающий коррекцию кода N регистра 17 при перезаписи его в счетчик 16. Минимальная частота i вх. min которой осуществляется равномерная расстановка импульсов на выходе умно теля частоты, определяется выражением.io2 Bx.min 98 где С, - максимальная емкость счетчика 15; К - коэффициент умножения. В циапазоне входных частот О - вх. min работу вступает блок 12 перекрытия доступа частоты f Q через элемент 4 на делитель 5, тем самым . сохраняя максимальный код С д, в счетчике 15. f , : Выходной (к - 1)-й импульс умножителя вырабатывает на инверсном выходе делителя 13 нулевой потенциал, запрещаюишй доступ импульсов io че- . элемент 21 на счетчик 16, тем самым прекращая доступ импульсов с элемента 20 на элемент 14. Импульсы на выходе умножителя частоты, могут появиться, только с приходом следующего импульса i g который обеспечивает прохождение частоты io2 на счетчик 16 и делитель 5. Таким образом, предлагаемый способ контроля выходных импульсов умноженной частоты позволяет обеспечить работоспособность устройства во всем диапазоне входных частот от .О до ... iBx.min Максимальная абсолютная погрешность любого из К выходных импульсов в диа- / пазоне умножаемых частот р , до tgif,тс,«внутри периода TBX не превышает значение TQ и определяется только погрешностью привязки импульсов входной частоты к импульсам частоты ig-j генератора,Следовательно,предлагаемое устройство позволяет уменьшить или вообще сключить динамическую ошибку в умножителе при иэдленении умножаемых чаоот в сторону увеличения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания графической информации | 1982 |

|

SU1086445A1 |

| Устройство для порогового контроля частоты | 1982 |

|

SU1051446A2 |

| Цифровой фазометр | 1982 |

|

SU1051451A1 |

| Цифровое устройство для решения системы линейных уравнений | 1976 |

|

SU624234A1 |

| Фазометр | 1982 |

|

SU1051450A1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU884102A1 |

| Устройство для скользящего усреднения электрических сигналов | 1977 |

|

SU624235A1 |

| Устройство для определения намолота зерна уборочным комбайном | 1981 |

|

SU1034641A1 |

| Устройство для считывания графической информации | 1982 |

|

SU1022189A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ, соцержащее блок коррекции, сострящий из послецоватепьно соединенных элемента переноса, счетчика имйульсов, элемента ИЛИ и элемента И, выкоа , которого поокпючен к счетному вкоцу . счетчика импульсов, блок умножения срстояишй из поспецовательно соециненных первого счетчика импульсов, запоминаюшего регистра, сумматора, элемента переноса второго счетчика импупьсов, элемента И и элемента ИЛИ, выхЬц к6торого поцключе1Г к управляющему вх:оцу элемента переноса и к второму вхоцу эпемента И, блока коррекции, перйый вхоц которого соецинен с входом млац шего сумматора, блока умножё-. кия, вторая группа вхоцов которого соецинена с шиной логического нуля, синхронизатор, первый вкоц которого к вкоцной шине, второй вхоц - к nej вому выхоцу генератора опорной частоты, а выхоц - к первому входу блока управления, первый выход которого среоинен с установочными входами целителя частоты и первого счетчика импульсов блока умножения, счетный вхоц которого соецинен с выходом целителя частоты, разрядные выходы которс«го соединены с разрядными вхоцами элемента переноса блока коррекций, управляющий вхоц которого пооключен к второму выхоцу блока управления и управляющему вкоду запоминающего регистра блока умножения, отличающееся тем, что, с целью повышения точности умножения и расширения функциональных возможностей устройства, в него ввеицены элемент совпадения и в блок умножения дополнительный элемент И, эле(Л мент запрета и целитель частоты, установочный вход подключен к С второму выходу блока управления, вхоц к первому входу элемента ИЛИ блока умножения, второй которого соединен с первым входом блока управпе ЕИЯ, второй вхоц которого соецинен с вторым г выходом генератора опорной частоты, а выхоц целителя частоты блока умнож&D U1 ния соединен с первым вхоцом цопопнвтельного Элемента .И этого блока, второй вход которого соецинен с вторым вхоцом синхронизатора и первым вхоцом эпемента совпадения, второй вхоц которого соецннен с выхоцом элемента запрета, блока умножения, рарядные входы которсяо соецинены с выходами первого счетчика импульсов этого же блока.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для умножения частоты следования периодических импульсов | 1976 |

|

SU576658A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU884102A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-09-07—Публикация

1982-01-12—Подача