1

Изобретение относится к измерительной технике, автоматике и может быть использовано в измерителях частоты, в системах регулирования с частотными датчиками и других устройствах для умножения частоты.

Известен умножитель частоты периодических импульсов, содержащий опорный генератор и блок заполнения, к выходу опорного генератора подключен делитель частоты с коэффициентом деления, равным требуемому коэффициенту умножения, а блок заполнения содержит два счетчика импульсов, первый подключен к делителю, а второй - к опорному генератору, запоминающий элемент, подключенный к выходам ячеек первого счетчика, и элемент сравнения, подключенный к выходам ячеек запоминающего элемента и второго счетчика импульсов, выход элемента сравнения соединен с выходом умножителя и через элемент ИЛИ - со входом установки нуля второго счетчика импульсов, причем вход

умножителя соединен с входом установки нуля запоминающего элемента и линией задержки, часть которой подключена к входу считывания первого счетчика, а конец - к входам установки нуля делителя и первого счетчика импульсов, а также к второму входу элемента ИЛИ l.

Недостатком указанного умножителя является относительно низкая точность умножения из-за ошибки, возникающей при определении периода входной частоты.

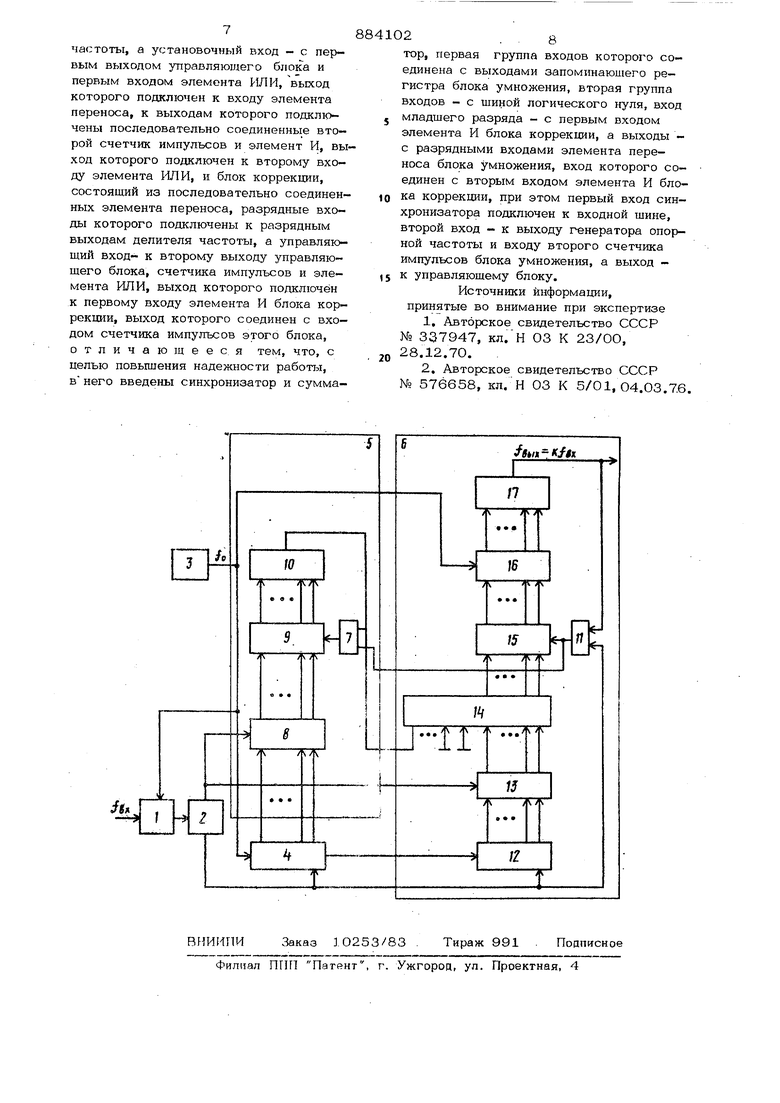

Наиболее близким по технической сущности к изобретению является устройство умножейия частоты следования импульсов,--содержащее управляющий блок, вход которого соединен с выходом входного формирователя, а первый выход - с установочным входом делителя частоты, генератор опорной частоты, выход которого под1слючен к первому управляющему . входу ключа и к входу делителя частоты, блок умножения, состоящий из элемента ИЛИ и последовательно соединенных первого счетчика импульсов, запоминающего регистра, элемента переноса, второго счетчика импульсов и эле мента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого объедиен с установочным входом первого счетчика импульсов и подключен к первому выходу управляющего блока, а выход - к управляющему входу элемента переноса, при этом вход первого счетчика импульсов соединен с выходом делителя частоты, вход запоминающего регистра - со вторым выходом управляющего блока, а вход второго счетчшса - с выходом ключа, и блок коррекции, состоящий из одновиб- ратора, цервого элемента И и последовательно соединенных блока переноса, счетчика и второго элемента И, причем вход одновибратора соединен с выходом элемента И блока умножения, разрядные выходы делителя частоты подключены к входам элемента переноса блока коррек Щ1И, управляющий вход которого соединен с вторым выходом управляющего бл ка, выход первого элемента И блока коррекции подключен к входу счетчика блока коррекции и ко второму управляющему входу ключа, первый вход - к выходу одновибратора, а второй вход - к выходу второго элемента И блока корре ции 2 J , Недостаток известного устройства низкая надежность работы. Цель изобретения - повьппение надеж 1иости работы устройства. С этой целью в устройство для умножения частоты следования импульсов, содержащее управляющий блок, первый выход которого соединен с установочным входом делителя чатоты, генератор опорной частоты, выход которого подключен к счетному входу делителя частоты, блок умножения, состоящий из за поминающего регистра, управляющий вхо которого подключен к второму выходу управляющего блока, а разрядные входы - к выходам первого счетчика импул сов, вход которого соединен с выходом делителя частоты, а установочный вход с первым выходом управляющего блока и первым входом элемента ИЛИ, выход которого подключен к входу элемента переноса, к выходам которого подключены последовательно соединенные второ счетчик импульсов и элемент И, выход ко торого подключен к второму входу элемен та , и блок коррекции, состоящий из следовательно соединенных элемента переноса, разрядные входы которого подключены к разрядным выходам делителя частоты, а управляющий вход - к второму выходу управляющего блока, счетчик импульсов и элемента ИЛИ, выход которого подключен к первому входу элемента И блока коррекции, выход которого соединен с входом счетчика импульсов этого блока, введены синхронизатор и сумматор, первая группа входов которого соединена с выходами запоминающего регистра блока умножения, вторая группа входов - с щиной логического нуля, вход младщего разряда с первым входом элемента И блока коррекции, а Выходы - с разрядными входами элемента переноса блока умножения,... вход которого соединен с вторым входом элемента И блока коррекции, при этом первый вход синхронинизатора подключен к входной .шине, второй вход - к выходу генератора опорной частоты и входу второго счетчика импульсов блока умножения, а выход - к управляющему блоку. На чертеже, представлена структурная электрическая схема устройства. Устройство содержит синхронизатор 1, выход которого подключен к входу управляющего блока 2, генератор 3 опорной частоты, делитель 4 частоты, блок коррекции 5 и бок умножения 6. Блок коррекции 5 состоит из элемента И 7 и последовательно соединенных элемента 8 переноса, счетчика 9 импульса и элемента ИЛИ 10. Блок умножения 6 содержит элемент ИЛИ 11 и последовательно соединенные первый счетчик 12 импульсов, запоминающий регистр 13, сумматор 14, элементы переноса 15, второй счетчик 16 импульсов и элемент И 17. Делитель 4 и счетчик 12 являются суммирующими двоичными счетчиками, счетчики 9 и 16 - вычитающими двоичными счетчиками. . Устройство работает следующим образом. Импульсы умножаемой частоты поступают на вход синхронизатора 1. При этом, перед каждым входным импульсом со сдвигом на интервал времени 4Jf о появляется импульс, совпадающий во времени с одним из импульсов эталонной частоты f Q , поступающий на вход блока 2.

Блок 2 на каждый импульс синхроизатора формирует два импульса. Длиельность первого импульса D l oВторой импульс образуется из первого мпульса путем задержки его на времяs

Импульсы от генератора 3 поступают на вход делителя 4, коэффициент деления которого равен заданному коэффи-Ю циенту К умножения.

Импульсы с выхода делителя 4, частота следования которых равна / К , поступают на вход счетчика 12.

Первым импульсом с управляющего15

блока 2 переписывается полученное значение кодов из делителя 4 через элемент 8 в счетчик 9 и из первого счетчика 12 в регистр 13.

При этом, к моменту прихода- перво- 20 го импульса с управляющего блока 2 на вход делителя 4 поступит N f импульсов.

В первом счетчике 12 зафиксируется. число импульсов N, равное целой части 25 от деления N/K,.а в делителе 4 зафиксируется остаток импульсов N -N.

Второй импульс с блока 2 через элемент 11 переписывает значение выходного кода сумматора 14, равного коду N1 30 О и N/1 + 1, при AN О, в счетчик 16 и сбрасывает в ноль делитель 4 и в счетчик 12, подготавливая их к новому заполнению в следующий период Tgy Выходные импульсы устройства умно- jj жения появляются каждый раз, как только счетчик 16 переходит в нулевое состояние, на вычитающий вход которого подаются импульсы f Q от генератора 3.

Каждым выходным импульсом уст- д

ройства умножения выходной код сумматора 14 переписьюается через элемент переноса 15 в счетчик 16, и процесс вьшитания повторяется

Очевидно, что выходные импульсы j будут расстановлены равномерно только при N -кратном К, т. е. при дЫ О.

При Ы О, блок 5 осуществляет коррекцию расстановки выходных импульсов по времени внутри периода Tgy . Коррекцня производится следующим образом.

При U.N ф-О, значение которого находится в счетчике 9, на выходе элемента ИЛИ 1О, соединенного с младшим разрядом второго входа сумматора 14, присутствует единичный уровень. Каждый выходной импульс устройства, либо второй импульс, вырабатываемый управляющим блоком 2, переписьюает выходной код сумматора 14, значение которого будет равно W. + 1, во второй счетчик 16. В этом случае появление следующего выходного импульса устройства будет позже на время Т. Кроме того, импульсы с выхода элемента 11 через элемент 7 подаются на вычитающий вход счетчика 9 и из числа дМ вычитается единица. За время Тру эта операция производится ДМ раз, пока счетчик 9 не установится в ноль. При этом на выходе элемента 10 устанавливается нулевой уровень, запрещаюший прохождение импульсов на вычитаюший вход счетчика 9 и исключающий коррекгцию кода Ы , запоминающего регистра 13 при перезаписи его на второй счерчик 16.

Таким образом, расстановка по времени ЛН выходных импульсов осуществляется путем коррекции кода N .

Кроме того, импульс, по которому осуществляется перезапись информации о измеренном периоде входной частоты, не может совпасть с импульсом опорного генератора, так как эти синхронны и всегда имеют определенный фазовый сдвиг.

Предлолсенный способ расстановки К выходных импульсов умножеигаой частоты и привязка их к входной частоте позволяет повысить надежность работы умножителя частоты.

Максимальная абсолютная погрешност любого из К выходных импульсов приведенного устройства для умножения частоты внутри периода Т не превышает значения Тр и определяется только погрещностью привязки импульсов входной частоты к импульсам опорного генератора.

Формула изобретения

Устройство для умножения частоты следования импульсов, содержащее управляющий блок, первый выход которого соединен с установочным входом делителя частоты, генератор опорной частоты, выход которого подключен к счетному входу делителя частоты, блок yivi- ножения, состоящий из запоминающего регистра, управляющий вход которого подключен к второму выходу управляк щего блока, а разрядные входы - к выходам первого счетчика импульсов, вход которого соединен с выходом делителя

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения частоты следования импульсов | 1982 |

|

SU1040598A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU705657A1 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU898600A1 |

| Устройство для умножения частоты следования периодических импульсов | 1976 |

|

SU576658A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU945964A1 |

| ЧАСТОТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ ЕРМАКОВА-ФЕДОРОВА (ВАРИАНТЫ) | 2007 |

|

RU2362175C2 |

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1780033A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ КОРРЕКЦИИ ПОГРЕШНОСТИ ЧАСТОТЫ ТАКТОВОГО ГЕНЕРАТОРА МИКРОКОНТРОЛЛЕРА (ВАРИАНТЫ) | 2008 |

|

RU2390786C1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

Авторы

Даты

1981-11-23—Публикация

1980-02-04—Подача