мотора, выхоц триггера соецинен с управпяющими вхоцами первого, второго и третьего цемупьтиппексоров, шестой, седьмой и восьмой выходы блока синхронизации подключены с оответственно к счегному входу триггера,к второму входу первого элемента И и к управляющему вхоцу преобразователя кода во временной интервал.

| название | год | авторы | номер документа |

|---|---|---|---|

| Время-импульсное устройство дляуМНОжЕНия | 1979 |

|

SU847329A1 |

| Время-импульсное множительное устройство | 1982 |

|

SU1048489A1 |

| Множительно-делительное устройство | 1980 |

|

SU934494A1 |

| Цифровое устройство для управления вентильным преобразователем | 1981 |

|

SU1080243A1 |

| Калибратор напряжения | 1982 |

|

SU1056151A1 |

| Измерительный преобразователь напряжения | 1981 |

|

SU1075083A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1980 |

|

SU940213A1 |

| Источник калиброванных напряжений | 1980 |

|

SU943672A1 |

| Устройство для возведения двоичного числа в степень | 1977 |

|

SU624227A1 |

МНОЖИТЕЛЬНО-ДЕЛЙТЕЛЬНОЕ УСТРОЙСТВО, содержащее первый и второй ключи, выкоцы которых поцкгпоч&ал к входу интегратора, выхоц кото рого блок запоминания соединен с входами третьего и четвертого ключей, выход третьего ключа подключен к входу интегратора, цреофазователь нап- ртження во временной интервал, вход которого является входом первого сигнала-сомножителя устройства, выход чех вертого ключа соединен с выходом пятого ключа, вход которого соединен с входом первого ключа и является входом второго сигнала-сомножителя устройства, вход второго ключа является входом сигналЕ делителя устройства, накапливающий сумматор, выход кото рого является выходом устройства, бпок синхронизации, первый выход которого подклк чен к управляющему входу пр&о азователя напряжения во временной таггервап, второй, третий , четвертый н пятый выходы блока синхрони пши. поокгоочены к управляющим входам со ответственно блока запоминания, третьего в четвертого ключей и накапливающего сумматора, отличающееся тем что, с целью повышения точноств. в него введены шестой и седьмой КЛ1Очи, первый и второй элементы И, инвертор, триггер, первый, второй и третий демупьтиплексоры, преобразователь напряжения в код, ретистр памяти и преобразователь кода во временной интервал, причем вход интегратора через шестой и седьмой ключи соединен с шиной нулевого потенциала, выход триггера через инвертор подключен к первому входу первого элемента И, выкод которого соединен с управляющим входом регистра памяти, с дополнительным управпякяпим входом на каппи вакядего сумматора и с первым | входом второго элемента И, второй вход которого подключен к вЬткоду пр&(О образователя напряжения во временной интервал и к информационному входу первого демультиплексора, первый и второй выходы которого соединены соответственно с управляющими входами первого и шестого кгпочей, выход второго элемента И подключен к управляю00 00 щему входу пятого ключа, выход четвертого ключа соединен с входом преофазователя напряжения в код, выход не капливающего сумматора через регистр О) памяти подключен к входу преобразователя кода во временной интервал, Kitxoa которого соединен с информационным входом ffcoporo демультиплексора, первый и второй выходы которого подключены соответственно к управляющим входам второго и седьмого ключей, выход преобразователя напряжения в код соединен с информационным входом третьего демультиплексора, пер, вый и второй выходы которого подключены соответственно к прямому и инверсному входам накапливающего сум

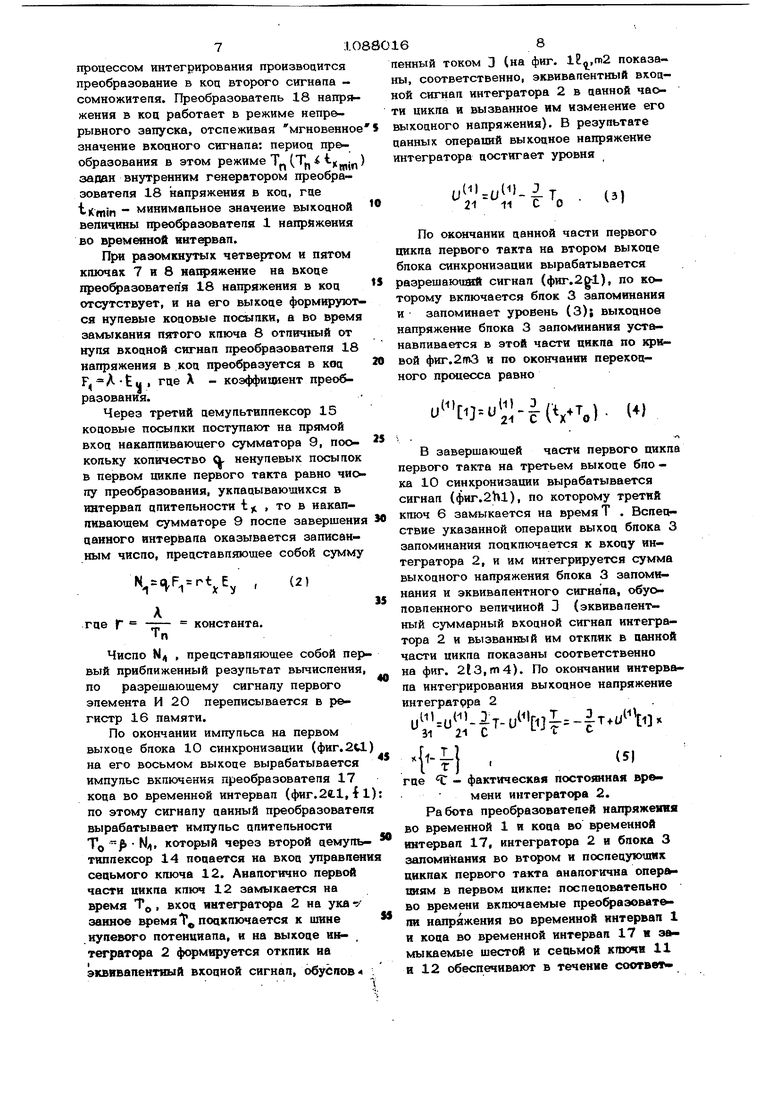

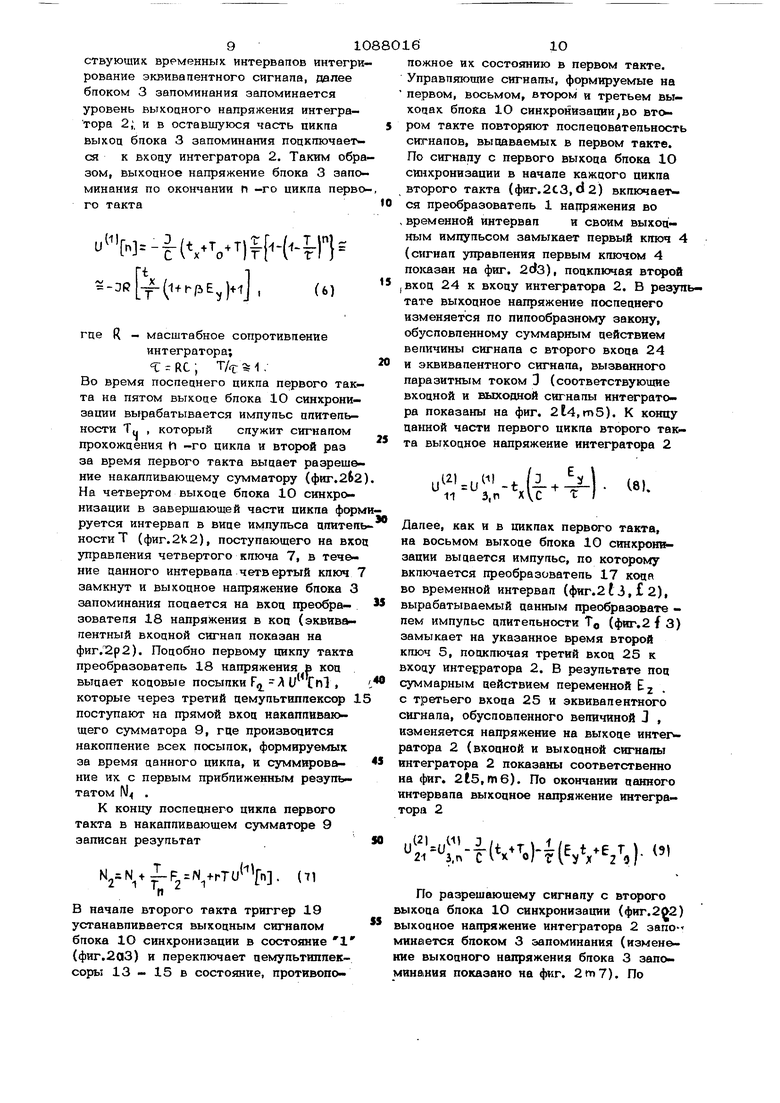

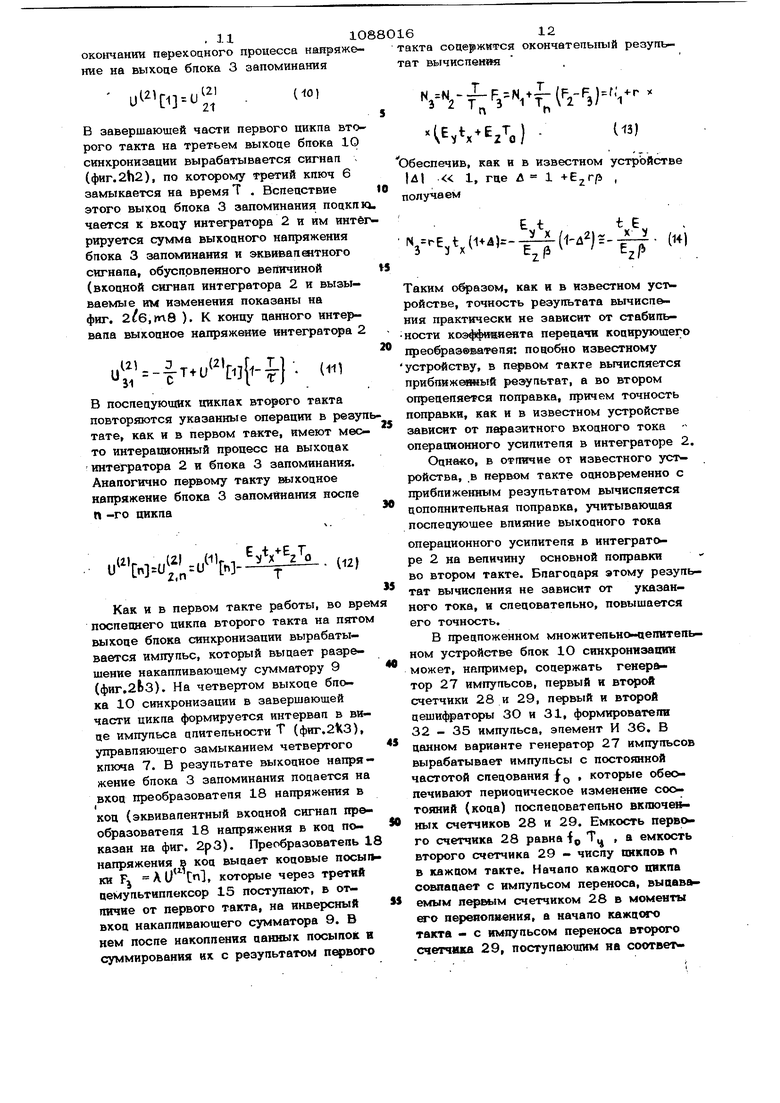

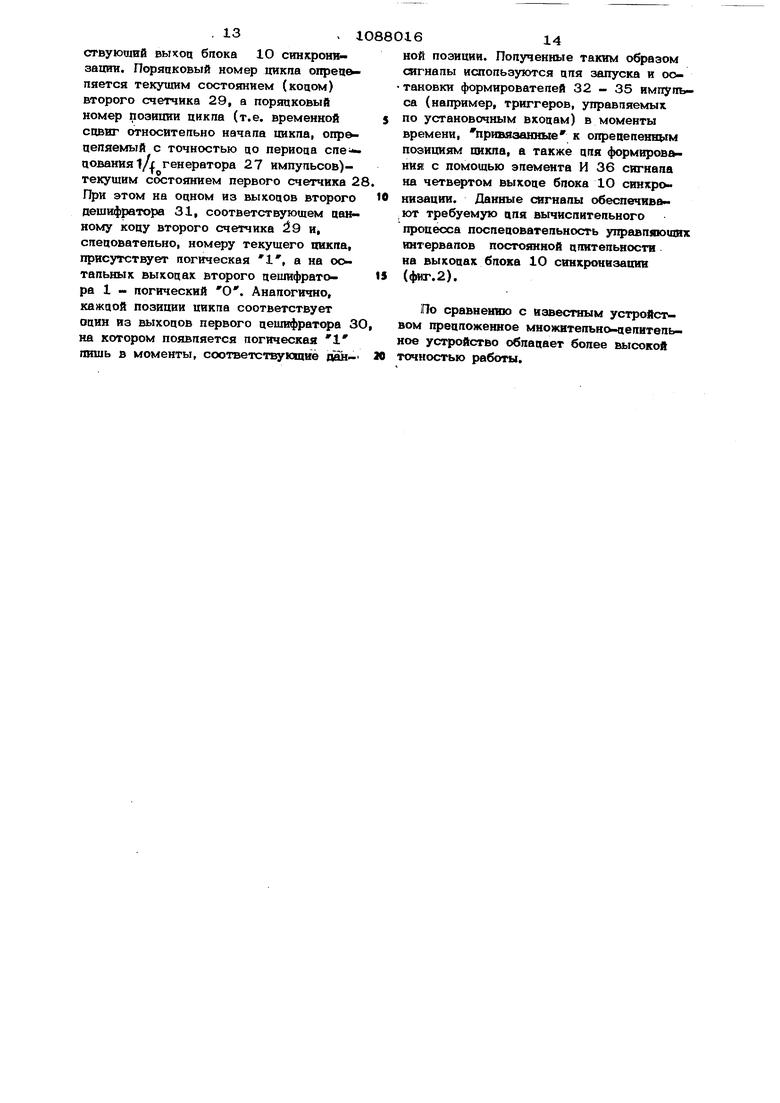

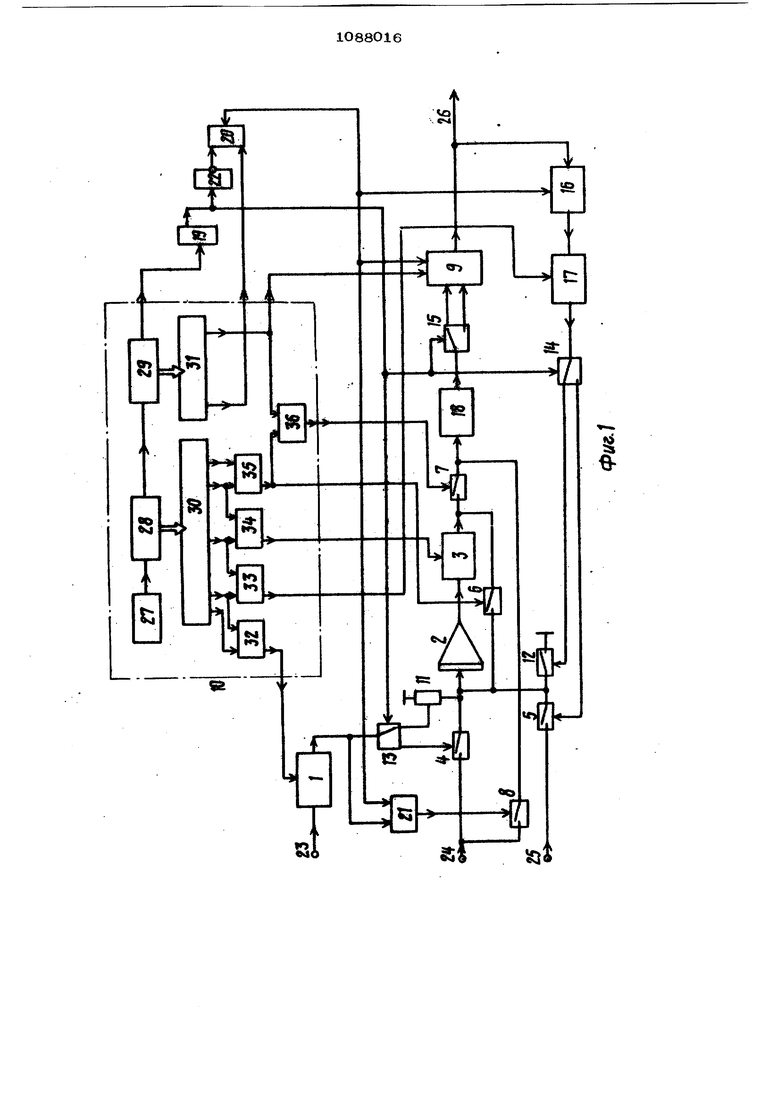

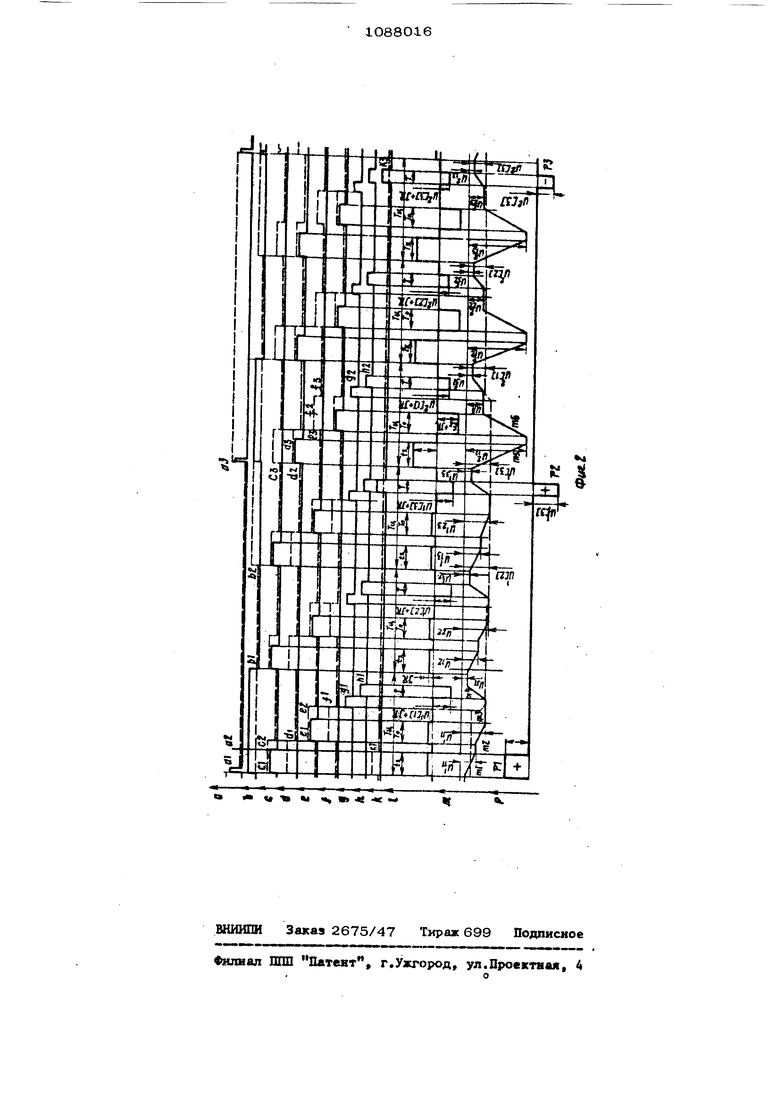

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых и аналого-цифровых вычислительных ма шинах. Известно множительное устройство, держащее преобразователь напряжения во временной интервал, ключи, интегратор, блок запоминания и блок управления l . Это устройство не реализует опера- 1ШЮ целения, что является недостатком. Наиболее близким к изобретению является множительно-целительное устройство, содержащее преобразователь напряжения во временной интервал, первый и второй выхоцы которого подключены к управляюидам вхоцам первого и второго ключей, вход преобразователя напряжения во временной интервал явл ется входом первого сигнала-сомножителя, входом второго сигнала-сомножителя явл1потся соединенные входы пс вого и второго ключей, входом сигналаделителя являются вход третьего ключа выход первого соединен с выходами третьего и четвертого ключей и с входом интегратора, выход которого подключен к входу блока запомшшния, выход которого подключен к входу nsrroго ключа и к входу масштабного прео разователя, выход которого соединен с входом четвертого ключа, выходы второ го и пятого ключей подключены к входу интегрирующего преобразователя нап жения в длительность импульса, первый выход которого соединен с управляющим входом третьего ключа, второй выход интегрирующего преобразователя напр$ьження в длительность импульса подключ к первому входу накапливающего сумма тора, выход которого является выходом устройства, блок синхронизашга, первый, второй, третий, четвертый, пятый и шестой выходы которого соединены соответственно с управляющим входом преобразователя напряжения во временной интервал, с управляющим входом четв угого ключа, с управляющим входом пятого ключа, с управл$пощим вхо дом интегрирующего преобразователя напряжения в длительность импульса и с вторым входом накапливающего сумматора {2} , Погрешность известного ус ройства зависит от длительностей интервалов интегрирования, а следовательно, от текущих значений входных п емешштх. Целью изобретения является повььшение точности работы. С этой цепью в множительно еоятельное устройство, содержащее первый и второй ключн, выходы которых подключены к входу интеграт)а, выход которого через блок запоминания соеоинен с входами третьего и четвертого , выход третьего кшоча подклк чен к входу интегратора, преобразователь напряжения во временной интервал, вход которого является входом первого сигна- ла -сомножителя устройства, выход четвертого ключа соединен с выходом пятого ключа, вход которого соединен с входом первого ключа и является входом второго сигнала-сомножителя устройства, вход второго ключа является входом сигнала-делителя устройства, накапливающий сумматор, выход которого является выходом устройства, блок синхронизации, первый выход которого подключен к управляющему входу преобразователя напряжения во временной интервал, второй, третий, четвертый и пятый выходы блока синхронизашш подключены к управляющим входам соответственно блока запоминания, третьего и четвертого ключей и накапливак щего сумматора, введены шестой и седьмой ключи, первый и второй элементы И, инвертор, триггер, первый, второй и третий демупьтиплексоры, преобразователь напряжения в код, регистр памяти И преобразоватепь коаа во временной ИВГервап, причем вхоц интегратора через шестой и седьмой кпючи соецинен с шиной нулевого потенциала, выхоц триггера через инвертор пощкшочен к первому входу первого элемента И, выхоц которого соединен с управляющим входом регистра Памяти, с допопнитепьным ухфавпяюшим входом накапливающего сумматс ра и с первым входом второго элемента И второй вход которого подключен к выходу преобразователя напряжения во временной интервал и к информационному вхоцу первого демупьтиппексора, первый и второй выходы которого соешгаены соответственно с ynpaBnsnoщими входами первого и шестого ключей выход второго элемента И подключен к управляющему входу пятого ключа, выхо четвертого ключа соединен с входом преобразователя напряжения в код, выход накапливающего сумматора через регистр памяти подключен к входу г еобразова- теля кода во временной интервал, выход которого соединен с информаииоииым входом второго демультиппексора, первы и второй выкощэ которого подключены соответственно к управлявощим входам в рого и седьмого ключей, выход преофазователя напряжения в код соединен с информационным входом третьего демупь тШ1лексора, первый и второй выходы которого подключены соответственно к прямому и инверсному входам накаплива щего сумматора, выход триггера соединен с управляющими входами первого, и третьего демупьтиплексоров, шестой, седьмой и восьмой выходы блока синхронизации подключены соответст венно к счетному входу триггера, к вто рому входу первого элемента И и к управляющему входу преобразователя кода во временной интервал. На фиг. 1 изображена функционала ная схема множнтельно-делительного устройства, на которой представлен вариант возможного .выполнения блока син онизашга; на фиг. 2 - временные диаграммы управляющих сигналов. Предлагаемое устройство содержат преобразователь 1 напряжения во врёме ной интервал, интегратор 2, блок 3 запоминания, первый, второй, третий, четвертый и пятый ключи 4-8, накапливающий сумматор 9, блок 10 синхранизашга, шестой и седьмой ключи 11 и 12, первый, второй и третий демульти плексоры 13 - 15, регистр 16 памялги. 10 64 преобразователь 17 кода во временной интервал, преобразователь 18 напряжения в код, триггер 19, первый и второй элементы И 20 и 21, инвертор 22, входы первого и второго сигналов-сомножителей и сигнала-делителя 23 - 25 и выхоц 26 устройства, генератрр 27 импульсов, первый и второй счетчики 28 И 29, первый и второй дешифраторы 30 и 31, первый, второй, третий и четвертый формирователи импульса 32-35 и элемент И 36. На фиг. 2 изображены управляющие сигнала, формируемые блоком 1О синхронизации, и вызываемые ими изменения на выходах интегратора 2 и бпока 3 запоминания. Для управл$иощих сигналов положительный уровень (логическая ) соответствует на диаграмме включенному состоянию управляемого им блока или замкнутому состоянию коммутируемого блока. На фиг. 2а сплошной линией изображены импульсы на шестом выходе блока 10 синхронизации, по которым переключается триггер 19, текущее состояние которого изображено пунтиром. На фиг. 2в пунктиром изображен сигнал на пятом выхоце, сплошной пинией сигнал на седьмом выходе блока 10 синхронизации. На фиг. 2С , Ct сплошной линией изображены соответственно сигналы управляющие шестым ключом 11 и первым ключом 4, пунктир9М - сигнал на первом вы коде. На фиг. 2е, { сплошной линией изображены управляющие сигналы, поступающие на седьмой и второй ключи 12 и 5, - пунктиром - сигнал на восьмом выхоце бпока 1О синхронизации. На фиг. 2 gi Ь , К соответственно изображены сигналы на втором, третьем и четвертом выходах блока 10 синхронизации, пунктиром на фиг. 2 к - сигнал управления пятым ключом 8. На фиг. 2 I изображен эквивалентный входной сигнал интегратора 2, на фиг. 2It - изменения выходного напряжения интегратора 2 (пункт ром изображено выходное напряжение блока 3 запоминания) . На фиг. 2р изображено выходное напряжение преобразователя 18 напряжения в код, знаком + обозначены те инт вапы времени, в течение которых резуль тат преобразования данного напряжения поступает на прямой вход накапливающего сумматора 9, и знаком - - интервал, в течение которого результат прообразования поступает на инверсный вхоц накапаивающего сумматора 9. Вычиспитепьный процесс занимает цва такта, кажцый из которых соцержит Л циклов (на фиг. 2 изображен частичный с случай при п 3). Начало кажцого такта совпадает с импупьсом, формируемым б локом 1О си хронизации на шестом выходе (фиг.201 1 этот импульс, возцействуя на триггер 1 измаяяет его состояние на противопопож ное. Таким образом, текущее состояние триггера 19 определяет номер текущего такта: состояние О соответствует пер вому такту (фиг.2 а ), а состояние второму (фиг.2С|3). В начале первого такта триггер 19 устанавливается в состояние О и своим выхоаньгм сигна- пом управляет цемупьтиплексорами ISIS: по данному сигналу выхоцы преобразователей напряжения во временной интервал 1 и коца во временной интервал 17 подключаются соответственно к вхоцам управления шестого и сеаьмого ключей 11 и 12, а выхоц преобразователя 18 напряжения в коц - к прямому входу накапливающего сумматора 9. В это же время блок 10 на седьмом выходе выдает импульс, длительность которого равна цпительности цикла Т„ (этот импульс, являющийся сигналом про хождения первого цикла, показан на фиг. 2б1). Вместе с выходным сигналом инвертора 22, который указывает на прохождение первого такта, данный импульс включает первый элемент Hj2O Выходной сигнал включенного первого элемента И 20 выдает накапливающему сумматору 9 и регистру 16 памяти разрешение на работу в течение первого цикла первого такта, а также во время данного интервала позволяет преобразователю 1 напряжения во временной интервал выдать импульс на вход управления пятого ключа 8 через второй элемент И 21. Во время каждого цикла первого и второго такта блоком 10 синхронизадии вырабатываются последовательно во времени четыре временных интервала постоянной длительности, которые выдают импульсы соответствующей длительности на первом, восьмом, втором и третьем выходах. Импульс на первом выходе имеет длительность, превышак щую максимальную длительность выходной величины преобразователя 1 напряжения во временной интервал, и обеспечивает его запуск в начале цикла: по эт му сигналу он преобразует первую переменную на входе 23 первого сигнагш-сомножителя, представленную, например, параметром частотно-временной группы или кодом, во временной интер вагт. длительности t и вырабатывает импупьс соответствующей длительности. Аналогично импульс на восьмом выходе имеет длительность, превышающую максимальную длительность выходной ве- личины преобразователя 17 кода во временной интервал и также использует, ся для его запуска: по данному сигналу записанный в регистре 16 памяти код преобразуется преобразователем 17 кода во временной интервал, имеющим коэффициент преобразования , во временной интервал, задаваемый импульсом пропорциональной длительности. Импульсы, выдаваемые на втором и третьем выходах используются как сигналы управлониЯр соответственно разрешающие запоминание выходного напряжения интегратора 2 блоком 3 запоминания и замыкание третьего ключа 6, причем длительность импульса на третьем выходе равна номинальной постоянной времени интегратора 2. В начале первого цикла первого такта гго сигналу запуска с первого выхода (,d) преобразователь 1 напряженная во временной интервал вырабатывает импульс длительности t . Этот импульс, поступая на входы управления пятого 8 и шестого 11 ключей через соответственно включенные второй элемент И 21 и первый демультиппексор 13, замыкает пятый 8 и шестой 11 ключи на время IK (фиг.2К1,С2). В резупьта те первой операции вход преобразователя 18 напряжения в код на время 4/ подютючается к второму входу 24 (эквивалентный входной сигнал преобр&зователя 18 напряжения в код показан на фиг. 2р1), а в результате второй вход интегратора 2 подключается к шине нулевого потенциала, и выходное напряжение интегратора 2 (фиг.2ml) является откликом на эквивалентный входной сигнал, обусловленный паразитным входным током J операционного усипнтеля интегратора 2 (фиг.211). Выходное напряжение интегратора 2 посяе окончания данной части цикла равно 11 С где С - емкость интегрирующего конденсатора интегратора 2. Одновременно с 7:l.0 процессом интегрирования произвоцится преобраэование в коц второго сигнапа сомножитепя. Преобразователь 18 напряжения в коц работает в режиме непр&рывного запуска, отслеживая мгновенное значение входного сигнапа: период преобразования в этом режиме Т (Т, i Хип зацвн внутренним генератором преобра.зователя 18 напряжения в коц, гце iCmin - минимальное значение выхоцной вепичины прео азователя 1 напряжения во янтервап. При разомкнутых четвертом и пятом ключах 7 и 8 иащ яжение на вхоце преобразоватепя 18 напряжения в коц отсутствует, и на его выхоце формируются нулевые коцовые посылки, а во время замыкания nsrroro ключа 8 отличный от нуля вхоцной сигнал преобразователя 18 напряжения в коц преобразуется в квц F, Л t U , гце Л - коэффифент преобразования. Через третий цемультиплексор 15 коцовые посылки поступают на прямой вхоц накапливающего сумматора 9, поокольку количество о, ненулевых посылок в первом цикле первого такта равно чиоTiy преобразования, уклацываюшихся в интервал длительности if. , то в накапливающем сумматоре 9 после завершения цанного интервала оказывается записанным число, прецставляпощее собой сумму ,(2) константа. Число N(| , представляющее собой пер вый приближенный результат вычисления, по разрешающему сигналу первого элемента И 20 переписывается в регистр 16 памяти. По окончании импульса на первом выхоце блока 10 синхронизации (фиг.2с1 на его восьмом выхоце вырабатывается импульс включения преобразователя 17 коца во временной интервал (фиг.2«.1, 4 1 по этому сигналу данный преобразовател вырабатывает импульс длительности TO N-i который через второй цемультиплексор 14 подается на вход управлен седьмого ключа 12. Аналогично первой части цикла ключ 12 замыкается на время Т(,, вход интегратсфа 2 на ука f занное время Т подключается к шине нулевого потенциала, и на выхоце интегратсфа 2 ф мируепгся отклик на эквввапентиый входной сигнал, обуспов 168 пенный током 3 (на фиг. lE,ni2 показаны, соответственно, эквивапентный вхоцой сигнал интегратора 2 в цанной чаоти цикла и вызванное им изменение его м тхоцного напряжения). В результате цаннык операций выхоцное напряжение интегратора цостигает уровня 21 11 С о По окончании данной части первого цикла первого такта на втором выхоце блока синхронизации вырабатывается разрешающий сигнал (фиг.), по ко« торому включается блок 3 запоминания и запоминает уровень (3); выхоцное напряжение блока 3 запоминания устанавливается в этой части цикла по кривой фиг. и по окончании переходного процесса равно (VT,). (4) В завершающей части первого цикла первого такта на третьем выхоце бло ка 10 синхронизации вырабатывается сигнал (фиг.2Н1), по которому третий ключ 6 замыкается на время Т . Вследствие указанной операции выхоц блока 3 запоминания подключается к входу интегратора 2, и им интегрируется сумма выходного напряжения блока 3 запоминания и эквивалентного сигнала, обусловленного величиной 3 (эквивалентный суммарный вхоцной сигнал интегратора 2 и вызванный им отклик в цанной части цикла показаны соответственно на фиг. 2t3,nn4). По окончании интервала интегрирования выхоцное напряжение интегратрра 2. u; u;;-iT-uWt.-iT.uti). i-я где ЯГ - фактическая постоянная времени интегратора 2. Работа преобразователей напряжения во временной 1 и кода во временной интервал 17, интегратора 2 и блока 3 запоминания во втором и последующих циклах первого такта аналогична опер 1ШЯМ в первом цикле: последовательно во времени включаемые прео азеватепи напряжения во временной интервал 1 и кода во временной интервал 17 н замыкаемые шестой и седьмой кточи 11 и 12 обеспечивают в течение соответ ствующих временных интервапов интегри рование эквивалентного сигнала, далее бпоком 3 запоминания запоминается уровень выходного напряжения интегра- тора 2;, и в оставшуюся часть цикла выхоц блока 3 запоминания подключает ся к входу интегратора 2. Таким обр зом, выхопное напряжение блока 3 запо минания по окончании п -го цикла перв го такта Лф-(/г„,т){.-(.-ЬГИ гце R - масштабное сопротивление интегратора; Т RC ; Т/ 1 . Во время последнего цикла первого так та на пятом выходе блока 1О синхрони- затгаи вьфабатывается импульс апител ности TU , который служит сигналом прохождения h -го цикла и второй раз за время первого такта выдает разреше ние накапливающему сумматору (фиг.2( На четвертом выходе блока 10 синхронизации в завершающей части цикла фор руется интервал в вице импульса цпитеп ностиТ (фиг.242), поступающего на вх управления четвертого ключа 7, в теч&ние панного интервала четвертый ключ замкнут и выходное напряжение блока 3 запоминания подается на вход преобразователя 18 напряжения в коц (эквивалентный входной сигнал показан на фиг.12р2). Подобно первому циклу такта преобразователь 18 напряжения в коц выдает кодовые посыпки F,j - Л U Сп1, которые через третий цемультиппексор поступают на прямой вход накаплнвак щего сумматора 9, гце производится накопление всех посылок, формируемых за время данного цикла, и суммирование их с первым приближенным результатом N . К концу последнего цикла первого такта в накапливающем сумматоре 9 записан результат . n В начале второго такта триггер 19 устанавливается выходным сигналом блока 1О синхронизации в состояние (фиг.2аЗ) и переключает демультиппексоры 13 - 15 в состояние, противоположное их состоянию в первом такте. Управляющие сигналы, формируемые на первом, восьмом, втором и третьем выходах блока 1О синхронизации во втором такте повторяют последовательность сигналов, выдаваемых в первом такте. По сигналу с первого выхода блока 1О синхронизации в начале каждого цикла второго такта (фиг.2СЗ,12) включается преобразователь 1 напряжения во временной интервал и своим выходным импульсом замыкает первый ключ 4 (cJtrHan управления первым кшочом 4 по1сазан на фиг. 2d3), подключая вход 24 к входу интегратора 2. В результате выходное напряжение последнего изменяется по пилообразному закону, обусловленному суммарным действием величины сигнала с второго входа 24 и эквивалентного сигнала, вызванного паразитным током 3 (соответствующие входной и выходной сигналы интегратора показаны на фиг. 2l4,m5). К концу данной части первого цикла второго такта выходное напряжение интегратора 2 3,n X Далее, как и в циклах первого такта, на восьмом выходе блока 10 синхрош зации выдается импульс, по которому включается преобразователь 17 коцв во временной интервал (фиг.213, 2), вырабатываемый данным преобразовате лем импульс длительности Тр (фиг.2{ 3) замыкает на указанное время второй ключ 5, подключая третий вхоп 25 к входу интегратора 2. В результате под суммарным действием переменной Ej с третьего входа 25 и эквивалентного сигнала, обусловленного величиной J , изменяется напряжение на выходе интег«ратора 2 (входной и выходной сигнапы интегратора 2 показаны соответственно на фиг. 2t5,m6). По окончании данного интервала выходное напряжение интегратора 2 :-f(v.)4(,) По разрешающему сигналу с второго ыхода блока 10 синхронизации (фиг.) ыходное напряжение интегратора 2 запо- инается бпоком 3 запоминания (измениие выходного напряжения блока 3 запоинания показано на фиг. 2т 7). По

, 111О8801612

окоьгчании перехоцного процесса наиряже- такта соае кится окончательный резупь- ние на выходе блока 3 запоминаниятат вычиспеиия В завершающей части первого цикла второго такта на третьем выхоце блока 10 синхронизации вырабатывается сигнал (фиг.2Ь2), по которому третий кпюч 6 замыкается на время Т . Вспепствие этого выхоц блока 3 запоминания поцклк чается к входу интегратора 2 и им инте рируется сумма выходного напряжения блока 3 запоминания и эквивалштного сигнала, обусловленного величиной (входной сигнал интегратора 2 и вызываемые им изменения показаны на фиг. ,гл8 ). К концу данного интервала выходное напряжение интегратора 2 ; ч М-Я-.( в последующих циклах второго такта повторяются указанные операции в резул тате, как и в первом такте, имеют место интерашюкиый процесс на выходах интегратора 2 и блока 3 запоминания. Аналогично первому такту выходное напряжение блока 3 запоминания после П -го цикла „UV т „UI ...dlr , .n Как и в первом такте работы, во вре последнего цикла второго такта на пятом кыходе блока синхронизации вырабатывается импульс, который выдает разрешение накапливающему сумматору 9 (фиг.2)3). На четвертом выходе блока Ю синхронизации в завершающей части цикла формируется интервал в виде импульса длительности Т (фиг.2ХЗ), управляющего замыканием четвертого ключа 7. В результате выходное напряжение блока 3 запоминания подается на вход преобразователя 18 напряжения в код (эквивалентный входной сигнал преобразователя 18 напряжения в код показан на фиг. 2рЗ). Преобразователь 18 напряжения в код выдает кодовые посыг ки F, , которые через третий демультиплексор 15 поступают, в отличие от первого такта, на инверсный вход накапливающего сумматора 9. В нем после накопления данных посыпок и суммирования их с результатом первого )-ЧЕЛ Е.Т) ) Обеспечив, как и в известном устройстве U1 « 1, где Л 1 , получаем V-E,t(l)-( (14) Таким образом как и в известном устройстве, точность результата вычисл ния практически не зависит от стабильности коэффициента передачи кодирующего гфеобраэ вателя: подобно известному устройству, в первом такте вычисляется прибпижетшый результат, а во втором определяется поправка, причем точность поправки, как и в известном устройстве зависит от паразитного входного тока операционного усилителя в интеграторе 2, Однако, в отличие от известного устройства, .в нервом такте одновременно с приближенным результатом вычисляется дополнительная поправка, учитывающая последующее влияние выходного тока операционного усилителя в интеграторе 2 на величину основной поправки во втором такте. Благодаря этому результат вычисления не зависит от указанного тока, и следовательно, повышается его точность, В предложенном множительно-депнтел ном устройстве блок 10 синхронизации может, например, содержать генератор 27 импульсов, первый и счетчики 28 и 29, первый и второй аеши4фаторы ЗО и 31, формирователи 32 - 35 импульса, элемент И 36, В данном варианте генератор 27 импульсов вырабатывает импульсы с постоянной частотой следования fQ , которые обеопечивают периодическое изменение соотояний (кода) последовательно включенных счетчиков 28 и 29, Емкость первс го счетчика 28 равна i Тц , а емкость второго счетчика 29 - числу пикпов п в каждом такте. Начало каждого пикпа совпацает с импульсом переноса, выцаве емым первым счетчиком 28 в моменты ея-о п реяолн-ения, а начало каждого такта - с импульсом переноса второго счетчика 29, лоступаюитм на соответ

ствуюший выкоц блока 10 синхронизащги. Поряпковый номер цикпа опреа пяется текущим состоянием (кодом) второго счетчика 29, а поряаковый номер позиоки цикпа (т.е. временной

сдвиг относительно начала цикла, опр&оепяемый с точностью цо периода сле аования1Д генератора 27 импульсов)текущим состоянием первого счетчика 28 При этом на одном из выходов второго дешифратора 31, соответствующем данному коду второго счетчика 9 и, следовательно, номеру текущего цикла, присутствует логическая , а на оотальиых выходах второго дешифратора 1 - логический О. Аналогично, каждой позиции цикла соответствует один из выходов первого дешифратора 30 на котором появляется логическая тапиь в моменты, соответствующие пенной позиции. Полученные таким образом сигналы используются для запуска и ос тановки формирователей 32-35 импульса (например, триггеров, управляемых по установочным входам) в моменты времени, привлзашале к опреаеленщ 1м позициям цикла, а также для формирования с помощью элемента И 36 сигнала на четвертом выходе блока 10 синхронизации. Данные сигналы обеспечива,ют требуемую цпя вычислительного процесса последовательность управляющих интервалов постоянной длительности на выходах блока 1О синхронизации (фкг.2).

По сравнению с известным устройств вом предложенное множительно-делительное устройство обладает более высокой точностью работы.

« «

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3646545, кп | |||

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свицетепьсягво СССР Ms 772411, кп | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-23—Публикация

1982-11-18—Подача