-Изобретение относится к импульсной технике, а именно к счетчикам .импульсов, в которых импульсы .непрерывно циркулируют в замкнутом шлейфе, содержащем линии задержки, и может быть применено в вычислительной технике и радиоприемной аппаратуре с цифровой -обработкой информации ....

Известен двоично-десятичный счетчик импульсов, содержащий замкнутый контур циркуляции импульсов, образованный полусумматорсяи, подключенным входом А и выходом S к линии задержки. Вход В и выход С полусумматора, соединенные с однобитовой линией задержки и элементом ИЛИ, образуют цепь переноса импульса в .следующий разряд Cl.

Недостатком данного устройства является наличие цепи переноса импульса в следующий разряд, что ведет к снижению быстродействия.

Известен накапливающий двричный счетчик., содержащий линию задержки, три элемента И, элемент НЕ, триггер,.элемент ИЛИ, элемент задержки и блок синхронизации. Первый элемент И входами соединен с выходом линии задержки и .нулевым выходом триггера. Выход первого элемента И подключен к первому входу элемента ИЛИ, выход которого соединен с входом линии задержки. Второй элемент И входами соединен через элемент НЕ с выходом линии задержки и единичным выходом триггера, выход второго элемента И соединен с вторым входом элемента ИЛИ и через элемент задержки с нулевым входом триггера. Третий элемент И входом соединен с выходом блока-синхронизации, а выходом с единичным входом триггера, входная шина соединена с входом блока синхронизации. В данном устройстве сокращено количество элементарных логических элементов, тем самым уменьшено время обработки импульса, т.е. увеличено быстродействие счетчика С2 .

Однако наличие цепи переноса импульса в следующий разряд, образованной вторым элементом и, элементом задержки,и триггером, ведет к снижению быстродействия счетчика.

Цель изобретения - повьанение быстродейс.твия.

Поставленная цель достигается тем, что в накапливающий двоичный счетчик, содержащий входную шину, блок (синхронизации, первый пороговый элемент ИЛИ, два пороговых элемента И, элемент НЕ и первую линию задержки, вход которой соединен с выходом первого порогового элемента ИЛИ, первый вход которого соединен с выходе первого порогового элемента И, выход элемента НЕ соединен с первым входом второго пороговрго элемента И, входная шина соединена с входом блока синхронизации,вве-i дены вторая линия задержки, связанная с первой линией задержки неурав новешенной электромагнитной связью, второй пороговый элемент ИЛИ, два усилителя и аттенюатор, вход которого соединен с первым входом первого порогового элемент-а И и с выходом первой линии задержки, выход второй линии задержки соединен с инверсным входом первого усилителя и с входом.второго усилителя, выход которого соединен с вторым входом первого порогового элемента И, выхо которого соединен с первым входом второго порогового элемента ИЛИ, выход которого соединен с вторым входом второго порогового элемента И, выход которого соединен с входом второй линии задержки, выход первого усилителя соединен с вторыми входами, первого и второго пороговых элементов ИЛИ, выходы блока синхронизации и аттенюатора соединены сооветственно с третьим входом первого порогового элемента ИЛИ и входом элемента НЕ.

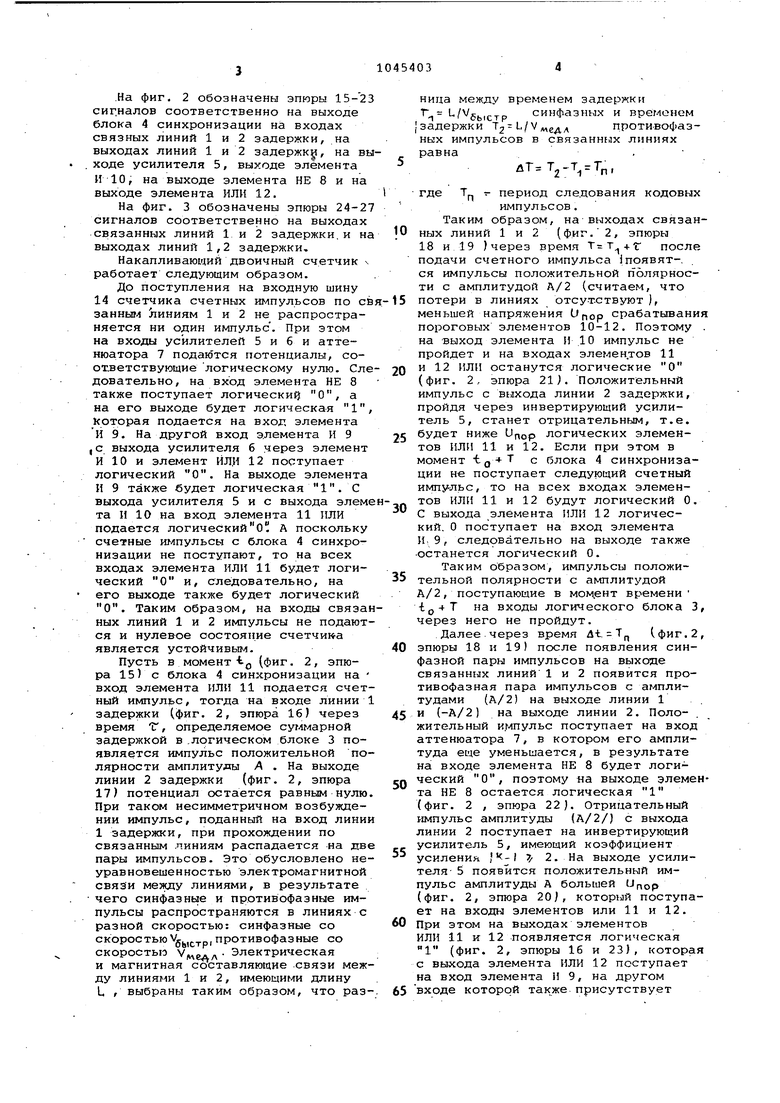

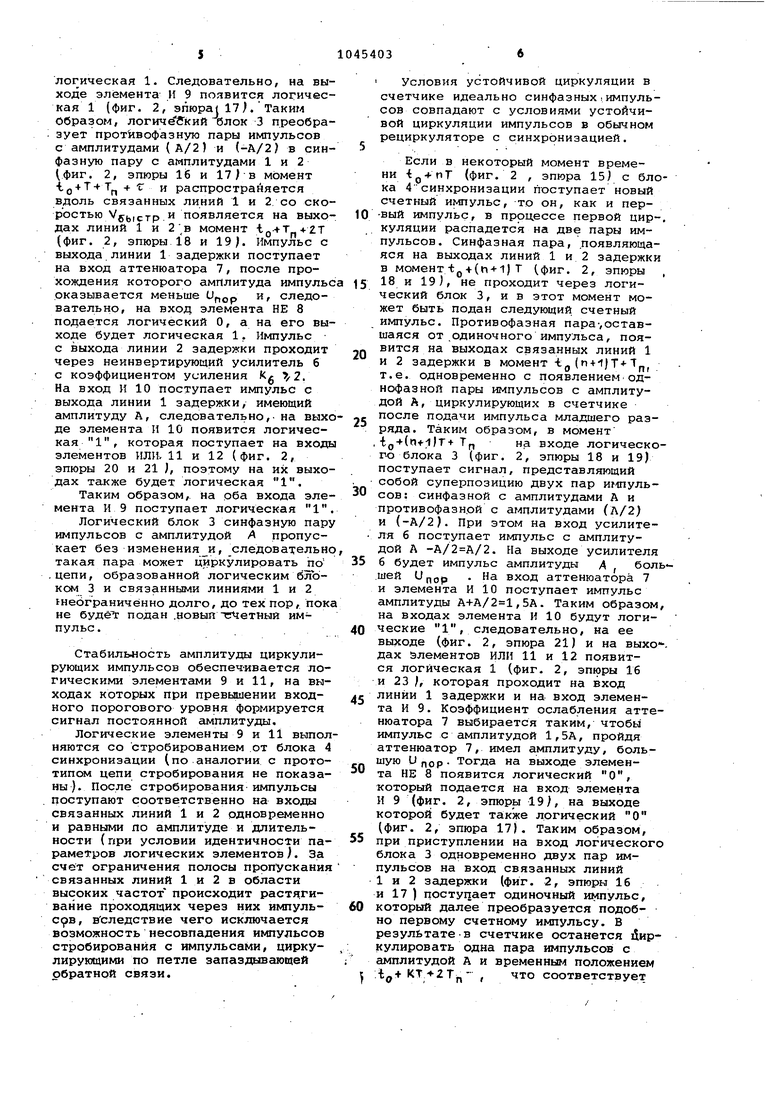

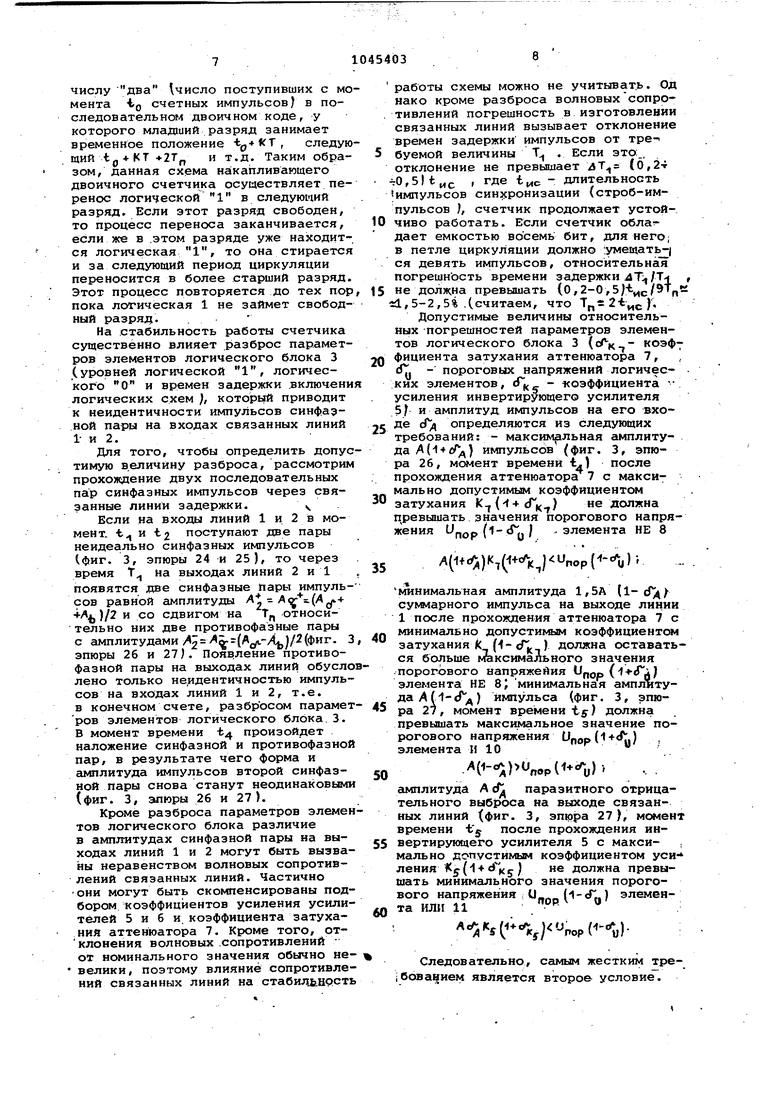

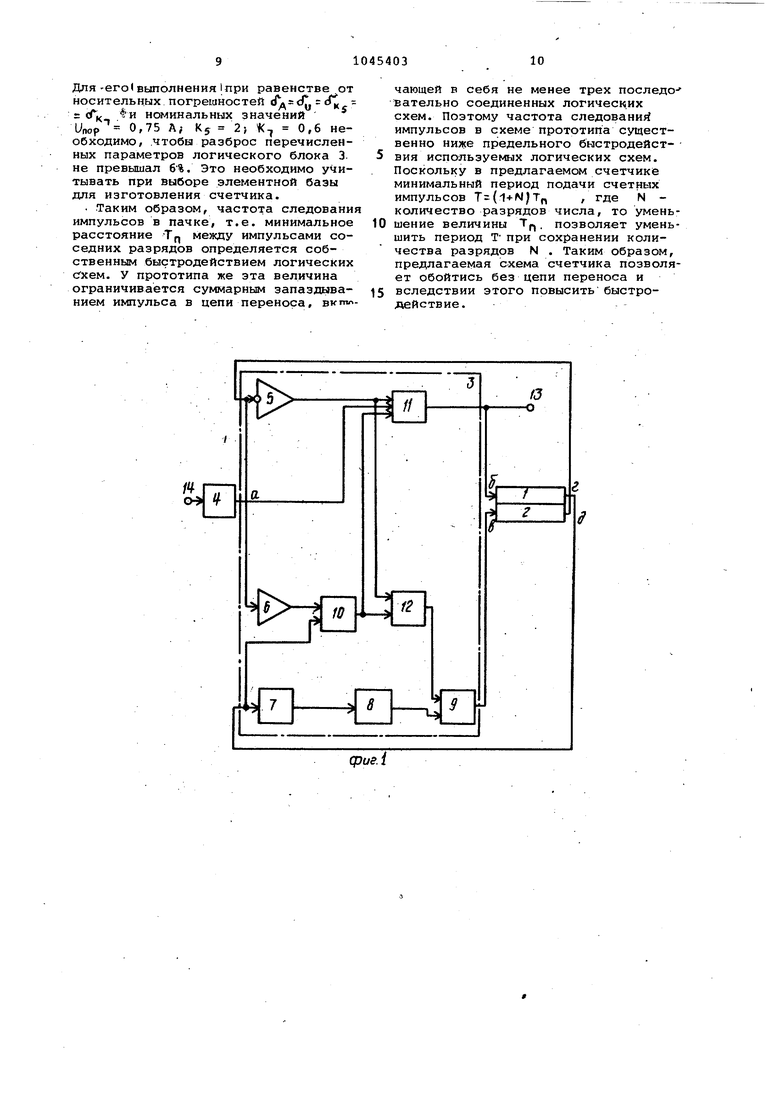

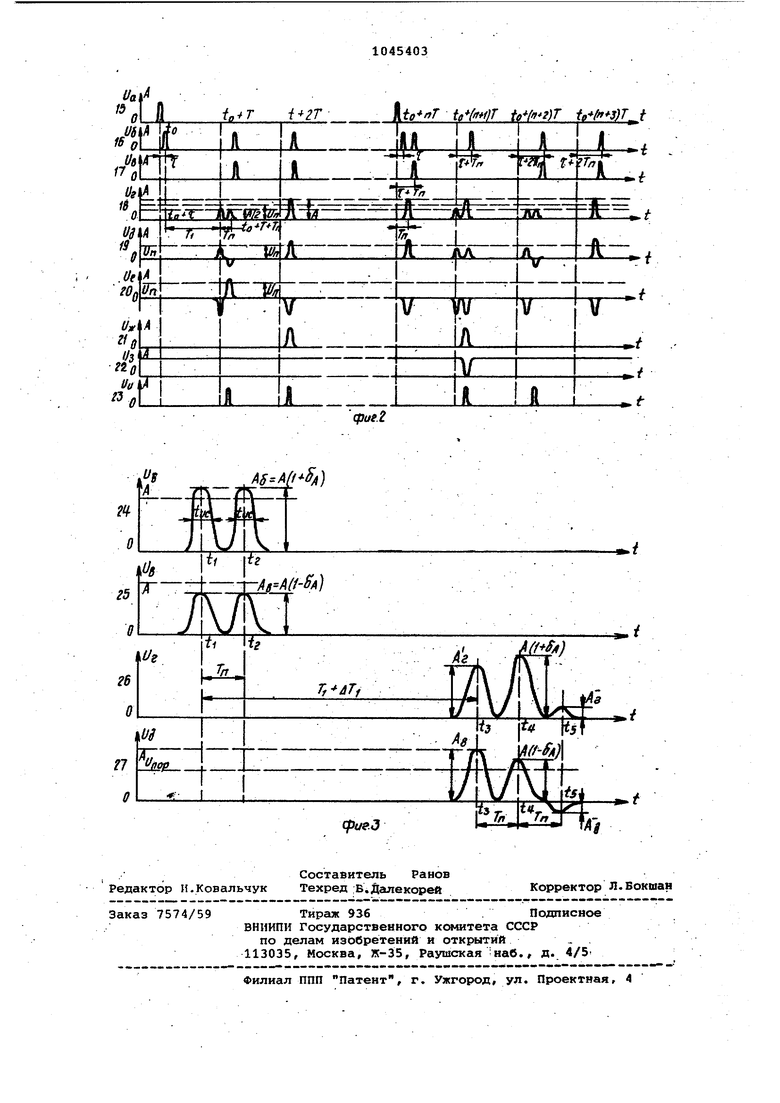

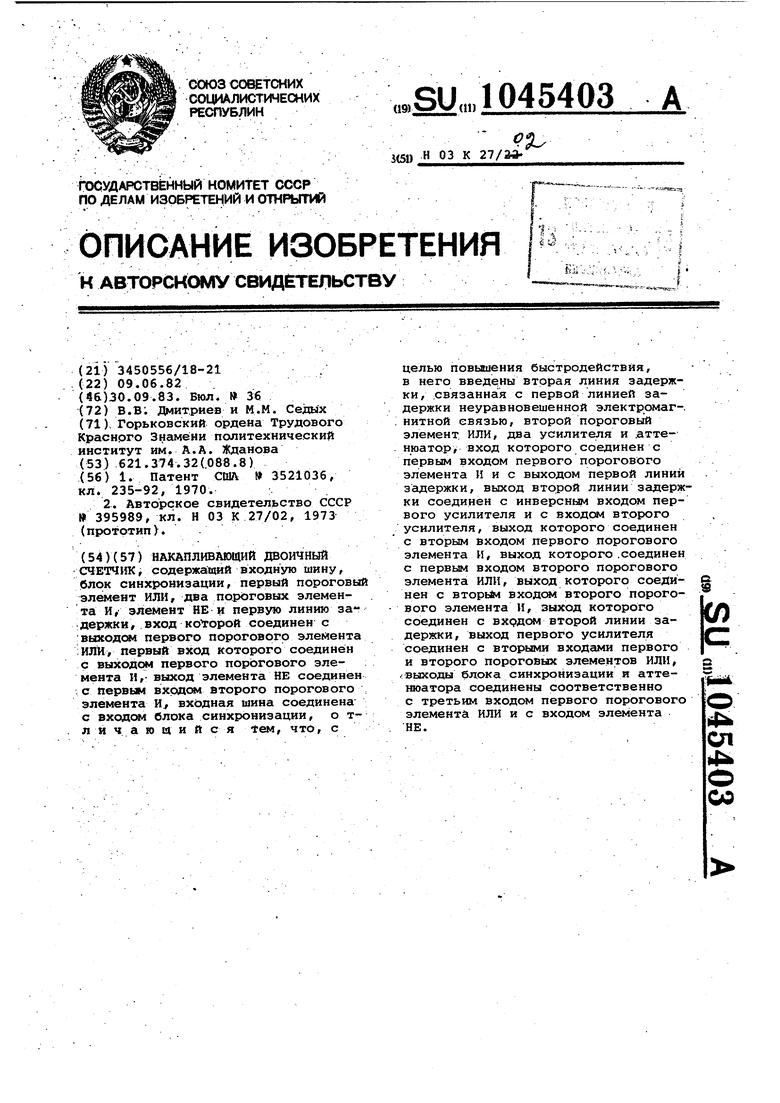

На фиг. 1 представлена схема накапливающего двоичного счетчика; :на .фиг. 2 и 3 - эпюры сигналов в характерных точках устройства.

Схема содержит связанные линии 1 и 2 задержки, логический блок 3, блок 4 синхронизации, усилители. 5 и 6, аттенюатор 7, элемент НЕ 8, пороговые элементы И 9 и 10, пороговые элемен ты ИЛИ 11 и 12, выходную шину 13 и входную шину 14.

Выход элемента ИЛИ 11 соединен с выходной шиной- 13 и с входом линии 1 задержки, выход которой соединен с входом аттенюатора 7 и с первым входом элемента И 10, выход которого соединен с первыми входами элементов ИЛИ 11 и 12, выход последнего из которых соединен с первым входом элемента И 9, второй вход которого соединен с выходом элемента НЕ 8, вход которого соединен с выходом аттенюатора 7, выход элемента И 9 соединен с входом линии 2 задержки, выход которой соединен инверсным входом усилителя 5 и с входом усилите:ля б, выход которого соединен с вторым входом элемента И 10, выход усилителя 5 соединен с вторыми входами элементов ИЛИ 11 и 12, входная шина 14 соединена с входом блока- 4 синхронизации, выход которого соедрнен с третьим входом элемента ИЛИ 11.,

Логический блок 3 содержит усилители 5 и б, аттенюатор 7, элемент НЕ 8, элементы И 9 и 10 и элементы ИЛИ 11 и 12.

.На фиг, 2 обозначены эпюры 15-23 сигналов соответственно на выходе блока 4 синхронизации на входах связных линий 1 и 2 задержки, на выходах линий 1 и 2 задержки, на выходе усилителя 5, выходе элемента И10, на выходе элемента НЕ 8 и на выходе элемента ИЛИ 12.

На фиг. 3 обозначены эпюры 24-27 сигналов соответственно на выходах связанных линий 1м 2 задержки.и на выходах линий 1,2 задержки.

Накапливающий двоичный счетчик ч работает следующим образом.

До поступления на входную шину 14 счетчика счетных шлпульсов по связанным линиям 1 и 2 не распространяется ни один импульс. При этом на входы усилителей 5 и б и аттенюатора 7 подаются потенциалы, соответствующие логическому нулю. Следовательно, на вход элемента НЕ 8 также поступает логически О, а на его выходе будет логическая 1, Которая подается на вход элемента И 9. На другой вход элемента И 9 с выхода усилителя б через элемент И 10 и элемент ЙЛ.И 12 поступает логический О. На выходе элемента И 9 также будет логическая 1. С выхода усилителя 5 и с выхода элемента Н 10 на вход элемента 11 ИЛИ подается логический О А поскольку счетные шлпульсы с блока 4 синхронизации не поступают, то на всех входах элемента ИЛИ 11 будет логический О и, следовательно, на его выходе также будет логический О. Таким образом, на входы связанных линий 1 и 2 импульсы не подаются и нулев-ое состояние счетчика является устойчивым.

Пусть в момент-tg (фиг, 2, эпюра 15) с блока 4 синхронизации на вход элемента ИЛИ 11 подается счетный импульс, тогда на входе линии 1 задержки (фиг. 2, эпюра 16) через время Т, определяемое суммарной задержкой в .логическом блоке 3 появляется импульс положительной полярности амплитуды А , На выходе линии 2 задержки (фиг. 2, эпюра 17) потенциал остается равным нулю. При таком несимметричном возбуждении импульс, поданный на вход линии 1 задержки, при прохождении по связанным .пиниям распадается на лае пары импульсов. Это обусловлено неуравновешенностью электромагнитной связи между линиями, в результате чего синфазные и пр.отивофазные импульсы распространяются в линиях с разной скоростью: синфазные со скороетьюVg противофазные со скоростью Электрическая и магнитная составляющие связи между линиями 1 и 2, имеющими длину L , выбраны таким образом, что раз-.

ница между временем задержки

Г .. синфазных и временем

задержки Т2 Ь/У„едд

проти-вофазных импульсов связанн.1х линиях равна

Т,,

где Т период следования кодовых импульсов.

Таким образом, на выходах связанных линий 1 и 2 (фиг, 2, эпюры 18 и 19 ) через время .-i-f после подачи счетного импульса {появят-. ся импульсы положительной полярности с амплитудой А/2 (считаем, что потери в линиях отсутствуют), меньшей напряжения срабатывани пороговых элементов 10-12, Поэтому на выход элемента И 10 импульс не пройдет и на входах элемен.тов 11 и 12 ИЛИ останутся логические О (фиг, 2, эпюра 21), Положительный импульс с выхода линии 2 задержки, пройдя через инвертирующий усилитель 5, станет отрицательным, т.е. будет ниже логических элементов ИЛИ 11 и 12. Если при этом в момент tg + T с блока 4 синхронизации не поступает следук)щий счетный импу-льс, то на всех входах элементов ИЛИ 11 и 12 будут логический 0. С выхода элемента ИЛИ 12 логический. О поступает на вход элемента И.9, следовательно на выходе также останется логический 0.

Таким образом, импульсы положительной полярности с амплитудой А/2, поступающие в монент времени на входы логического блока 3 через него не пройдут.

Далее через время Д-Ь, Т, (фиг, 2 эпюры 18 и 19) после появления синфазной пары импульсов на выходе связанных линий1 и 2 появится противофазная пара импульсов с амплитудами (А/2) на выходе линии 1 и (-А/2) на выходе линии 2. Положительный и.мпульс поступает на вход аттенюатора 7, в котором его амплитуда еще уменьшается, в результате на входе элемента НЕ 8 будет логический О, поэтому яа выходе элемета НЕ 8 остается логическая 1 (фиг. 2 , эпюра 22), Отрицательный импульс амплитуды (А/2/) с выхода линии 2 поступает на инвертирующий усилитель 5, имеющий коэффициент усиления 2. На выходе усилителя- 5 появится положительный импульс амплитуды А большей (фиг. 2, эпюра 20), который поступает на входы элементов или 11 и 12, При этом на выходах элементов ИЛИ 11 и 12 появляется логическая 1 (фиг. 2, эпюры 16 и 23), котора с выхода элемента ИЛИ 12 поступает на вход элемента И 9, на другом входе которой также присутствует

логическая 1. Следовательно, на выходе элемента И 9 появится логическая 1 (фиг. 2, sriropaj 17 К Таким Образом, логический блок 3 преобразует противофазную пары импульсов с амплитудами {А/2) и (-А/2) в синфазную пару с амплитудами 1 и 2 фиг. 2, эпюры 16 и 17 в момент ifl + T-t-T . т и распространяется вдоль связанных линий 1 и 2, со скоростью Vjjj,|c тр. и появляется на выходах линий 1 и момент (фиг. 2, эпюры 18 и 19). Импульс с выхода линии 1 задержки поступает на вход аттенюатора 7, после прохождения которого амплитуда импульс оказывается меньше Uf,op и, следовательно, на вход элемента НЕ 8 подается логический О, а на его выходе будет логическая 1. Импульс с выхода линии 2 задержки проходит через неинвертирующий усилитель б с коэффициентом усиления kg /2. На вход И 10 поступает импульс с выхода линии 1 задержки, имеющий амплитуду А, следовательно,- на выходе элемента И 10 появится логическая 1, которая поступает на входы элементов ИЛИ, 11 и 12 (фиг. 2, эпюры 20 и 21 ), поэтому на их выходах также будет логическая 1.

Таким образом, на оба входа элемента И 9 поступает логическая 1

Логический блок 3 синфазную пару импульсов с амплитудой А пропускает без изменения и, следовательно такая пара может циркулировать по .цепи, образованной логическим блоком 3 и связанными линиями 1 и 2 1не6граничённо долго, до тех пор, пок не подан .новып -сметный импульс.

Стабильность амплитуды циркулирующих импульсов обеспечивается логическими элементами 9 и 11, на выходах которых при превышении входного порогового уровня формируется сигнал постоянной амплитуды.

Логические элементы 9 и 11 выполняются со стробированием от блока 4 синхронизации (по аналогии с прототипсял цепи стробирования не показаны). После стробирования импульсы поступают соответственно на входы связанных линий 1 и 2 одновременно и равными по амплитуде и длительности (при условии идентичности параметров логических элементов). За счет ограничения полосы пропускания связанных линий 1 и 2 в области высоких частот происходит растягивание проходящих через них импульС9В, вследствие чего исключается возможность несовпадения импульсов стробирования с импульсами, циркулирующими по петле запаздывающей обратной связи.

Условия устойчивой циркуляции в счетчике идеально синфазных импульсов совпадают с условиями устойчивой циркуляции импульсов в обычном рециркуляторе с синхронизацией.

Если в некоторый момент времени i. (фиг. 2 , эпюра 15 с блока 4 синхронизации поступает новый счетный импульс, то он, как и первый импульс, в процессе первой циркуляции распадется на две пары импульсов. Синфазная пара, появляющаяся на выходах линий 1 и 2 задержки в момент tp + (n-t-1) Т (.фиг. 2, эпюры 18 и 19), не проходит через логический блок 3, и в этот момент может быть подан следующий счетный импульс. Противофазная пара-,оставшаяся от одиночного импульса, появится на выходах связанных линий 1 и 2 задержки в момент ( + )Т--Т т.е. одновременно с появлением однофазной пары импульсов с амплитудой А, циркулирующих в счетчике после подачи импульса младшего разряда. Таким образом, в момент , ig + (ii4-l)T+ Tf, на входе логического блока 3 (фиг. 2, эпюры 18 и 19) поступает сигнал, представляющий собой суперпозицию двух пар импульсов: синфазной с амплитудами А и противофазной с амплитудами (А/2) и (-А/2). При этом на вход усилителя 6 поступает импульс с амплитудой А . На выходе усилителя б будет импульс амплитуды Д бол

.шей и

На вход аттенюатора 7

пор

и элемента И 10 поступает импульс амплитуды А+А/2 1,5А. Таким образом на входах элемента И 10 будут логические 1, следовательно, на ее выходе (фиг. 2, эпюра 21) и на выхо дах элементов ИЛИ 11 и 12 появится логическая 1 (фиг. 2, эпюры 16 и 23 ), которая проходит на вход линии 1 задержки и на вход элемента И 9. Коэффициент ослабления аттенюатора 7 выбирается таким, чтобы импульс с амплитудой 1,5А, пройдя аттенюатор 7, имел амплитуду, большую и пор- Тогда на выходе элемента НЕ 8 появится логический О, который подается на вход элемента И 9 (фиг. 2, эпюры 19), на выходе которой будет та;кже логический О (фиг. 2, эпюра 17). Таким образом, при приступлении на вход логическог блока 3 одновременно двух пар импульсов на вход связанных линий 1 и 2 задержки (фиг. 2, эпюры 16 и 17 ) поступает одиночный импульс, который далее преобразуется подобно первому счетному импульсу. В результате-в счетчике останется Циркулировать одна пара импульсов с амплитудой А и вpeмeнны 4 положением iff КТ-«-2Т , что соответствует

числу число поступивших с момента ip счетных импульсов) в последовательном двоичном коде, у которого млад1иий разряд занимает временное положение следующий t + КТ +2Т, и т.д. Таким образом, данная схема накапливамщего двоичного счетчика осуществляет перенос логической 1 в следующий разряд. Если этот разряд свободен, то процесс переноса заканчивается, если же в .этом разряде уже находится логическая 1, то она стирается и за следующий период циркуляции переносится в более старший разряд. Этот процесс повторяется до тех пор пока логическая 1 не займет свободный разряд.

На стабильность работы счетчика существенно влияет разброс параметров элементов логического блока 3 (уровней логической 1, логического О и времен задержки .включени логических схем ), который приводит к неидентичности импульсов синфазной пары на входах связанных линий 1- и 2.

Для того, чтобы определить допустимую в.еличйну разброса, рассмотрим прохождение двух последовательных пар синфазных импульсов через связанные линии задержки. s.

Если на входы линий 1 и 2 в момент, t. и t поступают две пары неидеально синфазных импульсов (фиг. 3, эпюры 24 и 25), то через время Т на выходах линий 2 и 1 появятся две синфазные пары импульсов равной амплитуды t +Л )/2 и со сдвигом на Т относительно них две противофазные пары с амплктуяами (фкг. 3 эпюры 26 и 27). Появление противофазной пары на выходах линий обуслолено только не.идентичностью импульсов на входах линий 1 и 2, т.е. в конечном счете, разбросом параметров элементов логического блока.3. В момент времени t произойдет наложение синфазной и противофазной пар, в результате чего форма и амплитуда импульсов второй синфазной пары снова станут неодинаковыми (фиг. 3, зпюры 26 и 27).

Кроме разброса параметров элементов логического блока различие в амплитудах синфазной пары на выходах линий 1 и 2 могут быть вызваны неравенством волновых сопротивлений связанных линий. Частично они могут быть скомпенсированы подбором коэффициентов усиления усилителей 5 и б и коэффициента затухания аттенюатора 7. Кроме того, отклонения волновых .сопротивлений от номинального значения обычно невелики, поэтому влияние сопротивлений связанных линий на стабильность

работы схемы можно не учитывать. Ол нако кроме разброса волновых сопро. тивлений погрешность в изготовлении связанных линий вызывает отклонение времен задержки импульсов от тре-5 буемой величины Т. . Если это:,

отклонение не превышает Т (0,24 Of5lt. , где tuc - длительность импульсов синхронизации (строб-импульсов ), счетчик продолжает устой0 чиво работать. Если счетчик обла дает емкостью восемь бит, для него; в петле циркуляции должно :умещаться девять импульсов, относительная погрешность времени задержки лТ:, /Т. ,

5 не должна превышать {0,2-0,, 5-2,5% .(считаем, что )«

Допустимые величины относительных -погрешностей параметров элементов логического блока 3 (cf - коэф/1 фициента затухания аттенюатора 7,

сС - пороговых напряжений логичес- . .ких элементов, ц коэффициента . усиления инвертирующего усилителя 5) и амплитуд импульсов на его вхо5 Де iffy определяются из следующих требований: - максгш льная амплитуда () импульсов (фиг. 3, эпюра 26, момент времени t,) после прохождения аттенюатора 7 с максимально допустимым коэффициентом

затухания K-j {-1+сГц) не должна древышать значения порогового напряжения ( 0 .элемента НЕ 8

5 А(,)К,()и„ор{ - и) .

минимальная амплитуда 1,5А (1-cfд cynwapHoro импульса на выходе линии 1 после прохождения аттенюатора 7 с

Q минимально допустимым коэффициенте затухания Ik (I-cfj ) должна оставаться больше ьтаксимального значения порогового напряжейия ПОР ( элемента НЕ 8 минимальная амплитуда А () импульса (фиг. 3, эпю5 ра 27, момент времени -tg) должна превышать максимальное значение порогового напряжения Upop () элемента И 10

0 (-)VP(U)

амплитуда А сГ паразитного отрицательного выброса на выходе связанных линий (фиг. 3, эпюра 27), момент времени t после прохождения ин5 вертирующего усилителя 5 с макси- . мально допустимым коэффициентом уси- лeнкяKg( tff не должна превышать минимального значения порогового напряжения и« {l-cT,.) элемен0 та Ш1Н 11 . «

)Следовательно, самым жестким тре|бовавием является второе условие.

Для-его(выполнения I при равенстве от носительных погрешностей - Г fи номинальных значений Unop 0,75 А; Ку 2; -, 0,6 необходимо, чтобы разброс перечисленных параметров логического блока 3 не превышал б%. Это необходимо учитывать при выборе элементной базы для изготовления счетчика.

. Таким образом, частота следовани импульсов в пачке, т.е. минимальное расстояние Тр между импульсами соседних разрядов определяется собственным быстродействием логических . У прототипа же эта величина ограничивается суммарным запаздыванием импульса в цепи переноса, включающей в себя не менее трех последовательно соединенных логических схем. Поэтому частота следований импульсов в схеме прототипа существенно ниже предельного быстродейстВИЯ используемых логических схем. Поскольку в предлагаемом счетчике минимальный период подачи счетных импульсов T(l-«-N)Tf, , где N количество разрядов числа, то уменьшение величины Т, позволяет уменьшить период Т при сохранении количества разрядов N . Таким образом, предлагаемая схема счетчика позволяет обойтись без цепи переноса и

вследствии этого повысить быстродействие.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ИЗМЕРЕНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ В УСЛОВИЯХ ПОМЕХ | 1991 |

|

RU2030757C1 |

| ИЗМЕРИТЕЛЬНЫЙ ПРИБОР | 1992 |

|

RU2067290C1 |

| РАДИОЛОКАЦИОННЫЙ УРОВНЕМЕР | 1997 |

|

RU2124703C1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2003 |

|

RU2244375C1 |

| Устройство для измерения амплитуды одиночных импульсов | 1978 |

|

SU789804A1 |

| Устройство измерения временных интервалов в условиях помех | 1981 |

|

SU1008682A2 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2008 |

|

RU2376703C1 |

| Устройство для автоматического измерения амплитуды переменного сигнала | 1987 |

|

SU1513406A2 |

| УСТРОЙСТВО ДЛЯ ВОССТАНОВЛЕНИЯ ВРЕМЕННЫХ ПАРАМЕТРОВ ФЛУКТУИРУЮЩИХ ИМПУЛЬСНЫХ СИГНАЛОВ | 1993 |

|

RU2060509C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДИАГРАММ НАПРАВЛЕННОСТИ АНТЕННЫ В ДАЛЬНЕЙ ЗОНЕ | 1992 |

|

RU2082985C1 |

НАКАПЛИВАЮЩИЙ ДВОИЧНЫЙ СЧЕТЧ1Ж, содержащий входную шину, блок синхронизации, первый пороговый элемент ИЛИ, два пороговых элемента И , элемент НЕ и первую линию за:держки, вход которой соединен с выходом первого порогового элемента ;ИЛЙ первый вход которого соединён с выходом первого порогового эле- ; мента И,- выход элемента НЕ соединен .с первым вхрАсмл второго порогового , элемента И входная шина соединена с зходом блока синхронизации, о тл и ч а ю и и и с я тем, что, с целью повышения быстродействия, в него введе.ны вторая линия задержки, связанная с первой линией задержки неуравновешенной электромаг-. : ниткой связью, второй пороговый элемент ИЛИ, два усилителя и .аттенюатор, вход которого соединен с первым входом первого порогового элемента И и с выходом первой линий задержки, выход второй линии задержки соединен с инверсным входом первого усилителя и с входом второго усилителя, выход которого соединен с вторым входом первого порогового элемента И, выход которого .соединен с первым входом второго порогового элемента ИЛИ, выход которого соединен с BTopt i входе второго порогового элемента И, выход которого соединен с вхрдом второй линии задержки, выход первого усилителя соединен с вторыми входами первого и второго пороговых элементов ИЛИ, выходы блока синхронизации и аттенюатора соединены соответственно с третьим входом первого порогового элемента ИЛИ и с входом элемента lil НЕ. СП 4 О СО

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 3521036, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| НАКАПЛИВАЮЩИЙ ДВОИЧНЫЙ СЧЕТЧИК | 0 |

|

SU395989A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-09-30—Публикация

1982-06-09—Подача