, первой группы -го депифратора, входы второй группы которого, соединены с выходами соответствующих ч -х элементов И В групп, выходы (P-I) -X эле ментов Н П групп, гдер ,2, .. .,|nj-l подключены к соответствуюпщм входам .третьей группы р -х блоков сравнения 2. Устройство по П.1, от л и чающееся тем, что блок управ ления содержит триггер, генератор тактовых импульсов, элемент ИЛИ, эле мент задержки и распределитель сигналов , причем первьш вход блока уп-равления соединен с единичным входом триггера, прямой выход которого подключен к управляющему входу генератора тактовых импульсов, выход которого соединен с входом элемента задержки, первым входом элемента ИЛИ и вторым выходом блока управления, второй вход элемента ИЛИ под- , ключен к второму входу блока управле ния, а выход - к первому выходу блока управления, выход Элемента задерж ки соединен с первым входом распреде лителя сигналов, второй вход которого соединен с Л -м выходом распределителя сигналов и входом установки в ноль триггера, выходы распределителя сигналов соединены с соответствукяцими распределительными выходам блока управления. 3, Устройство по П.1, отличающееся тем, что блок выявления равных чисел содержит кодоЬрербразователь , реверсивный счетчик и Элемент задержки, причем тактовьш вход блока выявления равных чисел подключен к тактовому входу ре версивного счетчика, информационные входы которого соединены с соответствующими выходами кодопреобразователя, входы которого соединены с информационными входами блока выявления равных чисел, выход 00 ; реверсивного счетчика соединен с первьм выходом блока выявления равных чисел и через элемент задержкис BTopbJM выходом блока выявления рапных чисел. 4. Устройство по п.1, о т л и чающееся тем, что формирователь сброса содержит формирователь сигнала, Пm -входных элементов ИЛИ и И элементов И, причем информационные входы формирователя сброса соединены с соответствующими входами элементов ИЛИ, выходы которых соединены с первыми входами соот|ве ствующих элементов И, вторые входы которых через формирователь сигналов соединены с управляющим входом формирователя сброса, а выходы - с соответствующими выходами формирователя сброса. 5. Устройство по п.1, отличающееся тем, что коммутатор содержит И групп входных элементов И, п элементов ИЛИ и п групп выходных элементов И, причем R -и вход nepBofi группы входов, где R 1, 2,..., tl , соединен с первыми входами выходных элементов И соответствующей группы, вторые входы R -х выходных элементов И всех групп соединены с вь1ходами R -х элементов ИЛИ, входы которых соединены с выходами -х входных элементов И всех групп И соответствующими выходами первой группы коммутатора, первый вход i -го входного элемента И R-й группы соединен с соответствующим входом второй группы входов коммутатора, R -II вход третьей группы входов коммутатора соединен с вторыми входами элементов.И соответствующей группы, выходы выходных элементов И соединены с выходами второй группы коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки двоичных чисел | 1990 |

|

SU1783511A1 |

| Устройство для сортировки массивов чисел | 1988 |

|

SU1624440A1 |

| Устройство для сортировки чисел | 1989 |

|

SU1793438A1 |

| Устройство для сортировки чисел | 1990 |

|

SU1793437A1 |

| Многоканальное устройство для ввода информации | 1984 |

|

SU1265783A1 |

| Устройство для распределения информации | 1982 |

|

SU1076900A1 |

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для выбора упорядоченной последовательности данных | 1984 |

|

SU1218381A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

1. УСТРОЙСТВОдля СОРТИРОВКИ ДВОИЧНМХ ЧИСЕЛ, содержащее П входных , т-разрядных регистров, где П-число сортируемых чисел, m -число разрядов сортируемых чисел, И групп элементов И по m элементов И в группе, дешифраторы и блоки сравнения, причем вход- . ные информационные шины устройства г соединены с информационными входами соответствуювдх входных регистров, прямой выход -го разряда каждого входного регистра, где i 1,2,..., tl , подключен к первому входу i-го элемента И соответствуюп1ей группы, выходы -го блока сравнения, где j 1,2,.. .lni-2j , соединены с соответст- вующими входами первой группы (J +1)-го блока сравнения, входы первой группы первого блока сравнения соединены с соответствующими выходами первого дешифратора, выходы k -го дешифратора, где k 2,3,..., И1, подключены к соответствующим входам второй группы .Ij-ro блока сравнения, о т л и - , Чающееся тем, что, с целью расширения функциональных возможностей устройства путем сортировки чисел по возрастанию их величины, в него введены П выходных tH -разрядных регистров, выходы которых соединены с соответствующими выходными шинами устройства, К групп элементов И, где 2 (п+1) , (п+2) , ...,2П, блок управления, блок выявления равных чисел, .формирователь сброса и коммутатор, причем первый вход блока управления : подключен к шине начала работы устг ройства,а разрешающий выход соединен с вторыми входами элементов И всех групп,инверсный выход 4 -го разряда каждого входного регистра подключен к первому входу -го элемента И соответствующей Р. группы, второй вход блока упс равления соединен с первым выходом блока выявления равных чисел,а такТовый вы(Л ход - с тактовым входом блока выявления равных чисел,второй выход которого подключен к управляющему входу формирователя сброса, выходы которого соединены с установочными входами соответствующих входных регистров, распределительные выходы блока управления сое-, динены с входами первой группы комсо со мутатора, выходы первой группы кото-рого подключены к соответствующим входам выходных регистров, выходы второй группы коммутатора соединены с соответствующими информационными входами формирователя сброса, входы второй группы коммутатора соединены с соответствующими выходамиэлементов И П групп, входы третьей группьт коммутатора подключены к соответствующим выходам (ni-l) -fo блока сравнения и к соответствующим информационным входам выявления равных чисел, выходы ч -х элекентов И и групп подключены к соответствующ1ш входам

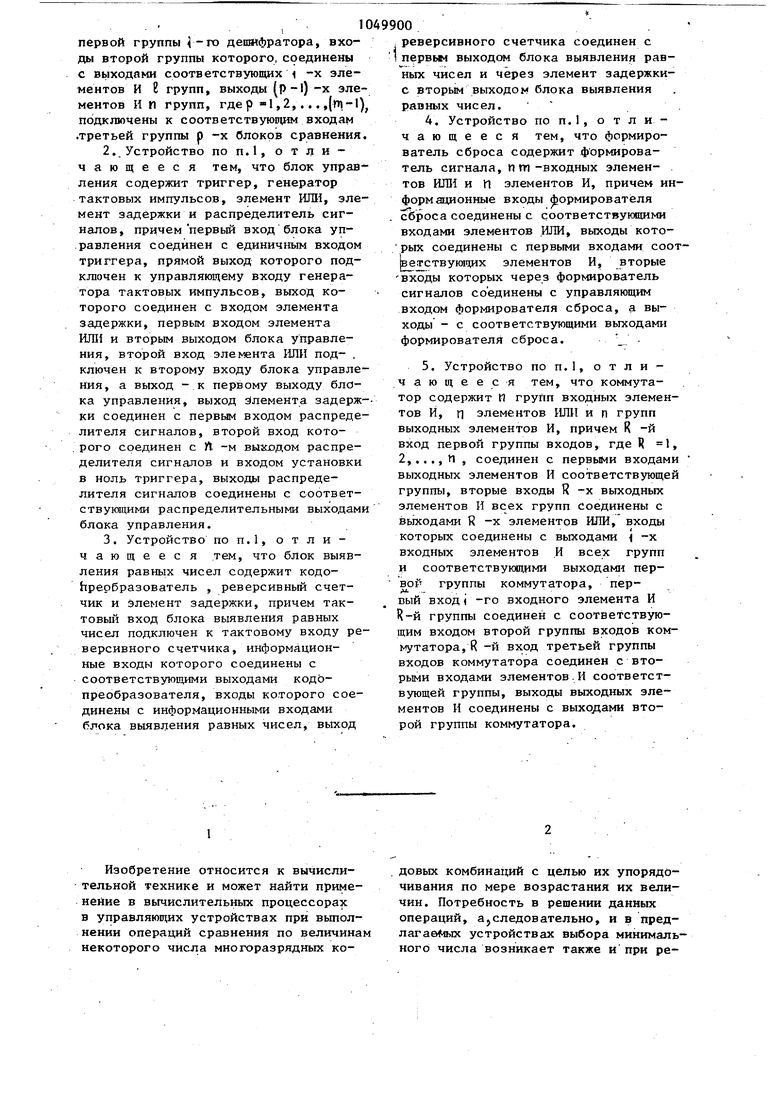

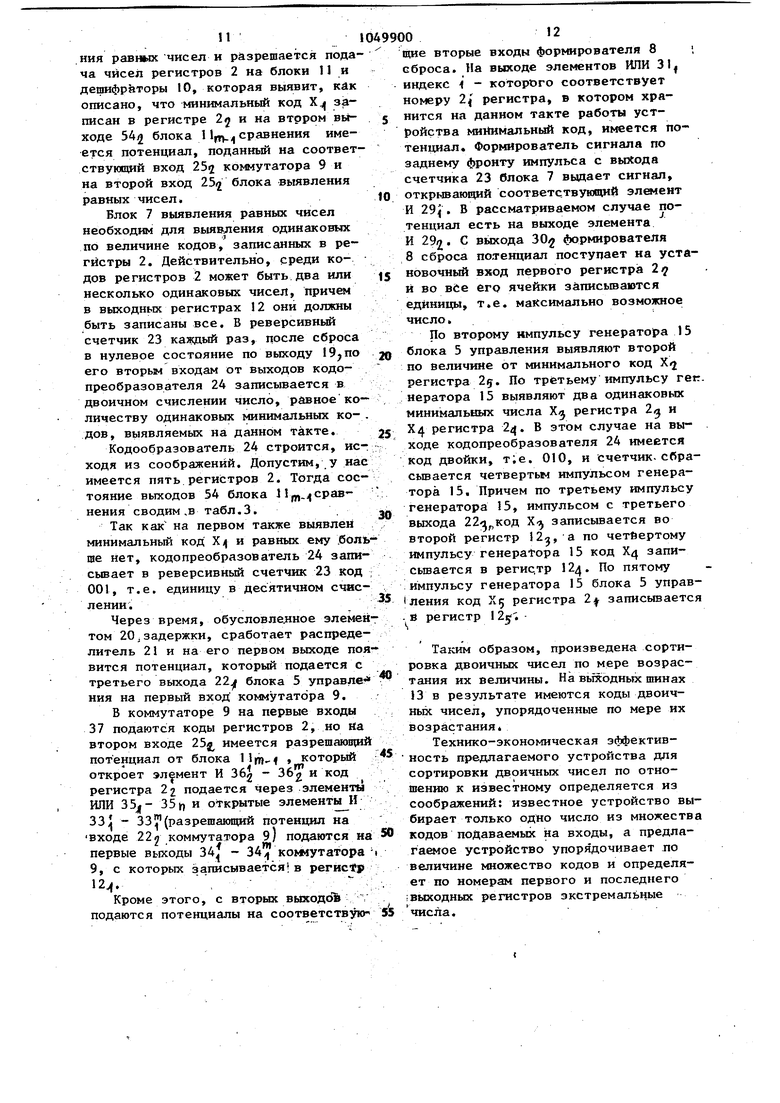

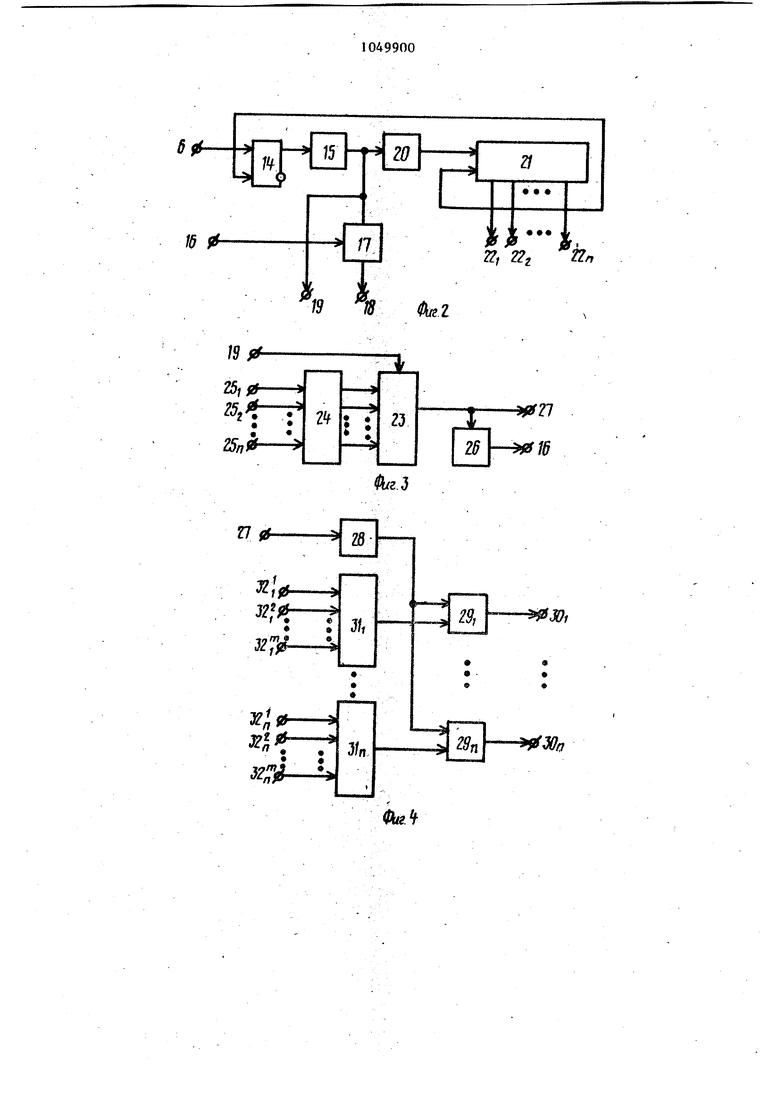

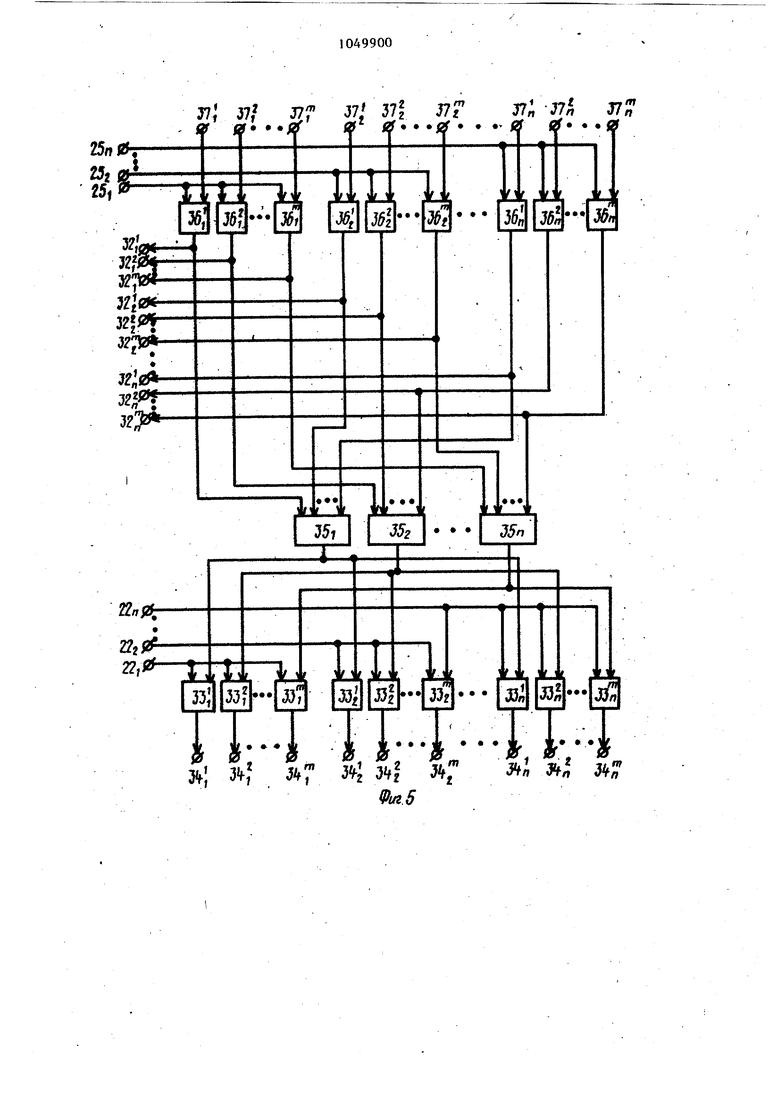

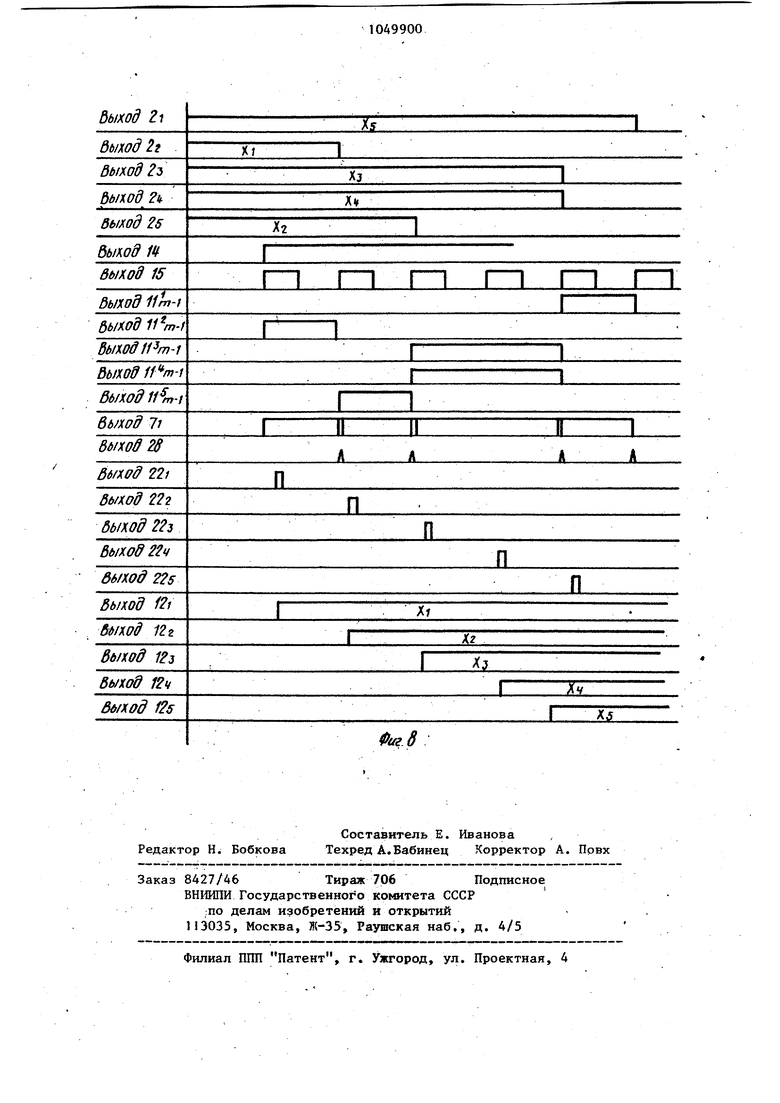

Изобретение относится к вычислительной технике и может найти применение в вычислительных процессорах в управляющих устройствах при вьшолнении операций сравнения по величинам некоторого числа многоразрядных кодовых комбинаций с целью их упорядочивания по мере возрастания их величин. Потребность в решении данных операций, аjследовательно, и в предлагав « 1х устройствах выбора минимального числа возникает также ипри решении экстремальных задач управления объектами с многими параметрами. Известно устройство для сравнения двоичных чисел, содержащее регистры первые, втюрые и третьи элементы И, триггеры, блоки сравнения, элементы ИЛИ и НЕ l . . Недостаток известного устройства состоит в том, что процесс сравнения двух чисел определяется подачей управляющих сигналов по второй,третье и четвертой входньм управляющим иинам, т.е. затрачивается дополнительк но время на процесс анализа и про- с иесс управления. Кроме того, информация в регистры вводится последовательно, а само устройство не решает задачи сортировки двоичных чисел с целью их упорядочивания по абсолютной величине, что снижает функциональные возможности известного устройства. Известно устройство для вьщеления многоразрядного кодй, содержащее VI (2т-l) узел анализа, (1 мажоритарных элементов, причем информационный вход каждого(i-j) -го узла анализа соединен с j -ым входом -ой группы входов устройства, где 1,2 №, J l,2,...,2ni-l), выход -го мажоритарного элемента подключен к .первому входу управления (i- 1) , (v 2 (2t4-1)1-го уэлов анализа, первый второй. Третий, четвертый и пятый выходы каждого 1j)-ro узла анализа соединены с вторым, третьим, четвертым, пятым и шестым входами управления (+)) -го узла анализа соответственно, выход результата { ix узла анализа подключен к -му входу 6-го мажоритарного элемента . Недостаток этого устройства состо ит в том, что оно выбирает.некое среднее и не выполняет функцийсортировки чисел, т.е. их упорядочивания, что-снижает функциональные воз мощности устройства. I . Наиболее близким к предлагаемому по совокупности конетруктившлх и функциональных признаков является устройство для определения экстрем ibHoro числа, содержащее регистры, элементы И, блоки сравнения, дешифраторы состояний, число которых равно числу регистров, причем входные шины соединены с входами регистров соответственно, выходы регистров сое динёны соответственно с входами деппя;) .раторов состояний,первыми входами блр ков сравнения и первыми входами элементов И, выходы которых соединены с выходными шинами устройства, а вторые входы - с выходами последнего блока сравнения, причем выходы каждого блока сравнения, кроме последнего соединены с вторым входами последующего блока сравнения, а вторые входы первого блока сравнения соединены с выходами первого дешифратора сос тояний третьи входы блоков сравне1тя соединены с выходами соответствующих дешифраторов состояний З . Однако устройство осуществляет выбор либо минимального, либо максимального числа, в зависимости от того прямые или инверсные коды ноданы в регистры, и не выполняет функций сортировки чисел, т.е. их упорядочивания по мере роста величины и выделения обоих экстремальных чисел, что приводит к ограниченным фуикциональньм возможностям. Цель изобретения - расширение функциональных возможностей устройства путем сортировки чисел по возрастанию их величины. Указанная цель достигается тем, что в устройство для сортировки двоичных чисел, содержащее П входных -разрядных регистров, где п -число сортируемых чисел, in -число разрядов сортируеь ых чисел, п групп элементов И пот элементов И в группе, дешифраторы и блоки сравнения, причем входные информационные шины устройства соединены с информационными входами соответствующих входных регистров, прямой выход i -го разряда каждо о входного регистра,.где 1 1,2,,. И, подключен к первому входу -го элемента Н соответствующей группы, выходы J -го блока сравнения, где j 1,2,,.. ,(m-2), соединены с соответствующими входами первой группы(j-i-1)-го блока сравнения, выходы первой группы первого блока сравнения соединены с соответствующими выходами первого дешифратора, выходы k -го дешифратора где k 2,3,...,m, подключены к соответствующим входам второй группы k-l)-ro блока сравнения, введены tl выходных W -разрядных регистров. выходцл которых соединены с соответствукщими выходиыми шинами устройства, ь групп элементов И, где () , (|Ц-2),..., 2h, блок управления, блок выяйлення равных чисел, формировател сброса и коммутатор, причем первый вход блока управления подключен к ш не начала работы устройства, а разрешающий выход соединен с вторыми входами элементов И всех групп, ин. версный выход f-ro разряда каждого входного регистра подключен к перво му входу 1 -го элемента И соответствующей ь группы, второй вход блока управления соединен с первым выходо блока выявления равных чисел, атактовый выход - с тактовым входом блока выя .ления равных чисел,второй выход которого подключен к управляющему ..-входу формирователя сброса, выходы которого соединены с установочньрш входами соответствующих входных регистров, распределительные выходы блока управления соединены с входами первой группы коммутатора, выходы первой группы которого подключены к соответствующим входам выходных регистров, выходы второй группы коммутатора соединены с соответстёзтощими информационными входами формирователя сброса, входы второй группы коммутатора соединены с соответствурщими выходами элементов И п групп, входы третьей группы коммутатора подключены к соответствующим выходам ( т-1) -го блока сравнения и к соответствующим информационным входам блок.а выявления равных ,чисел выходы { -X элементов И П групп под ключены к соответствующим входам первой группы -1 -го дешифратора, входы второй группы которого соединены с выходами соответствукнцих -( -х элементов И Е групп, выходы f элементов И 11 групп, где р 1,2,... (fn-l) , подключены к соответствующим входам третьей группы р -х блоков сравнения. При этом блок управления содержит триггер, генератор тактовых импульсов, элемент ИЛИ, элемент задержки и распределитель сигналов, причем первый вход блока управления соедине с единичным входом триггера, прямой выход которого подключен к управляющему входу генератора тактовых импульсов, выход которого соединен с входом элемента задержки, первым входом элемента ШВД и вторым выходом , блока управления, второй вход элемента ИЛИ подключен к второму входу блока управления, а выход - к пер вому выходу блока управления, выход элемента Задержки соединен с первым входом распределителя сигналов, второй вход которого соединен с п выходом распределителя сигналов и входом установки в ноль триггера, ды распределителя сигналов соединены с соответствующими распределительными выходами блока управления. Причем блок выявления равных чисел содержит кодопреобразователь, реверсивный счетчик и элемент задержки, причем тактовый вход блока выявления равных чисел подключен к тактовому входу реверсивного счетчика, информационные входы которого соединены с соответствующими выходами кодопрё образов&теля, входы которого соединены с информационньй и входами блока выявления равных чисел, выход реверсивного счетчика соединен с первым выходом блока выявления равных чисел и через элемент задержки - с вторьм выходом блока выявления равных чисел. Формирователь сброса содержит формирователь сигнала, п iTf-входовых элементов ИЛИ и п элементов И, причем информационные входы формирователя сброса соединены с соответствующими вкодами элементов ИЛИ, выходы которых соединены с первыми входами соответствующих элементов И, вторые входы которых через формирователь сигналов соединены с управляющим входом формирователя сброса, а выходы - с соответствующими выходами формирователя сброса. Кроме того, коммутатор содержит М групп входиьпс элементов И,Г1 элементов ИЛИ и П групп,выходных элементов И, причем R -и вход первой группы входов, где R 1,2,...,П , соединен с первыми входами выходных элементов И соответствую1цей Группы, вторые входы R -х выходных элементов И всех групп соединеиы с выходами R -х элементов ИЛИ, входы которых соединены с выходами -х входных элементов И всех групп и соответствующими выходами первой группы коммутатора, первый вход i -го входного элемента И К-и группы соединен с соответствукмцим входом второй группы входов коммутатора, R -и вход третьей группы входов коммутатора соединен с вторыми входами входных элементов И соответствующей группьг, выходы выходнйх элементов И соединеиы с выходами второй группы коммутатора. На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг.2функцибнальная схема блока управления; на фиг. 3 - функциональная схема блока выявления равных чисел; на фи1. 4 - функциональная схема формирователя сброса; на фиг. 5 - функцио -яапьная схема коммутатора; на фиг.6функциональная схема дешифраторов; . 7 - функциональная cxe. ма каждого из блоков сравне ,ния; на фиг. 8 - временные диаграммы, отображающие работу устройства для сортировки двоичных чисел во времени (под выходом N} понимается сигнал на 1-ом ВЕЛСоде И-ой позиции) Блок-схема предлагаемого устройства для сортировки Двоичных чисел содержит информационные входные ши1 f 1 1 ны -I где m -число разрядов двоичных чисел,П -число двоичиых чи- сел, входные регистры , элементы И 3,-31 , 4j -А| , блок 5 управления, ршну 6 начала работы устройства, блок 7 выявления равных чисел формирователь 8 сброса.регистров 2, коммутатор 9, дешифраторы состояний одиоименных разрядов регис ров 2, блоки 11,)- 11 сравнения, сра нивающие коды по разрядам, причем блок сравнения вьщает сигнал, определяющий, в каком из регистров 2 хранится минимальный код, выходные 12, выходные гшкны регистры 12,,-1 13, - 13„ устройства. Функциональная схема блока 5 управления содержит триггер 14, генератор 15 тактовых импульсов, синхронизирующий работу устройства, второй вход 16, элемент ИЛИ 17, первый и второй выходы 18 и 19, элемент 20 задержки, распределитель 21 сигналов реализованный как обычные распределители телемеханических устройств, сигналы на выходах которого появляюТ ся однозначно и последовательно во времени, аспределительные .выходы22 - 22, блока управления. Функциональная схема блока 7 выяв . ления равных чисел, содержит реверсивный счетчик 23, кодопрёобразователь 24, предназначенный длявыявлё ния одинаковых чисел и записи их количества в двоичном исчислении в счетчик 23, информационнее входы ДЗ, 25п,элемент 26 задержки (времени . Функциональная схема формирователя 8 сброса содержит управляклщй код 27 формирователь 28 сигнала,представляю0 - . 8 н(ий ЪЪбой дифференцирующую цепь для формирования заднего фронта сигнала. элементы И 2) 29п, выходы 30„ ЗЦ , входы второй lum 31,элементы32j- 32j. группы Функциональная схема коьмутаторя 9 содержит вмходные элементы И , выходы 34J- 34, элементы ИШ1 35j - 35fl, входные - элементы И 36 nftft от -nf 36, входы 37|- 3/f,. , Функциональная схема дешифраторов 10ж- lOfn содержит входы первой и второй группы 38 J- 38, 39/- , первые и вторые элементы И соответственно . 40,, 41|- 41(4, элементы ИЛИ 42 , выходы 43|- 43 дешифраторов соответственно. Функциональная схема каждого из , блоков 11 сравнения содержит первые ивторые элементы И соответственно , 45,- 45, входы второй группы 46,- 46, первые элементы НЕ 47( - 47f,, третьи элементы И , вторые элементы НЕ 49,-49п, четвертые элементы И 50, третьи элементы НЕ 51,- 51ц, пятые элементы И 52 ;|- 52fj ,первые элементы ИЛИ , выходы 54,- 54п, вторые элемен- i ты ши 55„. Устройство для сортировки двоичных чисел работает следующим образом. По входным шинам ij- 1ц в первые регистры. 2 заносятся двоичные числа в параллельнь1Х кодах, причем расположение чисел по регистрам 2 производится случайным образом. Задача состоит в том, что данные числа из первых регистров 2 переносят во вторые регистры 12 в порядке возрастания их величины, т.е. если допустим, в регистре 2, есть число 8, в ре истре 2j- 3, в регистре , в регистре 5, в регистре воичной системе счисления то в реистрах 12 после сортировки числа записьшают в. следующем порядке: в ре-истре в регистре 125-3, в регистре , в регистре , в регистре 125-1Q. После того, как числа, подлежащие сортировке, записаны в регистры 2, по второй входной шине 6 подается сигнал управления пуском устройства. анный сигнал поступает на первый ход блока 5 упргшления и перебрасывает триггер 14 в единичное состояние.отенциал с единичного выхода триггеа 14 запускает генератор тактовых мпульсов (фиг.2 и фиг.8). Импульсы с выхода генератора 15 подаются на второй вход элемента ИЛИ 17 и от вт рого выхода 19 блока 5 управления н первый вход блока выявления равных чисел. Кроме того, импульсами с выходами генератора 15 через элемент 20 задержки времени управляется дви жение распределителем 21 сигналов. Элемент 20 задержки времени необх.одим( для задержки времени появления сигналов на выходах распределителя 21 на время, большее времени переходных процессов в дешифраторах 10 и блоках 11 сравнения. Импульс с выхода генератора 15 через элем(5нт ИЛИ 17 с первого вьтхо да 18 блока 5управления подается н вторые входы первых 3 и вторых 4 эл ментов И, разрешая подачу содержимо первых регистров 2 на соответствующие входы дешифраторов 10, блоков J сравнения и коммутатора 9. По данно первому импульсу генератора 15 депш -ратрры 10 и блоки 11 сравнения пыяв ляют ifepBoe минимальное число, хранящееся в одном из регистров 2. Происходит это следующим образом Алгоритм выбора минимального кода состоит в последовательном анализе параллельных разрядов Л кодовых ко бинаций, записанных в регистрах 2, с -последовательным выявлением больших по величинам кодов в параллельных ((одноименных разрядах, начиная со старшего разряда вплоть до младшего. Причем анализ параллельных ра рядов кодовых комбинаций производит ся как дешифраторами 10, так и блоками 11 сравнения, но выявление кодовыхг комбинаций, меньших по величи не, чем наибольшие, производится пе вым дещифратором блоками 1Цm-it Рзвнения, причем последний блок сравнения выявляет минимальные (одну или несколько) кодовы комбинации, П р и. м е р. Пусть в регистрах 2 записаны кодовые комбинации: Причем минимальные по величине кодовые комбинации хранятся в регистрах. Сущность алгоритма работы устройства выбора минимального кода состоит в следующем. Возможны следующие события. Символы всех старших разрядовмогут быть равны единице, либо нулю, либо имеются символы, равные нулю и eдиницёJ В первых двух случаях на выходах дешифратора Ю(фиг.б) должны быть единичные потенциалы, а в третьем случае единичные потенциалы должны быть на тех выходах 43|43 , которые соответствуют по верхнему индексу регистрам 2, в старшие разряды KOTopbix записаны нулевые оим-;волы кодов. Для рассматриваемого случая единичный потенциал есть на выходах 43J, 43, 43|, 435, 43 Действительно, потенциалы на выходах злементов И 40 и 41 равны нулю и на выходах элементов ИЛИ 42 есть потенциалы, определяемые потенциалами, снимаемыми с прямых входов 38,- 38 дешифратора 104. Значения функций, снимаемых с выходов 43 дешифраторов 10, запишем в табл.1. Таким образом первый дешифратор 10|состояний выделяет номера регистров 2, в которых хранятся меньшие кодовые комбинации. Однако из табл.I следует, что дешифратор 1 Oj подобную функцию уже не выполняет. В этом случае блоки сравнения 1 Ц-11 л выделяют регистры с минимальными кодовыми комбинациями. Работу блоков 11 сравнения проследим для примера восьми регистров CDITласно логическим функциям, значения которьк сведены в табл.2, причем значение функции, определякяцсе состояг ние 5 -го блока, находится на пересечении 1 -го столбца и j -ой строки соответствующего раздела табл.2. Из табл.2 видно, что единичные потенциалы имеются на выходах 54л и 54 блока 11 сравнения и тем самым выделяют номера регистров и 27, в которых находятся минимальные кодовые комбинации. Пусть согласно примеру (фиг.8) имеется пять регистров 2, в которых записаны кодовые комбинации: минимальная X;j в регистре 22, следующая по величине Xg в регистре , следующая по величине Х-я в регистре 2 , равная Х кодовая комбинация Х в регистре 2 и Наибольшая по величине Хд - в регистре 2, По первому импульсу генератора 15 сбросится счетчик 23 блока 7 выявления равных чисел и разрешается подача чисел регистров 2 на блоки 11 и дешифраторы 10, которая выявит, KdK описано, что минимальный код Х записан в регистре 2 и на втором выходе 54 блока 1 Ip). сравнения имеется потенциал, поданный на соответствующий вход 252 коммутатора 9 и на второй вход 25 блока выявления равных чисел. Блок 7 выявления равных чисел необходим для выявления одинаковых по величине кодов, записанных в регистры 2. Действительно, среди кодов регистров 2 может быть два или несколько одинаковых чисел, причем в выходных регистрах 12 они должны быть записаны все, В реверсивный счетчик 23 каждый раз, после сброса в нулевое состояние по выходу 19jno его вторым входам от выходов кодопреобразователя 24 записъгоается в двоичном счислении число, рйвноеколичеству одинаковых минимальных ко- дов, выявляемых на данном такте. Кодообразователь 24 строится, исходя из соображений. Допустим, у нас имеется пять регистров 2. Тогда состояние выходов 54 блока lljj,cpaBнения сводим ,в табл.3. Так как на первом также выявлен минимальный код Х| и равных ему .боль ше нет, кодопреобразователь 24 записывает в реверсивный счетчик 23 код 001, т.е, единицу в Десятичном счислении, Через время, обусловленное элемен том 20, задержки, сработает распределитель 21 и на его первом выходе поя вится потенциал, который подается с третьего выхода 22 блока 5 управде ния на первый вход коммутатора 9, В коммутаторе 9 на первые входы 37 подаются коды регистров 2, но на втором входе 25у имеется разрешающий потенциал от блока который откроет элемент И 36 - Зб и код регистра 22 подается Через элементы ИЛИ 35jf- 35 и открытые элементной 33 jj - 331}(разрешающий потенцил на входе 222 коммутатора подаются на первые выходы 34 - 34у| коммутатора 9, с которых записывается; в регистр 12. , - Кроме этого, с вторых выходо подаются потенциалы на соответствующие вторые входы формирователя 8 ; сброса. На выходе элементов ИЛИ 31 индекс i - которого соответствует номеру 2 регистра, в котором хранится на данном такте работы устройства минимальный код, имеется потенциал. Формирователь сигнала по заднему фронту импульса с выхода счетчика 23 блока 7 выдает сигнал, открывающий соответствующий элемент И 29J, В рассматриваемом случае потенциал есть на выходе элемента И 292 выхода 30 формирователя 8 сброса потенциал поступает на установочный вход первого регистра 2 и во вСе его ячейки записьшаются единицы, т.е. максимально возможное число. По второму импульсу генератора 15 блока 5 управления выявляют второй по величине от минимального код Х« регистра 2. По третьему импульсу гаг. нератора 15 выявляют два одинаковых минимальных числа Х регистра 2 и X4 регистра 2|, В этом случае на выходе кодопреобразователя 24 имеется код двойки, т;е, 010, и счетчик-сбрасьшается четвертые импульсом генератора 15, Причем по третьему импульсу генератора 15, импульсом с третьего выхода Х- записьшается во второй регистр 12,а по четвертому импульсу генератора 15 код Х записьшается в регис.тр 12. По пятому импульсу генератора 15 блока 5 управления код Х регистра 2 записывается в регистр , Таким образом, произведена сортировка двоичных чисел по мере возрастания их величины. На вьтходных шинах 13 в результате имеются коды двоичньк чисел, упорядоченные по мере их возрастания. Технико-экономическая эффективность предлагаемого устройства для сортировки двоичных чисел по отношению к известному определяется из соображений: известное устройство выбирает только одно число из множества одов подаваемых на входы, а предлагаемое устройство упорядочивает по еличине множество кодов и определяет по номерам первого и последнего выходных регистров экстремальные числа.

Номера выходов блока 1i

гы

...-..„.

I

о о о 1

о о

,0

о о

1 о

1 1

1 1 1

о

1 1 1

о I 1 I 1

о 1 1

6 1 1

Продолжение табл. 3 Выходы кодопреобразователя 24

IIIZ I 12 13

о i 1 1

о о о о

1

о 1

1

1 о

о о о о о о 1

1 1 1 1 1 1

о о о о о о

nlnl оГ oU 07

tM

1

15

п

16

А

19

W

ч/ if

/Brj&

2, 2,

Фаг г л/ л г jQf в f Z5ff0 3v 7/ 37 i л г -jrA л fif Sf gf 9 gf ft 9 Jv; Л/; л j i, / 1 -Л. 2tl. «.

Авторы

Даты

1983-10-23—Публикация

1982-07-02—Подача