элементов И группь блока управления выход первого элемента задержки бло ка управления соединен с входом установки в единицу четвертого триггера, прямой выход которого соединен с вторым входом первого элемента И, прямые выходы первого второго и третьего триггеров соединены соответственно с вторыми входами третьего, второго и четвертого элементов И инверсный выход второго,триггера соединен с входом третьего элемента задержки, выходы первого и втб-. рого элементов ИЛИ соединены осот-:ветственно с входами, сброса третьего и первого триггеровр вход четвертого элемента задержки соединен с, выходом пятого элемента ИЛИ , первый вход которого соединен с БЫХОДО М третьего элемента И и вторым входом пятого элемента И, второй вход пятого элемента ИЛИ соединен с выходом четвертого элемента И. входом второго элемента задержки и вторыми входами группы элементов И, выход че твертого элемента задержки соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с входом установки в единицу пятого триггера, инверсный выход и вход сброса которого соединены соответственно с первым входом пятого элемента И и выходом третьего элемента ИЛИ

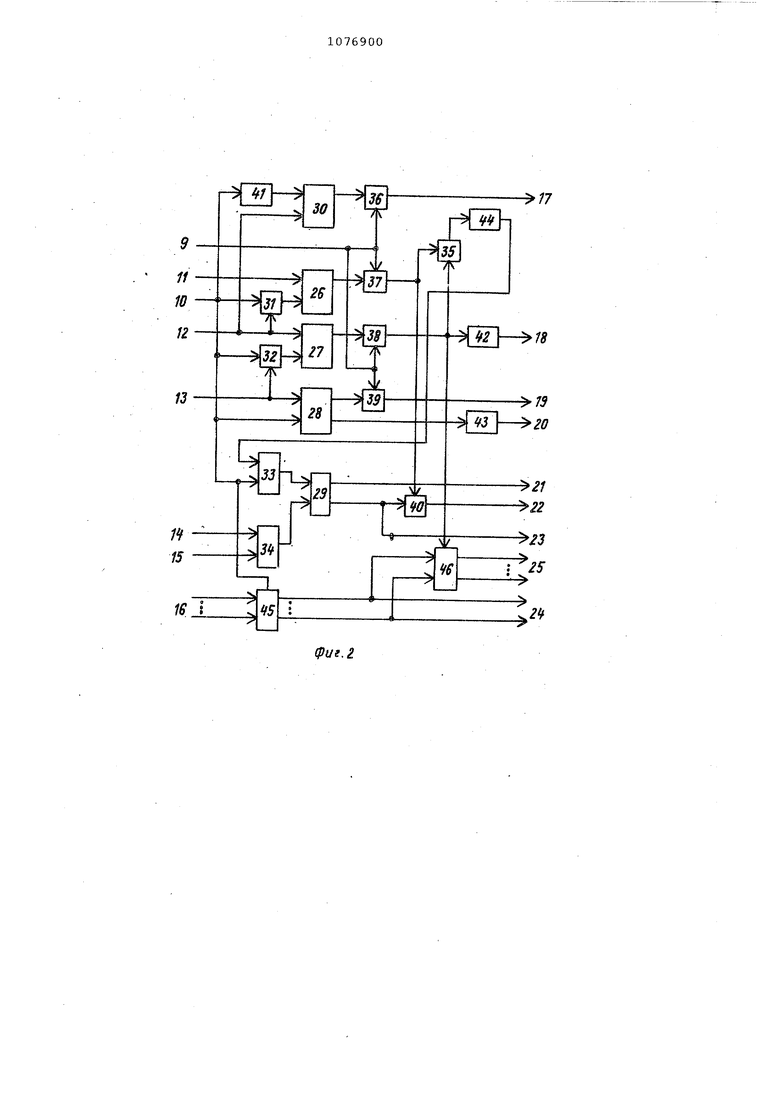

2. Устройство поп„ 1, отличающееся TeMf что-блок анализа результатов содержит двадцать элементов ИЛИ, двадцать пять элементов И и дешифраторf причем первые входы элементов ИЛИ с первого по шестой соединены соответственно с вторым, четвертым, третьим, первым и вторым входами первой группы бло-ка, вторые входы элементов ИЛИ с первого по шестой соединены соответственно с третьим, пятыМу шестыгд;, первым, ПЯТЫМ и шестым входами первой группы блока, первые входы первого и второго, третьего и четвертого, пятого и шестого г седьмого и восьмого / девятого и десятого,, одиннадцатого и двенадцатого элементов И соединены соответственно с первым, вторым, четвертым, шестым., пятым и третьим входами первой группы блока, первый вход тринадцатохо элемента И, второй вход тринадцатого . элеме-нта И, первый вход четырнадцатого элемента И, второй вход четьгрнадцатого элемента И, первый вход пятнадцатого элемента И, второй вход пятнадцатого элемента И соединены

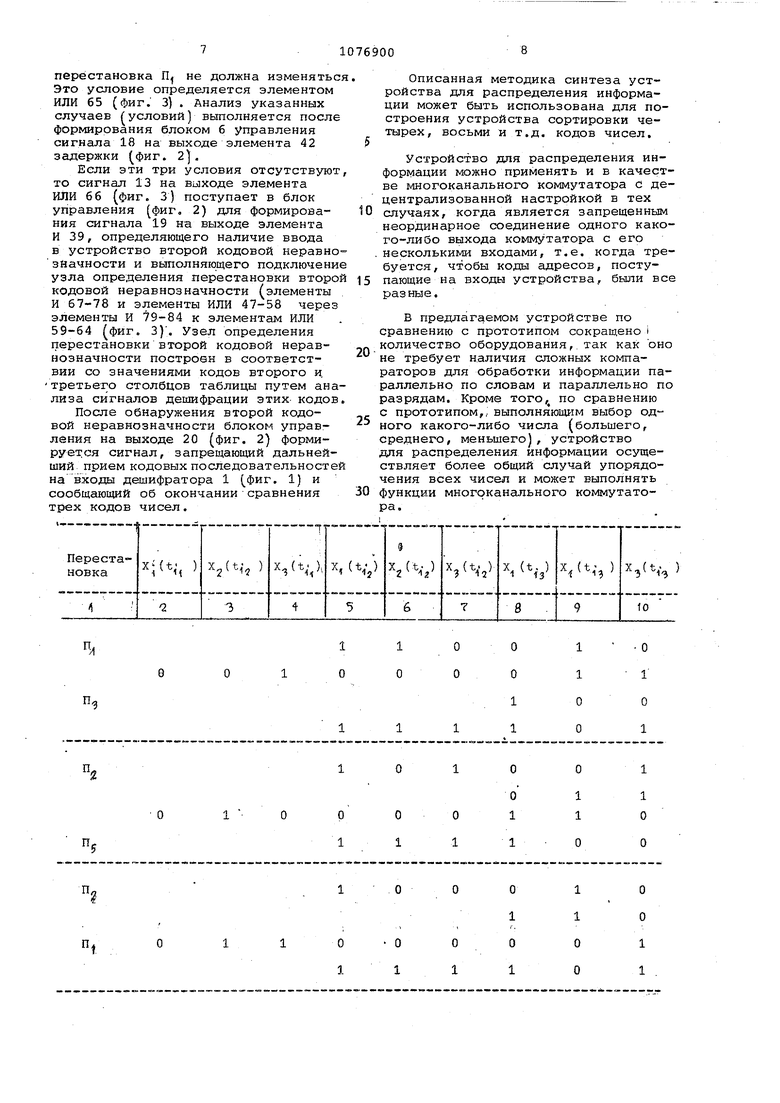

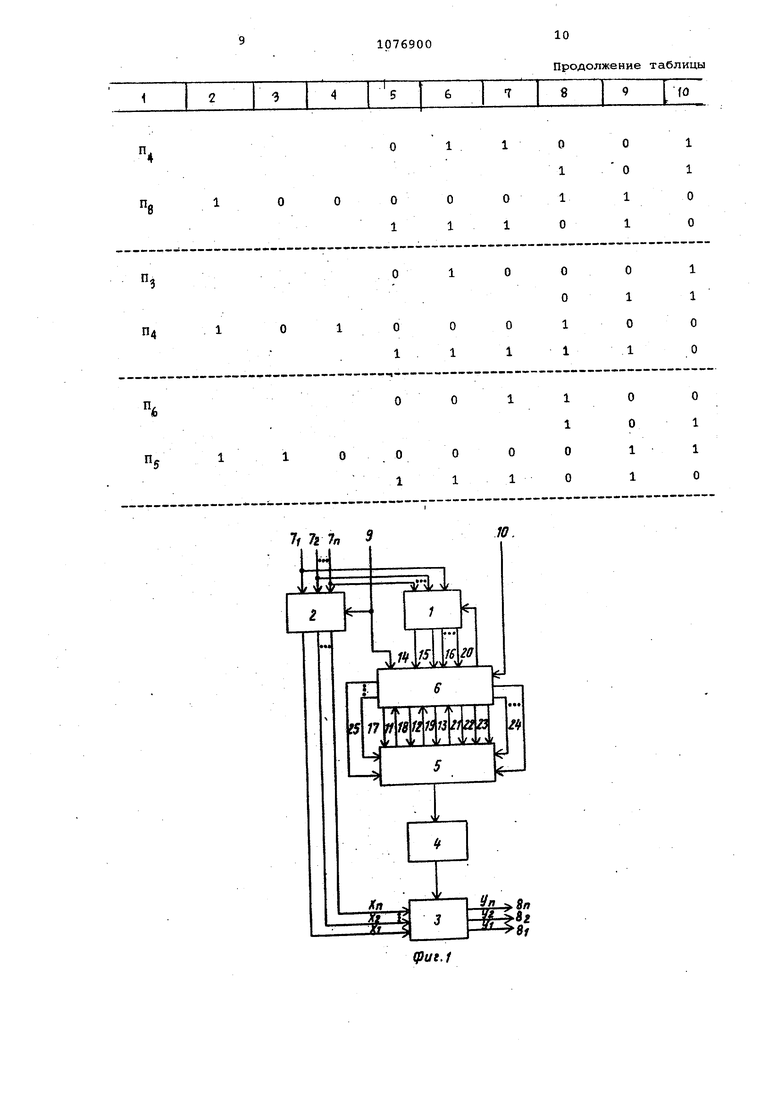

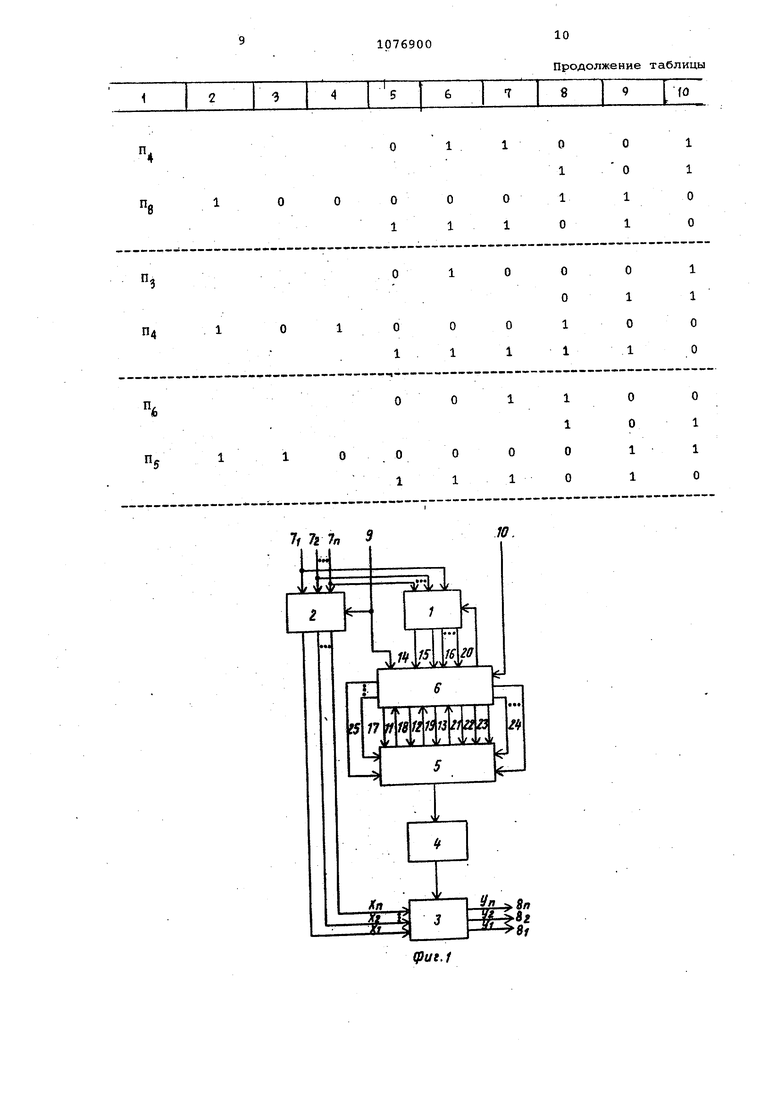

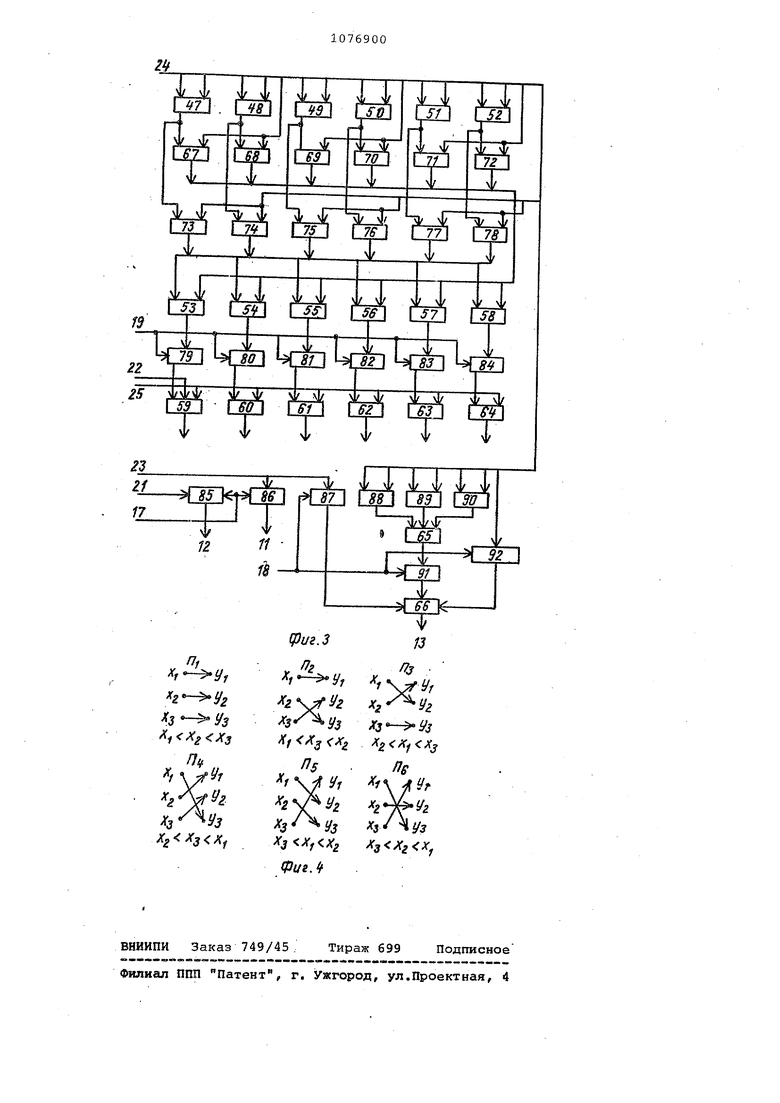

соответственно с первым, шестым, четвертым, третьим, пятым и вторым входами первой группы блока, выходы элементов ИЛИ с первого по шестой соединены соответственно с вторыми входами элементов И с первого по шестой и втор1 1ми входами элементов И с седьмого по двенадцатый, выхо&ы элементов И с первого по шестой соединены соответственно с первыми входами элементов ИЛИ с седьмого подвенадэдатый, выходы которых соединены с первыми входами элементов И с шесогнадцатого по двадцать первый, вторыевходы которых соединены с третьим входом блока, выходы элементов И с седьмого по двенадцатый соединены соответственно с вторыми входа-; ми восьмого, седьмого, девятого, десятого, одиннадцатого и двенадцатого элементов ИЛИ, выходы элементов И с шестнадцатого по двадцать первый соединены соответственно с первыми входами элементов ИЛИ с тринадцатого по восемнадца тый, вторые входы которых соединены соответственно с входами с первого по шестой второй группы блока, третий вход тринадцатого элемента ИЛИ соединен с пятым входом блока, шестой вход которого соединен с первыми входами двадцать второго и . двадцать третьего элементов И, вторые входы которых соединены соответственно с первым входом двадцать четвертого элемента И,- первым и вторым входами блока, первым входом двадцать пятого элемента И.и управляющим входом дешифратора, второй вход двадцать четвертого элемента И соединен с четвертым входом блока, выходы элементов И с тринадцатого по пятнадцатый соединены соответственно с входами с первого по третий девятнадцатого элемента ИЛИ, выход которого соединен с вторым входом двадцать пятого элемента И, выход которого соединен с первым входом двадцатого элемента ИЛИ, второй вход которого соединен с выходом двадцать третьего элемента И, а третий вход - с выходом дешифратора, информационные входы которого соединены соответственно с входами первой группы блока, выходы двадцать второго и двадцать четвертого элементов И, двадцатого элемента ИЛИ являются соответственно вторым, четвертым и третьим выходами блока, выходы элементов ИЛИ с тринадцатого по восемнадцатый являются первым входом блока. Изобретение относится к вычисли тельной технике и предназначено для сортировки кодов чисел в возрастающем или убывающем порядке или для коммутации цифровых каналов свя зи. Известно устройство,предназначен ное для выбора среднего по величине числа, в состав которого входят схемы сравнения и узлы анализа l Недостатком данного.устройства являются ограниченные функциональные; возможности. Наиболее близким техническим решением к предлагаемому является уст ройство для обработки цифровой информации, содержащее компараторы, блок мультиплексоров, дешифратор и блок анализа результатов, причем, входные шины сравниваемых чисел соединены с информационными входами блока мультиплексоров и компарэ торов, выходы которых соединены с информационными входами блока анализа результатов, управляющие входы которого подключены к выходам дешифратора, а управляющие выходы - к управляющим входам блока мультиплек соров 2 . Однако известное устройство характеризуется ограниченными функциональными возможностями, так как оно предназначено для сравнения тре двоичных чисел и выбора по величине только одного из них - большего среднего или меньшего. Цель изобретения - расширение о ласти применения устройства путем обеспечения возможности осуществле ния сортировки кодов сел как в: возрастающем, так и в убывающем порядке и сокращение количества оборудования устройства. Поставленная цель достигается тем, что в устройство для распределения информации, содержащее дешифратор, блок анализа результатов и блок мультиплексоров, причем информационные входы с первого по п -и (п - число информационных двоичных слов) дешифратора соединены соответственно с информационными входами с первого по, П -и устройства , выходы с первого по г -и блока мультиплексоров являются информационными выходами устройства, введены входной регистр, шифратор и блок управления, содержащий четыре элемента задержки, пять триггеров, четыре элемента ИЛИ, пять элементов И, группу элементов Ни регистр причем информационные входы вход- ного регистра соединены соответственно с информационными входами дешифратора, информационные выхода входного регистра соединены соответственно с информационными входа. ми блока мультиплексоров, управляю,. щий вход которого соединен с выходом шифратора, .информационный вход которого соединен с.первым выходом блока анализа результатов, рторой выход которого соединен с входом у.становки в единицу первого триггера блока управления, третий выход блока анализа результатов соединен с входом установки в единицу второго триггера и первым входом первого элемента ИЛИ блока управления, четвертый выход блока анализа результатов соединен .с входом установки в единицу третьего триггера, входом сброса четвертого триггера и первым входом второго элемента ИЛИ блока уп равления, первый и второй входы третьего элемента ИЛИ которого соединены соответственно с первым и вторым выходами дешифратора, первые входы элементов И с первого по четвертый блока управления соединены с управляющим входом входного регистра и входом синхронизации устройства, вход первого элемента з.адержки, вторые входы первого и второго элементов ИЛИ, вход сброса второго триггера, первый вход четвертого элемента ИЛИ и управляющий вход регистра блока управления соединены с установочным входом устройства, информационные входы регистра блока управления соединены соответственно с выходами дешифратора, входы с первого по шестой блока анализа результатов соединены соответственно с выходом первого элемента И, выходом второго элемента задержки, выходом второго элемента И, выходом пятого триггера, выходом пятого элемента И и первым входом пятого элемента И блока управления, выход третьего элемента задержки которого соединен с управляющим входом дешифратора, выходы регистра блока управления соединены соответственно с первыми входами элементов И группы и входами первой группы блока анализа результатов у входы второй группы которого соединены соответственно с ; выходами элементов И группы блока управления, выход первого элемента задержки блока управления соединен с входом установки в единицу четвертого триггера, прямой выход которого соединен с вторым в.ходом первого элемента И, прямые выходы пер- : вого, второго и третьего триггеров соединены соответственно с вторыми входами третьего, второго и четвертого элементов И, ин-вёрсный выход второго триггера соединен с входом третьего элемента задержки, выходы первого и второго элементов ИЛИ соединены соответственно с входами сброса третьего и первого триггеров, вход четвертого элемента задержкисоединен с выходом пятого элемента ИЛИ, первый вход KOTOpoi o соединен с выходом третьего элемег-гга И и вгг рым входом пятого элемента И, втор вход пятого элемента ИЛИ соединен выходом четвертого элемента И,, вхо дом второго элемента задержки и вт рыми входами группы элементов И, выход четвертого элемента задержки .соединен с вторым входом четвертог элемента .ИЛИ, выход которого соеди нен с входом установки в- единицу пятого триггера, инверсный выход и вход сброса которого соединены соответственно с первым входом пятого элемента И и выходом третье элемента ИЛИ а Кроме того, блок анализа резуль татов содержит двадцать элементов ИЛИ, двадцать пять элементов И и дешифратор, причем первые входы элементов ИЛИ с первого по шестой соединены соответственно с вторым, четвертым/ третьим, первым и вторы входами- первой группы блока, вторы входы элементов ИЛИ с первого по шегстой соединены соответственно с третьим, пятым, шестом, первым, ПЯ1ТЫМ и шестьп вход1;ами первой груп пы блока, первые входа первого и в рого, третьего и четвертого, пятог и шестого, седьмого и восьмого девятого и десятого, одиннадцатого и двенадцатого элементов И соеди-нены соответственно с первым, вторым, четвертым, шестым, пятым и третьим входами первой группы блок первый вход тринадцатого элемента второй вход тринадцатого элемента первый вход четырнадцатого элемент И, второй вход четырнадцатого элемента И, первый вход пятнадцатого элемента И, второй вход пятнадцато элемента И соединены соответственно с первым, шестым, четвертым,- третьи пятым и вторь / входами первой групп блока, выходы элеке1 тов ИЛИ с перво го по шестой соединены соотватственно с вторым-И входами элементов И с первого rto шестой и вторыми входадМИ элементов И с седьмого по двенадцатый выходы элементов И с первого по Шестой соединены соответственно с первыми входами элементов ИЛИ с седьмого по двенадцатый, выходы которых соединены с пер выми входами элементов И с шестнадцатого по двадцать первый, вторые входы которых соединены с третьим входом блока, выходы элементов И с седьмого по двенадцатый соединены соответственно с вторыми входами восьмого, седьмого, девятого, десятого, одиннадцатого и двенадцатого элементов ИЛИ, выходы элементов И с шестнадцатого по двадцать первый соединены соответственно с первыми входами элементов ИЛИ с тринадцатого по восемнадцатый, вторые входы которых соединены соответственно с входами с первого по шестой в1орой группы .блока, третий вход тринадцатого элемента ИЛИ соединен с пятым входом блока, шестой вход которого соединен с первыми входами двадцать второго и двадцать третьего элементов И, вторые входы которых соединены соответственно с первым входом двадцать четвертого элемента И, первым и вторым входами блока, первым входом двадцать пятого элемента И и,управляющим входом дешифратора, второй вход двадцать четвертого элемента И соединен с четвертым входом блока, выходы элементов И с тринадцатого по пятнадцатый соединены соответственно с входами с первого по третий девятнадцатого элемента ИЛИ, выход которого соединен с вторым входом двадцать пятого элемента И, выход которого соединен с первым входом двадцатого элемента ИЛИ, второй вход которого соединен с выходом двадцать третьего элемента И, а третий вход - с выходом дешифратора, информационные входы которого соединены соответственно с входами первой группы блока, выходы двадцать второго и двадцать четвертого элементов И, двадцатого элемента ИЛИ явл-яются соответственно вторым, четвертым и третьим выходами блока, выходы элементов ИЛИ с тринадцатого по восемнадцатый являются ibepBbiM входом блока На фиГе 1 изо.бражена структурная схема устройства для распределения информации; на фиг. 2 -- функциональная схема блока управления/ на фиг, 3 - функциональная схема блока анализа результатов; на фиг. 4 - схема перестановки блоков сорти-руемых кодов чисел. В состав устройства входят Дешифратор 1, входной регистр 2, блок 3 рдультиплексоров, шифратор 4, блок 5 анализа результатов, блок б .управления, информационные входы 7 с первого по г -и, информационные выходы 8 с первого по Я -и, вход 9 синхронизации, управляющий вход 10, входы 11-16..блока .6, выходы 17-23 блока б, первая группа выходов 24 блока б, вторая группа выходов 25 блока 6 управления, пять триггеров 26-30, пять элементов ИЛИ 31-35, пять элементов И 36-40, четыре элемента 41-44 задержки, регистр 45, группа элементов И 46, элементы ИЛИ 47-66, элементы И 67-91 и дешифратор 92 единицы. Устройство для распределения инфор1мации работает следующим образом. Сигнал, определяющий начало работы устройства, поступает на управляющий вход 10 устройства (фиг.1) и устанавливает три-ггеры 26-28 и регистр 45 в нулевое состояние, а триггер 30 в единичное (фиг. 2) . При сортировке кодов чисел они поступают последовательно по разрядам и параллельно по словам на ин формационные входы 7 устройства (фиг. 1). Битовый срез (код определенных разрядов поступивших чисел чисел декодируется дешифратором 1 фиг. 1) и зажимается в триггере 29 и регистре 45 (фиг. 2). Сигнал с триггера 30 поступает на вход элемента И 36, на другой вход которого поступает синхронизирующий сигнал (вход 9 синхронизации устройства). На выходе элемента И 3 вырабатывается сигнал 17 опроса, который поступает на входы элементов И 85 и 86 блока анализа результатов (фиг. 3). На выходах элементов И 85 и 86 формируются сигналы 11 и 12 анализа состояния -триггера 29 (фиг. 2). Единичное состояниетриггера 29 определяет равенство разрядов битовых срезов (коды битовых срезов 000 или 111) , а нулевое соетояние - появление первой неравнозначности в битовом Срезе. При наличии сигнала 11 на элементе И 86 (фиг, 3) он поступает на триггер 26 фиг. 2). Сигнал с триггера 26 поступает на вход элемента И 37, на др гой вход которого поступает сийхронизирующий сигнал (вход 9 синхронизации устройства). Сигнал с выхода элемента И 37 через вход 22 и элемент. ИЛИ 59 блока анализа результатов (фиг. З) поступает в шифратор 4 (фиг. 1), который настраивает бло .3 мультиплексоров на необходимую перестановку битов сортируемых кодов чисел. Для сортировки трех кодов чисел существует шесть перестан вок П - Tig (фиг. 4) . После выполнения настройки блока 3 мультиплексоров на требуемую перестановку (коммутацию определенных его входов и выходов) осуществляетс передача битового среза из входного регистра 2 через блок 3 мультиплексоров на информационные выходы В устройства.. Сигнал с выхода элемента И 37 (фиг. 2) через элемент ИЛИ 35, элемент 44 задержки и элемент ИЛИ 33 поступает также на сброс триггера 29. Указанные действия выполняются до тех пор, пока не появится первая неравнозначность битов в битовом срезе. При этом на выходе элемента И 85 появляется сигнал 12 (фиг. 3V, который поступает на триггер 27 (йиг. 2). Сигнал с триггера 27 поступает на вход элемента И 38, на другой вход которого поступает синхронизирующий сигнал (вхо 9 синхронизации устройства). Сигнал с выхода элемента И 38 через группу элементов И 46 И элементы ИЛИ 59-64 блока анализа результатов (фиг. З) поступает в шифратор 4 (фиг. 1), который настраивает блок . 3 мультиплексоров на необходимую перестановку. Каждый из элементов ИЛИ 59-64 (фиг. 3) выполняет сборку сигналов для осуществления перестановки П ( - число перестановок, - б). Каждой кодовой неравнозначности соответствует два типа перестановок , из которых выбирается для схемной реализации любая. Например, коду битового среза трех чисел 001 соответствуют перестановки П и П(фиг. 4). Это связано с тем, что условно принято следукядее: максимальный код числа или разряд битового среза всех трех кодов чисел должен быть выведен на выходе Ч-., (8) , а минимальный код числа (разряд) - на выходе Y, (8д) . Поэтому коду 001 (Х Х Х) соответствуют перестановки П ;, и 1, в которых третий бит Х является максимальным (вход Хз блока 3 мультиплексоров должен быть соединен с выходом Блок 5 анализа результатов синтезирован в соответствии с таблицей определения перестановок битов. Бо втором столбце таблицы помещены биты первой кодовой неравнозначности , а в колонке 1 - соответствующие им номера перестановок. Третий столбец содержит коды битовых срезов, поступающие на входы 7 устройства в момент времени t(,n которые не изменяют соответствующих перестановок первых кодовых неравнозначностей. Так, если первая неравнозначность была 001, то последующие коды битовых срезов.110, 000 и 111 не изменяют перестановку П) или П 3 . .Возможны три случая повторения перестановок первой кодовой неравнозначности. Первый случай - случай повторения поступления первой кодовой неравнозначности. В блоке анализа результатов (фиг. 3) он определяется с помощью дешифратора 92 одной единицы, наличие сигнала с выхода которого сигнализирует о необходимости поворота предыдущей перестановки. Второй случай связан с равенством всех трех битов в битовом срезе (коды 000 и 111) и реализуется элементом И 87, сигнал с выхода которого подтверждает, что триггер 29 (фиг. 2) находится в. единичном состоянии (наличие кода 000 или 111 на информационных входах 7 устройства) . Третий случай соответствует равенству двух других битов в битовом срезе. Например, если первая кодовая неравнозначность 001 ( Хз)f то при поступлении кода 110 перестановка П не должна изменять Это условие определяется элементом ИЛИ 65 (фиг. 3) . Анализ указанных случаев условий) выполняется посл формирования блоком 6 управления сигнала 18 на выходе элемента 42 задержки (фиг. 2, Если эти три условия отсутствую то сигнал 13 на выходе элемента ИЛИ 66 (фиг. 3) поступает в блок управления фиг, 2) для формирования сигнала 19 на выходе элемента И 39, определяющего наличие ввода в устройство второй кодовой неравно значности и выполняющего подключени узла определения перестановки второ кодовой неравнозначности (элементы И 67-78 и элементы ИЛИ 47-58 через элементы И 79-84 к элементам ИЛИ 59-64 (фиг. 3). Узел определения перестановки второй кодовой неравнозначности построен в соответствии со значениями кодов второго и, третьего столбцов таблицы путем ана лиза сигналов дешифрации этих кодов После обнаружения второй кодовой неравнозначности блоком управления на выходе 20 (фиг. 2) формируется сигнал, запрещающий дальнейший прием кодовых последовательносте на входы дешифратора 1 (фиг. 1) и сообщающий об окончании сравнения трех кодов чисел. Описанная методика синтеза устройства для распределения информации может быть использована для построения устройства сортировки четырех, восьми и т.д. кодов чисел. Устройство для распределения информации можно применять и в качестве многоканального коммутатора с децентрализованной настройкой в тех случаях, когда является запрещенным неординарное соединение одного какого-либо выхода коммутатора с его несколькими входами, т.е. когда требуется, чтобы коды адресов, поступающие на входы устройства, были все разные. В предлагаемом устройстве по сравнению с прототипом сокращено i количество оборудования,, так как оно не требует наличия сложных компараторов для обработки информации параллельно по словам и параллельно по разрядам. Кроме того, по сравнению с прототипом,, выполняющим выбор одного какого-либо числа (большего, среднего, меньшего), устройство для распределения информации осуществляет более общий случай упорядочения всех чисел и может выполнять функции многоканального коммутатора.

Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ ДЛЯ ОРГАНИЗАЦИИ ОБМЕНА СООБЩЕНИЯМИ | 2007 |

|

RU2359320C2 |

| Многоканальный измеритель интенсивности импульсов | 1991 |

|

SU1807423A1 |

| Вычислительное устройство | 1981 |

|

SU993270A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1718215A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Устройство для спектрального анализа | 1984 |

|

SU1241256A1 |

| Устройство для автоматического контроля генератора случайных чисел | 1982 |

|

SU1020837A1 |

1. УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ИНФОРМАЦИИ, содержащее дешифратор, блок анализа результатов и блок мультиплексоров, причем информационные вхолы с первого по п -и (П - число информационных двоичных слов) дешифратора соединены соответственно с информационными входами с первого по п -и устройства, выходы с первого по и -и блока мультиплексоров являются информационными выходами устройства, отличающееся тем, что, с целью расширения области применения путем обеспечения возможности осуществления сортировки кодов чисел как в возрастающем, так и в убывающем порядке и сокращения количества оборудования ,в него введены входной регистр, шифратор и блок управления, содержащий четыре элемента задержки, пять триггеров, четыре элемента ИЛИ, пять элементов И, группу элемен±ов И и регистр, причем информационные входы входного регистра соединены соответственно с информационными входами дешифратора, информационные выходы входного регистра соединены соответственно с информационными входами блока мультиплексоров, управляющий вход которого соединен с выходом шифратора, информационный вход которого соединен с первым выходом блока анализа результатов, второй выход которого соединен с входом установки в единицу первого триггера блока управления, третий выход блока анализа результатов соединен с входом установки в единицу второго триггера и первым входом первого элемента ИЛИ блока управления, четвертый выход блока анализа результатов соединен с входом установки в единицу третьего триггера, входом сброса четвертого триггера и первым входом второго элемента ИЛИ блока управления, первый,и второй входы третьего элемента ИЛН которого соединены соот-г ветсхвенно с первым и вторым выходами дешифратора, первые входы элементов И с первого по четвертый блока управления соединены с управляющим входом входного регистра и входом синхронизации устройства, вход первого элемента задержки, вторые входы первого и второго элементов ИЛИ, вход сброса второго триггера, первый вход четвертого элемента ИЛИ и управляющий вход регистра блока управления соединены с установочным О входом устройства, информационные входы регистра блока управления соединены соответственно с выходами С5 дешифратора, входы с первого по шессо той блока анализа результатов соединены соответственно с выходом первого элемента И, выходом второго о элемента задержки, выходом второго элемента И,пряЬ ым выходом пятого триггера, выходом пятого элемента И и первым входом пятого элемента И блокауправления, выход третьего элемента задержки которого соединен с управляющим входом дешифратора, выходы регистра блока управления соединены соответственно с первыми входами элементов И группы н входами первой группы блока анализа результатов, входы второй группы которого, соединены соответственно с выходами

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения среднего из трех чисел | 1977 |

|

SU717758A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-02-28—Публикация

1982-04-30—Подача