Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах сортировки деталей по группам.

Цель изобретения - упрощение регистра сдвига путем сокращения числа тактовых входов с четырех до двух.

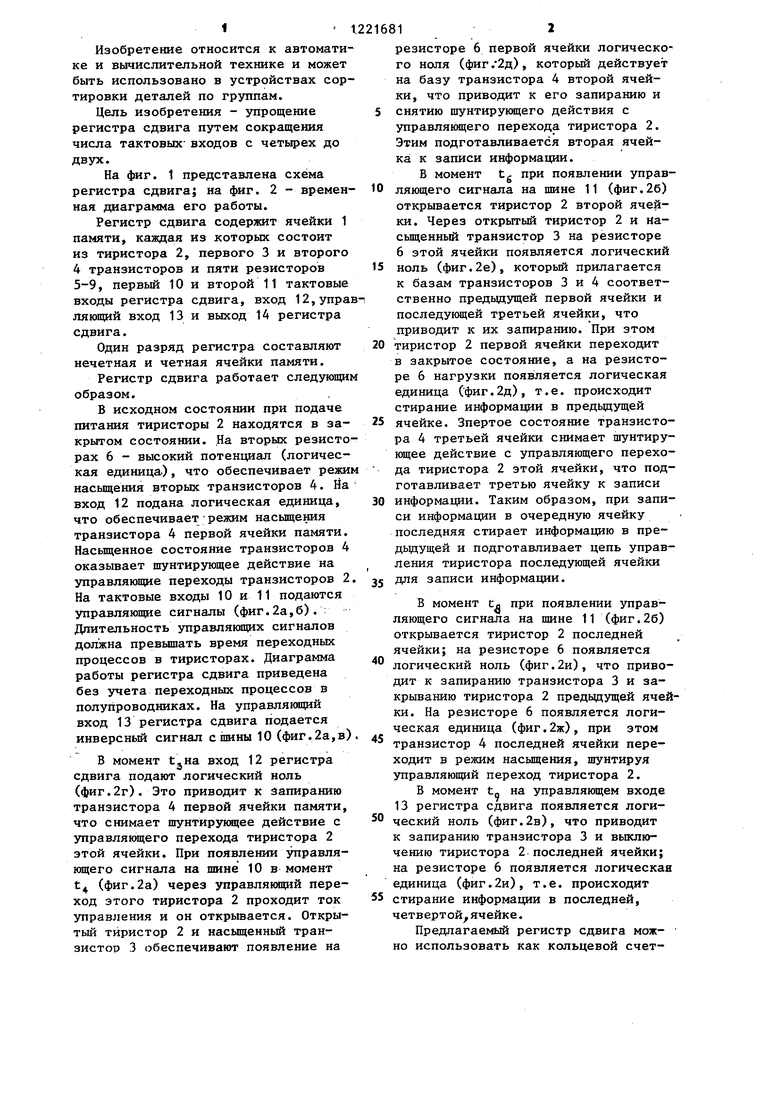

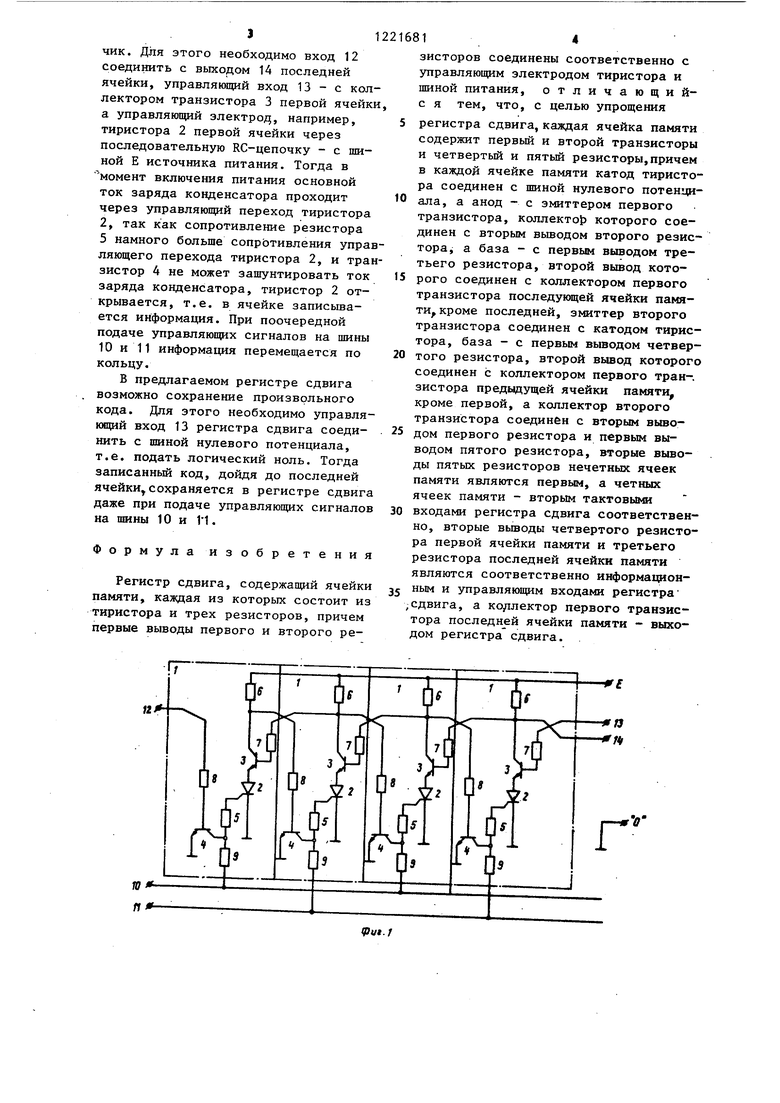

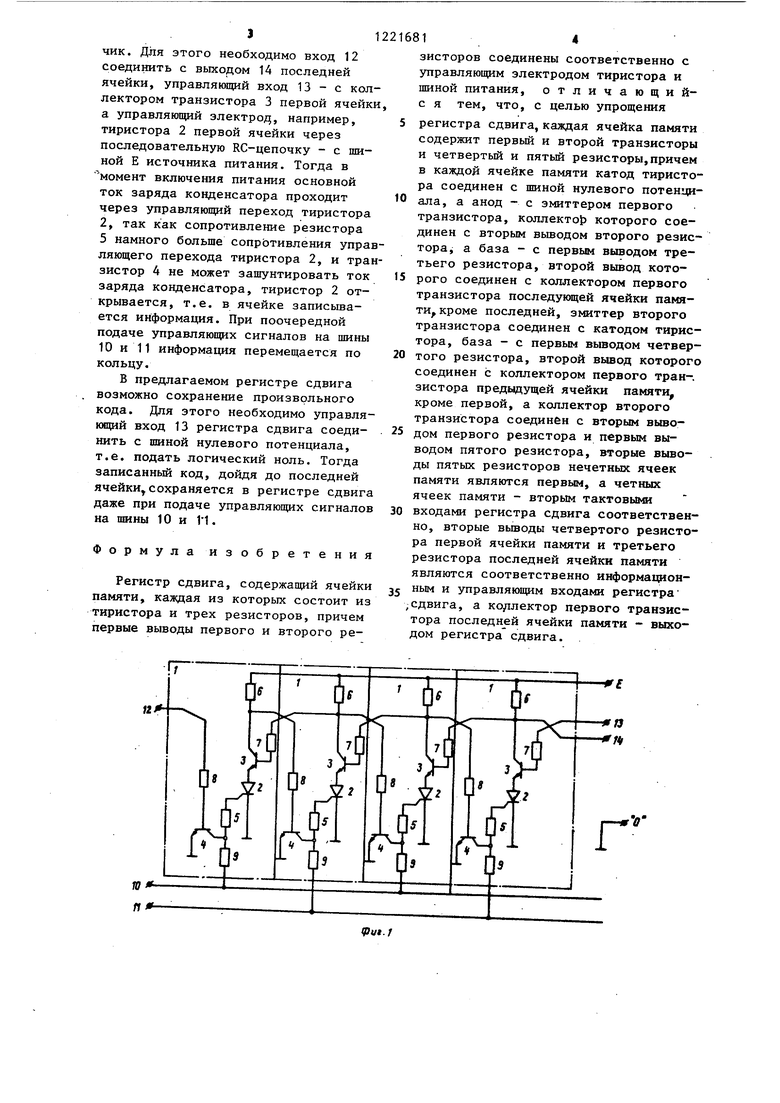

На фиг. 1 представлена схема регистра сдвига; на фиг. 2 - временная диаграмма его работы.

Регистр сдвига содержит ячейки 1 памяти, каждая из которых состоит из тиристора 2, первого 3 и второго 4 транзисторов и пяти резисторов 5-9, первый 10 и второй 11 тактовые входы регистра сдвига, вход 12,управ ляющий вход 13 и выход 14 регистра сдвига.

Один разряд регистра составляют нечетная и четная ячейки памяти.

Регистр сдвига работает следующим образом.

В исходном состоянии при подаче питания тиристоры 2 находятся в закрытом состоянии. На вторых резисторах 6 - высокий потенциал (логическая единица), что обеспечивает режим насыщения вторых транзисторов 4. На вход 12 подана логическая , что обеспечивает режим насыщения транзистора 4 первой ячейки памяти. Насыщенное состояние транзисторов 4 оказывает шунтирующее действие на управляющие переходы транзисторов 2. На тактовые входы 10 и 11 подаются управляющие сигналы (фиг.2а,б). Длительность управлякнцих сигналов должна превышать время переходных процессов в тиристорах. Диаграмма работы регистра сдвига приведена без учета переходных процессов в полупроводниках. На управлякиций вход 13 регистра сдвига подается инверсный сигнал с шины 10 (фиг.2а,в)

В момент tjHa вход 12 регистра сдвига подают логический ноль (фиг.2г). Это приводит к Запиранию транзистора 4 первой ячейки памяти, что снимает шунтирукяцее действие с управляющего перехода тиристора 2 этой ячейки. При появлении управпя ющего сигнала на шине 10 в момент t (фиг.2а) через управляющий переход этого тиристора 2 проходит ток управления и он открывается. Открытый тиристор 2 и насыщенньй транзистор 3 обеспечивают появление на

резисторе 6 первой ячейки логического ноля (фиг .2д) , который действует на базу транзистора 4 второй ячейки, что приводит к его запиранию и 5 снятию шунтирукяцего действия с управляющего перехода тиристора 2. Этим подготавливается вторая ячейка к записи информации.

В момент tg при появлении управ0 ляющего сигнала на шине 11 (фиг.2б) открывается тиристор 2 второй ячейки. Через открытый тиристор 2 и Насыщенный транзистор 3 на резисторе 6 этой ячейки появляется логический

5 ноль (фиг.2е), который прилагается к базам транзисторов 3 и 4 соответственно предыдущей первой ячейки и последуннцей третьей ячейки, что приводит к их запиранию. При этом

0 тиристор 2 первой ячейки переходит в закрытое состояние, а на резисторе 6 нагрузки появляется логическая единица Сфиг.2д), т.е. происходит стирание информации в предьщущей

5 ячейке. Зпертое состояние транзистора 4 третьей ячейки снимает шунтирующее действие с управляющего перехода тиристора 2 этой ячейки, что подготавливает третью ячейку к записи

0 информации. Таким образом, при записи информации в очередную ячейку последняя стирает информацию в предыдущей и подготавливает цепь управления тиристора последующей ячейки

5 для записи информации.

В момент tc

On при ляющего сигнала на

0

5

появлении управ- шине 11 (фиг.2б)

открывается тиристор 2 последней ячейки; на резисторе 6 появляется логический ноль (фиг.2и), что приводит к запиранию транзистора 3 и закрыванию тиристора 2 предьщущей ячейки. На резисторе 6 появляется логическая единица (фиг.2ж), при этом транзистор 4 последней ячейки переходит в режим насыщения, шунтируя управляющий переход тиристора 2.

В момент tn на управлякмцем входе 13 регистра сдвига появляется логи0 ческий ноль (фиг.2в), что приводит к запиранию транзистора 3 и выключению тиристора 2 последней ячейки; на резисторе 6 появляется логическая единица (фиг.2и), т.е. происходит

5 стирание информации в последней, четвертой,ячейке.

Предлагаемый регистр сдвига можно использовать как кольцевой счетчик. Для этого необходимо вход 12 соединить с выходом 14 последней ячейки, управляющий вход 13 - с коллектором транзистора 3 первой ячейки, а управляющий электрод, например, тиристора 2 первой ячейки через последовательную RC-цепочку - с шиной Е источника питания. Тогда в момент включения питания основной ток заряда конденсатора проходит через управляющий переход тиристора 2, так как сопротивление резистора 5 намного больше сопротивления управляющего перехода тиристора 2, и транзистор 4 не может эашунтировать ток заряда конденсатора, тиристор 2 открывается, т.е. в ячейке записывается информация. При поочередной подаче управляющих сигналов на шины 10 и 11 информация перемещается по кольцу.

В предлагаемом регистре сдвига возможно сохранение произвольного кода. Для этого необходимо управляющий вход 13 регистра сдвига соединить с шиной нулевого потенциала, т.е. подать логический ноль. Тогда записанньш код, дойдя до последней ячейки сохраняется в регистре сдвига даже при подаче управляющих сигналов на шины 10 и Г1.

Формула изобретения

Регистр сдвига, содержащий ячейки памяти, каждая из которых состоит из тиристора и трех резисторов, причем первые выводы первого и второго ре, ав

я

10

и з 15

221681

зисторов соединены соответственно с управляющим электродом тиристора и шиной питания, отличающий- с я тем, что, с целью упрощения регистра сдвига, каждая ячейка памяти содержит первьш и второй транзисторы и четвертьй и пятый резисторы,причем в каждой ячейке памяти катод тиристора соединен с шиной нулевого потенциала, а анод - с эмиттером первого транзистора, коллекто1 которого соединен с вторым вьшодом второго резистора j а база - с первым выводом третьего резистора, второй вывод которого соединен с коллектором первого транзистора последукяцей ячейки памяти, кроме последней, эмиттер второго транзистора соединен с катодом тиристора, база - с первым выводом четвертого резистора, второй вывод которого соединен с коллектором первого тран-. зистора предыдущей ячейки памяти, кроме первой, а коллектор второго транзистора соединен с вторым выводом первого резистора и первым выводом пятого резистора, вторые выводы пятых резисторов нечетных ячеек памяти являются первым, а четных ячеек памяти - вторым тактовыми входами регистра сдвига соответственно, вторые вьшоды четвертого резистора первой ячейки памяти и третьего резистора последней ячейки памяти являются соответственно информадаон- ным и управляющим входами регистра ,сдвига, а коллектор первого транзистора последн ей ячейки памяти - выходом регистра сдвига.

20

25

30

35

а

Ю

6

rr

t

п

г п

д Вых.

ЯП1

е Вых.

я/72

ж

Вых. ЙПЗ

и Вых.

япч

Ui.2

Составитель А.Дерюгин Редактор А.Огар Техред В.Кадар Корректор Л.Пнлипенко

Заказ 1616/56 Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г. Ужгород, ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для регистра сдвига | 1974 |

|

SU1327186A1 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1205243A2 |

| Коммутатор | 1984 |

|

SU1233273A1 |

| Устройство для отображения графической информации на газоразрядном матричном индикаторе | 1987 |

|

SU1495846A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В БИПОЛЯРНЫЙ КОД | 2002 |

|

RU2218660C2 |

| Способ поиска дефектов в цифровых блоках и устройство для его осуществления | 1985 |

|

SU1260884A1 |

| УСТРОЙСТВО ИМПУЛЬСНО-ФАЗОВОГО УПРАВЛЕНИЯ | 1999 |

|

RU2160957C2 |

| Регистр сдвига | 1982 |

|

SU1136217A1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

| Устройство для индикации отказов в трехканальной вычислительной системе | 1989 |

|

SU1721608A1 |

Изобретение относится к области автоматики и вычислительной техники , и позволяет упростить регистр сдвига путем сокращения числа тактовых входов с четырех до двух. Один разряд регистра сдвига составляют две ячейки памяти, каждая из которых состоит из тиристора, двух транзисторов и пяти резисторов. Сокращение числа тактовых шин по сравнению с прототипом стало возможным благодаря введению в состав ячейки двух транзисторов и двух резисторов. 2 ял. 1С ю о 00

| Ячейка памяти | 1978 |

|

SU677012A1 |

| Ауэн Л.Ф | |||

| Цифровые и переключающие устройства на тиристорах | |||

| М.: Энергия, 1974, с.78. | |||

Авторы

Даты

1986-03-30—Публикация

1984-08-14—Подача