1

Изобретение относится к вычислительной технике и может быть использовано для создания быстродействзло- щего сдвигового регистра с высоким уровнем помехоустойчивости.

Целью изобретения является повышение помехоустойчивости и увеличение быстродействия ячейки памяти для регистра сдвига.

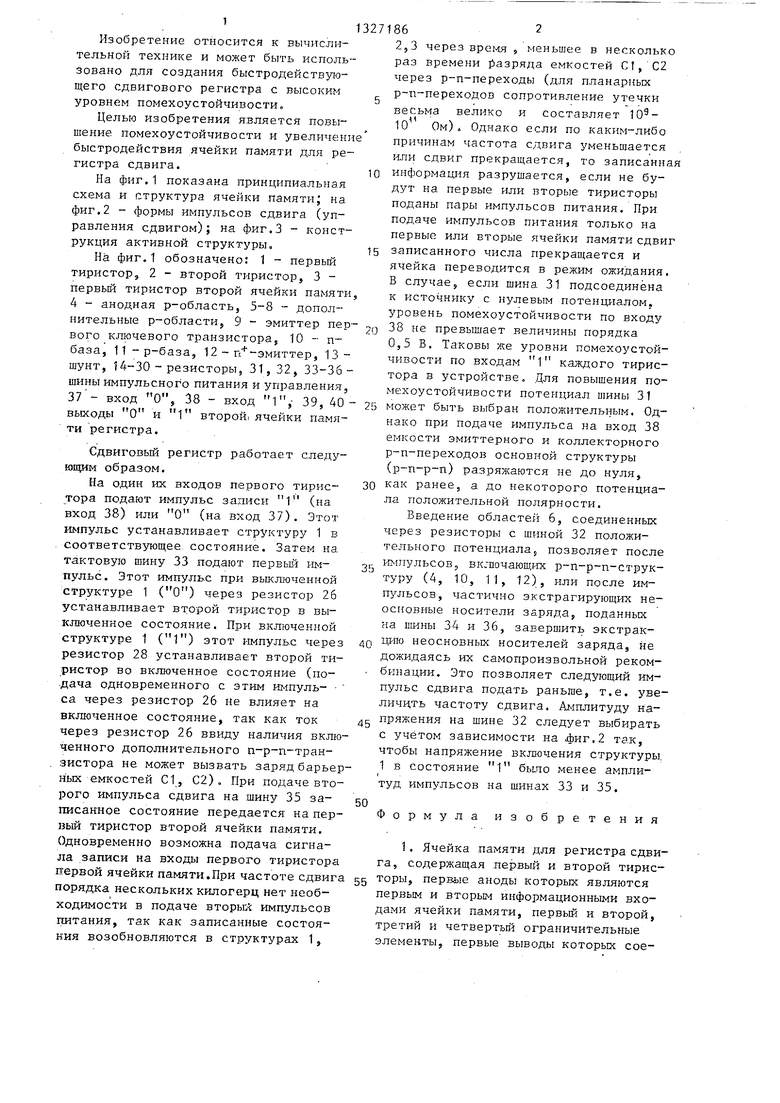

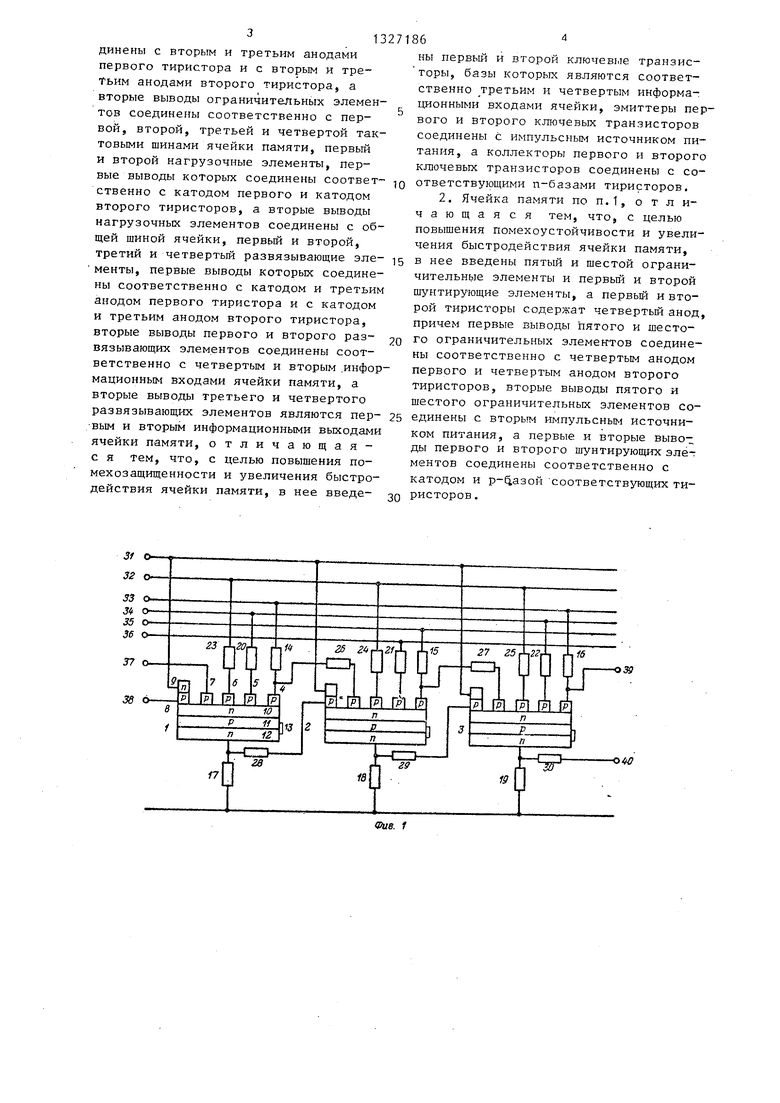

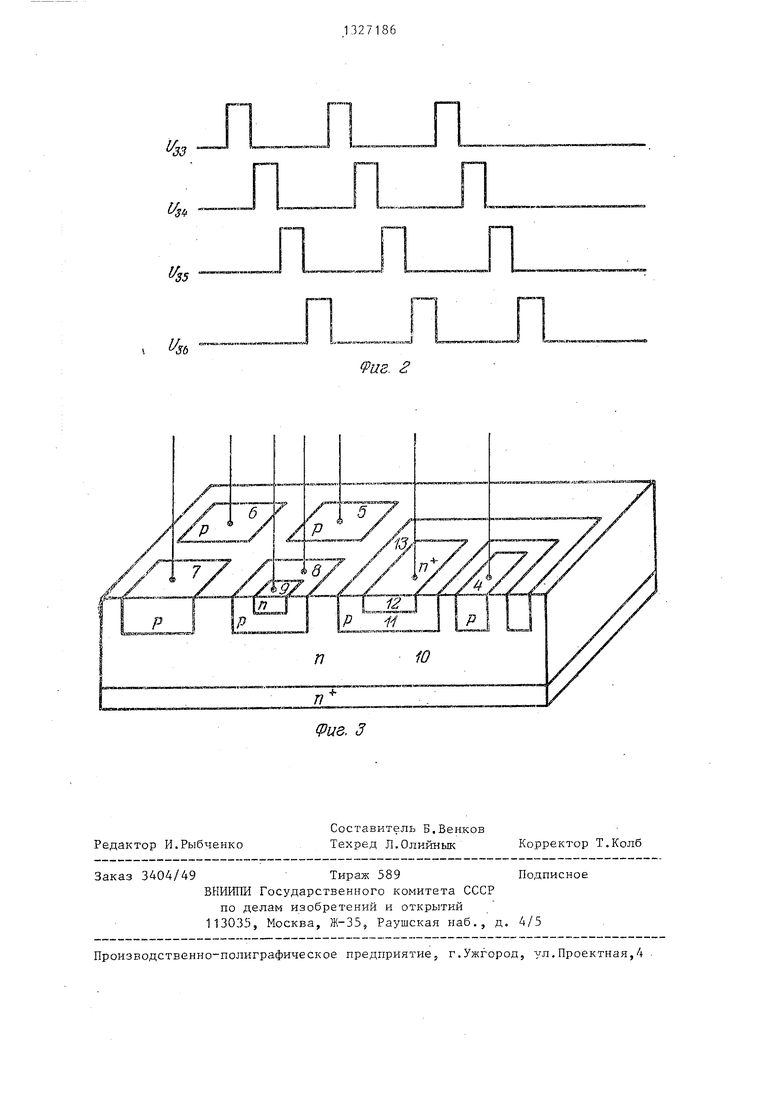

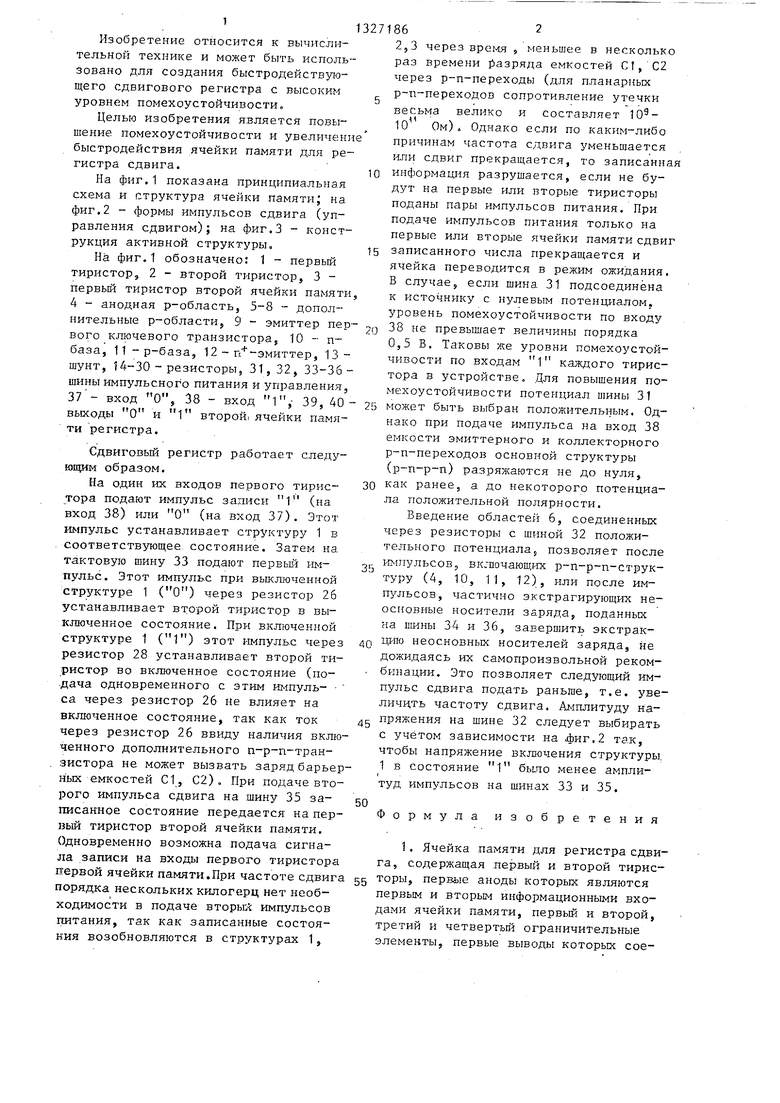

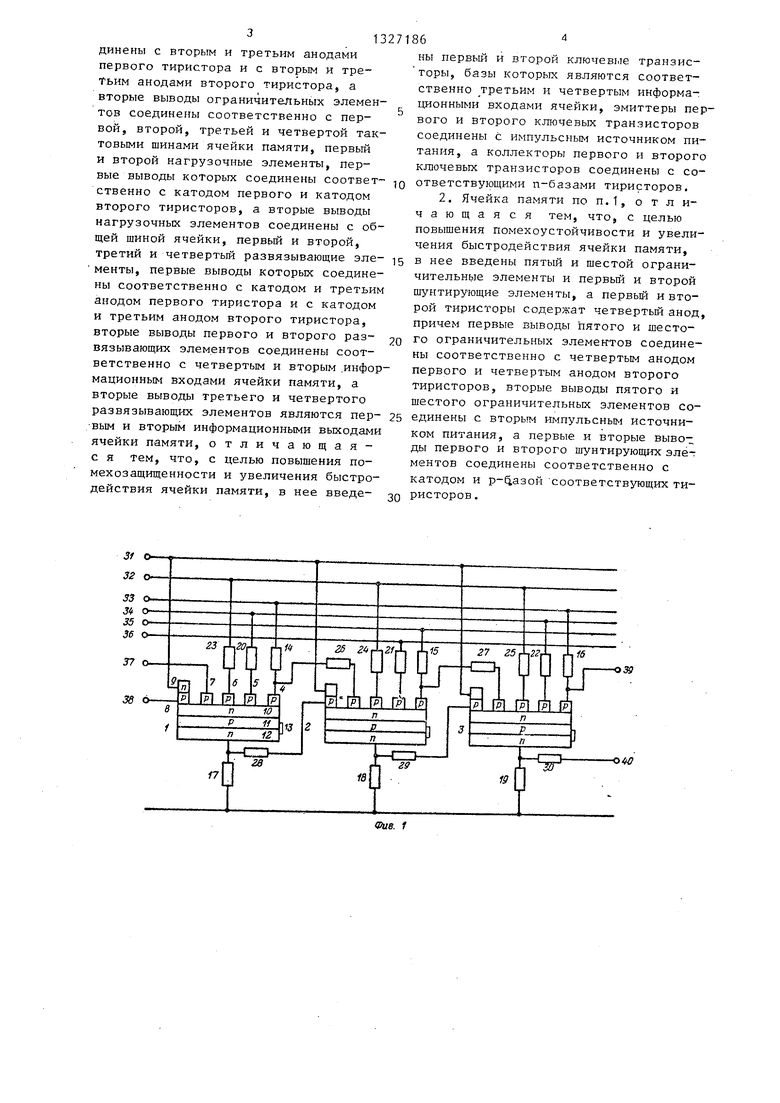

На фиг.1 показана принципиальная схема и структура ячейки памяти; на фиг,2 - формы импульсов сдвига (управления сдвигом); на фиг.З - конструкция активной структуры,

На фиг.1 обозначено: 1 - первьй тиристор, 2 - второй тиристор, 3 - первый тиристор второй ячейки памяти 4 - анодная р-область, 5-8 - дополнительные р-области, 9 - эмиттер пер- вого ключевого транзистора, 10 - п- база, 11-р-база, 12 - п -эмиттер, 13- шунт, 14-30 резисторы, 31, 32, 33-36- шины импульсного питания и управления, 37- вход О, 38 - вход 1,- 39, 40- выходы ти регистра.

О и 1 второй, ячейки памяСдвиговый регистр работает следующим образом.

На один их входов первого тирис- тора подают импульс записи 1 (на вход 38) или О (на вход 37). Этот импульс устанавливает структуру 1 в соответствующее состояние. Затем на тактовую шину 33 подают первьш им- пульс. Этот импульс при выключенной структуре 1 (О) через резистор 26 устанавливает второй тиристор в выключенное состояние. Прр включенной структуре 1 (1) этот импульс через резистор 28 устанавливает второй тиристор во включенное состояние (по- .дача одновременного с этим импуль- са через резистор 26 не влияет на включенное состояние, так как ток через резистор 26 ввиду наличия включенного дополнительного п-р-п-тран- зистора не может вызвать заряд барьерных емкостей С1, С2), При подаче второго импульса сдвига на шину 35 за- писанное состояние передается на первый тиристор второй ячейки памяти. Одновременно возможна подача сигнала записи на входы первого тиристора первой ячейки памяти При частоте сдвиг порядка нескольких килогерц нет необходимости в подаче вторыЛ импульсов питания, так как записанные состояния возобновляются в структурах 1,

862

2,3 через Bpei-w , меньшее в несколько раз времени разряда емкостей С1, С2 через р-п-переходы (для планарных р-п-переходов сопротивление утечки весьма велико и составляет 10 Ом). Однако если по каким-либо причинам частота сдвига уменьшается или сдвиг прекращается, то записанная информация разрушается, если не будут на первые или вторые тиристоры поданы пары импульсов питания. При подаче импульсов питания только на первые или вторые ячейки памяти сдвиг записанного числа прекращается и ячейка переводится в режим ожид,ания, В случае, если шина 31 подсоединена к источнику с нулевым потенциалом, уровень помехоустойчивости по входу 38 не превышает величины порядка 0,5 В, Таковы же уровни помехоустойчивости по входам 1 каждого тиристора в устройстве. Для повышения помехоустойчивости потенциал шины 31 может быть выбран положительным. Однако при подаче импульса на вход 38 емкости эмиттерного и коллекторного р-п-переходов основной структуры (р-п-р-п) разрял аются не до нуля, как ранее, а до некоторого потенциала положительной полярности.

Введение областей 6, соединенных через резисторы с шиной 32 положительного потенциалау позволяет после 1-1мпульсов, вк:почаюш,г-пс р-п-р-п-струк- туру (4, 10, 11, 12), или после импульсов, частично экстрагирующих неосновные носители заряда, поданных на шины 34 и 36, завершить экстракцию неосновных носителей заряда, не ожидаясь их самопроизвольной рекомбинации. Это позволяет следующий импульс сдвига подать раньте, т.е. уве- ичдть частоту сдвига. Амплитуду напряжения на шине 32 следует выбирать с учётом зависимости на 41иг.2 так, чтобы напряжение включения структуры. 1 в состояние 1 было менее амплитуд импульсов на шинах 33 и 35.

ормула изобретения

1. Ячейка памяти для регистра сдвига, содержащая первый и второй тиристоры, первые аноды которых являются первым и вторым информационными входами ячейки памяти, первый и второй, третий и четвертьм ограничительные элементы, первые выводы которых соединены с вторым и третьим анодами первого тиристора и с вторым и третьим анодами второго тиристора, а вторые выводы ограничительных элементов соединены соответственно с первой, второй, третьей и четвертой тактовыми шинами ячейки памяти, первый и второй нагрузочные элементы, первые выводы которых соединены соответственно с катодом первого и катодом второго тиристоров, а вторые выводы нагрузочных элементов соединены с общей шиной ячейки, первый и второй, третий и четвертьш развязывающие эле- менты, первые выводы которых соединены соответственно с катодом и третьим анодом первого тиристора и с катодом и третьим анодом второго тиристора, вторые выводы первого и второго раз- вязывающих элементов соединены соответственно с четвертым и вторым .информационным входами ячейки памяти, а вторые выводы третьего и четвертого развязывающих элементов являются пер- вым и вторым информационными выходами ячейки памяти, отличающая- с я тем, что, с целью повышения помехозащищенности и увеличения быстродействия ячейки памяти, в нее введе-

152о 25зо

7186

вы первый и второй ключевые транзис- торы, базы которых являются соответственно третьим и четвертым информационными входами ячейки, эмиттеры первого и второго ключевых транзисторов соединены с импульсным источником питания, а коллекторы первого и второго ключевых транзисторов соединены с со- JO ответствующими п-базами тиристоров.

2. Ячейка памяти по п.1, о т л и- чающаяся тем, что, с целью повышения помехоустойчивости и увеличения быстродействия ячейки памяти, в нее введены пятый и шестой ограничительные элементы и первый и второй шунтирующие элементы, а первьш и второй тиристоры содержат четвертьш анод, причем первые выводы пятого и шестого ограничительных элементов соединены соответственно с четвертым анодом первого и четвертым анодом второго тиристоров, вторые выводы пятого и шестого ограничительных элементов соединены с вторьгм и 1пульсным источником питания, а первые и вторые выводы первого и второго шунтирующих эле-т ментов соединены соответственно с катодом и соответствующих тиристоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕХТАКТНЫЙ РЕГИСТР СДВИГА НА ТИРИСТОРАХ | 1972 |

|

SU347918A1 |

| Трехтактный регистр сдвига | 1973 |

|

SU454693A2 |

| Регистр сдвига | 1984 |

|

SU1221681A1 |

| Устройство для включения реле при пониженном напряжении питания | 1989 |

|

SU1720105A1 |

| Кольцевое пересчетное устройство | 1983 |

|

SU1100731A1 |

| Коммутатор | 1984 |

|

SU1233273A1 |

| Регистр сдвига | 1982 |

|

SU1049979A1 |

| ПАТЕ^Тй1М[Ш';=^^ГНД БсесонэзнАЯ | 1973 |

|

SU377881A1 |

| Запоминающее устройство | 1990 |

|

SU1751814A1 |

| Устройство для включения реле при пониженном напряжении питания В.Г.Вохмянина | 1989 |

|

SU1720106A1 |

Изобретение относится к области вычислительной техники. Целью изобретения является повышение помехоустойчивости и увеличение быстродействия ячейки памяти для регистра сдвига. Поставленная цель достигается тем, что в схему введены первый и второй ключевые транзисторы, эмиттеры которых соединены с импульсным источником питания, коллекторы соединены с п-ба- зами тиристоров, а базы являются информационными входами ячейки памяти. 3 ил.

3t О

о«

33

. 3

Sd

цг. 2

Фиг. 3

Редактор И.Рыбченко

Составитель Б.Венков Техред Л.Олийнык

Заказ 3404/49Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-ЗЗ, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул,Проектная,4

Корректор Т.Колб

Авторы

Даты

1987-07-30—Публикация

1974-05-31—Подача