. И:к)бретение относится к импульсной технике и может быть использоэанр при построении анало1о-цифровых преобразователей и в контрольно-измерительной аппаратуре.

Известен нуль-орган, содержащий операционный усилитель, ключевой элемент,, диоды, конденсатор, резисторы, транзистор и пороговый элемент l .

Недостатком данного устройства является то, что йаличие помехи во сигнале при изменении его полярности с положительной на отрицательную приводит к ложным срабатываниям нуль-органа. Кроме того, если время действия высокочастотной помехи превышает время разряда конденсатора, то в работе нуль-органа возникают сбои.

Наиболее близким к предлагаемому по технической сущности является устройство для сравнения напряжений, которое содержит усилитель, триггер Шмитта, источник измеряемого напряжения, источник опорного напряжения и два одновибратора 2 .

Недостатком известного устройства является то, что устойчивость его к помехам определяется временем действия выходных импульсов одновибраторов, по истечении которого наличие помехи во входном сигнале приводит к ложным срабатываниям устройства.

Цель- изобретения - повышение помехоустойчивости компаратора в широком диапазоне изменения частоты измеряемого сигнгша.

Поставленная цель достигаемся тем, что в компараторе, содержащем усилитель, инвертирующий вход которого соединен с источником измеряемого напряжения, а неинвертируквдий вход с источником опорного напряжения, две блокирующие цепи и нагрузку, каждая из блокирующих цепей содержит элемент И-НЕ, входы которого являются входг1ми блокирующей цепи, выход соединен через первый резистор с дифференцируклдей RC -цепью, выход которой подключен к базе транзистора, коллектор которого через второй резистор подключен непосредственно к входу первого э/грмента НЕ, выход которого является выходом блокирующей цепи, и к третьему резистору и конденсатору, соединенным с общей шиной, а также Дополнительно введены второй и третий элементы НЕ, четвертый и пятый резисторы и три диода, причем выхода и первые входы первой и второй . блокирующей цепей перекрестно связаны а выход усилителя непосредственно соединен с вторым входом второй блокирующей цепи и через второй элемент НЕ с вторым входом первой блокирующей цепи и через четвертый резистор с нагрузкой и с катодом первого диода, анод которого соединен с обгдей шиной, катод второго диода подключен к выходу первой блокирующей цепи, а анод - к нагрузке и к катоду третьего диода, анод которого соединен через пятый резистор с выходом третьего элемента НЕ, вход которого подключен к выходу второй блокируютцей цепи.

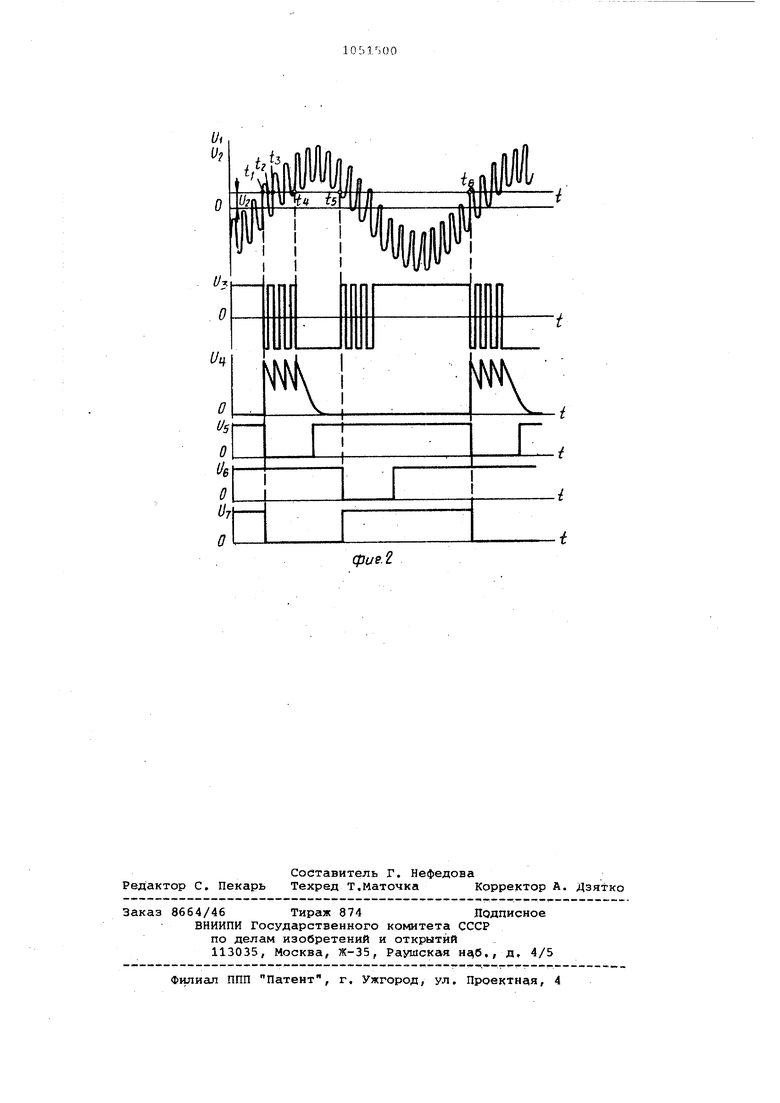

На фиг. 1 приведена структурная схема компаратора} на фиг. 2 - временные диаграммы, пояснякяцие работу компаратора.

Компаратор содержит усилитель 1, инвертирующий вход которого соединен с источником 2 измеряемого напряжения а неинвертирующий вход - с источником 3 опорного напряжения, нагрузку .4, первую блокирующую цепь 5, вторую блокирующую цепь б, каждая из которых состоит из элемента И-НЕ 7, первого резистора 8, дифференцирующей RC цепи, выполненной на конденсаторе 9 и резисторе 10, транзистора 11, второго резистора 12, первого элемента НЕ 13, третьего резистора 14 и конденсатора 15.

Кроме того, компаратор содержит второй 16 и третий 1 элементы НЕ, четвертый 18 и пятый 19 резисторы,, первый 20, второй 21 и третий 22 диоды.

,На фиг. 2 обозначено: U - напряжение на выходе источника 2измеряемого напряжения; Ifj - напряжение на выходе источника 3 опорного напряжения; 0-5 напряжение на выходе усилителя 1; U4 - напряжение на конденсаторе 15;. Uj - напряжение на выходе первой блокирующей цепи 5;, b(j -напряжение на выходе второй блокирующей цепи 6; U7 - напряжение на нагрузке 4.

Компаратор работает следунидим образом.

Измеряемый сигнал, содержащий высокочастотную помеху, сравнивается с опорным сигналом з усилителе 1. В момент времени t(cM. фиг. 2) происходит изменение полярности выходного сигнала усилителя 1 с положительной на отрицательную, а сигналы на выходах блокирукяцих цепей 5 и 6 соответствуют логической единице При этом на выходе элемента И-НЕ 7 формируется сигнал логического нуля, а выходной импульс дифференцируйзщей RC -цепи, образованной конденсатором 9 и резистором 10, переводит транзистор 11 в состояние насыщения, что приводит к заряду конденсатора 1 iepea резибгор 12. Разряд конденсатора 15 происходит через резай ор 14 причем постоянная времени заряда конденсатора 15 значительно меньше постоянной времени его разряда, а длительность импульса на выходе дифференцирующей цепи выбирается равно времени заряда конденсатора 15.

Выходной сигнал элемента НЕ 13, соответствующий логическому нулю, блокирует работу второй блокирую.щей цепи 6 и через диод 21 поступает на нагрузку 4, т, е, выход компаратора шунтируется первой блокирующей цепью 5.

В момент времени i-i происходит изменение полярности выходного сигнала усилителя 1 с отрицательной на положительную, но сигнал -на -выходе второй блокирующей цепи 6 не меняет своего значения, поскольк на первом ее входе сигнал соответствует логическому нулю. Выходной сигнал первой блокирукяцей цепи 5 также не меняет своего значения и соответствует логическому нулю, так как. на входе элемента НЕ 13 действует напряжение конденсатора 15.

Следующее изменение полярности сигнала на выходе усилителя 1 в момент времени -1з формирует импульс на выходе дифференцирующей RC -цепи. Транзистор 11 открывается и конденсатор 15 подзаряжается чере резистор 12. Такой подзаряд и разря конденсатора 15 будет происходить до тех пор, пока будет изменяться полярность .выходного сигнала усилителя 1 из-за наличия помехи в измеряемом сигнале, т. е. до момента времени t4 .

Таким образом, напряжение на нагрузке 4 в интервале ti - 5 соответствует логическому нулю.

В момент времени is происходит изменение полярности выходного) сигнала усилителя 1 с отрицательной на положительную, а сигналы на выходах блокирующих цепей ,5 и 6 соответствуют логической единице. С этого момента времени вступает в действие вторая блокирующая цепь.6, Работа этой цепи аналогична работе первой

блокирующей цепи 5, т , е. в момент времени tg чз выходе второй блокирующей цепи формируется сигнал, соответствующий логическому нулю, который блокирует работу первой блокирующей

0 цепи 5. При этом выходной сигнал элемента НЕ 17, соответствующий логической единице, через резистор 19 и диод 22 поступает на нагрузку 4, где происходит суммирование выход5- ных сигналов усилителя 1 и элемента НЕ 17. В результате ;напряжение на нагрузке 4 в интервале ig-t соответствует логической единице. С момента времени t работа компаратора повторяется.

Таким образом, наличие высокочастотной помехи в изг-юряемом сигнале не приводит к ложным срабатываниям компаратора.

Если уровни выходных сигналов усилителя 1 не соответствуют уровням входных сигналов элементов 6 и 16 компаратора, то необходимо использовать устройства согласования, выполненные по одной из известных

0 схем. Например, для этого можно

использ.овать резистивные дарители напряжения ;Либо включить в 1|епь отрицательной обратной связи усилителя 1 диод и стабилитрон.

5 , При использовании в качестве

усилителя 1 микросхемы дополнительных согласующих устройств не требуется, так как уровень ее выход ных сигналов согласован со стандарт0 ными ТТЛ-схемами.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОФУНКЦИОНАЛЬНЫЙ ПИКОВЫЙ ДЕТЕКТОР | 2019 |

|

RU2708687C1 |

| Помехоустойчивый триггер | 1988 |

|

SU1688402A1 |

| ИНДУКТИВНЫЙ ДАТЧИК | 2008 |

|

RU2367968C1 |

| Устройство для управления и защиты преобразователя | 1985 |

|

SU1336171A1 |

| РЕЛЕ ВРЕМЕНИ (С ВЫХОДОМ НА СИМИСТОРЕ) | 1992 |

|

RU2130213C1 |

| Устройство для управления и защиты преобразователя | 1986 |

|

SU1403281A2 |

| СЕНСОР ДЛЯ ОБНАРУЖЕНИЯ ДВИЖУЩИХСЯ ОБЪЕКТОВ ПРИ ПОМОЩИ СВЕРХШИРОКОПОЛОСНОГО ЗОНДИРУЮЩЕГО СИГНАЛА (ВАРИАНТЫ) | 2006 |

|

RU2311658C9 |

| СТАБИЛИЗИРОВАННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ | 2014 |

|

RU2541519C1 |

| Устройство для управления высоковольтным силовым транзистором | 1991 |

|

SU1835118A3 |

| Аналоговое запоминающее устройство | 1978 |

|

SU771729A1 |

КОМПАРАТОР, содержащий усилитель, инвертирующий вход которого соединен с источником измеряемого напряжения, а неинвертирующий вход - с источником опорного напряжения, две блокирующие цепи и нагруэ ку,отличающийся тем, что, с целью повышения помехоустойчивости в широком диапазоне изменения частоты измеряемого сигнала, в нем каждая из блокирующих цепей содержит элемент И-НЕ, входы которого являются входаит блокирующей цепи, выход соединен через первый резистор с дифференцирующей RC -цепью выход которой подключен к базе транзистора, коллектор которого через второй резистор подключен непосредственно к входу первого элемента НЕ, выход которого является выходом блокируюспей цепи, и х третьему резистору и конденсатору, соединенным с общей шиной, а также дополнительно введены второй и третий элементы НЕ, четвертый и пятый резисторы и три .диода, причем выходы и первые входы первой и второй блокируквдих цепей пе рекрестно связаны, а выход усилителя непосредственно соединен с вторым входом второй блокирукхцей цепи и через второй элемент НЕ с вторым входом первой блокирующей цепи и (Л через четвертый резистор с нагрузкой и с катодом первого диода, анод которого соединен с общей шиной, катод второго диода подключен к выходу первой блокирующей -цепи, а анод - к нагрузке и к катоду третьего диода, анод которого соединен через пятый резистор с выходом третьего элемента НЕ, вход которого подключен СП к выходу второй блокируклцей цепи. СП

Авторы

Даты

1983-10-30—Публикация

1981-02-06—Подача