1

(21)4619569/21 (22) 14.12.88 (46)30.10.91. Бюл. №40

(71)Рязанский радиотехнический институт

(72)А.О Симкин (53)621.374(088.8)

(56)Авторское свидетельство СССР 600698, кл. Н 03 К 3/286, 1975.

Авторское свидетельство СССР N 1506545,кл. Н 03 К 23/00, 1988. (54) ПОМЕХОУСТОЙЧИВЫЙ ТРИГГЕР

(57)Изобретение относится к автоматике и телемеханике и может быть использовано для деления в два раза частоты следования импульсных сигналов со случайными моментами прихода и окончания с одновременным запоминанием бинарного состояния импульсного сигнала, а также для построения различных пересчетных и распределительных устройств, работающих в условиях действия интенсивных высокочастотных помех. Цель изобретения - расширение функциональных возможностей и повышение помехоустойчивости - достигается путем введения в каждое из плеч триггера управляемого фазоинвертора, компараторов, алгебраического сумматора, пассивной нелинейной интегрирующей RC-цепи, усилителя постоянного тока, элемента И-ИЛ И- НЕ, элемента И-НЕ, резисторов, ключевых элементов и преобразователей уровней. Устройство также содержит входную шину, вы- ходные шины, общую шину, элемент И-ИЛИ-НЕ и элемент И-НЕ. Помехоустойчивость повышается за счет нелинейного изменения параметров пассивных нелинейных интегрирующих RC-цепей плеч триггера, а расширение функциональных возможностей обусловлено наличием выходных сигналов триггера, изменяющихся как по положительным, так и по отрицательным фронтам входных импльсов. 1 з.п ф-лы, 6 ил.

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный время-импульсный интегрирующий преобразователь напряжения с четырьмя функциями широтно-импульсной модуляции | 2023 |

|

RU2822374C1 |

| Устройство для измерения перемещений | 1990 |

|

SU1758433A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПОДАЧЕЙ ТОПЛИВА В ДВИГАТЕЛЬ ВНУТРЕННЕГО СГОРАНИЯ | 1994 |

|

RU2107179C1 |

| Универсальный время-импульсный интегрирующий преобразователь напряжения с функцией широтно-импульсной модуляции | 2023 |

|

RU2819373C1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| ВРЕМЯ-ИМПУЛЬСНЫЙ УНИВЕРСАЛЬНЫЙ ИНТЕГРИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 2018 |

|

RU2689805C1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Стабилизированный источник постоянного напряжения | 1985 |

|

SU1309012A1 |

| Способ измерения периода непрерывного незашумленного аналогового сигнала, не имеющего постоянной составляющей | 1990 |

|

SU1762255A1 |

| Устройство для измерения действующего значения переменного напряжения | 1990 |

|

SU1712892A1 |

Изобретение относится к автоматике и телемеханике и может быть использовано для деления в два раза частоты следования импульсных сигналов со случайными моментами прохода и окончания с запоминанием бинарного состояния импульсного сигнала, а также для построения помехоустойчивой памяти различных пересчетных и распределительных устройств, работающих в условиях действия интенсивных высокочастотных помех.

Целью изобретения является расширение функциональных возможностей и повышение помехоустойчивости

Поставленная цель достигается за счет введения новых конструктивных признаков, обеспечивающих высокую помехоустойчивость нелинейным изменениям параметров пассивных нелинейных интегрирующих RC- цепей плеч триггера, а также обеспечивающих возможность получения выходных сигналов, изменяющихся как по положительным, так и по отрицательным фронтам входных импульсов.

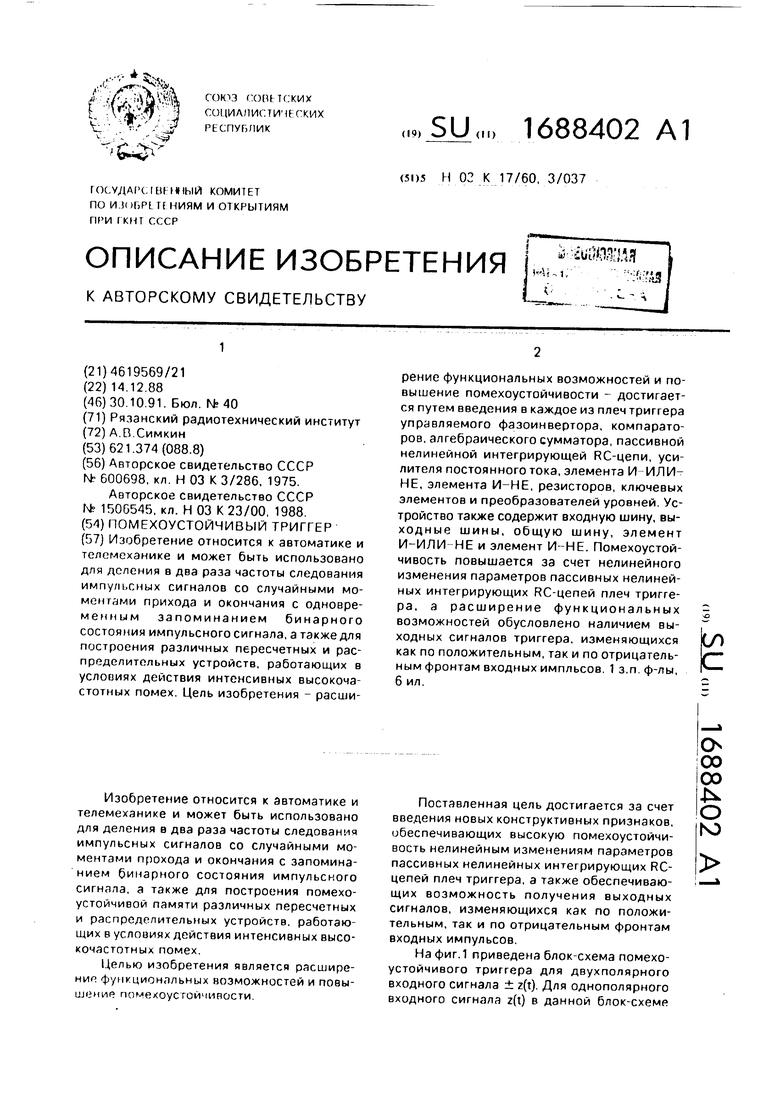

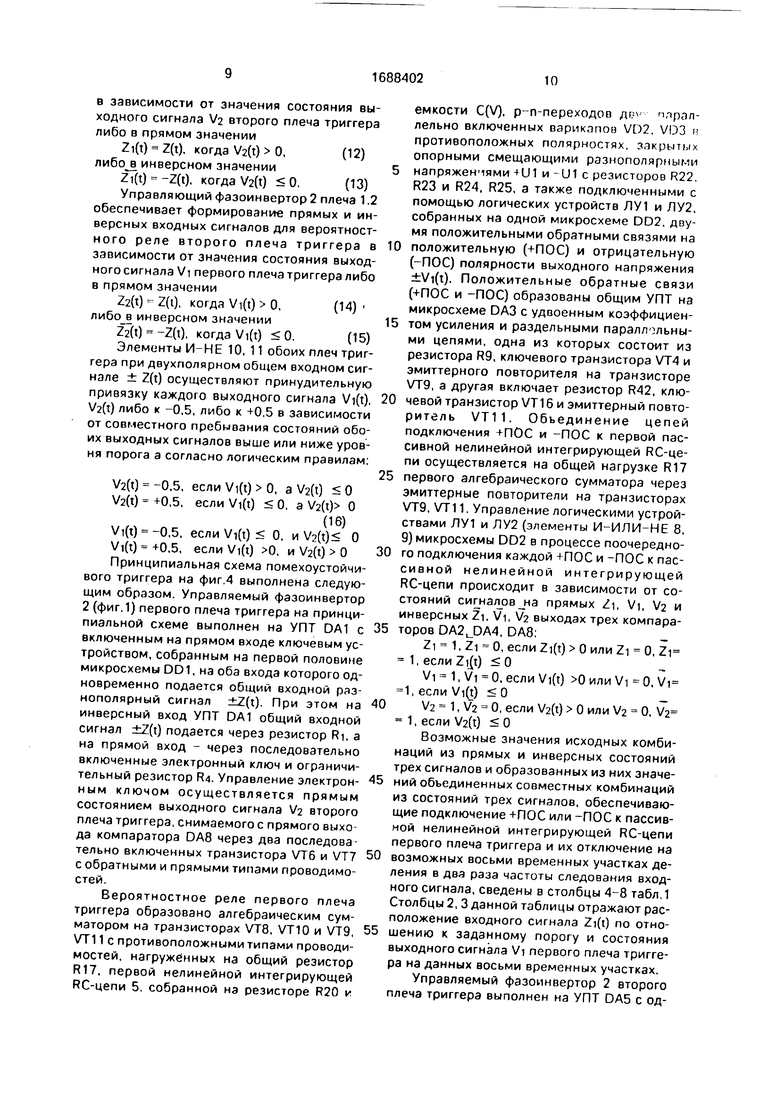

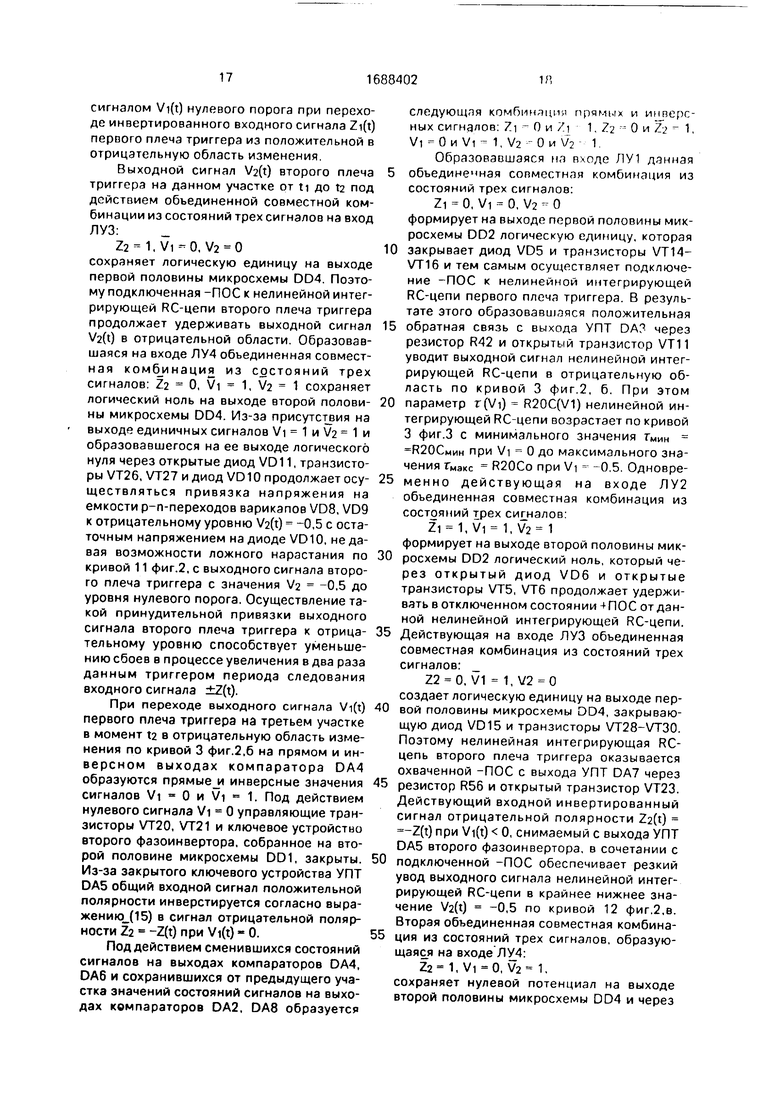

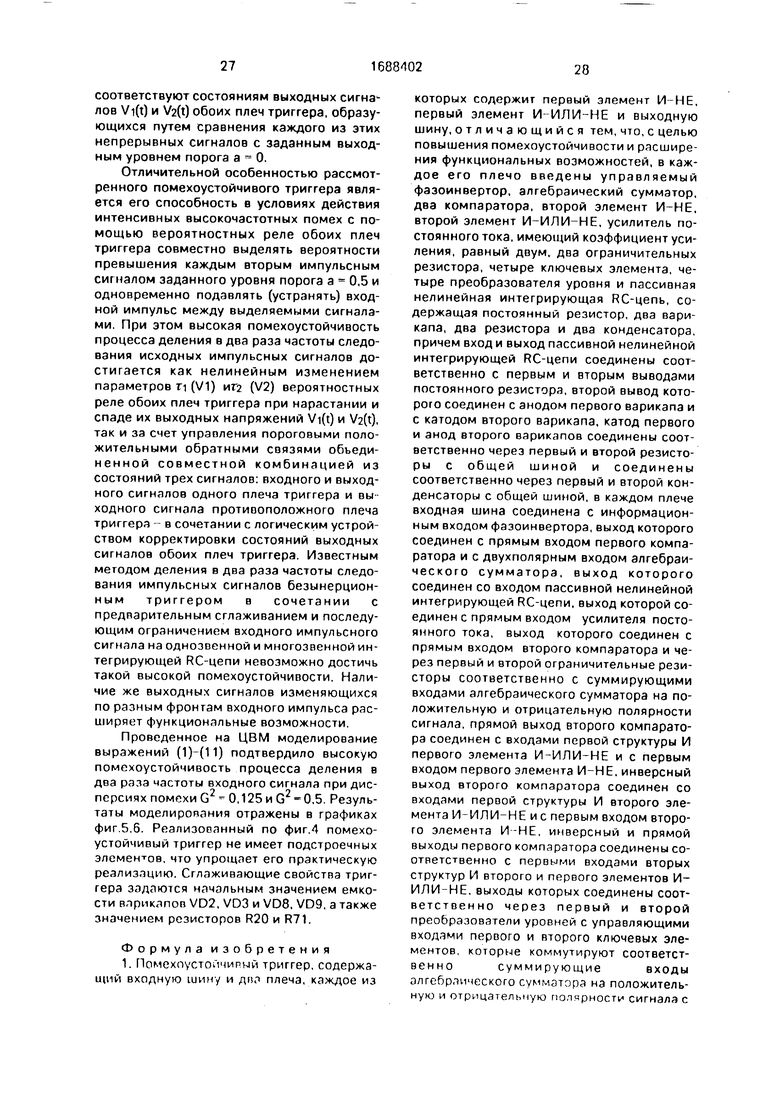

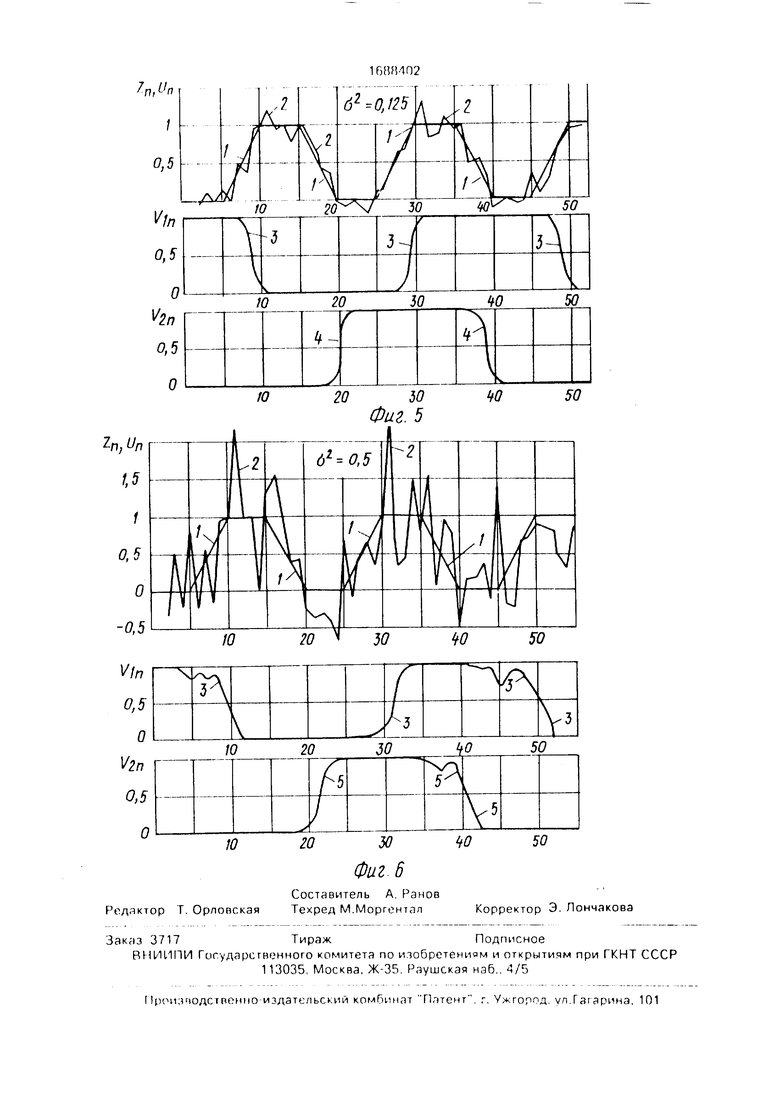

На фиг.1 приведена блок-схема помехоустойчивого триггера для двухполярного входного сигнала ± z(t). Для однополярного входного сигнала z(t) в данной блок-схеме

О оо оо

О N)

значение порога а 0,5 вычитается из общего входного сигнала Z(t) и добавляется к выходным сигналам Zi(t), Za(t) управляемых фазоинверторов обоих плеч триггера, такое же значение уровня порога а - 0,5 подается на инверсные входы первого и второго компараторов и вводятся смещающие положительные напряжения Ui 3 В, Ua 1 В на катод и анод варикапов пассивной нелинейной интегрирующей RC-цепи.

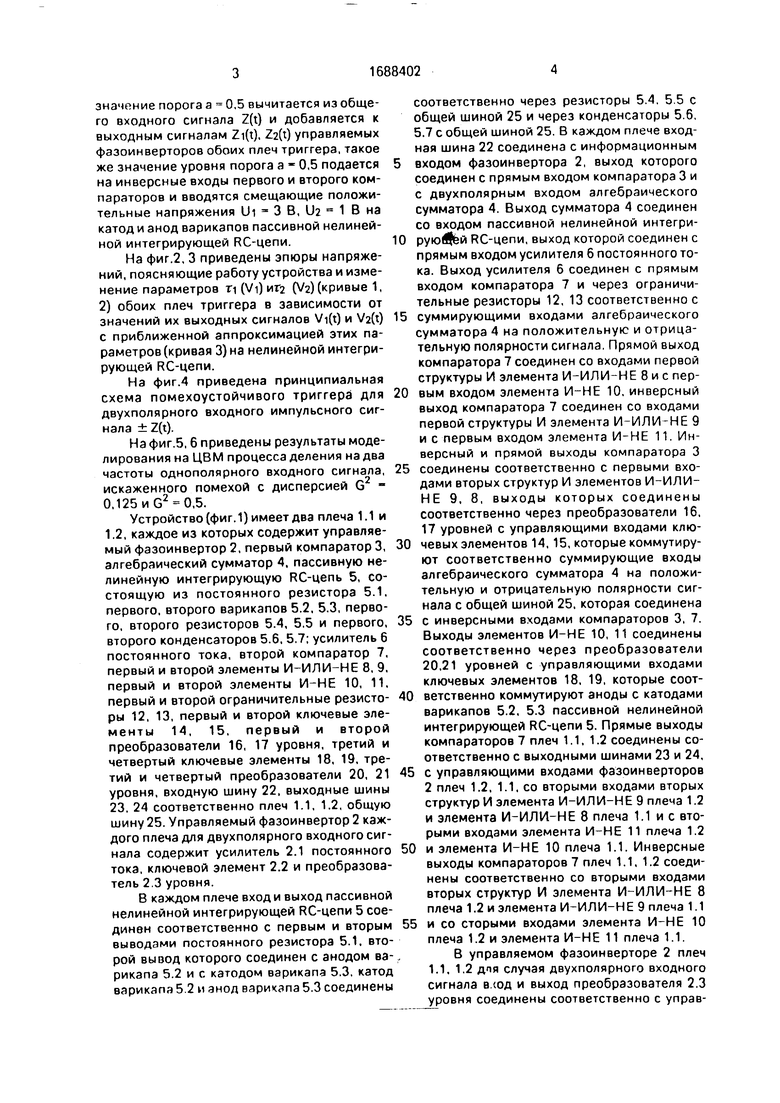

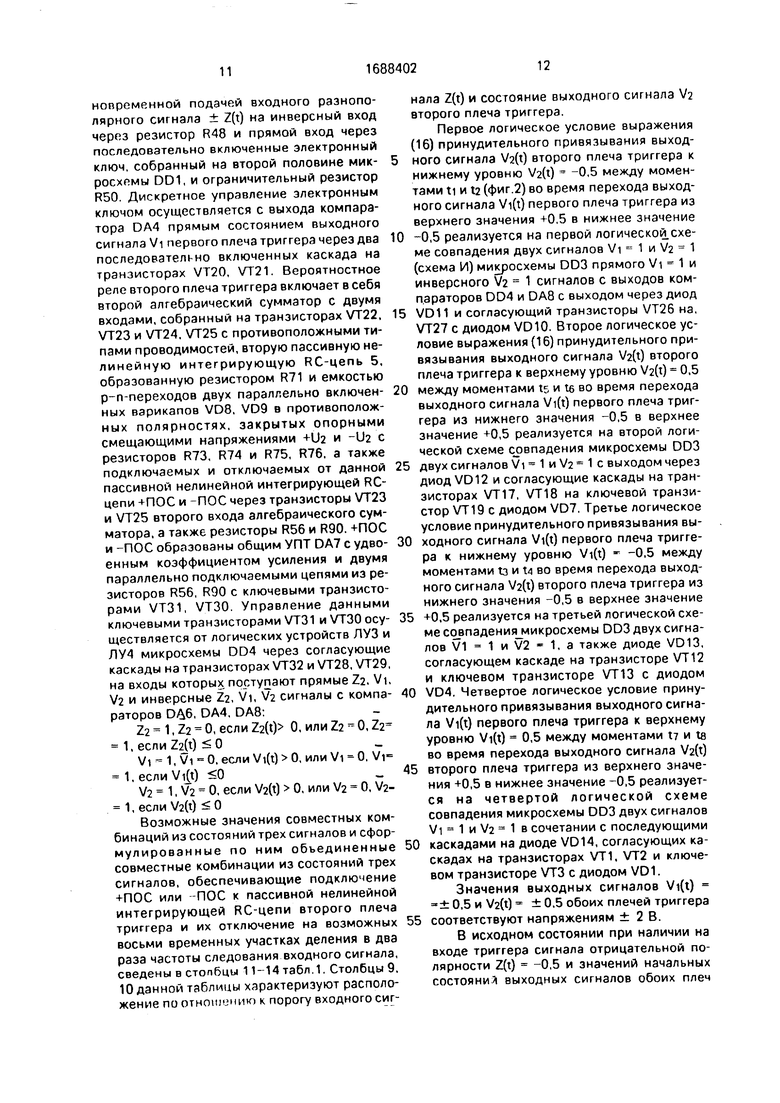

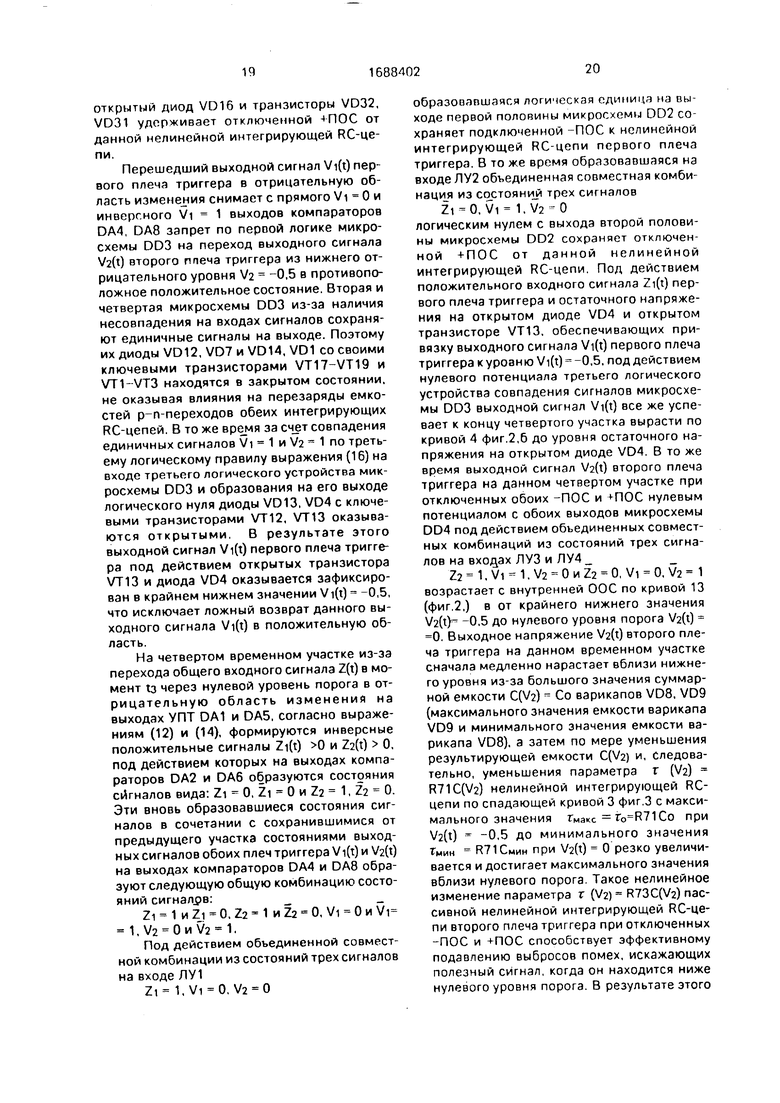

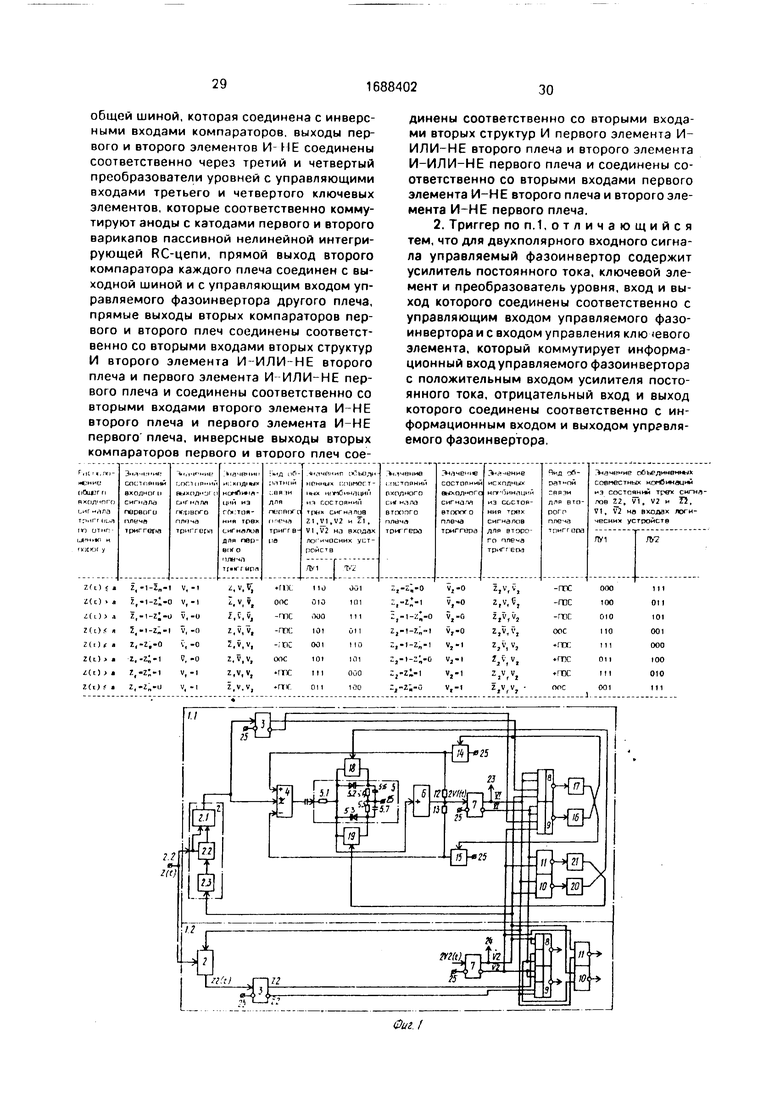

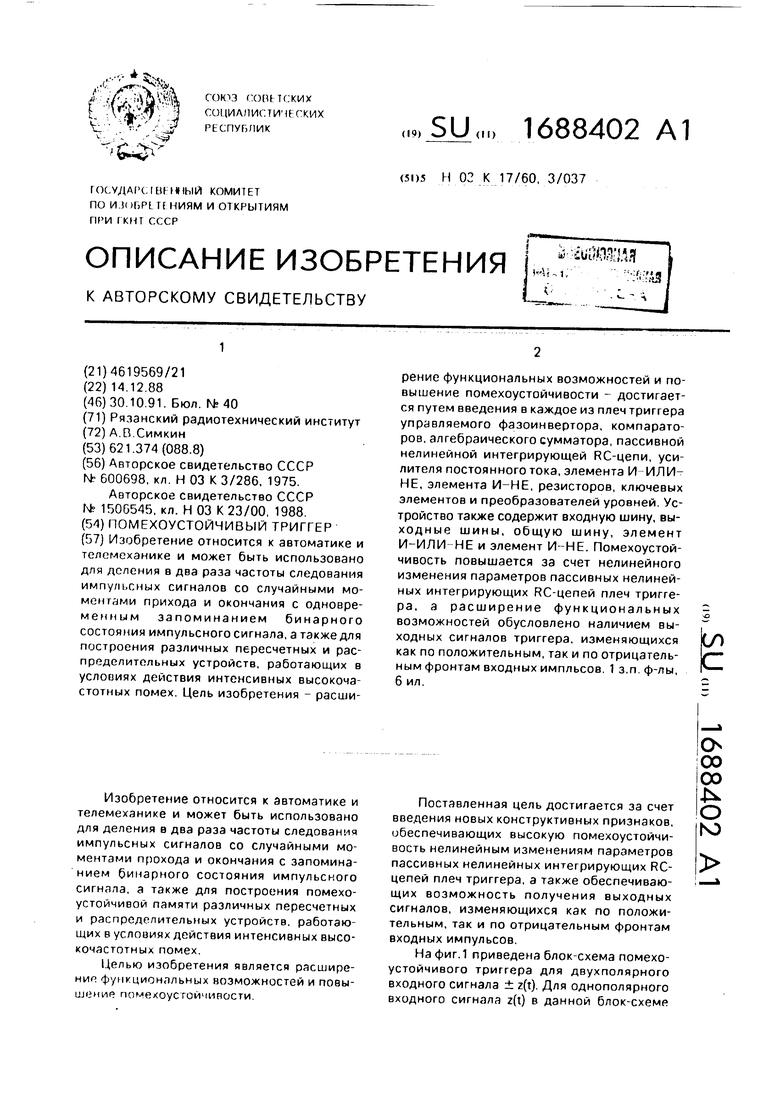

На фиг.2, 3 приведены эпюры напряжений, поясняющие работу устройства и изменение параметров TI (Vi) лтг (Лг) (кривые 1, 2) обоих плеч триггера в зависимости от значений их выходных сигналов Vi(t) и V2(t) с приближенной аппроксимацией этих параметров (кривая 3) на нелинейной интегрирующей RC-цепи.

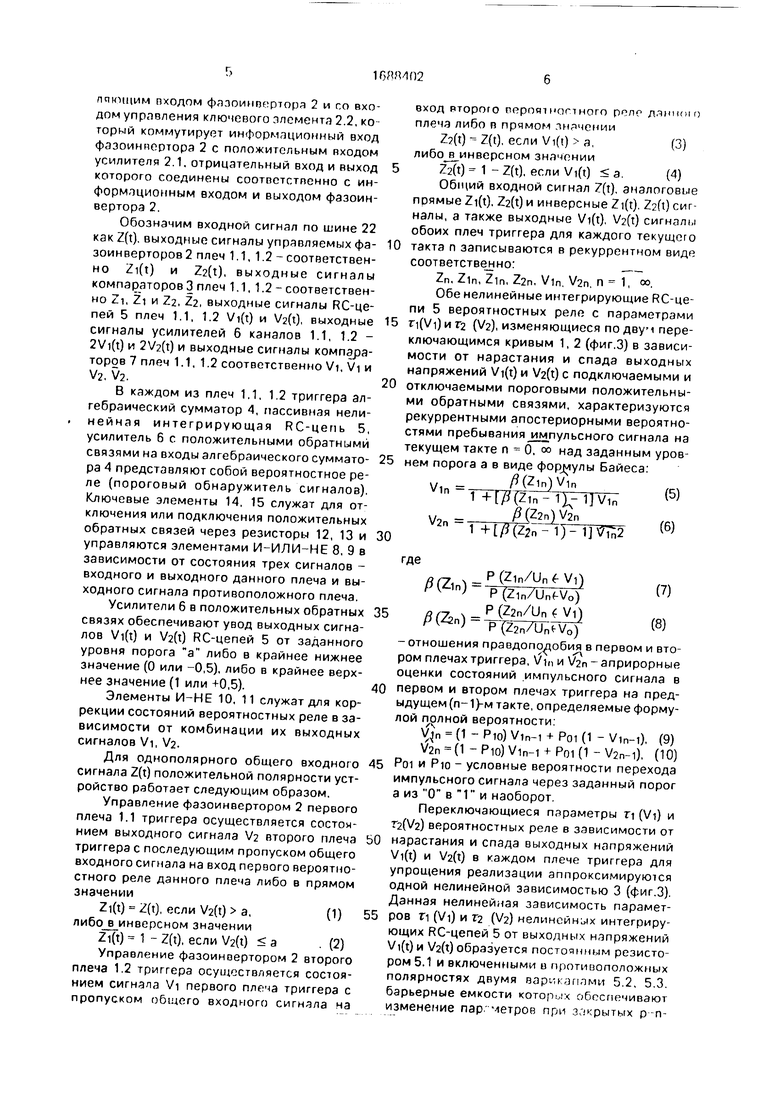

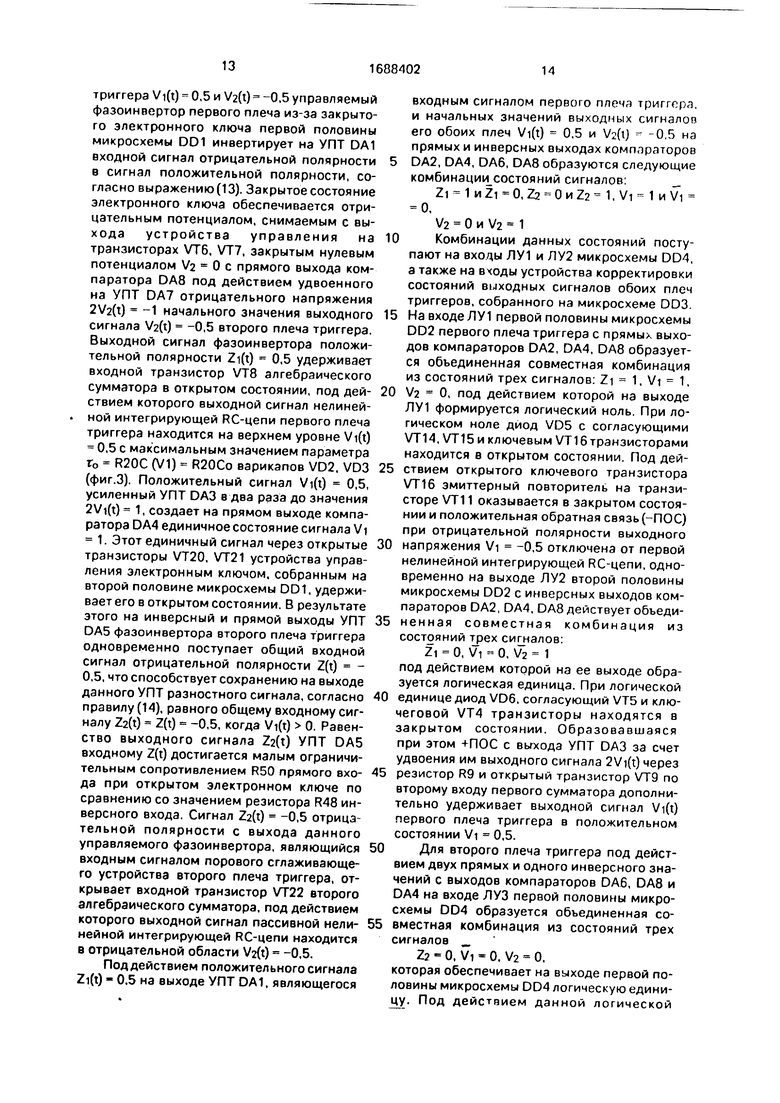

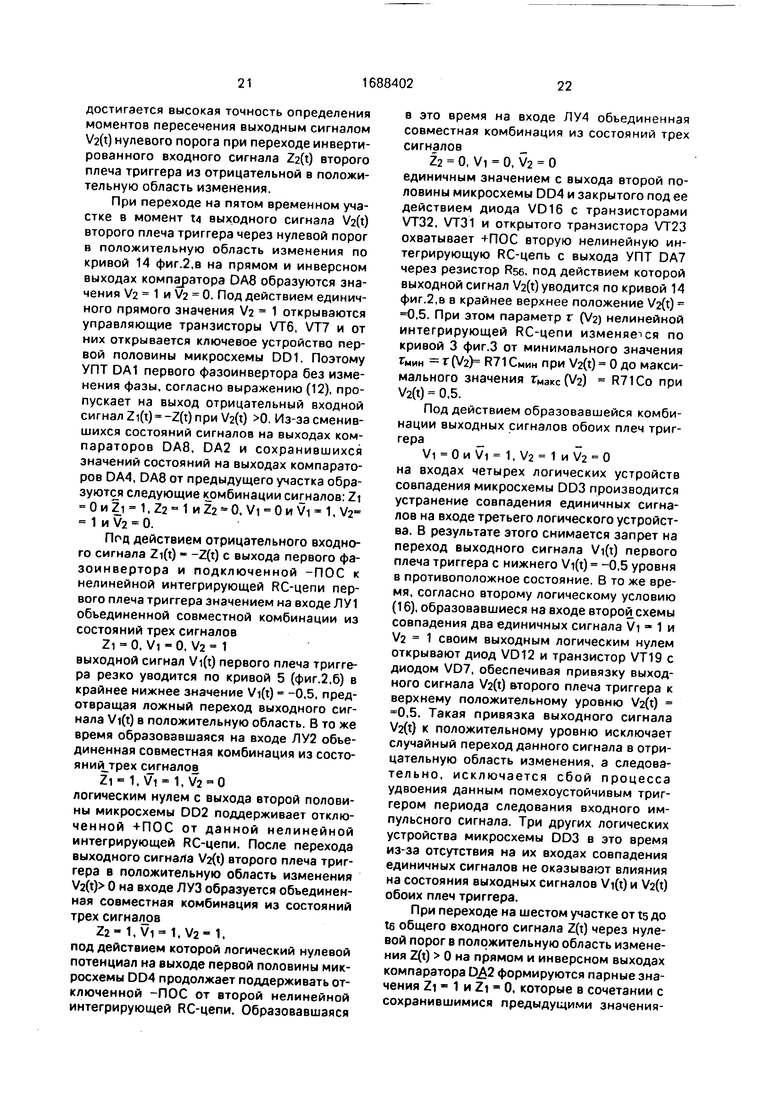

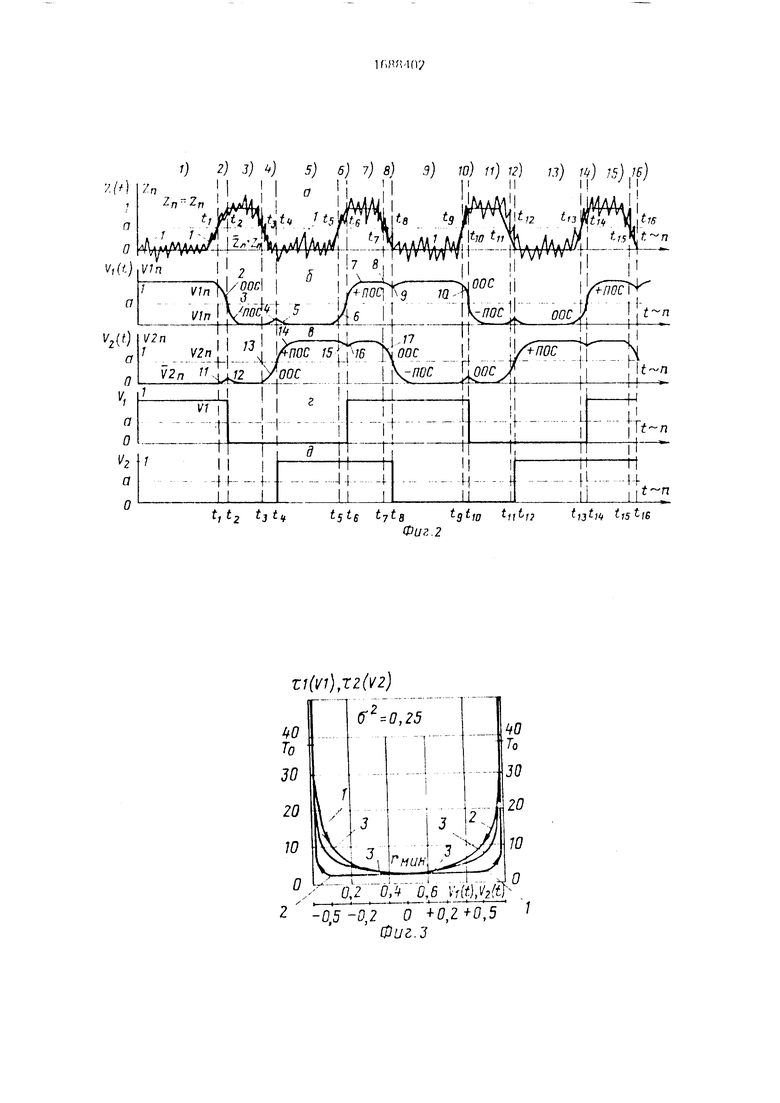

На фиг.4 приведена принципиальная схема помехоустойчивого триггера для двухполярного входного импульсного сигнала ± Z(t).

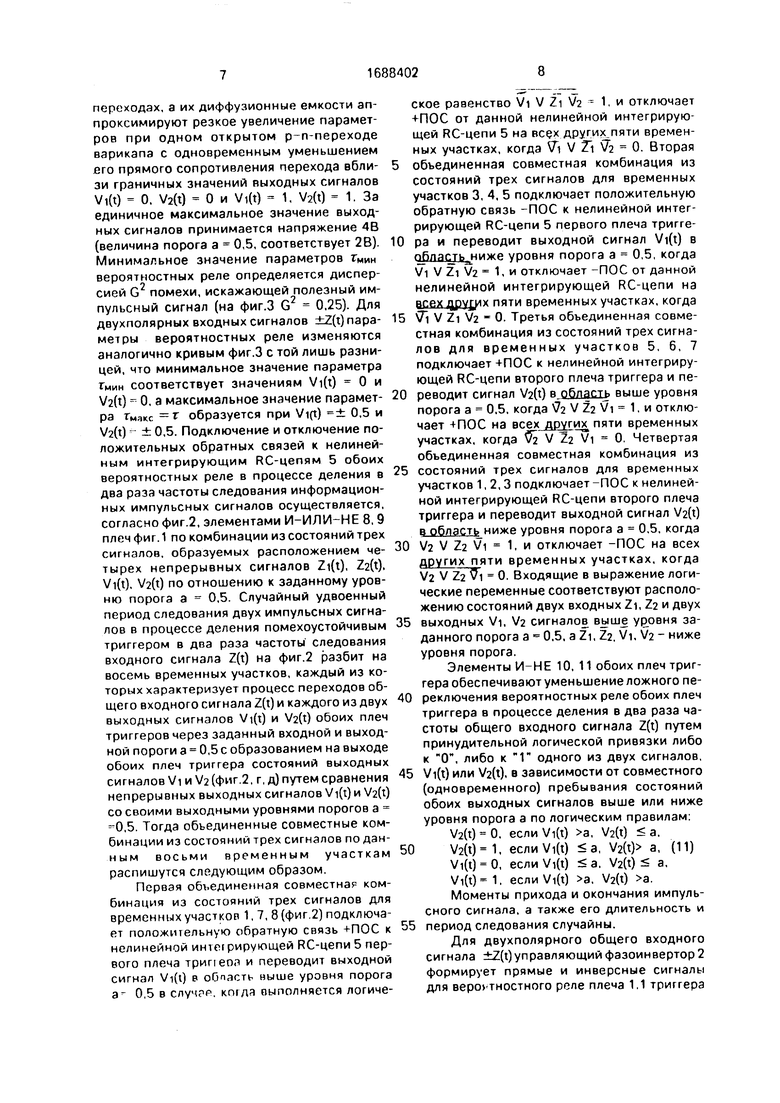

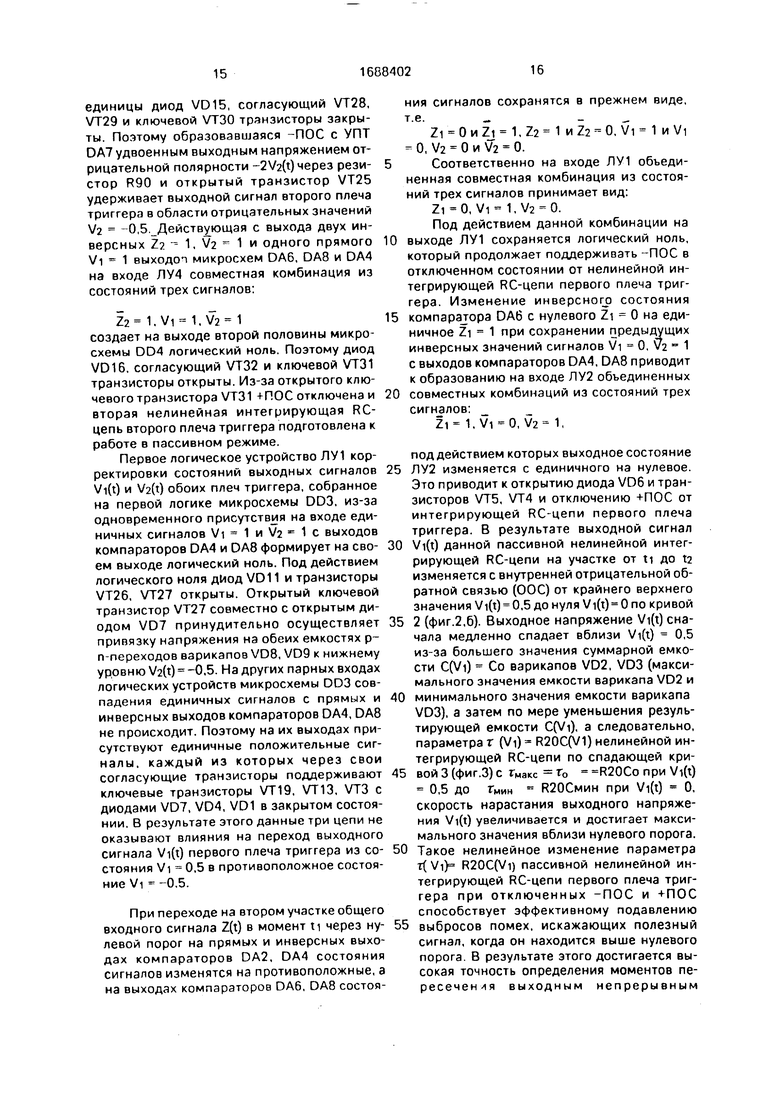

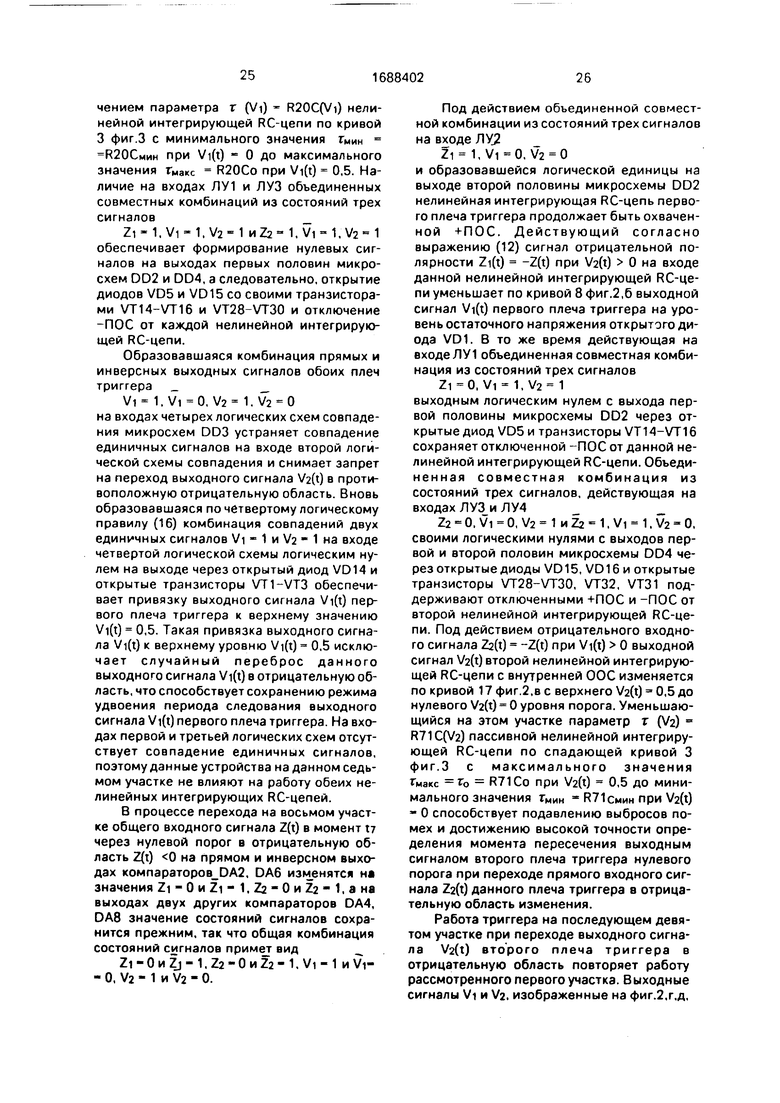

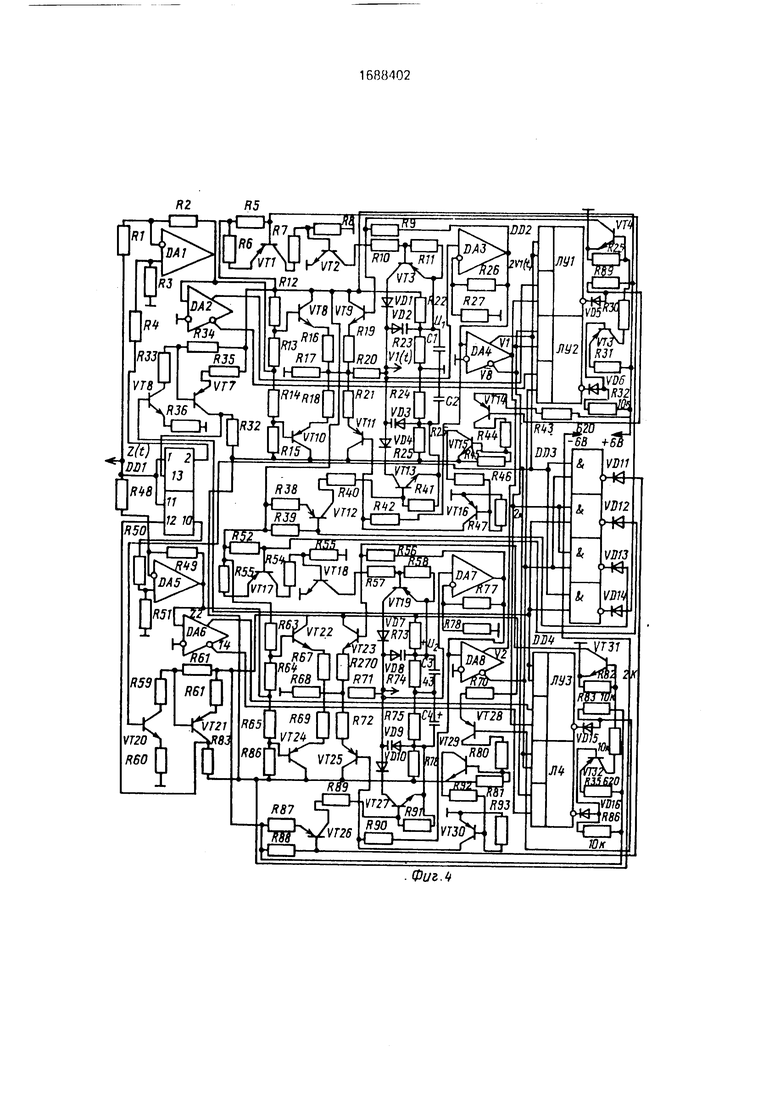

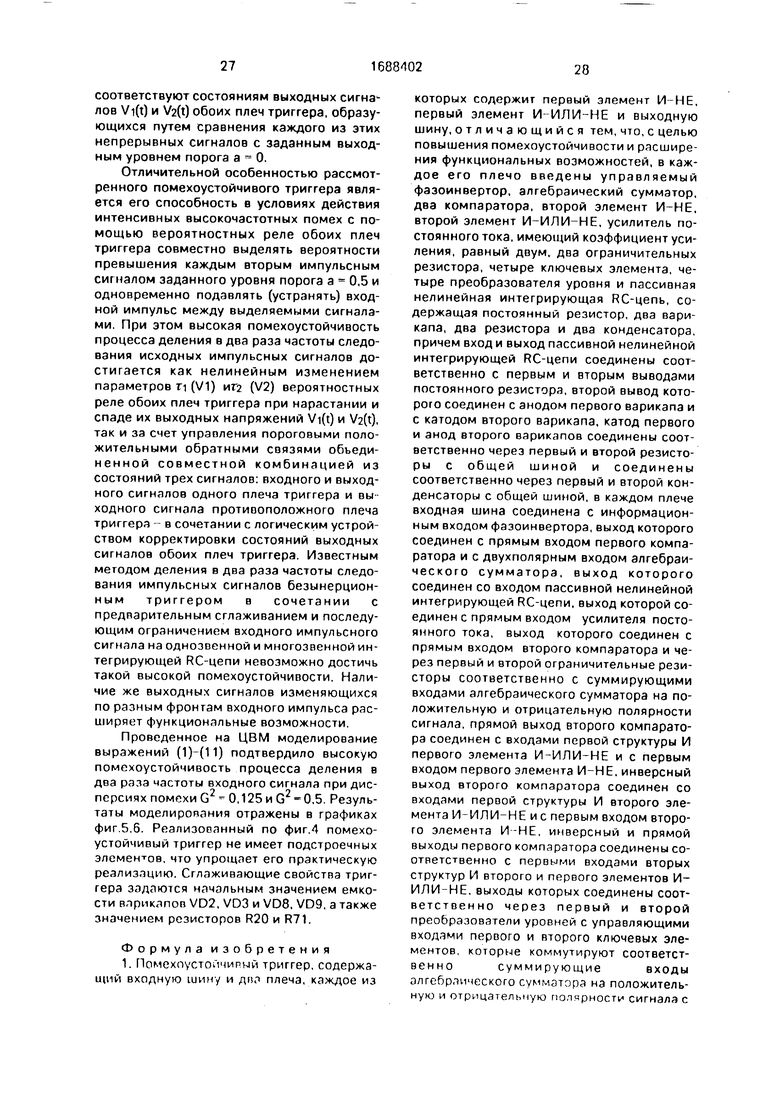

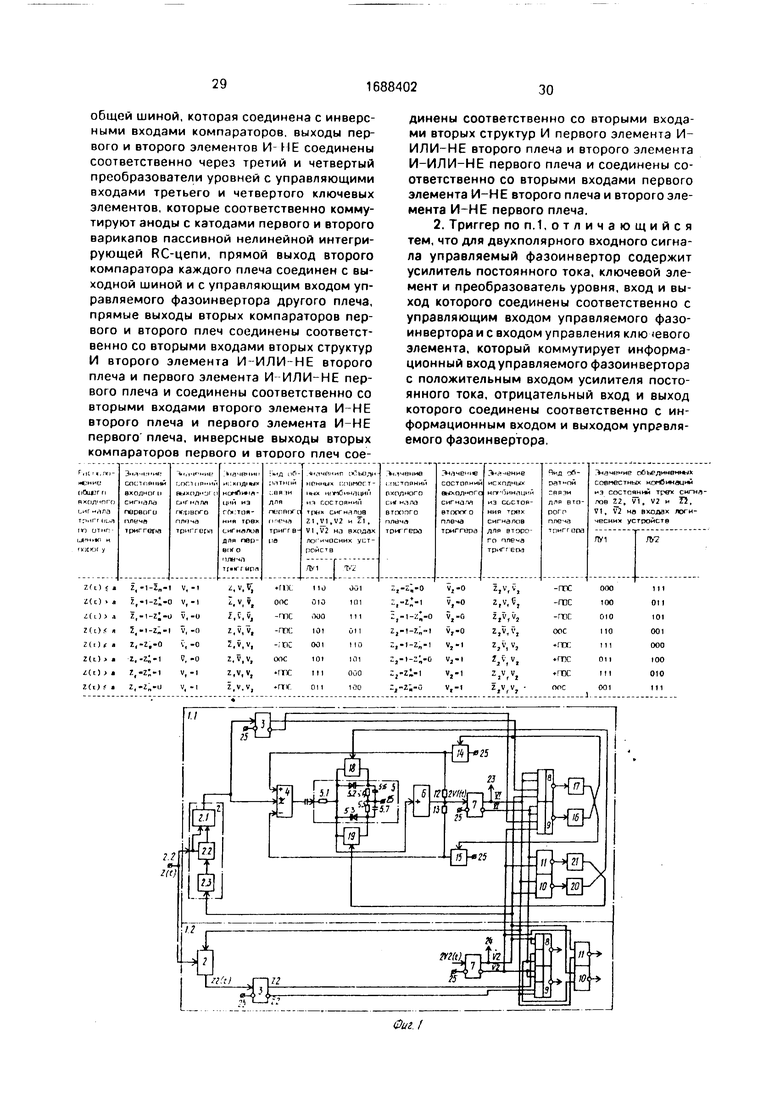

На фиг.5, 6 приведены результаты моделирования на ЦВМ процесса деления на два частоты однополярного входного сигнала, искаженного помехой с дисперсией G2 - 0,125 и G2 0,5.

Устройство (фиг. 1) имеет два плеча 1.1 и 1.2, каждое из которых содержит управляемый фазоинвертор 2, первый компаратор 3, алгебраический сумматор 4, пассивную нелинейную интегрирующую RC-цепь 5, состоящую из постоянного резистора 5.1, первого, второго варикапов 5.2. 5.3, первого, второго резисторов 5.4, 5.5 и первого, второго конденсаторов 5.6. 5.7; усилитель 6 постоянного тока, второй компаратор 7, первый и второй элементы И-ИЛИ-НЕ 8, 9, первый и второй элементы И-НЕ 10, 11, первый и второй ограничительные резисторы 12, 13, первый и второй ключевые элементы 14, 15, первый и второй преобразователи 16, 17 уровня, третий и четвертый ключевые элементы 18, 19, третий и четвертый преобразователи 20, 21 уровня, входную шину 22, выходные шины 23, 24 соответственно плеч 1.1, 1.2, общую шину 25. Управляемый фазоинвертор 2 каждого плеча для двухполярного входного сигнала содержит усилитель 2.1 постоянного тока, ключевой элемент 2.2 и преобразователь 2.3 уровня.

В каждом плече входи выход пассивной нелинейной интегрирующей RC-цепи 5 соединен соответственно с первым и вторым выводами постоянного резистора 5.1, второй вывод которого соединен с анодом варикапа 5.2 и с катодом варикапа 5.3, катод варикапа 5.2 и анод варикапа 5.3 соединены

соответственно через резисторы 5.4, 5.5 с общей шиной 25 и через конденсаторы 5.6, 5.7 с общей шиной 25. В каждом плече входная шина 22 соединена с информационным

входом фазоинвертора 2, выход которого соединен с прямым входом компаратора 3 и с двухполярным входом алгебраического сумматора 4. Выход сумматора 4 соединен со входом пассивной нелинейной интегри0 RC-цепи, выход которой соединен с прямым входом усилителя 6 постоянного тока. Выход усилителя 6 соединен с прямым входом компаратора 7 и через ограничительные резисторы 12, 13 соответственно с

5 суммирующими входами алгебраического сумматора 4 на положительную и отрицательную полярности сигнала. Прямой выход компаратора 7 соединен со входами первой структуры И элемента И-ИЛИ-НЕ 8 и с пер0 вым входом элемента И-НЕ 10, инверсный выход компаратора 7 соединен со входами первой структуры И элемента И-ИЛИ-НЕ 9 и с первым входом элемента И-НЕ 11. Инверсный и прямой выходы компаратора 3

5 соединены соответственно с первыми входами вторых структур И элементов И-ИЛИ- НЕ 9. 8, выходы которых соединены соответственно через преобразователи 16, 17 уровней с управляющими входами клю0 чевых элементов 14,15, которые коммутируют соответственно суммирующие входы алгебраического сумматора 4 на положительную и отрицательную полярности сигнала с общей шиной 25. которая соединена

5 с инверсными входами компараторов 3, 7. Выходы элементов И-НЕ 10, 11 соединены соответственно через преобразователи 20.21 уровней с управляющими входами ключевых элементов 18, 19, которые соот0 ветственно коммутируют аноды с катодами варикапов 5.2, 5.3 пассивной нелинейной интегрирующей RC-цепи 5. Прямые выходы компараторов 7 плеч 1.1, 1.2 соединены соответственно с выходными шинами 23 и 24,

5 с управляющими входами фазоинверторов 2 плеч 1.2, 1.1. со вторыми входами вторых структур И элемента И-ИЛИ-НЕ 9 плеча 1.2 и элемента И-ИЛИ-НЕ 8 плеча 1.1 и с вторыми входами элемента И-НЕ 11 плеча 1.2

0 и элемента И-НЕ 10 плеча 1.1. Инверсные выходы компараторов 7 плеч 1.1, 1.2 соединены соответственно со вторыми входами вторых структур И элемента И-ИЛИ-НЕ 8 плеча 1.2 и элемента И-ИЛИ-НЕ 9 плеча 1.1

5 и со сторыми входами элемента И-НЕ 10 плеча 1.2 и элемента И-НЕ 11 плеча 1.1.

В управляемом фазоинверторе 2 плеч 1.1. 1.2 дня случая двухполярного входного сигнала в.юд и выход преобразователя 2.3 уровня соединены соответственно с управлпющим входом фазоинвертора 2 и со входом управления ключевого элемента 2.2, ко торый коммутирует информационный вход фазоиннертора 2 с положительным входом усилителя 2.1, отрицательный вход и выход которого соединены соответственно с информационным входом и выходом фазоин- вертора 2.

Обозначим входной сигнал по шине 22 как Z(t). выходные сигналы управляемых фа- зоинверторов2 плеч 1.1, 1.2 -соответственно Zi(t) и Z2(t), выходные сигналы компараторов 3 плеч 1.1, 1.2 - соответственно Zi, Zi и Z2, Z2, выходные сигналы RC-це- пей 5 плеч 1.1, 1.2 Vi(t) и V2(t), выходные сигналы усилителей б каналов 1.1, 1.2 - 2Vi(t) и 2V2(t) и выходные сигналы компараторов 7 плеч 1.1, 1.2 соответственно Vi, Vi и V2, V2.

В каждом из плеч 1.1, 1.2 триггера алгебраический сумматор 4, пассивная нелинейная интегрирующая RC-цепь 5, усилитель 6 с положительными обратными связями на входы алгебраического сумматора 4 представляют собой вероятностное реле (пороговый обнаружитель сигналов). Ключевые элементы 14, 15 служат для отключения или подключения положительных обратных связей через резисторы 12, 13 и управляются элементами И-ИЛИ-НЕ 8, 9 в зависимости от состояния трех сигналов - входного и выходного данного плеча и выходного сигнала противоположного плеча.

Усилители 6 в положительных обратных связях обеспечивают увод выходных сигналов Vi(t) и V2(t) RC-цепей 5 от заданного уровня порога а либо в крайнее нижнее значение (0 или -0,5), либо в крайнее верхнее значение (1 или +0,5).

Элементы И-НЕ 10, 11 служат для коррекции состояний вероятностных реле в зависимости от комбинации их выходных сигналов Vi, V2.

Для однополярного общего входного сигнала Z(t) положительной полярности устройство работает следующим образом.

Управление фазоинвертором 2 первого плеча 1.1 триггера осуществляется состоянием выходного сигнала V2 второго плеча триггера с последующим пропуском общего входного сигнала на вход первого вероятностного реле данного плеча либо в прямом значении

Zi(t) 2(t), если V2(t) a.(1)

либо в инверсном значении

Zi(t) - 1 - 2(1), если V2(t) а. (2)

Управление фазоиноертором 2 второго плеча 1.2 триггера осуществляется состоянием сигнала Vi первого плеча триггера с пропуском общего входного сигнала на

вход второго перпятмппного реле данною плеча либо в прямом значении

Z(t) Z(t), если Vi(i)a,(3)

либо в инверсном значении Z2(t) 1 - Z(t), если Vi(t) a.(4)

Общий входной сигнал Z(t), аналоговые прямые Zi(t), Z2(t) и инверсные Zi(t). Z2(t) сигналы, а также выходные Vi(t), V2(t) сигналы обоих плеч триггера для каждого текущего такта п записываются в рекуррентном виде

соответственно:

Zn. Zin, Zin, Z2n- Vin, V2n. n 1, оз. Обе нелинейные интегрирующие RC-це- пи 5 вероятностных реле с параметрами T(l) (V2), изменяющиеся по двум переключающимся кривым 1, 2 (фиг.З) в зависимости от нарастания и спада выходных напряжений Vi(t) и V2(t) с подключаемыми и отключаемыми пороговыми положительными обратными связями, характеризуются рекуррентными апостериорными вероятностями пребывания импульсного сигнала на текущем такте п 0, °° над заданным уров- нем порога а в виде формулы Байеса:

/(Zin)Vln

Vlf1 1 + 0(Zln-1b1 Vm

(

i (zm- i)-i№2

(5)

(6)

где

ЙГ7 P (Zm/Un f Vi)

1n) P (Zm/Unf-V &

5 Л,Л-Р 2п/ип 1)(8)

P(Z2n P(Z2n/Un(-V0)(Щ

-отношения правдоподобия в первом и втором плечах триггера, Vin и V2n - априрорные оценки состояний .импульсного сигнала в

0 первом и втором плечах триггера на пред- ыдущем(п-1)-м такте, определяемые формулой полной вероятности.

VJn (1 - Рю) Vin-1 + Poi (1 - Vm-i). (9) V2n (1 - Рю) Vm-i + Poi (1 - V2n-i). (Ю)

5 POI и Рю - условные вероятности перехода импульсного сигнала через заданный порог а из О в 1 и наоборот.

Переключающиеся параметры ri (Vi) и T2(V2) вероятностных реле в зависимости от

О нарастания и спада выходных напряжений Vi(t) и V2(t) в каждом плече триггера для упрощения реализации аппроксимируются одной нелинейной зависимостью 3 (фиг.З). Данная нелинейная зависимость парамет5 ров Г1 (Vi) и Г2 (V2) нелинейных интегрирующих RC-цепей 5 от выходных напряжений Vi(t)n V2(t) образуется постоянным резистором 5.1 и включенными в противоположных полярностях двумя варикапами 5.2. 5.3. барьерные емкости которых обеспечивают изменение пар: метров при закрытых р-ппереходах, а их диффузионные емкости аппроксимируют резкое увеличение параметров при одном открытом р-п-переходе варикапа с одновременным уменьшением его прямого сопротивления перехода вблизи граничных значений выходных сигналов Vi(t) 0. V2(t) 0 и Vi(t) 1, V2(t) 1. За единичное максимальное значение выходных сигналов принимается напряжение 4В (величина порога а 0,5, соответствует 2В). Минимальное значение параметров гмин вероятностных реле определяется дисперсией G помехи, искажающей полезный импульсный сигнал (на фиг.З G2 0,25). Для двухполярных входных сигналов ±2(t) параметры вероятностных реле изменяются аналогично кривым фиг.З с той лишь разницей, что минимальное значение параметра Гмин соответствует значениям Vi(t) 0 и V2(t) 0, а максимальное значение параметра Тмзкс т образуется при Vi(t) ± 0,5 и V2(t) - ± 0,5. Подключение и отключение положительных обратных связей к нелинейным интегрирующим RC-цепям 5 обоих вероятностных реле в процессе деления в два раза частоты следования информационных импульсных сигналов осуществляется, согласно фиг.2, элементами И-ИЛИ-НЕ 8, 9 плеч фиг. 1 по комбинации из состояний трех сигналов, образуемых расположением четырех непрерывных сигналов Zi(t), Z2(t), Vi(t), V2(t) no отношению к заданному уровню порога а 0,5. Случайный удвоенный период следования двух импульсных сигналов в процессе деления помехоустойчивым триггером в два раза частоты следования входного сигнала Z(t) на фиг.2 разбит на восемь временных участков, каждый из которых характеризует процесс переходов общего входного сигнала Z(t) и каждого из двух выходных сигналов Vi(t) и V2(t) обоих плеч триггеров через заданный входной и выходной пороги а 0,5 с образованием на выходе обоих плеч триггера состояний выходных сигналов Vi и /2(фиг.2, г, д) путем сравнения непрерывных выходных сигналов Vi(t) и V2(t) со своими выходными уровнями порогов а -0,5. Тогда объединенные совместные комбинации из состояний трех сигналов по дан- ным восьми временным участкам распишутся следующим образом.

Первая объединенная совместная комбинация из состояний трех сигналов для временных участков 1,7,8 (фиг.2) подключает положительную обратную связь +ПОС к нелинейной нитрирующей RC-цепи 5 первого плеча трипеол и переводит выходной сигнал Vi(t) в область выше уровня порога а- 0,5 в . когда выполняется логическое равенство Vi V Zi V2 - 1, и отключает +ПОС от данной нелинейной интегрирующей RC-цепи 5 на всех других пяти временных участках, когда Vi V Zi V2 0. Вторая

объединенная совместная комбинация из состояний трех сигналов для временных участков 3, 4, 5 подключает положительную обратную связь -ПОС к нелинейной интегрирующей RC-цепи 5 первого плеча триггера и переводит выходной сигнал Vi(t) в область ниже уровня порога а 0,5, когда Vi V Zi V2 1, и отключает -ПОС от данной нелинейной интегрирующей RC-цепи на всех Jjyjj/ix пяти временных участках, когда

V Zi V2 - 0. Третья объединенная совместная комбинация из состояний трех сигналов для временных участков 5, 6, 7 подключает +ПОС к нелинейной интегрирующей RC-цепи второго плеча триггера и переводит сигнал V2(t) в область выше уровня порога а 0,5. когда V2 V Z2 Vi 1, и отключает +ПОС на всех других пяти временных участках, когда 0 V Z2 Vi 0. Четвертая объединенная совместная комбинация из

состояний трех сигналов для временных участков 1,2,3 подключает -ПОС к нелинейной интегрирующей RC-цепи второго плеча триггера и переводит выходной сигнал V2(t) в область ниже уровня порога а 0,5, когда

V2 V Z2 Vi 1, и отключает -ПОС на всех других пяти временных участках, когда V2 V Z2 9i 0. Входящие в выражение логические переменные соответствуют расположению состояний двух входных Zi, Z2 и двух

выходных VL V2 сигналов уровня заданного порога а 0,5. a Zi, Z2. Vi, V2 - ниже уровня порога.

Элементы И-НЕ 10, 11 обоих плеч триггера обеспечивают уменьшение ложного переключения вероятностных реле обоих плеч триггера в процессе деления в два раза частоты общего входного сигнала Z(t) путем принудительной логической привязки либо к О, либо к 1 одного из двух сигналов,

Vi(t) или V2(t), в зависимости от совместного (одновременного) пребывания состояний обоих выходных сигналов выше или ниже уровня порога а по логическим правилам: V2(t) 0. если Vi(t) a, V2(t) a.

V2(t)1, ecflnVi(t) a, V2(t) a, (11) Vi(t) - 0, если Vi(t) a, V2(t) a, Vi(t)- 1, если Vi(t) a, V2(t) a. Моменты прихода и окончания импульсного сигнала, а также его длительность и

период следования случайны.

Для двухполярного общего входного сигнала :(1)управляющийфэзоинвертор2 формирует прямые и инверсные сигналы для веро тностного реле плеча 1.1 триггера

в зависимости от значения состояния выходного сигнала V2 второго плеча триггера либо в прямом значении

Zi(t) Z(t). когда V2(t) 0,(12)

либол инверсном значении

Zi(t) -Z(t), когда V2(t) 0.(13)

Управляющий фазоинвертор 2 плеча 1.2 обеспечивает формирование прямых и инверсных входных сигналов для вероятностного реле второго плеча триггера в зависимости от значения состояния выходного сигнала Vi первого плеча триггера либо в прямом значении

Z2(t)-Z(t). когда Vi(t) 0,(14)

инверсном значении

Z2(t) Z(t), когда Vi(t) 0.(15)

Элементы И-НЕ 10. 11 обоих плеч триггера при двухполярном общем входном сигнале ± Z(t) осуществляют принудительную привязку каждого выходного сигнала Vi(t), V2(t) либо к -0,5, либо к +0,5 в зависимости от совместного пребывания состояний обоих выходных сигналов выше или ниже уровня порога а согласно логическим правилам:

V2(t) -0.5, если Vi(t) 0, a V2(t) О V2(t) +0.5, если Vi(t) 0, a V2(t) О

(16)

Vi(t) - -0,5, если Vi(t) 0. и V2(t) О Vi(t) +0,5, если Vi(t) 0, и V2(t) О Принципиальная схема помехоустойчивого триггера на фиг.4 выполнена следующим образом. Управляемый фазоинвертор 2 (фиг.1) первого плеча триггера на принципиальной схеме выполнен на УПТ DA1 с включенным на прямом входе ключевым устройством, собранным на первой половине микросхемы DD1, на оба входа которого одновременно подается общий входной раз- нополярный сигнал ±Z(t). При этом на инверсный вход УПТ DA1 общий входной сигнал ±Z(t) подается через резистор RL а на прямой вход - через последовательно включенные электронный ключ и ограничительный резистор R4. Управление электрон- ным ключом осуществляется прямым состоянием выходного сигнала V2 второго плеча триггера, снимаемого с прямого выхода компаратора DA8 через два последовательно включенных транзистора VT6 и VT7 с обратными и прямыми типами проводимо- стей.

Вероятностное реле первого плеча триггера образовано алгебраическим сумматором на транзисторах VT8, VT10 и VT9, VT11 с противоположнымитипами проводи- мостей, нагруженных на общий резистор R17, первой нелинейной интегрирующей RC-цепи 5, собранной на резисторе R20 v

емкости C(V). p-n-переходов параллельно включенных варикапоа VD2. VD3 с противоположных полярностях, закрытых опорными смещающими разнополярными 5 напряжениями +U1и-U1с резисторов R22, R23 и R24, R25, а также подключенными с помощью логических устройств ЛУ1 и ЛУ2, собранных на одной микросхеме DD2, двумя положительными обратными связями на 0 положительную (+ПОС) и отрицательную (-ПОС) полярности выходного напряжения ±Vi(t). Положительные обратные связи (+ПОС и -ПОС) образованы общим УПТ на микросхеме DA3 с удвоенным коэффициен5 том усиления и раздельными параллельными цепями, одна из которых состоит из резистора R9, ключевого транзистора VT4 и эмиттерного повторителя на транзисторе VT9, а другая включает резистор R42, клю0 чевой транзистор VT16 и эмиттерный повторитель VT11. Объединение цепей подключения +ПОС и -ПОС к первой пассивной нелинейной интегрирующей RC-цепи осуществляется на общей нагрузке R17

5 первого алгебраического сумматора через эмиттерные повторители на транзисторах VT9, VT11. Управление логическими устройствами ЛУ1 и ЛУ2 (элементы И-ИЛИ-НЕ 8, 9) микросхемы DD2 в процессе поочередно0 го подключения каждой +ПОС и -ПОС к пассивной нелинейной интегрирующей RC-цепи происходит в зависимости от состояний сигналрв на прямых Zi, Vi, V2 и инверсных Zi, Vi, V2 выходах трех компара5 торов DA2J3A4, DA8:

Zi 1. Zi 0, если Zi(t) 0 или Zi 0, Zi 1, еслиг т.) 0

Vi 1, Vi 0. если Vi(t) 0 или Vi 0, Vi 1, если Vi(t) 0

0 Mi 1, V2 0, если V2(t) 0 или V2 О, V2 1, если V2(t) 0

Возможные значения исходных комбинаций из прямых и инверсных состояний трех сигналов и образованных из них значе5 ний объединенных совместных комбинаций из состояний трех сигналов, обеспечивающие подключение +ПОС или -ПОС к пассивной нелинейной интегрирующей RC-цепи первого плеча триггера и их отключение на

0 возможных восьми временных участках деления в два раза частоты следования входного сигнала, сведены в столбцы 4-8 табл.1 Столбцы 2, 3 данной таблицы отражают расположение входного сигнала Zi(t) по отно5 шению к заданному порогу и состояния выходного сигнала Vi первого плеча триггера на данных восьми временных участках.

Управляемый фазоинвертор 2 второго плеча триггера выполнен на УПТ DA5 с однепременной подачей входного разнопо- лярного сигнала ± Z(t) на инверсный вход через резистор R48 и прямой вход через последовательно включенные электронный ключ, собранный на второй половине микросхемы DD1, и ограничительный резистор R50. Дискретное управление электронным ключом осуществляется с выхода компаратора DA4 прямым состоянием выходного сигнала Vi первого плеча триггера через два последовательно включенных каскада на транзисторах VT20, VT21. Вероятностное реле второго плеча триггера включает в себя второй алгебраический сумматор с двумя входами, собранный на транзисторах VT22, VT23 и VT24, VT25 с противоположными типами проводимостей, вторую пассивную нелинейную интегрирующую RC-цепь 5, образованную резистором R71 и емкостью p-n-переходов двух параллельно включенных варикапов VD8, VD9 в противоположных полярностях, закрытых опорными смещающими напряжениями +1)2 и -1)2 с резисторов R73, R74 и R75, R76, а также подключаемых и отключаемых от данной пассивной нелинейной интегрирующей RC- цепи +ПОС и -ПОС через транзисторы VT23 и VT25 второго входа алгебраического сумматора, а также резисторы R56 и R90. +ПОС и -ПОС образованы общим УПТ DA7 с удвоенным коэффициентом усиления и двумя параллельно подключаемыми цепями из резисторов R56, R90 с ключевыми транзисторами VT31, VT30. Управление данными ключевыми транзисторами VT31 и VT30 осуществляется от логических устройств ЛУЗ и ЛУ4 микросхемы DD4 через согласующие каскады на транзисторах VT32 и VT28, VT29, на входы которых поступают прямые 2.2, Vi, V2 и инверсные Z2, Vi, /2 сигналы с компараторов DA.6, DA4, DA8:

Vi - 1, Vi 0. если Vi(t) 0, или Vi 0, Vi 1,если ) 0

V2 1, V2 0, если V2(t) 0, или V2 О, V2- 1, если Vz(t) О

Возможные значения совместных комбинаций из состояний трех сигналов и сфор- мулированные по ним объединенные совместные комбинации из состояний трех сигналов, обеспечивающие подключение +ПОС или -ПОС к пассивной нелинейной интегрирующей RC-цепи второго плеча триггера и их отключение на возможных восьми временных участках деления в два раза частоты следования входного сигнала, сведены в стопбцы 11-14 табл.1. Столбцы 9. 10 данной таблицы характеризуют расположение по отношению к порогу входного сигнала Z(t) и состояние выходного сигнала /2 второго плеча триггера.

Первое логическое условие выражения (16) принудительного привязывания выходного сигнала V2(t) второго плеча триггера к нижнему уровню V2(t) -0,5 между моментами ti и t2 (фиг.2) во время перехода выходного сигнала Vi(t) первого плеча триггера из верхнего значения +0,5 в нижнее значение

-0,5 реализуется на первой логической.схе- ме совпадения двух сигналов Vi 1 и V2 1 (схема И) микросхемы DD3 прямого Vi 1 и инверсного V2 1 сигналов с выходов компараторов DD4 и DA8 с выходом через диод

VD11 и согласующий транзисторы VT26 на, VT27 с диодом VD10. Второе логическое условие выражения (16) принудительного привязывания выходного сигнала /2(t) второго плеча триггера к верхнему уровню V2(t) 0,5

между моментами ts и te во время перехода выходного сигнала Vi(t) первого плеча триггера из нижнего значения -0,5 в верхнее значение +0,5 реализуется на второй логической схеме совпадения микросхемы DD3

двух сигналов Vi 1 и V2 1 с выходом через диод VD12 и согласующие каскады на транзисторах VT17, VT18 на ключевой транзистор VT19 с диодом VD7. Третье логическое условие принудительного привязывания выходного сигнала Vi(t) первого плеча триггера к нижнему уровню Vi(t) « -0,5 между моментами 1з и t4 во время перехода выходного сигнала V2(t) второго плеча триггера из нижнего значения -0,5 в верхнее значение

+0,5 реализуется на третьей логической схеме совпадения микросхемы DD3 двух сигналов V1 1 и V2 - 1, а также диоде VD13, согласующем каскаде на транзисторе VT12 и ключевом транзисторе VT13 с диодом

VD4. Четвертое логическое условие принудительного привязывания выходного сигнала Vi(t) первого плеча триггера к верхнему уровню Vi(t) 0,5 между моментами t и ta во время перехода выходного сигнала V2(t)

второго плеча триггера из верхнего значения +0,5 в нижнее значение -0,5 реализуется на четвертой логической схеме совпадения микросхемы DD3 двух сигналов Vi 1 и V2 1 в сочетании с последующими

каскадами на диоде VD14, согласующих каскадах на транзисторах VT1, VT2 и ключевом транзисторе VT3 с диодом VD1.

Значения выходных сигналов Vi(t) ± 0,5 и V2(t) ± 0.5 обоих плечей триггера

5 соответствуют напряжениям ± 2 В.

В исходном состоянии при наличии на входе триггера сигнала отрицательной полярности Z(t) -0,5 и значений начальных состояний выходных сигналов обоих плеч

триггера Vi(t) 0,5 и V2(t) -0,5 управляемый фазоинвертор первого плеча из-за закрытого электронного ключа первой половины микросхемы DD1 инвертирует на УПТ DA1 входной сигнал отрицательной полярности в сигнал положительной полярности, согласно выражению (13). Закрытое состояние электронного ключа обеспечивается отрицательным потенциалом, снимаемым с выхода устройства управления на транзисторах VT6. VT7, закрытым нулевым потенциалом V2 0 с прямого выхода компаратора DA8 под действием удвоенного на УПТ DA7 отрицательного напряжения 2V2(t) -1 начального значения выходного сигнала V2(t) -0,5 второго плеча триггера. Выходной сигнал фазоинвертора положительной полярности Zi(t) 0,5 удерживает входной транзистор VT8 алгебраического сумматора в открытом состоянии, под действием которого выходной сигнал нелинейной интегрирующей RC-цепи первого плеча триггера находится на верхнем уровне Vi(t) 0,5 с максимальным значением параметра Г0 R20C (V1) R20Co варикапов VD2, VD3 (фиг.З). Положительный сигнал Vi(t) 0,5, усиленный УПТ DA3 в два раза до значения 2Vi(t) 1, создает на прямом выходе компаратора DA4 единичное состояние сигнала Vi 1. Этот единичный сигнал через открытые транзисторы VT20, VT21 устройства управления электронным ключом, собранным на второй половине микросхемы DD1, удерживает его в открытом состоянии. В результате этого на инверсный и прямой выходы УПТ DA5 фазоинвертора второго плеча триггера одновременно поступает общий входной сигнал отрицательной полярности Z(t) - 0,5, что способствует сохранению на выходе данного УПТ разностного сигнала, согласно правилу (14), равного общему входному сигналу Z2(t) Z(t) -0,5, когда Vi(t) 0. Равенство выходного сигнала Z2(t) УПТ DA5 входному Z(t) достигается малым ограничительным сопротивлением R50 прямого входа при открытом электронном ключе по сравнению со значением резистора R48 инверсного входа. Сигнал Z2(t) -0,5 отрицательной полярности с выхода данного управляемого фазоинвертора, являющийся входным сигналом порового сглаживающего устройства второго плеча триггера, открывает входной транзистор VT22 второго алгебраического сумматора, под действием которого выходной сигнал пассивной нелинейной интегрирующей RC-цепи находится в отрицательной области /2(t) -0,5.

Под действием положительного сигнала Zi(t) - 0,5 на выходе УПТ DA1, являющегося

входным сигналом первого плеча триггера. и начальных значений выходных сигналов его обоих плеч Vi(t) 0,5 и V2(t) - -0,5 на прямых и инверсных выходах компараторов 5 DA2, DA4, DA6, DA8 образуются следующие комбинации состояний сигналов:

Zi 1nZi- 0, Z2 OnZ2 1. Vi- 1 и Vi 0,

V2 0 и V2 1

0 Комбинации данных состояний поступают на вхоцы ЛУ1 и ЛУ2 микросхемы DD4, а также на входы устройства корректировки состояний выходных сигналов обоих плеч триггеров, собранного на микросхеме DD3. 5 На входе ЛУ1 первой половины микросхемы DD2 первого плеча триггера с прямых выходов компараторов DA2, DA4, DA8 образуется объединенная совместная комбинация из состояний трех сигналов: Zi 1, Vi 1, 0 /2 0, под действием которой на выходе ЛУ1 формируется логический ноль. При логическом ноле диод VD5 с согласующими VT14, VT15 и ключевым VT1 б транзисторами находится в открытом состоянии. Под дей- 5 ствием открытого ключевого транзистора VT16 эмиттерный повторитель на транзисторе VT11 оказывается в закрытом состоянии и положительная обратная связь (-ПОС) при отрицательной полярности выходного 0 напряжения Vi -0,5 отключена от первой нелинейной интегрирующей RC-цепи, одновременно на выходе ЛУ2 второй половины микросхемы DD2 с инверсных выходов компараторов DA2, DA4, DA8 действует обьеди- 5 ненная совместная комбинация из состояний трех сигналов:

Zi 0, Vi 0. V2 1

под действием которой на ее выходе образуется логическая единица. При логической 0 единице диод VD6. согласующий VT5 и клю- чеговой VT4 транзисторы находятся в закрытом состоянии. Образовавшаяся при этом +ПОС с выхода УПТ DA3 за счет удвоения им выходного сигнала 2Vi(t) через 5 резистор R9 и открытый транзистор VT9 по второму входу первого сумматора дополнительно удерживает выходной сигнал Vi(t) первого плеча триггера в положительном состоянии Vi 0,5.

0 Для второго плеча триггера под действием двух прямых и одного инверсного значений с выходов компараторов DA6, DA8 и DA4 на входе ЛУЗ первой половины микросхемы DD4 образуется объединенная со- 5 вместная комбинация из состояний трех сигналов

Z2 - 0, Vi - 0. V2 О,

которая обеспечивает на выходе первой половины микросхемы DD4 логическую единицу. Под действием данной логической

единицы диод VD15, согласующий VT28, VT29 и ключевой VT30 транзисторы закрыты. Поэтому образовавшаяся -ПОС с УПТ DA7 удвоенным выходным напряжением отрицательной полярности (t) через резистор R90 и открытый транзистор VT25 удерживает выходной сигнал второго плеча триггера в области отрицательных значений V2 -0,5.Действующая с выхода двух инверсных Z - 1, /2 1 и одного прямого Vi 1 выходоп микросхем DA6, DA8 и DA4 на входе ЛУ4 совместная комбинация из состояний трех сигналов:

Z2 1. V1 1. 1

создает на выходе второй половины микросхемы DD4 логический ноль. Поэтому диод VD16, согласующий VT32 и ключевой VT31 транзисторы открыты. Из-за открытого ключевого транзистора VT31 +ПОС отключена и вторая нелинейная интегрирующая RC- цепь второго плеча триггера подготовлена к работе в пассивном режиме.

Первое логическое устройство ЛУ1 корректировки состояний выходных сигналов Vi(t) и /2(t) обоих плеч триггера, собранное на первой логике микросхемы DD3, из-за одновременного присутствия на входе единичных сигналов Vi 1 и V2 1 с выходов компараторов DA4 и DA8 формирует на своем выходе логический ноль. Под действием логического ноля диод VD11 и транзисторы VT26, VT27 открыты. Открытый ключевой транзистор VT27 совместно с открытым диодом VD7 принудительно осуществляет привязку напряжения на обеих емкостях р- n-переходов варикапов VD8, VD9 к нижнему уровню Va(t) -0,5. На других парных входах логических устройств микросхемы DD3 совпадения единичных сигналов с прямых и инверсных выходов компараторов DA4, DA8 не происходит. Поэтому на их выходах присутствуют единичные положительные сигналы, каждый из которых через свои согласующие транзисторы поддерживают ключевые транзисторы VT19, VT13, VT3 с диодами VD7, VD4, VD1 в закрытом состоянии. В результате этого данные три цепи не оказывают влияния на переход выходного сигнала Vi(t) первого плеча триггера из состояния Vi 0,5 в противоположное состояние Vi -0.5.

При переходе на втором участке общего входного сигнала Z(t) в момент ц через нулевой порог на прямых и инверсных выходах компараторов DA2, DA4 состояния сигналов изменятся на противоположные, а на выходах компараторов DA6, DA8 состояния сигналов сохранятся в прежнем виде, т.е.

Zi OnZi 1,Z2 1 nZ2 0, Vi- 1 и Vi О, V2 - 0 и V2 0.

Соответственно на входе ЛУ1 объединенная совместная комбинация из состояний трех сигналов принимает вид:

Zi-0.Vi-1.V2-0.

Под действием данной комбинации на выходе ЛУ1 сохраняется логический ноль, который продолжает поддерживать -ПОС в отключенном состоянии от нелинейной интегрирующей RC-цепи первого плеча триггера. Изменение инверсного состояния KOMnapajopa DA6 с нулевого Z1 0 на единичное Zi 1 при сохранении предыдущих инверсных значений сигналов Vi О, V2 - 1 с выходов компараторов DA4, DA8 приводит к образованию на входе ЛУ2 объединенных совместных комбинаций из состояний трех сигналов:

Zi- 1. Vi-0. V2 1,

под действием которых выходное состояние

ЛУ2 изменяется с единичного на нулевое. Это приводит к открытию диода VD6 и транзисторов VT5, VT4 и отключению +ПОС от интегрирующей RC-цепи первого плеча триггера. В результате выходной сигнал

Vi(t) данной пассивной нелинейной интегрирующей RC-цепи на участке от ti до t2 изменяется с внутренней отрицательной обратной связью (ООС) от крайнего верхнего значения Vi(t) 0,5 до нуля Vi(t) 0 по кривой

2 (фиг.2,б). Выходное напряжение Vi(t) сначала медленно спадает вблизи Vi(t) 0,5 из-за большего значения суммарной емкости C(Vi) Со варикапов VD2, VD3 (максимального значения емкости варикапа VD2 и

минимального значения емкости варикапа VD3), а затем по мере уменьшения результирующей емкости C(Vi), а следовательно, параметра т (Vi) R20C(V1) нелинейной интегрирующей RC-цепи по спадающей кривой 3 (фиг.З) с г„акс Г0 R20Co при Vi(t) 0,5 до Гмин - R20CMHH при Vi(t) - О, скорость нарастания выходного напряжения Vi(t) увеличивается и достигает максимального значения вблизи нулевого порога.

0 Такое нелинейное изменение параметра i(Vi) R20C(Vi) пассивной нелинейной интегрирующей RC-цепи первого плеча триггера при отключенных -ПОС и +ПОС способствует эффективному подавлению

5 выбросов помех, искажающих полезный сигнал, когда он находится выше нулевого порога. В результате этого достигается высокая точность определения моментов пе- ресечен 1я выходным непрерывным

сигналом Vi(t) нулевого порога при переходе инвертированного входного сигнала Zi(t) первого плеча триггера из положительной в отрицательную область изменения.

Выходной сигнал V2(t) второго плеча триггера на данном участке от ti до t2 под действием объединенной совместной комбинации из состояний трех сигналов на вход ЛУЗ:

Z2 1, Vi-0, V2 0

сохраняет логическую единицу на выходе первой половины микросхемы DD4. Поэтому подключенная -ПОС к нелинейной интегрирующей RC-цепи второго плеча триггера продолжает удерживать выходной сигнал V2(t) в отрицательной области. Образовавшаяся на входе ЛУ4 объединенная совместная комбинация из состояний трех сигналов: Z2 0, Vi 1, V2 1 сохраняет логический ноль на выходе второй половины микросхемы DD4. Из-за присутствия на выходе единичных сигналов Vi 1 и V2 1 и образовавшегося на ее выходе логического нуля через открытые диод VD11, транзисторы VT26, VT27 и диод VD10 продолжает осуществляться привязка напряжения на емкости p-n-переходов варикапов VD8, VD9 к отрицательному уровню V2(t) -0,5 с остаточным напряжением на диоде VD10, не давая возможности ложного нарастания по кривой 11 фиг.2, с выходного сигнала второго плеча триггера с значения V2 -0,5 до уровня нулевого порога. Осуществление такой принудительной привязки выходного сигнала второго плеча триггера к отрицательному уровню способствует уменьшению сбоев в процессе увеличения в два раза данным триггером периода следования входного сигнала ±Z(t).

При переходе выходного сигнала Vi(t) первого плеча триггера на третьем участке в момент г в отрицательную область изменения по кривой 3 фиг.2,б на прямом и инверсном выходах компаратора DA4 образуются прямые и инверсные значения сигналов Vi 0 и Vi 1. Под действием нулевого сигнала Vi 0 управляющие транзисторы VT20, VT21 и ключевое устройство второго фазоинвертора, собранное на второй половине микросхемы DD1, закрыты. Из-за закрытого ключевого устройства УПТ DA5 общий входной сигнал положительной полярности инверстируется согласно выра- жению(15) в сигнал отрицательной полярности 7.2 -Z(t) при Vi(t) - 0.

Под действием сменившихся состояний сигналов на выходах компараторов DA4, DA6 и сохранившихся от предыдущего участка значений состояний сигналов на выходах компараторов DA2, DA8 образуется

следующая комбинация прямых и и(изерс ных сигналов: Zi - 0 и 7л 1, 7.2 0 и Z - 1, Vi 0 и Vi - 1, V2 -- 0 и V2 - 1

Образовавшаяся на входе ЛУ1 данная 5 объединенная совместная комбинация из состояний трех сигналов:

Zi 0, Vi 0, V2-0

формирует на выходе первой половины микросхемы DD2 логическую единицу, которая

0 закрывает диод VD5 и транзисторы VT14- VT16 и тем самым осуществляет подключение -ПОС к нелинейной интегрирующей RC-цепи первого плеча триггера. В результате этого образовавшаяся положительная

5 обратная связь с выхода УПТ DA3 через резистор R42 и открытый транзистор VT11 уводит выходной сигнал нелинейной интегрирующей RC-цепи в отрицательную область по кривой 3 фиг.2, б. При этом

0 параметр r(Vi) R20C(V1) нелинейной интегрирующей RC-цепи возрастает по кривой 3 фиг.З с минимального значения Гмин R20CMMH при Vi 0 до максимального значения Гмэкс R20Co при Vi -- -0,5. Одновре5 менно действующая на входе ЛУ2 объединенная совместная комбинация из состояний трех сигналов:

Zi 1, Vi 1, V2 1 формирует на выходе второй половины мик0 росхемы DD2 логический ноль, который через открытый диод VD6 и открытые транзисторы VT5, VT6 продолжает удерживать в отключенном состоянии ПОС отданной нелинейной интегрирующей RC-цепи.

5 Действующая на входе ЛУЗ объединенная совместная комбинация из состояний трех сигналов:

Z2 0, V1 1, V2 0 создает логическую единицу на выходе пер0 вой половины микросхемы DD4, закрывающую диод VD15 и транзисторы VT28-VT30. Поэтому нелинейная интегрирующая RC- цепь второго плеча триггера оказывается охваченной -ПОС с выхода УПТ DA7 через

5 резистор R56 и открытый транзистор VT23. Действующий входной инвертированный сигнал отрицательной полярности Z2(t) -Z(t) при Vi(t) 0, снимаемый с выхода УПТ DA5 второго фазоинвертора, в сочетании с

0 подключенной -ПОС обеспечивает резкий увод выходного сигнала нелинейной интегрирующей RC-цепи в крайнее нижнее значение V2(t) -0,5 по кривой 12 фиг.2,в. Вторая объединенная совместная комбина5 ция из состояний трех сигналов, образующаяся на входе Л У4:

Z2 1, Vi 0, V2 1,

сохраняет нулевой потенциал на выходе второй половины микросхемы DD4 и через

открытый диод VD16 и транзисторы VD32, VD31 удерживает отключенной -tflOC от данной нелинейной интегрирующей RC-це- пи.

Перешедший выходной сигнал Vi(t) первого плеча триггера в отрицательную область изменения снимает с прямого Vi 0 и инверсного Vi 1 выходов компараторов DA4, DA8 запрет по первой логике микросхемы DD3 на переход выходного сигнала V2(t) второго ппеча триггера из нижнего отрицательного уровня V2 -0,5 в противоположное положительное состояние. Вторая и четвертая микросхемы DD3 из-за наличия несовпадения на входах сигналов сохраняют единичные сигналы на выходе. Поэтому их диоды VD12, VD7 и VD14, VD1 со своими ключевыми транзисторами VT17-VT19 и VT1-VT3 находятся в закрытом состоянии, не оказывая влияния на перезаряды емкостей p-n-переходов обеих интегрирующих RC-цепей. В то же время за счет совпадения единичных сигналов Vi 1 и V2 1 по третьему логическому правилу выражения (16) на входе третьего логического устройства микросхемы DD3 и образования на его выходе логического нуля диоды VD13, VD4 с ключевыми транзисторами VT12, VT13 оказываются открытыми. В результате этого выходной сигнал Vi(t) первого плеча триггера под действием открытых транзистора VT13 и диода VD4 оказывается зафиксирован в крайнем нижнем значении Vi(t) -0,5, что исключает ложный возврат данного выходного сигнала Vi(t) в положительную область.

На четвертом временном участке из-за перехода общего входного сигнала Z(t) в момент t3 через нулевой уровень порога в от- рицательную область изменений на выходах УПТ DA1 и DA5, согласно выражениям (12) и (14), формируются инверсные положительные сигналы Zi(t) 0 и Zj(t) О, под действием которых на выходах компараторов DA2 и DA6 образуются состояния сигналов вида: Zi 0, Zi 0 и 7.1 1, Zi 0. Эти вновь образовавшиеся состояния сигналов в сочетании с сохранившимися от предыдущего участка состояниями выходных сигналов обоих плеч триггера Vi(t) и V2(t) на выходах компараторов DA4 и DA8 образуют следующую общую комбинацию состояний сигналрв: Zi 1 и Zj О, Z2 - 1 и Za 0, Vi 0 и Vi

-1,V2 OnV2-1.

Под действием объединенной совместной комбинации из состояний трех сигналов на входе ЛУ1

Zi 1, Vi 0, V2 0

образовавшаяся логическая единица на выходе первой половины микросхемы DD2 сохраняет подключенной -ПОС к нелинейной интегрирующей RC-цепи первого плеча триггера. В то же время образовавшаяся на входе ЛУ2 объединенная совместная комбинация из состояний трех сигналов

Zt O, Vi 1, V2 0

логическим нулем с выхода второй половины микросхемы DD2 сохраняет отключенной +ПОС от данной нелинейной интегрирующей RC-цепи. Под действием положительного входного сигнала Zi(t) первого плеча триггера и остаточного напряжения на открытом диоде VD4 и открытом транзисторе VT13, обеспечивающих привязку выходного сигнала Vi(t) первого плеча триггера к уровню Vi(t) -0,5, под действием нулевого потенциала третьего логического устройства совпадения сигналов микросхемы DD3 выходной сигнал Vi(t) все же успевает к концу четвертого участка вырасти по кривой 4 фиг.2,б до уровня остаточного напряжения на открытом диоде VD4. В то же время выходной сигнал V2(t) второго плеча триггера на данном четвертом участке при отключенных обоих -ПОС и +ПОС нулевым потенциалом с обоих выходов микросхемы DD4 под действием объединенных совместных комбинаций из состояний трех сигналов на входах ЛУЗ и ЛУ4

Z2 1, Vi 1, V2 0 и Z2 0, Vi 0. V2 - 1 возрастает с внутренней ООС по кривой 13 (фиг.2,) в от крайнего нижнего значения V2(t)- -0,5 до нулевого уровня порога /2(t) 0. Выходное напряжение V2(t) второго плеча триггера на данном временном участке сначала медленно нарастает вблизи нижнего уровня из-за большого значения суммарной емкости C(V2) Со варикапов VD8, VD9 (максимального значения емкости варикапа VD9 и минимального значения емкости варикапа VD8). а затем по мере уменьшения результирующей емкости С(/2) и, следовательно, уменьшения параметра г (V2) R71C(V2) нелинейной интегрирующей RC- цепи по спадающей кривой 3 фиг.З с максимального значения Гмакс r0 R71Co при V2(t) -0,5 до минимального значения Тмин Р71Смин при V2(t) 0 резко увеличивается и достигает максимального значения вблизи нулевого порога. Такое нелинейное изменение параметра г (V2) R73C(V2) пассивной нелинейной интегрирующей RC-цепи второго плеча триггера при отключенных -ПОС и +ПОС способствует эффективному подавлению выбросов помех, искажающих полезный сигнал, когда он находится ниже нулевого уровня порога. В результате этого

достигается высокая точность определения моментов пересечения выходным сигналом V2(t) нулевого порога при переходе инвертированного входного сигнала Za(t) второго плеча триггера из отрицательной в положительную область изменения.

При переходе на пятом временном участке в момент т.4 выходного сигнала V2(t) второго плеча триггера через нулевой порог в положительную область изменения по кривой 14 фиг.2,в на прямом и инверсном выходах компаратора DA8 образуются значения V2 1 и V2 0. Под действием единичного прямого значения V2 1 открываются управляющие транзисторы VT6, VT7 и от них открывается ключевое устройство первой половины микросхемы DD1. Поэтому УПТ DA1 первого фазоинвертора без изменения фазы, согласно выражению (12), пропускает на выход отрицательный входной сигнал Zi(t) -Z(t) при V2(t) 0. Из-за сменившихся состояний сигналов на выходах компараторов ОА8, DA2 и сохранившихся значений состояний на выходах компараторов DA4, DA8 от предыдущего участка образуются следующие комбинации сигналов: Zi - О и Zi - 1, Z2 - 1 и - 0, Vi - 0 и Vi - 1, V2

1 И V2 0.

Под действием отрицательного входного сигнала Zi(t) - -Z(t) с выхода первого фазоинвертора и подключенной -ПОС к нелинейной интегрирующей RC-цепи первого плеча триггера значением на входе ЛУ1 объединенной совместной комбинации из состояний трех сигналов

Zi - 0. Vi - О, V2 1

выходной сигнал Vi(t) первого плеча триггера резко уводится по кривой 5 (фиг.2,6) в крайнее нижнее значение Vt(t) - -0,5, предотвращая ложный переход выходного сигнала Vi(t) в положительную область. В то же время образовавшаяся на входе ЛУ2 объединенная совместная комбинация из состо- сигналов

Zi-1.Vi-1.V2-О

логическим нулем с выхода второй половины микросхемы DD2 поддерживает отключенной + ПОС от данной нелинейной интегрирующей RC-цепи. После перехода выходного сигна/ra Va(t) второго плеча триггера в положительную область изменения V2(t) 0 на входе ЛУЗ образуется объединенная совместная комбинация из состояний трех сигналов

Zz- 1. Vi-1. Va- 1.

под действием которой логический нулевой потенциал на выходе первой половины микросхемы DD4 продолжает поддерживать отключенной -ПОС от второй нелинейной интегрирующей RC-цепи. Образовавшаяся

в это время на входе ЛУ4 объединенная совместная комбинация из состояний трех сигналов

Z2 0, Vi О, V2 О

единичным значением с выхода второй половины микросхемы DD4 и закрытого под ее действием диода VD16 с транзисторами VT32, VT31 и открытого транзистора VT23 охватывает +ПОС вторую нелинейную интегрирующую RC-цепь с выхода УПТ DA7 через резистор Rse. под действием которой выходной сигнал V2(t) уводится по кривой 14 фиг.2,в в крайнее верхнее положение V2(t) 0,5. При этом параметр г (V2) нелинейной интегрирующей RC-цепи изменяется по кривой 3 фиг.З от минимального значения Гмин r(V2 R71 Смин при V2(t) 0 до максимального значения rMaitc(V2) R71Co при V2(t) 0,5.

Под действием образовавшейся комбинации выходных сигналов обоих плеч триггера

Vi-Ои Vi- 1. V2- 1 и V2-0 на входах четырех логических устройств совпадения микросхемы DD3 производится устранение совпадения единичных сигналов на входе третьего логического устройства. В результате этого снимается запрет на переход выходного сигнала Vi(t) первого плеча триггера с нижнего Vi(t) -0,5 уровня в противоположное состояние. В то же время, согласно второму логическому условию (16), образовавшиеся на входе второй схемы совпадения два единичных сигнала Vi - 1 и V2 1 своим выходным логическим нулем открывают диод VD12 и транзистор VT19 с диодом VD7, обеспечивая привязку выходного сигнала V2(t) второго плеча триггера к верхнему положительному уровню V2(t) 0,5. Такая привязка выходного сигнала V2(t) к положительному уровню исключает случайный переход данного сигнала в отрицательную область изменения, а следовательно, исключается сбой процесса удвоения данным помехоустойчивым триггером периода следования входного импульсного сигнала. Три других логических устройства микросхемы OD3 в это время из-за отсутствия на их входах совпадения единичных сигналов не оказывают влияния на состояния выходных сигналов Vi(t) и V2(t) обоих плеч триггера.

При переходе на шестом участке от ts до te общего входного сигнала Z(t) через нулевой порог в положительную область изменения Z(t) 0 на прямом и инверсном выходах компаратора DA.2 формируются парные значения Zi 1 и Zi - 0. которые в сочетании с сохранившимися предыдущими значениями из выходах компараторов DA4, DA6, DA8 образуют общую комбинацию состояний сигналов вида

Zi - 1 и Zi - 0. Z2 0 и Zj 1, Vi 0 и Vi - 1, V2 1 и V2 - 0.

Образовавшаяся на входах ЛУ1 и ЛУ2 обьединенная совместная комбинация из состояний трех сигналов,

1,Vi-0, V2 1 nZi 0, Vi 1, V2-0,

своими выходными логическими нулями микросхемы DD2 через открытые диоды VD5, VD6 и открытые транзисторы VT14- VT16, VT5, VT4 отключает +ПОС и -ПОС от первой нелинейной интегрирующей RC-це- пи. Поэтому выходной сигнал Vi(t) данной интегрирующей RC-цепи под действием положительного входного сигнала Zi(t) Z(t) с внутренней ООС нарастает по кривой 6 фиг.2,б на рассматриваемом участке от Vi(t) - 0,5 до Vi(t) 0. Происходящее на этом участке уменьшение параметра t(Vi) - -R20C(Vi) пассивной нелинейной интегрирующий RC-цепи по спадающей кривой 3 фиг.З с максимального значения гМакс -TO R20Co при Vi(t) -0,5 до минимального значения Тмин R20CMHH при Vi(t) 0 способствует эффективному подавлению выбросов помех и достижению высокой точности определения моментов пересечения выходным сигналом Vi(t) первого плеча триггера нулевого порога при переходе прямого входного сигнала Zi(t) данного первого плеча триггера в положительную область изменения. Действующая на входе ЛУЗ обьединенная совместная комбинация из состояний трех CHI налов Z2-0, Vi 1, V2- 1,

продолжает удерживать логическим нулем с выхода первой половины микросхемы DD4 через открытые диод VD15 и транзисторы VT28 - VT30 -ПОС в отключенном состоянии, а обьединенная совместная комбинация из состояний трех сигналов на входе ЛУ4

Z2 1. Vi -О, V2 0,

логической единицей на выходе второй половины микросхемы DD4 и закрытых под действием этой единицы диода VD16 и транзисторов VT32, VT31 продолжает осуществлять охват +ПОС нелинейной интегрирующей RC-цепи второго плеча триггера. Действующий на входе данной нелинейной интегрирующей RC-цепи инвертированный согласно выражению (15) сигнал Z;(0 -Z(t) при Vi(t) 0 отрицательной полярности уменьшает уровень выходного си(нлл;| по кривой 15 фиг.2,в на уровень остаточного напряжения открытого

в это время диода VD7. Такое принудительное привязывание выходного сигнала V2(t) второго плеча триггера к верхнему уровню V2(t) 0,5 способствует устранению преждевременного перехода данного выходного сигнала через нулевой порог в отрицательную область, тем самым устраняется сбой процесса удвоения периода следования выходного сигнала V2(t) второго плеча триггера по сравнению с периодом следования общего входного сигнала Z(t).

При переходе на седьмом участке в момент te выходного сигнала Vi(t) первого плеча триггера через нулевой порог в положительную область изменения по кривой 7 фиг.2,б на прямом и инверсном выходах компаратора DA4 образуются парные значения Vi 1 и Vi 0. Под действием единичного значения Vi 1 с прямого выхода компаратора и открытые управляющие транзисторы VT20. VT21 ключевое устройство второй половины микросхемы DD1 оказывается в открытом состоянии. Поэтому УПТ DA5 второго фазоинвертора пропускает согласно выражению (14) без изменения фазы положительный входной сигнал Z2(t) Z(t) при Vi(t) 0. В результате сменившихся состояний сигналов на выходах компараторов DA2, DA6 и сохранившихся от предыдущего участка значений состояний сигналов на выходах компараторов DA4, DA8 образуются следующие общие комбинации сигналов:

Zi 1 и Zj - О, Z2 1 и Z2 0. Vi 1 и Vi 0. V2 1 и V2 - 0.

Образованные на входах ЛУ2 и ЛУ4 объединенные совместные комбинации из состояний трех сигналов

Zi - 0, Vi - О, V2 - 0 и 2г -- 0. Vi - 1, V2 0 создают на выходах вторых половин микросхем DD2 и DD4 логические единицы, под действием которых диоды VD6 и VD16 со своими каскадами на транзисторах VT5, VT4 и VT32, VT31 закрыты. Обе нелинейные интегрирующие RC-цепи, охваченные +ПОС с выходов своих УПТ DA3 и DAT. уводят оба выходных сигнала в крайнее верхнее значение Vi(t) 0,5 и V2(t) -0,5 по кривым 7 и 16 фиг. 2, б, в. Резкому уводу выходного сигнала V(t) второго плеча триггера на максимальный уровень V(t) - 0.5 также способствует образовавшаяся согласно выражению (14) положительная полярность входного сигнала Z(t) - Z(t) на выходе УПТ DA5 второго фазоинпрртора из-за перехода выходного сигнала Vi(i) порпого плеча триггера в положительную область Vi(t) 0.

Перелод с +ПОС выходного сигнала Vi(t) первого плеча триггера в крайнее верхнее значение Vi(t) 0,5 сопропождастся увеличением параметра г (Vi) - R20C(Vi) нелинейной интегрирующей RC-цепи по кривой 3 фиг.З с минимального значения гмин R20CMHH при Vi(t) - 0 до максимального значения Гмакс R20Co при Vi(t) 0,5. Наличие на входах ЛУ1 и ЛУЗ объединенных совместных комбинаций из состояний трех сигналов

Zi-1. Vi-1, V2- 1 и2Ь- 1. Vi-1.Vz-1 обеспечивает формирование нулевых сигналов на выходах первых половин микросхем DD2 и DD4, а следовательно, открытие диодов VD5 и VD15 со своими транзисторами VT14-VT16 и VT28-VT30 и отключение -ПОС от каждой нелинейной интегрирующей RC-цепи.

Образовавшаяся комбинация прямых и инверсных выходных сигналов обоих плеч триггера

Vi- 1. Vi 0, V2 1. V2 0 на входах четырех логических схем совпадения микросхем DD3 устраняет совпадение единичных сигналов на входе второй логической схемы совпадения и снимает запрет на переход выходного сигнала V2(t) в противоположную отрицательную область. Вновь образовавшаяся по четвертому логическому правилу (16) комбинация совпадений двух единичных сигналов Vi - 1 и V2 - 1 на входе четвертой логической схемы логическим нулем на выходе через открытый диод VD14 и открытые транзисторы VT1-VT3 обеспечивает привязку выходного сигнала Vi(t) первого плеча триггера к верхнему значению Vi(t) 0,5. Такая привязка выходного сигнала Vi(t) к верхнему уровню Vi(t) 0,5 исключает случайный переброс данного выходного сигнала Vi(t) в отрицательную область, что способствует сохранению режима удвоения периода следования выходного сигнала Vi(t) первого плеча триггера. На входах первой и третьей логических схем отсутствует совпадение единичных сигналов, поэтому данные устройства на данном седьмом участке не влияют на работу обеих нелинейных интегрирующих RC-цепей.

В процессе перехода на восьмом участке общего входного сигнала Z(t) в момент ty через нулевой порог в отрицательную область Z(t) 0 на прямом и инверсном выходах компараторов ОА2, DA6 изменятся на значения Zi - 0 и Zi - 1, Za - 0 и 2.2 - 1. а на выходах двух других компараторов DA4, DA8 значение состояний сигналов сохранится прежним, так что общая комбинация состояний сигналов примет вид

Zi-OnZ -1.Z2-OMZ2-1. Vi-1 nVi- - О, V2 - 1 и V2 - 0.

Под действием объединенной совместной комбинации из состояний трех сигналов на входе ЛУ2

Zi 1, Vi 0. V2 0

и образовавшейся логической единицы на выходе второй половины микросхемы DD2 нелинейная интегрирующая RC-цепь первого плеча триггера продолжает быть охваченной + ПОС. Действующий согласно выражению (12) сигнал отрицательной полярности Zi(t) -Z(t) при V2(t) 0 на входе данной нелинейной интегрирующей RC-цепи уменьшает по кривой 8 фиг.2,б выходной сигнал Vi(t) первого плеча триггера на уровень остаточного напряжения открытого диода VD1. В то же время действующая на входе ЛУ1 объединенная совместная комбинация из состояний трех сигналов

Zi 0, Vi 1, V2 1

выходным логическим нулем с выхода первой половины микросхемы DD2 через открытые диод VD5 и транзисторы VT14-VT16 сохраняет отключенной -ПОС от данной нелинейной интегрирующей RC-цепи. Объеди- ненная совместная комбинация из состояний трех сигналов, действующая на входах ЛУЗ и

Z2 0. /1 О, V2 1 И Z2 1, Vi 1. /2 О,

своими логическими нулями с выходов первой и второй половин микросхемы DD4 через открытые диоды VD15, VD16 и открытые транзисторы VT28-VT30, VT32, VT31 поддерживают отключенными +ПОС и -ПОС от второй нелинейной интегрирующей RC-цепи. Под действием отрицательного входного сигнала Z2(t) -Z(t) при Vi(t) 0 выходной сигнал V2(t) второй нелинейной интегрирующей RC-цепи с внутренней ООС изменяется по кривой 17 фиг.2,в с верхнего V2(t) 0,5 до нулевого V2(t) 0 уровня порога. Уменьшающийся на этом участке параметр т (Va) R71C(V2) пассивной нелинейной интегрирующей RC-цепи по спадающей кривой 3 фиг.З с максимального значения Гмакс Г0 R71Co при V2(t) 0,5 до минимального значения Тмин Р71смин при V2(t) - О способствует подавлению выбросов помех и достижению высокой точности определения момента пересечения выходным сигналом второго плеча триггера нулевого порога при переходе прямого входного сигнала Za(t) данного плеча триггера в отрицательную область изменения.

Работа триггера на последующем девятом участке при переходе выходного сигнала V2(t) второго плеча триггера в отрицательную область повторяет работу рассмотренного первого участка. Выходные сигналы Vi и V2, изображенные на фиг.2,г,д,

соответствуют состояниям выходных сигна лов Vi(t) и V2(t) обоих плеч триггера, образующихся путем сравнения каждого из этих непрерывных сигналов с заданным выходным уровнем порога а 0.

Отличительной особенностью рассмотренного помехоустойчивого триггера является его способность в условиях действия интенсивных высокочастотных помех с помощью вероятностных реле обоих плеч триггера совместно выделять вероятности превышения каждым вторым импульсным сигналом заданного уровня порога а 0,5 и одновременно подавлять (устранять) входной импульс между выделяемыми сигналами. При этом высокая помехоустойчивость процесса деления в два раза частоты следования исходных импульсных сигналов достигается как нелинейным изменением параметров ri (V1) иГ2 (V2) вероятностных реле обоих плеч триггера при нарастании и спаде их выходных напряжений Vi(t) и V2(t), так и за счет управления пороговыми положительными обратными связями объединенной совместной комбинацией из состояний трех сигналов: входного и выходного сигналов одного плеча триггера и вы ходного сигнала противоположного плеча триггера - в сочетании с логическим устройством корректировки состояний выходных сигналов обоих плеч триггера. Известным методом деления в два раза частоты следования импульсных сигналов безынерционным триггером в сочетании с предварительным сглаживанием и последующим ограничением входного импульсного сигнала на однозвенной и многозвенной интегрирующей RC-цепи невозможно достичь такой высокой помехоустойчивости. Наличие же выходных сигналов изменяющихся по разным фронтам входного импульса расширяет функциональные возможности.

Проведенное на ЦВМ моделирование выражений (1)-(11) подтвердило высокую помехоустойчивость процесса деления в два раза частоты входного сигнала при дисперсиях помехи G 0,125 и G 0,5. Результаты моделирования отражены в графиках фиг.5.6. Реализованный по фиг.4 помехоустойчивый триггер не имеет подстроенных элементов. что упрощает его практическую реализацию. Сглаживающие свойства триггера задаются начальным значением емкости влрикяпов VD2, VD3 и VD8. VD9, а также значением резисторов R20 и R71.

Формула изобретения

которых содержит первый элемент И-НЕ, первый элемент И-ИЛИ-НЕ и выходную шину, отличающийся тем, что, с целью повышения помехоустойчивости и расширения функциональных возможностей, в каждое его плечо введены управляемый фазоинвертор, алгебраический сумматор, два компаратора, второй элемент И-НЕ, второй элемент И-ИЛИ-НЕ, усилитель постоянного тока, имеющий коэффициент усиления, равный двум, два ограничительных резистора, четыре ключевых элемента, четыре преобразователя уровня и пассивная нелинейная интегрирующая RC-цепь, содержащая постоянный резистор, два варикапа, два резистора и два конденсатора, причем вход и выход пассивной нелинейной интегрирующей RC-цепи соединены соответственно с первым и вторым выводами постоянного резистора, второй вывод которого соединен с анодом первого варикапа и с катодом второго варикапа, катод первого и анод второго варикапов соединены соответственно через первый и второй резисторы с общей шиной и соединены соответственно через первый и второй конденсаторы с общей шиной, в каждом плече входная шина соединена с информационным входом фазоинвертора, выход которого соединен с прямым входом первого компаратора и с двухполярным входом алгебраического сумматора, выход которого соединен со входом пассивной нелинейной интегрирующей RC-цепи, выход которой соединен с прямым входом усилителя постоянного тока, выход которого соединен с прямым входом второго компаратора и через первый и второй ограничительные резисторы соответственно с суммирующими входами алгебраического сумматора на положительную и отрицательную полярности сигнала, прямой выход второго компаратора соединен с входами первой структуры И первого элемента И-ИЛИ-НЕ и с первым входом первого элемента И-НЕ. инверсный выход второго компаратора соединен со входами первой структуры И второго элемента И-ИЛИ-НЕ и с первым входом второго элемента И-НЕ, инверсный и прямой выходы первого компаратора соединены соответственно с первыми входами вторых структур И второго и первого элементов И- ИЛИ-НЕ. выходы которых соединены соответственно через первый и второй преобразователи уровней с управляющими входами первого и второго ключевых элементов, которые коммутируют соответственносуммирующиевходыалгебраического сумматора на положительную и отрицательную полярности сигналя с

общей шиной, которая соединена с инверсными входами компараторов, выходы первого и второго элементов И- НЕ соединены соответственно через третий и четвертый преобразователи уровней с управляющими входами третьего и четвертого ключевых элементов, которые соответственно коммутируют аноды с катодами первого и второго варикапов пассивной нелинейной интегрирующей RC-цепи, прямой выход второго компаратора каждого плеча соединен с выходной шиной и с управляющим входом управляемого фазоинвертора другого плеча, прямые выходы вторых компараторов первого и второго плеч соединены соответственно со вторыми входами вторых структур И второго элемента И-ИЛИ-НЕ второго плеча и первого элемента И-ИЛИ-НЕ первого плеча и соединены соответственно со вторыми входами второго элемента И-НЕ второго плеча и первого элемента И-НЕ первого плеча, инверсные выходы вторых компараторов первого и второго плеч соединены соответственно со вторыми входами вторых структур И первого элемента И-ИЛИ-НЕ второго плеча и второго элемента И-ИЛИ-НЕ первого плеча и соединены соответственно со вторыми входами первого элемента И-НЕ второго плеча и второго элемента И-НЕ первого плеча.

гч

I т .CD СЛ

I

сэ NO

В

С; см CD

4

сэ

ГЧ)

р

U1

R2

to

30

10

20

50

Ю

2050

Фиг. 5

-0,5

10

20

50

ho

10

2050W

Фиг 6

16ПН4П2

50

50

W

50

w

50

50

E

50

ho

50

50

Авторы

Даты

1991-10-30—Публикация

1988-12-14—Подача