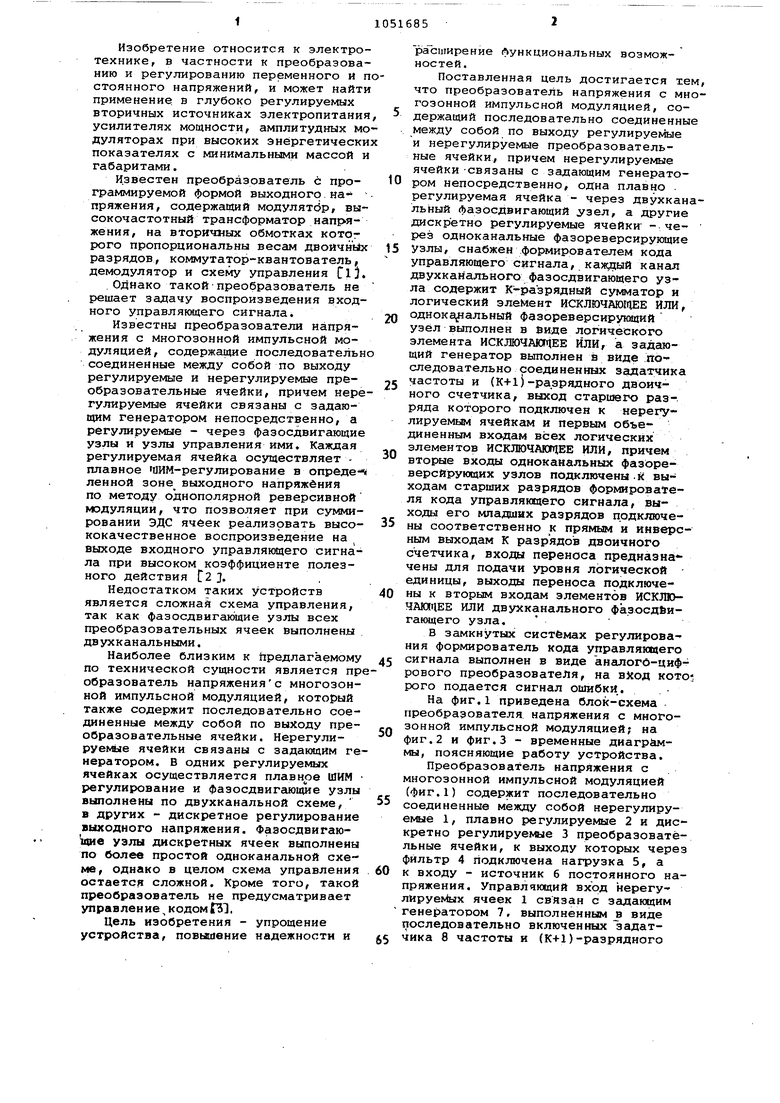

Изобретение относится к электро технике, в частности к преобразова нию и регулированию переменного и стоянного напряжений, и может найт применение, в глубоко регулируемых вторичных источниках электропитани усилителях мощности, амплитудных мо дуляторах при высоких энергетически показателях с минимальными массой и габаритами. Известен преобразователь с программируемой формой выходного. на- пряжения, содержавши модулятор, вы сокочастотный трансформатор напр-яжения, на вторичных обмотках котог рого пропорциональны весам двоичньЛх разрядов, коммутатор-квантователь, демодулятор и схему управления Cl3 . Однако такой-преобразователь не решает задачу воспроизведения входного управляющего сигнала. Известны преобразователи напряжения с Многозонной импульсной модуляцией, содержащие последовательн соединенные между собой по выходу регулируемые и нерегулируемые преобразовательные ячейки, причем нере гулируемые ячейки связаны с задающим генератором непосредственно, а регулируемые - через фазосдвигающие узлы и узлы управления ими. Каждая регулируемая ячейка ос5Т4ествляет плавное ШИМ-регулирование в определенной зоне выходного напряжения по методу однополярной реверсивной модуляции, что позволяет при суммировании ЭДС ячеек реализовать высококачественное воспроизведение на выходе входного управляющего сигнала при высоком коэффициенте полезного действия Г2 J. Недостатком таких устройств является сложнай схема управления, так как фазосдвигающие узлы всех преобразовательных ячеек выполнены двухканальными. Наиболее близким к предлагаемому по технической сущности является пр образователь напряженияс многозонной импульсной модуляцией, который также содержит последовательно соединенные между собой по выходу преобразовательные ячейки. Нерегулируемые ячейки связаны с задающим ге нератором. В одних регулируемых ячейках осуществляется плавное ШИМ регулирование и фазосдвиггиоище узлы выполнены по двухканальной схеме, в других - дискретное регулирование выходного напряжения. Фазосдвигаю цие узлы дискретных ячеек выполнены по Солее простой одноканальной схеме, однако в целом схема управления остается сложной. Кроме того, такой преобразователь не предусматривает управление кодом ГЗТ, Цель изобретения - упрощение устройства, повышение надежности и расширение лункциональных возможностей. Поставленная цель достигается тем, что преобразователь напряжения с многозонной импульсной модуляцией, содержащий последовательно соединенные между собой по выходу регулируемые и нерегулируемые преобразовательные ячейки, причем нерегулируемые ячейки-связаны с задающим генератором непосредственно, одна плавно . регулируемая ячейка - через двухканальный фазосдвигающий узел, а другие дискретно регулируемые ячейки- - че- рез одноканальные фазореверсирующие УЗЛЫ, снабжен .формирователем кода управляющего сигнала, канал двухкайального фазосдвигающего узла содержит К-разрядный сумиатор и логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, однока 1альный фазореверсирующий узел выполнен в виде логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а задающий генератор выполнен в виде последовательно соединенных задатчика частоты и (К+1)-разрядного двоичного счетчика, выход старшего разряда которого подключен к нерегулируемым ячейкам и первым объединенным входам всех логических элементов ИСКЛЮЧАЮГЦЕЕ ИЛИ, причем втоЕдле входы однокаиальных фазореверсйрующих узлов подключены . и выходам старших разрядов формирователя кода управляющего сигнала, выходы его младших разрядов подключены соответственно к прямым и ииверсным выходам К разрядов дэоичиого счетчика, входы переноса предназна чены для подачи уровня логической единицы, выходы переноса подключены к вторым входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ двухканального фазосдЬигающего узла. В замкнутых системах регулирования формирователь кода управляющего сигнала выполнен в виде аналого-цифрового преобразователя, на виод кото рого подается сигнал ошибки.. На фиг.1 приведена блок-схема преобразователя напряжения с многозонной импульсной модуляцией; на фиг.2 и фиг.З - временные диаграммы, поясняющие работу устройства. Преобразователь напряжения с многозонной импульсной модуляцией (фиг.1) содержит последовательно соединенные между собой нерегулируемые 1, плавно регулируемые 2 и дискретно регулируемые 3 преобразовательные ячейки, к выходу которых через фИльтр 4 подключена нагрузка 5, а к входу - источник 6 постоянного напряжения. Управляющий вход нерегулируемых ячеек 1 связан с задающим генератором 7, выполненным в виде последовательно включенных задатчика 8 частоты и (К+1)-разрядного

двоичнаго счетчика 9. Управляющие входы плавно регулируемой ячейки 2 подключены к задающему генератору 7 через двухканальный фазосдвигающий узел 10, содержащий К-разрядные сумматоры 11 и 12 .и логические эле менты ИСКЛЮЧАЩЕЕ ИЛИ 13 И 14. Управляющие входы дискретно регулируемых ячеек 3 через одноканальные фаэореверсирующие узлы 15, выполненные на логических элементах ИСКЛЮЧАЮЩЕЕ ИЛИ, подключены к выходам старших разрядов формирователя 16 кода уп авляющего сигнала. Выход старшего разряда счетчика 9 подключен к нерегулируемьм ячейкам 1 и первым объединенным входам всез4 логических элементов ИСКЛЮЧАЮЩЕЕ ИЛ 13-15, Первые суммируняцие входы сумматоровИ и 12 подключены к выходам младших разрядов формирователя .16 кода управлякзщего сигнала. Второй суммирующий вход одного суммтора 11 подключен к прямым, другого сумматора 12 - к инверсным выходам К разрядов двоичного счетчика 9. Входы переноса сумматоров предназначены для подачи уровня логической единицы, выходы переноса подключены к вторым входам логических элементов 13 и 14 двухканального фазосдвигакзщего узла 10.

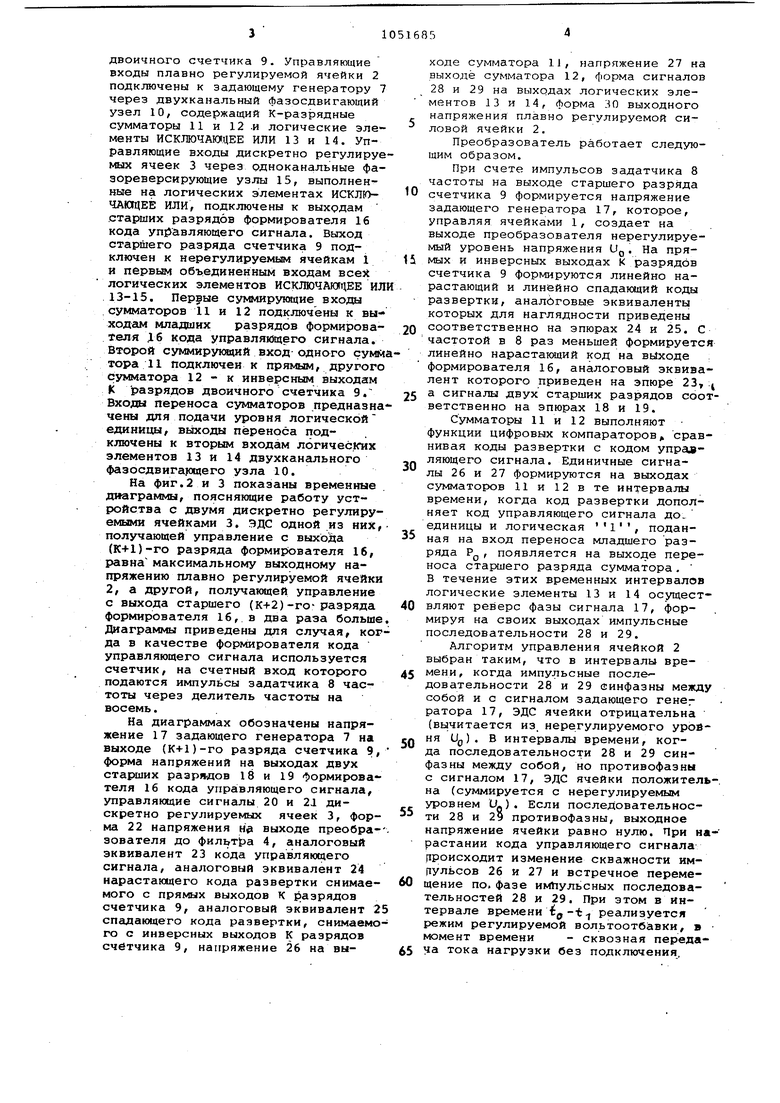

На фиг.2 и 3 показаны временные диаграммы, поясняющие работу устройства с двумя дискретно регулируемыми ячейками 3. ЭДС одной из них, получающей управление с выхода (К+1)-го разряда формирователя 16, равна максимальному выходному напряжению плавно регулиру-емой ячейки 2, а другой, получающей управление с выхода старшего (к+2)-го-разряда формирователя 16,.в два раза больше Диаграммы приведены для случая, когда в качестве формирователя кода управляющего сигнала используется счетчик, на счетный вход которого подаются импульсы задатчика 8 частоты через делитель частоты на восемь.

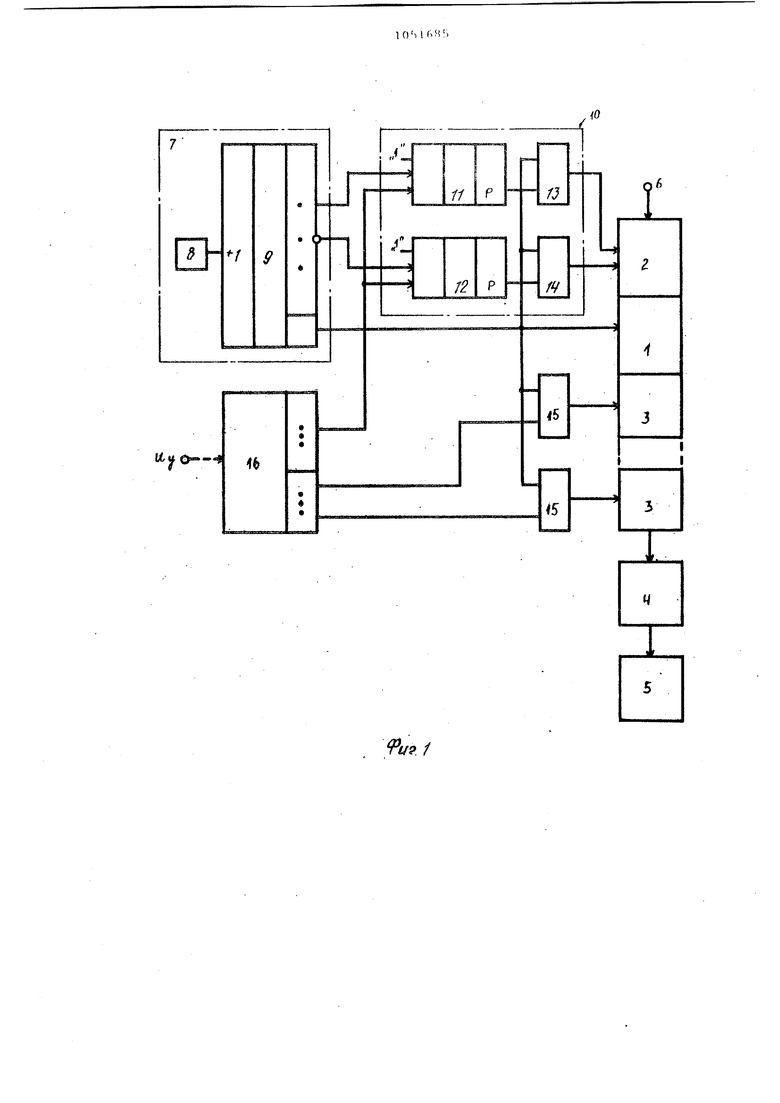

На диаграммах обозначены напряжение 17 задающего генератора 7 на выходе (К+1)-го разряда счетчика 9, форма напряжений на выходах двух старших разрядов 18 и 19 формирователя 16 кода управляющего сигнала, управляющие сигналы 20 и 21 дискретно регулируемых ячеек 3, форма 22 напряжения и выходе преобразователя до фильтЬа 4, аналоговый эквивалент 23 кода управляющего сигнала, аналоговый эквивалент 24 нарастающего кода развертки снимаемого с прямых выходов К разрядов счетчика 9, аналоговый эквивалент 2 спадающего кода развертки, снимаемого с инверсных выходов К разрядов счетчика 9, напряжение 26 на выходе сумматора 11, напряжение 27 на выходе сумматора 12, форма сигналов 28 и 29 на выходах логических элементов 13 и 14, форма 30 выходного напряжения плавно регулируемой силовой ячейки 2,

Преобразователь работает следующим образом.

При счете импульсов задатчика 8 частоты на выходе старшего разряда

0 счетчика 9 формируется напряжение задающего генератора 17, которое, управляя ячейками 1, создает на выходе преобразователя нерегулируемый уровень напряжения Ug. На пря5мых и инверсных выходах К разрядов счетчика 9 формируются линейно нарастающий и линейно спадающий коды развертки, аналоговые эквиваленты которых для наглядности приведены соответственно на эпюрах 24 и 25. С

0 частотой в 8 раз меньшей формируется линейно нарастакняий код на выходе , формирователя 16, аналоговый эквивалент которого приведен на эпюре 23 а сигналы двух старших разрядов соот5ветственно на эпюрах 18 и 19.

Сумматоры 11 и 12 выполняют функции цифровых компараторов„ сравнивая коды развертки с кодом управляющего сигнала. Единичные сигна0лы 26 и 27 формируются на выходах сумматоров 11 и 12 в те интервалы времени, когда код развертки дополняет код управляющего сигнала до, единицы и логическая , подан5ная на вход переноса младшего разряда Рд, появляется на выходе переноса старшего разряда сумматора. В течение этих временных интервалов логические элементы 13 и 14 осущест0вляют реверс фазы сигнала 17, формируя на своих выходах импульсные последовательности 28 и 29.

Алгоритм управления ячейкой 2 выбран таким, что в интервалы времени, когда импульсные после

5 довательности 28 и 29 синфазны между собой и с сигналом задающего гене ратора 17, ЭДС ячейки отрицательна (вычитается из. нерегулируемого уройня Up). В интервалы времени, ког0да последовательности 28 и 29 синфазны между собой, но противофазны с сигналом 17, ЭДС ячейки положитель-. на (суммируется с нерегулируемым уровнем и.). Если последовательнос5ти 28 и 29 противофазны, выходное напряжение ячейки равно нулю. При нарастании кода управляющего сигнала гроисходит изменение скважности им 1ульсов 26 я 21 ч встречное переме0щение по. фазе импульсных последовательностей 28 и 29. При этом в Интервале времени tp-t реализуется режим регулируемой вольтоотбйвки, в момент времени - сквозная передача тока нагрузки без подключения.

5 ЭДС ячейки, в интервале времени . - режим регулируемой вольтодобавки. Таким образом, предлагаемая структура обеспечивает работу преобразовательной ячейки с однополярной реверсивной модуляцией подобную .работе ячейки с использованием аналоговой развертки с тем отличием, что изменение фазы сигналов 26-30 . происходит не плавно, а ск чкообраз но на величину, кратную дискрете фазы, определяемой разрядностью кода развертки. Фазореверсирующие узлы 15 осущес вляют реверс фазы напряжения задающего генератора 17 в течение интервалов времени, когда сигналы на выходах старших разрядов 18 и 19 форм рователя 16 имеют единичное значени формируя на управляющих входах дискретно регулируемых ячеек 3 импуль ные последовательности 20 и 21. Алгоритм управления ячейками 3 такой, что если управляющий сигнал 20 (21) синфазен с сигналом 17 задающего генератора, ЭДС ячейки отрицательна (вычитается из-О), если сигнал 20 (21) и 17 противофазны - ЗДС ячей(и положительна (суммируется с t/o) . Та ким образом, уровням логического О сигналов 18 и 19 соответствуе режим полной вольтоотбавки соответс вующих ячеек 3, уровням логической Ч - режим полной вольтодобйвки. Поясним формирование результирую щей импульсной последовательности 2 преобразователя. Момент ёремени i,g соответствует нулевому коду формиррвателя 16, когда .напряжения, на йсех его выходах соответствует уров О. Все регулируню логического 3 находятся в режим емые ячейки 2 и полной вольтоотбавки (выходное напряжение равно CJ(j-4U, где U - ЭДС ячейки 2). В интервале времени . ячейка 2 осуществляет плавное ШИМгрегулирование в двух зонах в соответствии с эпюрой 30, обеспечивая рост выходного напряжения до уровня . В момент времени ±2 п реключается в режим вольтодобавки дискретно регулируемая ячейка с ЭДС и (ее управляющий сигнал 20), а ячейка 2 переходит в режим полной вольтоотбавки (код младших К-разрядов формиродателя 16 снова становится нулевым), В интервале времени -tg -t плавное регулирование выходного напряжения до уровня (Jg осуществляется за счет ячейки 2. В момент времени tj на вольтодобавку переключается ячейка 3 с ЭДС 2 (ее управлякдаий сигнал 21), а ячейка 2 и ячейка 3 с ЭДС, равной Ъ, переходят в режим полной вольтоотбавки. С момента времени t обе ячейки 3 работают в режиме вольтодобавки, а момент времени 5 соответствует максимальной мощности в нагрузке, когда ЭДС всех ячеек 1-3 включены согласно.-Таким образом, при изменении кода управляющего сигнала от нулевого до максимального значения на выходе преобразователя реализуется многозонная импульсная модуляция, при которой регулирование осуществляется в комплексе: по амплитуде дискретно по зонам (в данном примере реализуется 8 зон) и плавно в каждой дискретной зоне с помощью т1ИМ. Функции формирователя 16 кода может выполнять АЦП (ана-лого-цифровой преобразователь). Таким образом, предлагаемое устройство может управляться как аналоговым сигналом Uy, так и непосредственно его кодом, например,при подключении к ЭВМ, что расширяет функциональные возможности преобразователя по сравнению с известным. Схема управления значительно упрощена и выполнена на цифровых элементах, обладающих по сравнению с аналоговыми большей помехоустойчивостью и надежностью. Схема управления преобразователем может быть выполнена на интегральных микросхемах без настройки, Е1егулиров ки и применения навесных элементов, что способствует серийной пригодности преобразователя. Применение дискретно регулируемых ячеек с выход-, ными напряжениями, пропорциональными весам двоичных разрядов, уменьшает число ячеек при заданном качестве регулирования. При кодовом управлении тремя регулируемыми ячейками реализуется 8, четырьмя - 16 зон регулирования, тогда как при обычном для реализации того же числа зон требуется соответственно 4 и 8 силовых ячеек.

:п

rj

//

/

/4/

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения с многозонной импульсной модуляцией | 1983 |

|

SU1343521A2 |

| Устройство для управления многоячейковым преобразователем напряжения | 1982 |

|

SU1072238A1 |

| Преобразователь напряжения с многозонной импульсной модуляцией | 1985 |

|

SU1259449A1 |

| Преобразователь напряжения с многозонной импульсной модуляцией | 1980 |

|

SU985772A1 |

| Устройство для управления преобразователем постоянного напряжения в постоянное | 1983 |

|

SU1144174A1 |

| Многозонный стабилизатор постоянного напряжения | 1990 |

|

SU1700544A1 |

| Устройство для управления 2 @ -ячейковым преобразователем напряжения | 1986 |

|

SU1327250A1 |

| Устройство для управления преобразователем напряжения | 1982 |

|

SU1156222A1 |

| Устройство для управления преобразователем напряжения с многозонной модуляцией | 1984 |

|

SU1356157A1 |

| Устройство для управления регулятором напряжения | 1982 |

|

SU1043809A1 |

1. ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ С МНОГОЗОИНОЙ ИМПУЛЬСНОЙ МОДУЛЯЦИЕЙ, содержащий последовательно соединенные между собой по выходу регулируемые и нерегулируемые преобразовательные ячейки, причем нерегулируемые ячейки связаны с задающим генератором непосредственно, одна плавно регулируемая ячейка через двухканальный фазосдвигающий.-. узел, а другие дискретно регулируемые ячейки - через одноканальные фазореверсирующие узлы, отличающийся тем, что, с целью упрощения, повышения надежности и расширения функциональных возможноетей, он снабжен формирователем кода управляющего сигнала, каждый канал двухканального фазосдвигающего узла содержит К-разрядный сумматор и логический злемент ИСКЛЮЧАЮЩЕЕ ИЛИ, оД ноканальный фазореверсирующий узел выполнен в виде логического элемента Иск;гОЧАЮ1ЦЕЕ или, а задающий генератор выполнен в виде последовательно соединенных задатчика частоты и (К+1)-разрядного двоичного счетчика, выход старшего разряда которого подключен к нерегулируекалм ячейкам и . первым объединенным входам всех логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем вторые входы одноканальных фазореверсирующих узлов г Ь подключены к выходам старших раз-, рядов формирователя кода управляющего сигнала, выходы его млгшших раз рядов подключены к первым суммирующим входам сумматоров, вторые входы которых подключены соответствен§ но к прямым и инверсным выходам К разрядов двоичного счетчика, вхо,цы переноса предназначены для подачи уровня логической единицы, выходы переноса подключены к зторам входам сл элементов ИСКЛЮЧАЮЩЕЕ ИЛИ двухканального фазосдвиггиощего узла. о 2. Преобразователь напряжения по п.1,о тлич ающи йс я тем, 00 что в замкнутых системах регулирования формирователь кода управляющего сл сигнала выполнен в виде ангшого-цифрового преобразователя, вход которого предиазначен для под;ключения к усилителю сигнгша ошибки.

ittto.

1Ф

1/ 1

Eh:

фие.2

I

Il

1

г

Авторы

Даты

1983-10-30—Публикация

1982-06-11—Подача