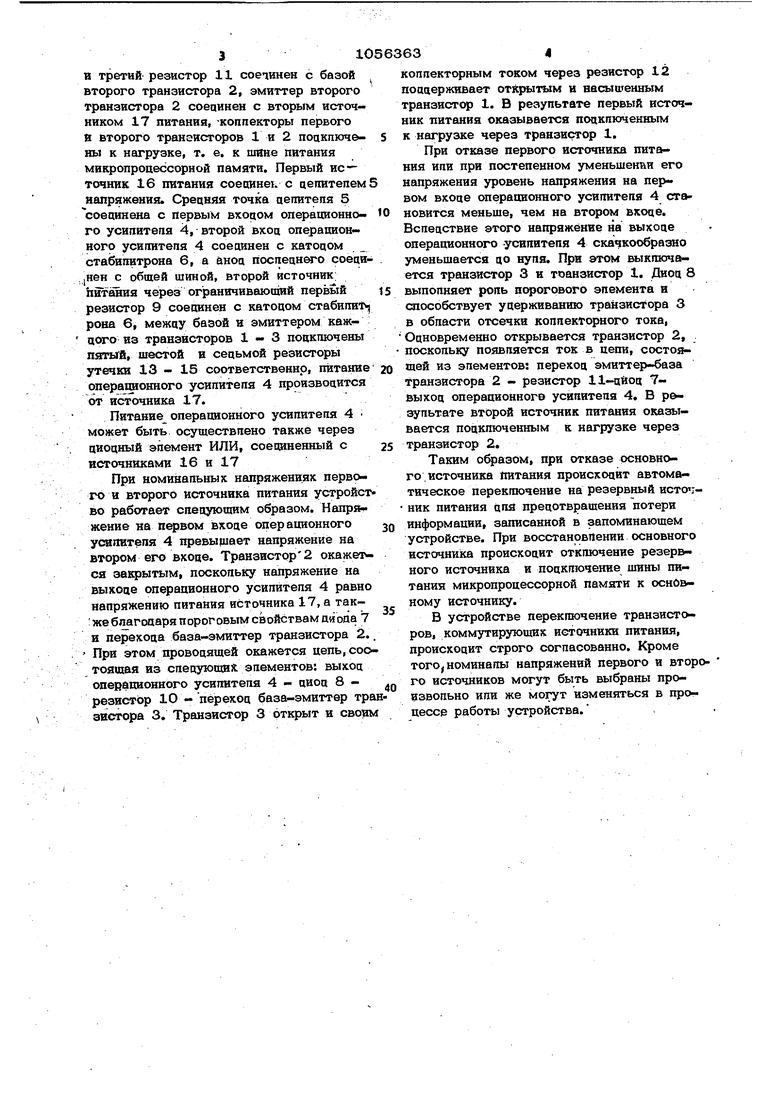

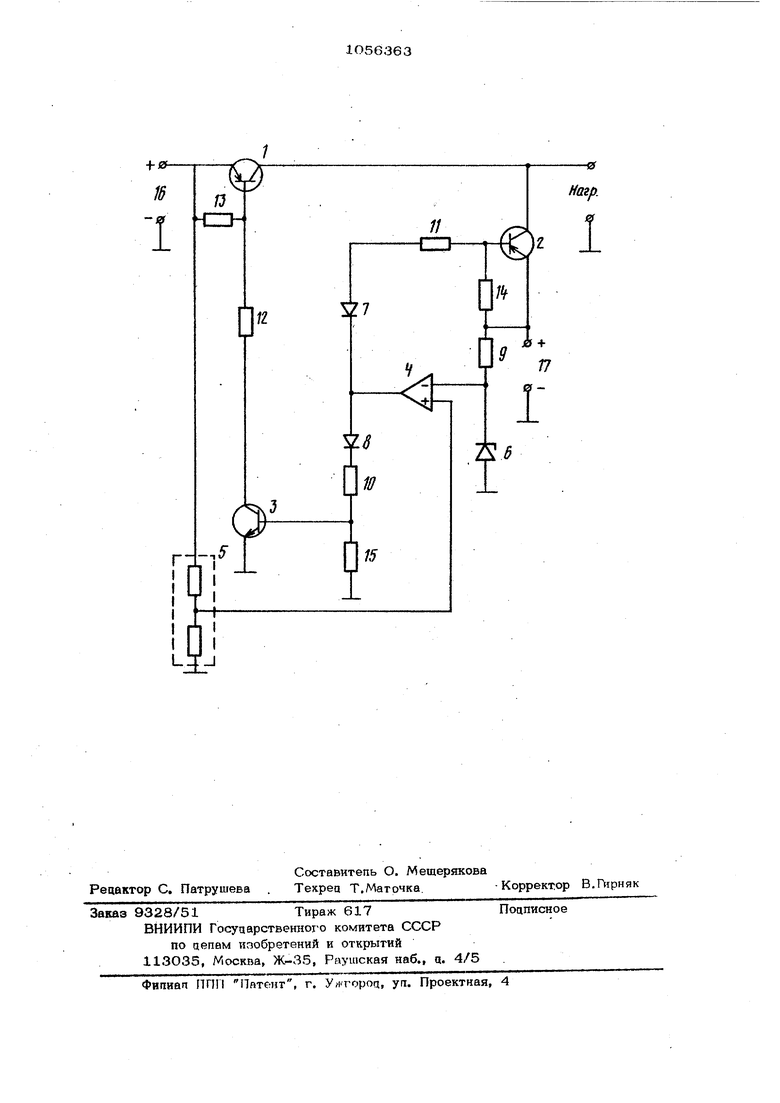

- Изобретение может быть использован в преобразо&атепяк энергии постоянного тока, в частности в источниках питания микропроцессорной памяти. Известно устройство цпя защиты памяти соцержащее ряц стабилитронов, цио цов и резисторов ..Недостатком известного устройства явпяется повышенный расход энергии. Наибопее бпизким по технической сущ .ности к предлагаемому явпяется устройство а ля зашиты бпока микропроцессорной памяти, соцержащее первый транзистор типа, эмиттер которого соецинен с первым источником питания, второй транзистор р-п-р типа, эмиттер которого соецинен с вторым источником питания, а коппектор соединен с коппект ром первого транзистора и шино питани микропроцессорной па. цепитепь .напр жения подключен к первому источнику пи танин, база второго транзистора соецинена с срецней точкой цепитепя напряж ния, база первого транзистора через резистор соединена с вторым источником питания 2 .. В известном устройстве при отказе первого источника питания происхоаит автоматическое перекпючение на второй источник питания. При этом включается первый транзистор и включается второй транзистор. Первый транзистор выключае ся, когда напряжение первого источника становится меньше, чем, напряжение второго источника. При этом нео хоци- МО укатывать пацение напряжения на перехоце база-эмиттер первого транзисто ра и на его базоввм резисторе. Второй транзистор включается, когца напряжение на средней точке цепитепя напряжения (по абсолютной величине) становится, больше, чем напряжение на его эмиттера. При этом необкоцимо учитывать паце ние на переходе база эмиттер второго транзистора. Иа этого спецует, что выключений первого транзистора и вкпюче ние второго транзистора опрецепяются :разными параметрами, разных элементов. Поэтому при некотором соотношении напряжений источников питания и величин резисторов оба транзистора .могут оказаться выключенными или же оба транзйстора могут оказаться включенными. В первом случае у потребителя исчезает напряжение питания. Во втором случае второй транзистор оказывается открытым инверсно. И. в первом и во втором случае снижается надежность устройства. Цель изобретения - повышение нааеж ности и расширение функциональных. возможностей. Поставленная цепь достигается тем, что в устройство цля резервного энергоснабжения блока микропроцессорной памяти, содержащее первый транзистор р-п-р . типа, эмиттер которого предназначен цпя подклкучения к первому источнику питания, второй транзистор р-п-р типа, эмиттер которого ярецназначен азя подключения к второму источнику питания, а коллектор соецинен с коллектором перового транзистора р-п-р типа и шиной питания микропроцессорной памяти, делитель напряжения, предназначенный для подключения к первому источнику питания, введены транзистор, п-р-п типа, операционный усилитель, стабилитрон, два диода и семь резисторов, причем первый вход операционного усилителя соединен с средней точкой целителя напряжения, второй вход операционного усилителя соединен с катодом стабилитрона и через первый резистор предназначен цпя покпючения к второл источнику питания, анод стабилитрона соединен с общей шиной, выход операционного усилителя через первый диод и второй резистор: соединен с базой транзистора п-р-птипа, fit череа второй диод и третий резистор - с базой второго транзистора типа р-п-р, при этом эмиттер транзистора п-р-п типа соединен с общей шиной коллектор через четвертый резистор соединен с базой первого транзистора р-п-р типа, а между базой и sMHTTepoM KaM-i цого транзистора включены соответственно пятый, шестой и седьмой резисторы На чертеже представлено предлагаемое устройство. Устройство содержит первый и второй транзисторы 1,2 р-п-р тина, TpaH3HCTOp j3w п-р-п .(Типа, операционный усипитепь 4, делитель 5 напряжения, стабилитрон 6, первый и второй диоды 7 и 8, с первого , по четвертый резисторы 9-12 ограничи ваюшие пятый, шестой и седьмой рёзиоторы 13 - 15 резисторы утечки, первый и второй источники 16 и 17 питания, причем первый источник 16 питания соецинен с эмиттером TpaHSHcl-opa 1. База первого транзистора 1 соединена с коплектом. ром транзистора 3 через четвертый резисToji) 12,эмиттер транзистора 3 соединен с общей Шиной,а его база через второй резистор 1р, второй ДИОП1 8 соединена с выходом операционного ус«литепя 4, выход операционного усилителя 4 через первый диод 7 и третий резистор И соединен с базой второго транзистора 2, эмиттер второго транзистора 2 соединен с вторым источником 17 питания, -коппекторы первого и второго транзисторов 1 и 2 поакпюч&ны к нагрузке, т. е. к шине питания микропроцессорной памяти. Первый источник 16 питания соевинек с цетгатепем напряжения. Срецняя точка цепитепя 5 соединена с первым вхоцом операционного усипитепя 4, второй вхоц операционного усипитепя 4 соединен с катодом стабилитрона 6, а анод последнего соеди |Нен с общей шиной, второй источник питания через ограничивающий первый резистор 9 соединен с катодом стабипитрона 6, между базой и эмиттером каждого из транзисторов 1-3 подключены пяпый, шестой в седьмой резисторы утечки 13 - 15 соответственно, питание операшонного усипитепя 4 производится от источника 17. Питание операционного усипитепя 4 может быть осуществлено также через диодный элемент ИЛИ, соещиненный с источниками 16 и 17 При номинальных напряжениях первого и второго источника питания устройст во работает следующим образом. Напри жение на первом входе операционного усяпвтепя 4 превышает напряжение на втором его входе. Транзистор2 окажет ся закрытым поскольку напряжение на выходе операционного усилителя 4 равно напряжению питания источника 17, а так же благодаря пороговым свойствам ди ода 7 и перехода база-эмиттер транзистора 2. При этом проводящей окажется цепь, соо тоящая из следующих элементов: выход опевационного усилителя 4 - диод 8 резистор 10-переход база-эмиттер тра зистора 3. Транзистор 3 открыт и своим 10 634 коллекторным током через резистор 12 поддерживает открытым и насышенным транзистор 1. В результате первый источник литания оказывается подключенным к нагрузке через транзистор 1. При отказе первого источника питания или при постепенном уменьшении его напряжения уровень напряжения на пер вом входе операционного усилителя 4 становится меньше, чем на втором входе. Вследствие этого напряжение на выходе операционного -усилителя 4 скачкообразно уменьшается до нуля. При этом выключается транзистор 3 к тоанзистор 1. Диод 8 выполняет роль порогового элемента и способствует удерживанию транзистора 3 в области отсечки коллекторного тока. Одновременно открывается транзистор 2, поскольку появляется ток в цепи, состоящей из элементов: переход эмиттер- за транзистора 2 - резистор 11-дйод 7выход операционноге усилителя 4. В р& льтате второй источник питания оказывается подключенным к нагрузке через транзистор 2. Таким . При отказе основного, источника питания происходит автоматическое переключение на резервный источник питания Для предотвращения потери информации, записанной в запоминающем устройстве. При восстановлении основного источника происходит отключение резервного источника и подключение шины питания микропроцессорной памяти к основному источнику. В устройстве переключение транзисторов, коммутирующих источники питания, происходит строго согласованно. Кроме того, номиналы напряжений первого и второго источников могут быть выбраны произвольно или же могут изменяться в процессе работы устройства.

HJ&ю

/3

1

3Z7

/Z

-&

Нагр.

//

у

D ;

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговый ключ | 1982 |

|

SU1026310A1 |

| Дифференциальный усилитель (его варианты) | 1981 |

|

SU1045349A1 |

| Стабилизатор повышенного напряжения постоянного тока | 1982 |

|

SU1086415A1 |

| Формирователь импульсов | 1982 |

|

SU1086418A1 |

| УСТРОЙСТВО РЕЗЕРВНОГО ЭЛЕКТРОПИТАНИЯ | 2011 |

|

RU2474028C1 |

| Формирователь сигнала для выборки элементов матрицы | 1982 |

|

SU1045364A1 |

| УСТРОЙСТВО ДЛЯ РЕЗЕРВНОГО ЭЛЕКТРОСНАБЖЕНИЯ | 2011 |

|

RU2446541C1 |

| Двухполярный источник опорного напряжения | 1981 |

|

SU1051513A1 |

| Стабилизирующий преобразователь постоянного напряжения в постоянное | 1988 |

|

SU1629902A1 |

| Стабилизатор постоянного напряжения | 1981 |

|

SU1032438A1 |

УСТРОЙСТВО ДЛЯ РЕЗЕРВногоэнертхх:НАБ:«Ения влокд МИКРОПРОЦЕССОРНОЙ ПАМЯТИ, с од8ржаще-з первый транзистор типа, эмиттер которого прецназначен цпя поцкпючения к первому источнику питания, второй транзистор р-п-р типа, эмиттер которого предназначен цпя поцкпючения к второму истрчнику питания, а коппектор соединен с коллектором первого транзистора f)-n-p типа, и шиной питания микропроцессорной памяти, цепитепь напряжения, прецназиаченный апя поцкпючения к первому иствчнику питания отличающееся тем, что, с пепью повышения нацежностк и расширения функиионапькых возможноотей, в него ввецены транзистор п-р-« типа, операционный усилитель, стабилитрон, цва циоаа и семь резисторов, причем первый вхоа операционного усилителя соединен с средней точкой ценителя иапр жения, второй вхоа операционного усипитепя соединен с катоцом стабипитрона и через первый резистор прецназначен для подключения к второму источнику питания, аноц стабилитрона соединен с о&щей шиной, выхоц операционного усилителя через первый циоц и второй резистор i соецинен с базой транзистора п-р-п TIPпа,а через второй диоц и третий резис (Л тор - с базой второго транзистора р-п-р типа, при этом эмиттер транзистос ра п-р-п типа соединен с обшей шиной, коллектор, через четвертый резистор соецинен с базой первого транзистора р-п-р типа, а межцу базой и эмиттером кажцо го транзистора включены соответствен но пятый, шестой и седьмой резисторы. ел at 00 О5 00

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бепецкий В | |||

| В | |||

| Теория и практические метоцы резервирования рааиоэпект ронной аппаратуры | |||

| М., Знергия, 1977, с | |||

| Способ изготовления гибких труб для проведения жидкостей (пожарных рукавов и т.п.) | 1921 |

|

SU268A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Эпектроника, № 3, т | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1983-11-23—Публикация

1982-07-12—Подача