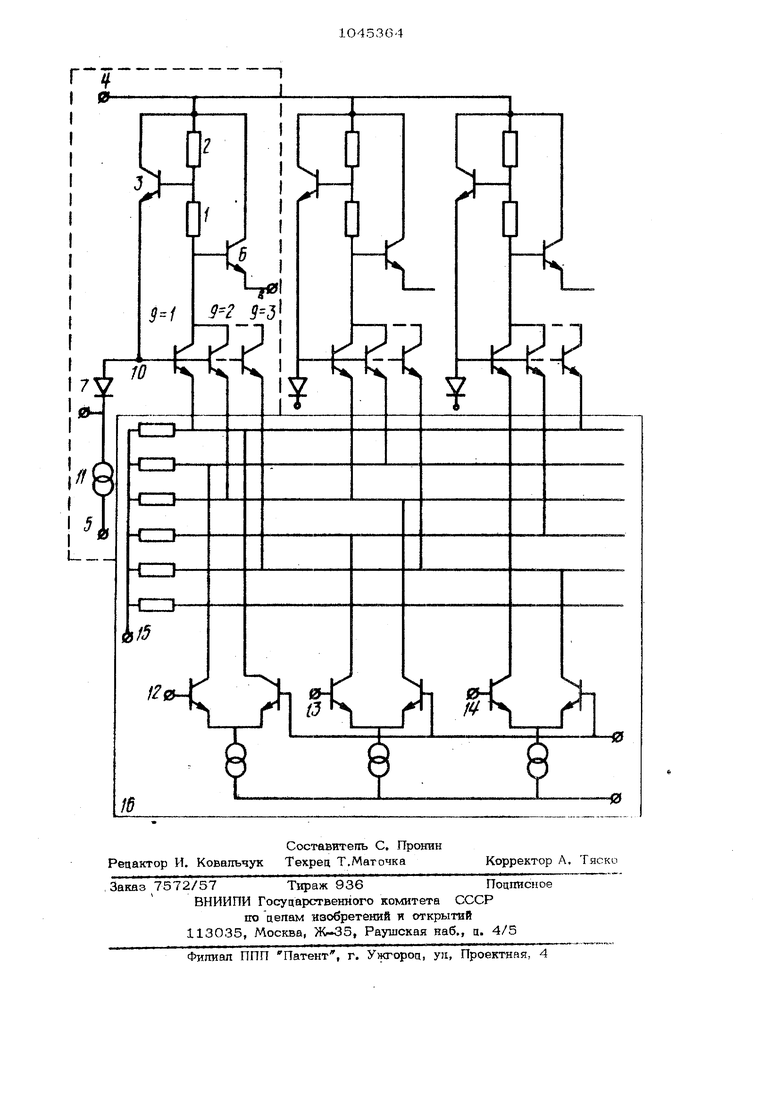

Изобретение относится к имггупъсной и вычистгатепьной технике и преаиазнач& но цпя испопьзования в качестве оцного из эпементов управпения матрицей накопитепя памяти интегрального запоминающего устройства. Известен цешифратор, состоящий из И -а феснык вхоаных устройств, прецставпяющих собой эмиттерые повторитегга кажпый из которых поцкпючен к вхоцу ЭСЛ инвертора П Однако в ианном устройстве высокие логические перепаоы, приводящие к недостаточно высокому быстродействию. Наиболее близким по технической сущности к предлагаемому является формирователь сигнала выборки ипи невыборки на iJJMiie матрицы накопителя, содержащий выхоцной транзистор, цва резистора и Vi входных транзисторов, базы которых объецинены, коллекторы, поцключе1Ш1 к базе выходного транзистор и через последовательно соециненные первый и второй резисторы к ипшо питания, эмиттеры входных транзисторов соединены с вxoдa iи, эмиттер выходной го транзистора подкточен к выходной шине 2 3 Недостатком прототипа является на сыщенный режим работы транзисторов и низкое быстродействие. Цель изобретения - повышение быстро действия. Поставленная цель достигается тем, что формирователь сигнала для выборки эпементов матрицы, содержащий выходно транзистор, два резистора и И входных транзисторов, базы которых объединены, коллекторы подключены к базе выход ного транзистора и через поспедоватегаьн соединенные первый и второй резисторы к шине питания, эмиттеры Входных транзисторов соединены с входами, эмиттер выходного транзистора подключен к выхо ной шине, дополнительно содержит транзистор, диоц и источник тока, выход источника тока соединен с катодом циоца, анод.которого подключен к эмиттеру транзистора и базам входных транзисторов, коплектор транзистора соединен с шиной питания, база - с общим выводом первого и второго резисторов. На чертеже показано устройстйЬ вы борки эпементов, матрицы, в котором используется предлагаемый формирователь. Формирователь содержит резисторы 1 и 2, дополнительный транзистор 3, шины 4 и 5 питания, выходной транзио642тор б, диоц 7, выходную тину 8, входные транзисторы , базовый вывод 10, источник 11 TOKQ, входные шины 12 - 14 дешифратора, источник 15 смешения, дешифратор 16, Формирователь сигнала работает следующим образом. Пусть на входные щинъ: 12 - 14 д&шифратора - поступает комбинация транзнсторов. Тогда ток в коллекторной ВХОШ1ЫХ транзисторов отсутствует и через резисторы 1 и 2 текут только базовые токи транзисторов 3 и 6. На шине 8 матрицы накопителя формируется высокий потенхшал, величина которого ниже величины потенциала шины 4 питания на величину падений напряжения на резисторах 1 и 2 за счет протекания базовых токов транзисторов 3 и 6 и в личину падения напряжения на открытом переходе база-эмиттер транзистора 6. В( выбранном канале через транзистор 3 и диод 7 течет ток источника 11 тока и на выводе 10 формируется потенциал ниже потенциала на шине 4 питания на величину падения напряжений на резисторе 2 за счет протекания базовых токов транзисторов 3 и 6 и открытом переходе база-эмиттер транзисторов 3, а на эмиттерах входных транзисторов формируется потенциал, равный напряжению источника смешения, подключенного к шине 15. Величина источника смещения должна быть не более чем на 0,4 В ниже потенциала на выводе 10, чтобы обеспечить надежное запирание входного транзистора в режиме выборки. Если на входы дешифратора подается такая комбинация логических сигналов, что ток протекает хотя бы через один входной транзистор, то за счет протекания тока в цепи входной транзистор, резистор 1 на выводе 8 фор1 1ируется низкий потенциал ниже потенциала шины 4 питания на величину падений напряжений :на резисторах 2 и 1 за счет протекания коллекторного тока входных транзисторов я базовых токов транзисторов 3j 6 и падения напряжения на открытом переходе база-эмиттер транзистора 6. В результате логический перепад между состояниями выборки и невыборки на выходной шине 8 формируется в оа новном на резисторе 1 за счет протека кия ипи отсутсвия тока в резисторе 1 и на резисторе 2 за счет разницы токов в режимах выборки и невыборки. В невыбранном канапе через транзистор 3 и диод 7 течет базовый ток входных тран3Юзисторов и на вывопе Ю формируется потенш1ап ний;е потенштапа ишны питания 4 но, сгу птарную вет1чину падений напр женнй на резисторе 2 за счет прот кания в основном коппекторного тока вхоцных транзисторов и на открытом перекопе база-эмиттер транзисторов 3. На эмиттере вхоциого транзистора, по которому протекает ток, формируется потенциал ниже потенциала на выводе 10 на величину падения напряжения на открытом переходе база-эмиттер вхоцно гъ транзистора. В результате погичеокий перепад на эмиттере BxotjHoro транзистора можно сделать меньше величины равной половине величины падения напряжения на открытом переходе база-эмит тер. В зависимости от комбинации логических сигналов на входах дешифратора 12 - 14 можно проводить разное копичество входны транзисторов в одном И - вентиле. При этом суммарный ток в резисторе 1 при невыборке слабо от лкчаётся для любой комбинации сигналов на входе дешифратора иэ-за наличия дополнительной цепи на транзисторе 3, резисторе 2, диоде 7, осуществляющей отрицательную обратную связь следуюпшм образом: увеличение тока в резисторах 1 и 2 вызывает понижение потенциала на базе транзистора 3, затем понижение потенциала на выводах 10, т. е. понижение потенциала на базах входных транзио 644 торов, что прквоант к уменьшению тока во входных транзисторах вентиля И. В режик е переключения переходный процесс на эмиттерах входных транзисторов проходит значительно быстрее уме}гьшения логического перепада на них с 2, О до 0,4 В. Переходный процесс в схеме проходит достаточно быстро, когда суммарная емкость в коллекторном узпе входных транзисторов близка по ъв личине к суммарной емкости в узпе поцключения эмиттера входного транзиотора. Если суммарная емкость в Konrteifrторном узле входных транзисторов значительно больше, чем в эмиттерном, то для увеличения быстродействия необходимо поставить развязывающий транзистор. Таким образом, поскольку формирование сигнала выборки и невыборки осущест вляется в определенных узлах электричеокой схемы при меньших логических пере. . падах, чем у прототипа, достигается более высокое быстродействие при той же потребляемой мощности. . В предлагаемом формирователе по сравнению с прототипом повышается быстрооействие на 20% при той же потребляемой мощности. Внедрение изобретения позволяет улучшить йоказателн ЗУ (по времени выборки //адреса) и увеличить технл логические запасы по этому параметру.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигнала выборки шины матрицы накопителя | 1981 |

|

SU1027824A1 |

| Формирователь сигнала | 1983 |

|

SU1170593A1 |

| Мультиплексор | 1986 |

|

SU1378048A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Логический переключающийэлЕМЕНТ | 1979 |

|

SU849489A1 |

| Дешифратор | 1986 |

|

SU1336251A1 |

| Формирователь уровня считывания | 1984 |

|

SU1244718A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Формирователь сигналов выборки | 1985 |

|

SU1336099A1 |

| Формирователь импульсов | 1982 |

|

SU1086418A1 |

ФОРМИРОВАТЕЛЬ СИГНА ЛА ВЫБОРКИ ЭЛЕМЕНТОВ МАТРИЦЫ, содержащий выходной транзистор, цва резистора и ц входных транзисторов, базы которых объецинены, коппекторы поцкпючены к базе выкоцного транзистора и через поспецоватепьно соециненные первый и второй резисторы к ишне питания, эмиттеры входных: транзисторов со&цинены с вкоцами, эмиттер выхоцного транзистора подключен к выходной шине, отличающийся тем, что, с цепью увеличения быстродействия, он дополнительно содержит транзистор, циоц и источник тока, причем выход источника тока соединен с катодом оиода, которого подключен к эмиттеру транзистора и базам входных транзисторов, коллектор транзистора соецинен с шиной питания, база - с общим выводом первого и второго резисторов

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ сбора и удаления отходов из емкостей | 1986 |

|

SU1489861A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для увеличения сцепной силы тяги паровозов и других повозок | 1919 |

|

SU355A1 |

| Парный автоматический сцепной прибор для железнодорожных вагонов | 0 |

|

SU78A1 |

Авторы

Даты

1983-09-30—Публикация

1982-04-21—Подача