Изобретение относится к автоматике и вычислительной технике и может быть использовано, в частности, в системах контурного программного управления перемещениями исполнительных органов станков и технологического оборудования.

Известны линейно-круговые интерполяторы [1] , содержащие координатные каналы с перекрестными обратными связями, выполненными на базе накапливающих сумматоров, и осуществляющие в процессе своего функционирования для упрощения интерполятора нормализацию входных кодов относительно емкости Z накапливающих сумматоров путем умножения входных кодов на коэффициент 2n, но при этом для импульсных последовательностей на выходах координатных каналов, период следования Т которых определяется выражением T = int  , где int { } - целая часть, выражения в скобках;

, где int { } - целая часть, выражения в скобках;

Δ - выходной код управления интерполяцией координатного канала;

τ - период следования импульсов тактовой частоты, период Т имеет большую погрешность относительно номинального значения, вызывая увеличение погрешности воспроизведения координатных составляющих контурной скорости, что приводит к увеличению и накоплению по ходу отработки перемещения погрешности интерполяции.

Известен линейно-круговой интерполятор [2] , содержащий блок ввода информации, регистр длины отрезка, блок задания скорости, два блока суммирования и вычитывания, два регистра памяти, два регистра суммы, две схемы совпадения, два вторых блока суммирования и вычитания, два блока сравнения.

Для выполнения линейной интерполяции в устройстве задаются исходные данные: величина перемещения Δ х по координате х, величина перемещения Δ у по координате у, величина перемещения l в заданном направлении, контурная скорость, в соответствии с которой блок задания скорости вырабатывает импульсную последовательность частотой следования Fk. Для выполнения круговой интерполяции задаются следующие исходные данные: координаты хн, ун начальной точки перемещения относительно центра окружности, радиус R окружности, контурная скорость, определяемая как и в случае линейной интерполяции частотой Fk импульсов на выходе блока задания скорости.

В каждом координатном канале совокупность регистра памяти, схемы совпадения, второго блока суммирования, регистра суммы, блок сравнения и второй схемы совпадения образует управляемый делитель частоты с дробным коэффициентом деления, выполняющий преобразование в соответствии с общим выражением

F =  · f, N≅ Z, где F и f - выходная и входная частоты импульсов управляемого делителя соответственно,

· f, N≅ Z, где F и f - выходная и входная частоты импульсов управляемого делителя соответственно,

N, Z - входные управляющие коды, и формирующий на временном масштабе Z·  = Z·τ N выходных импульсов, неравномерность следования Δ Т которых не превышает периода следования τ входных импульсов за счет учета остатка от деления Z на N в циклах преобразования управляемого делителя. При этом обеспечивается точное воспроизведение интегрального значения заданной скорости в виде N выходных импульсов перемещения на временном масштабе Z τ , но вместе с тем имеет место неравномерность следования выходных импульсов. Относительная неравномерность

= Z·τ N выходных импульсов, неравномерность следования Δ Т которых не превышает периода следования τ входных импульсов за счет учета остатка от деления Z на N в циклах преобразования управляемого делителя. При этом обеспечивается точное воспроизведение интегрального значения заданной скорости в виде N выходных импульсов перемещения на временном масштабе Z τ , но вместе с тем имеет место неравномерность следования выходных импульсов. Относительная неравномерность ≅

≅  =

=  и может достигать максимальных значений для

и может достигать максимальных значений для  , близких к единице.

, близких к единице.

Известный интерполятор вырабатывает на своих выходах импульсные последовательности с частотами Fх, Fy, являющиеся проекциями контурной скорости Fk на соответствующие координатные оси в случае линейной интерполяции

Fx=  Fк;

Fк;

Fy=  Fк,

Fк,

в случае круговой интерполяции

F =

=  Fк; ; yo = yн;

Fк; ; yo = yн;

F =

=  Fк; ; xo = xн, i = 0,1,2, . . . , где хi, yi - текущие координаты точек интерполяции окружности относительно ее центра, изменяющиеся во времени за счет обратных связей с выходов устройства по каждой координате на первые блоки суммирования и вычитания противоположной координаты.

Fк; ; xo = xн, i = 0,1,2, . . . , где хi, yi - текущие координаты точек интерполяции окружности относительно ее центра, изменяющиеся во времени за счет обратных связей с выходов устройства по каждой координате на первые блоки суммирования и вычитания противоположной координаты.

Недостатком известного линейно-кругового интерполятора является значительная неравномерность следования выходных импульсов в связи с относительно низкими значениями частоты и близкими в общем случае к единице значениями  ,

,  ,

,  ,

,  (для круговой интеpполяции имеется ввиду нерегулярность мгновенных выходных частот - координатные частоты меняются в этом случае от 0 до Fk), что ограничивает функциональные возможности интерполятора, поскольку не позволяет использовать его при работе в системе с дискретным приводом на частотах вне диапазона приемистости, требующих для их достижения реализации режима разгона-торможения. Известное устройство имеет также недостаточно высокую точность интерполяции.

(для круговой интеpполяции имеется ввиду нерегулярность мгновенных выходных частот - координатные частоты меняются в этом случае от 0 до Fk), что ограничивает функциональные возможности интерполятора, поскольку не позволяет использовать его при работе в системе с дискретным приводом на частотах вне диапазона приемистости, требующих для их достижения реализации режима разгона-торможения. Известное устройство имеет также недостаточно высокую точность интерполяции.

Целью изобретения является расширение частотного диапазона интерполятора, расширение его функциональных возможностей и точности интерполяции.

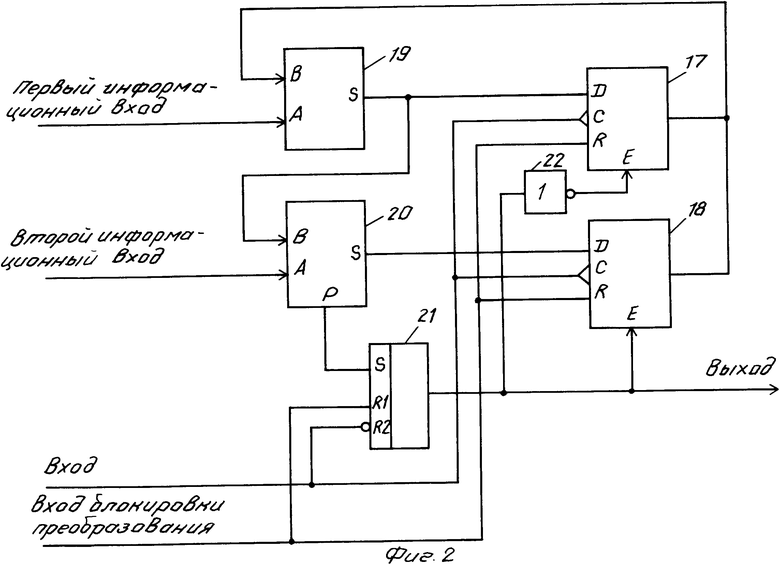

Управляемый делитель частоты с дробным коэффициентом деления содержит два регистра с тремя состояниями выходов, два сумматора, триггер, инвертор, первый и второй регистры, информационными входами подключенные к выходам первого и второго сумматоров соответственно, выходами - к второму входу первого сумматора, выходом подключенного к второму входу второго сумматора, выходом переполнения соединенного с входом установки триггера, выполненного с приоритетным состоянием сброса, выходом, являющимся выходом управляемого делителя частоты, соединенного с входом разрушения чтения второго регистра непосредственно, а первого регистра через инвертор, при этом первый вход сброса триггера соединен с входами сброса регистров и является входом блокировки преобразования, второй инверсный вход сброса триггера соединен с синхровходами записи регистров и является входом управляемого делителя частоты, первые информационные входы первого и второго сумматоров являются первыми и вторыми информационными входами управляемого делителя частоты соответственно.

Формирователь сигналов сканирования кода скорости содержит реверсивный счетчик импульсов, задатчик кода ускорения, блок совпадения кодов, счетчик импульсов, задатчик кода максимальной скорости, два блока сравнения, два триггера, элемент ИЛИ, два элемента И, реверсивный счетчик импульсов, счетный вход которого является входом, первый вход сброса - входом управления, второй вход сброса, соединенный с входами установки триггеров и входами записи задатчиков, - входом записи, третий вход сброса, соединенный с выходным элементом ИЛИ, - первым выходом формирователя, входом направления счета, причем реверсивный счетчик импульсов, соединен с выходом второго триггера, выходом переполнения при счете на вычитание - с синхровходом второго триггера и первым входом элемента ИЛИ, выходом - с первым входом блока совпадения кодов, вторым входом соединенного с выходом задатчика кода ускорения, выходом, являющимся третьим выходом формирователя, - с вторым входом элемента ИЛИ, третьим входом соединенного с выходом первого элемента И, первым входом соединенного с первым выходом первого блока сравнения кодов, первый вход которого является первым информационным входом формирователя, второй вход соединен с выходом задатчика кода максимальной скорости, второй выход соединен с первым входом второго элемента И, третий выход - с входом блокировки сброса второго триггера и входом блокировки счетчика импульсов, счетный вход и вход сброса которого являются счетным входом и входом запуска формирователя соответственно, а выход соединен с первым входом второго блока сравнения кодов, второй вход и вход стробирования которого являются вторым информационным входом и входом стробирования формирователя соответственно, а выход соединен с первыми входами сброса триггеров, вторыми входами сброса подключенных к линии сигнала "Торможение", первый триггер выходом соединен с вторыми входами элементов И, выход второго элемента И является вторым выходом формирователя.

Формирователь сигналов управления кадра содержит схему запуска отработки кадра , формирователь конца кадра, регистр, три элемента И, схему запуска, синхровход которой является синхровходом, первый и второй выходы - первым и вторыми выходами формирователя соответственно, вход соединен с выходом формирователя сигналов конца кадра, первый и второй входы которого являются первым и вторым входами формирователя соответственно, а первый и второй входы управления соединены с первым и вторым выходами регистра соответственно, входом записи подключенного к второму выходу схемы запуска и первым входам второго и третьего элементов И, вторым и третьим выходами - к входам первого элемента И соответственно, выход которого является третьим выходом, при этом первый выход регистра, выходы второго и третьего элементов И являются четвертым, пятым и шестым выходами формирователя соответственно, первый, второй, третий выходы регистра, вторые входы второго и третьего элементов И подключены к сигнальным линиям "Диапазон приемистости", "Отработка заданного перемещения", "Разрешение отработки торможения", "Разрешение записи кода скорости", "Запуск счетчика пути разгона" соответственно.

В предлагаемом линейно-круговом интерполяторе наличие в каждом координатном канале первого и второго делителя частоты, имеющих коэффициенты деления 2n1 и 2n2 соответственно, подключение задатчика кода скорости перемещения к информационному входу преобразователя код-частота со сдвигом (n1 + n2) в сторону старших разрядов, подключение (n1 + n2) младших разрядов информационного входа преобразователя код-частота к нулевой информационной шине позволяют минимизировать неравномерность следования выходных импульсов координатных перемещений интерполятора и расширить область частот корректурного функцио- нирования при введении в состав интерполятора формирователя сканирования кода скорости и выполнении задатчика кода скорости перемещения в виде реверсивного счетчика импульсов. Подключение в каждом координатном канале второй информационной шины соответствующего канала к информационному входу задатчика кода и направления перемещения и выхода регистра к второму информационному входу управляемых делителей частоты с дробным коэффициентом деления каждого канала со сдвигом n2 в сторону старших разрядов с подключением n2 младших разрядов этих входов к нулевой информационной шине, подключение счетного входа задатчика кода и направления перемещения каждого канала к выходу первого делителя частоты противоположного канала позволяют путем увеличения частоты функционирования координатных каналов интерполятора в 2n2 раз и соответствующего уменьшения дискреты интерполяции повысить точность интерполяции.

Введение в состав интерполятора формирователя сигнала знака круговой интерполяции позволяет расширить диапазон отрабатываемых заданных перемещений путем автоматической смены в процессе круговой интерполяции состояния направления счета задатчиков кода и направления перемещения координатных каналов.

Наличие в предлагаемом интерполяторе коммутатора, производящего при необходимости переключение выходных сигналов координатных каналов, позволяет минимизировать величину погрешности интерполяции, выполняемой с использованием режима разгон-торможение, осуществляя управление формирователем сигналов при сканировании кода скорости каналами первого координатного канала, для которого задается отработка перемещения, по координате с большим заданным перемещением.

Введение в координатные каналы элемента И, блокирующего счет импульсов счетчиком по достижении им нулевого состояния, предотвращает отработку лишних импульсов перемещения из-за наличия погрешности круговой интерполяции и линейной интерполяции с использованием режима разгона-торможения.

Выполнение преобразователя код-частота в виде управляемого делителя частоты с дробным коэффициентом деления позволяет избежать повышения погрешности формирования унитарного кода скорости при увеличении его в 2(n1+n2) раз.

Вариант выполнения формирователя сигналов сканирования кода скорости и введение в интерполятор формирователя сигнала управления кадра, второго элемента И позволяют расширить функциональные возможности интерполятора введением режимов отработки безразмерных перемещений, завершающихся по внешним управляющим сигналам, отработки перемещений с чередованием кадров с движением на постоянной скорости и с ускорением.

Аналоги предлагаемого технического решения не имеют с ним общих признаков, отличающих заявляемое решение от прототипа, в связи с чем предлагаемое решение обладает существенными отличиями.

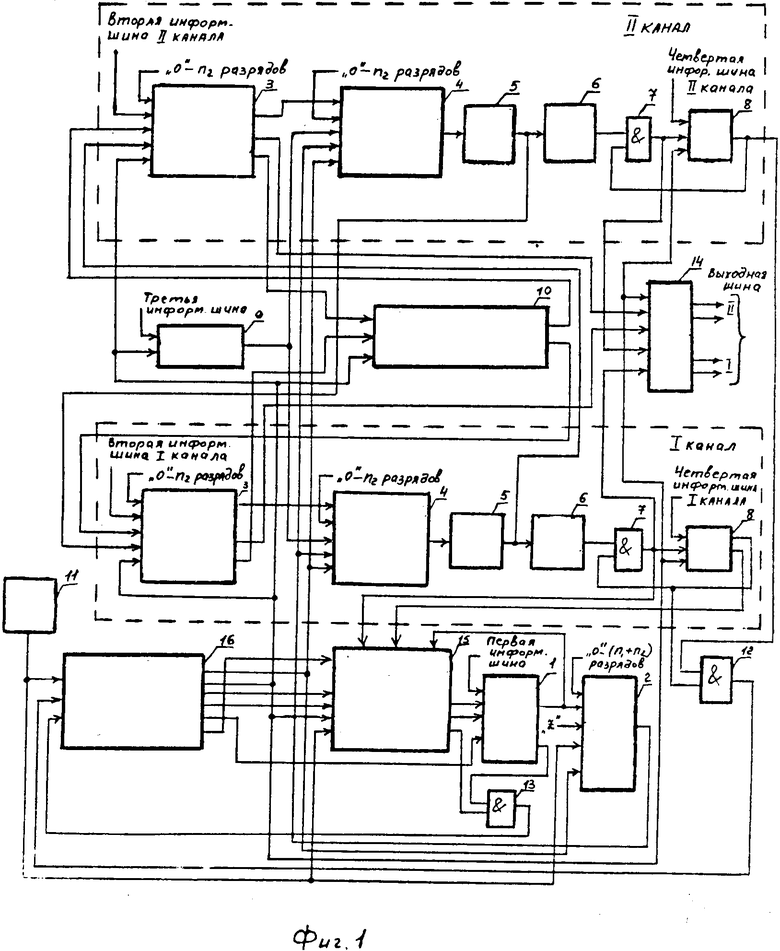

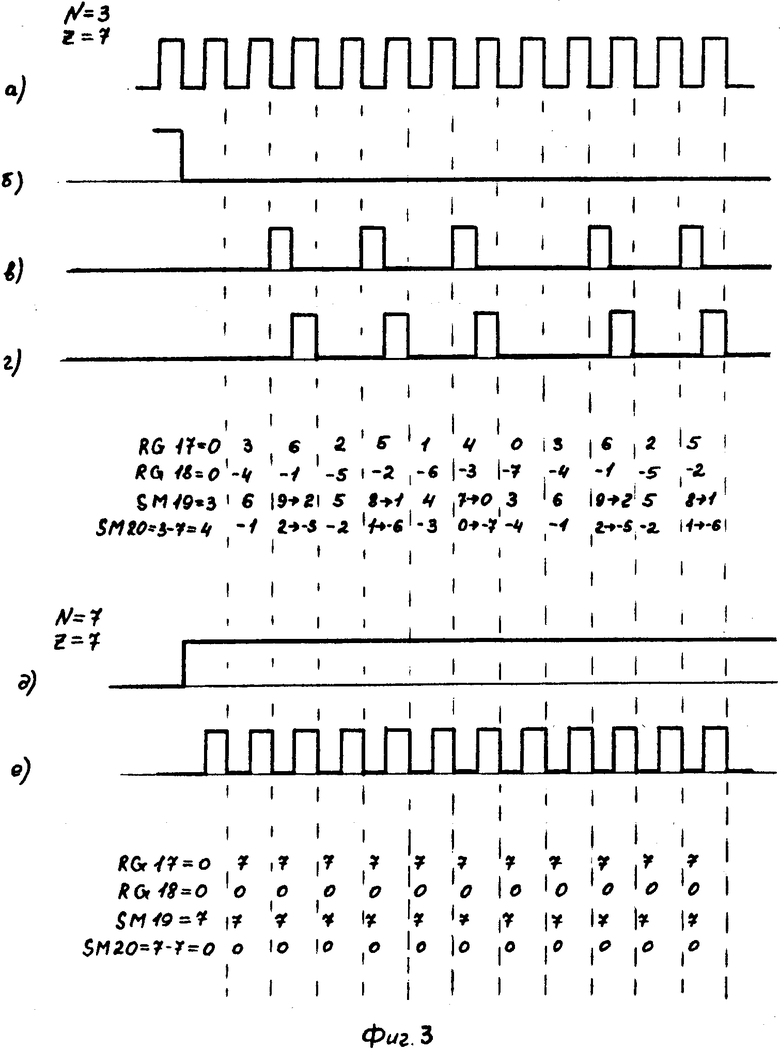

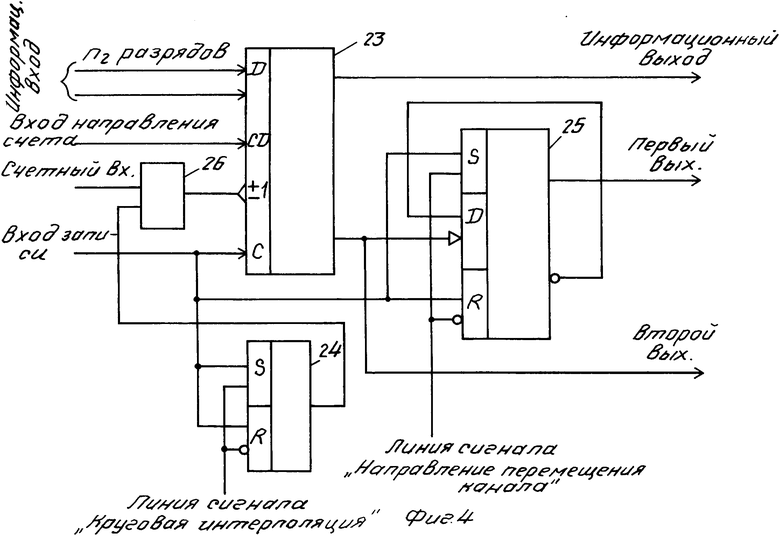

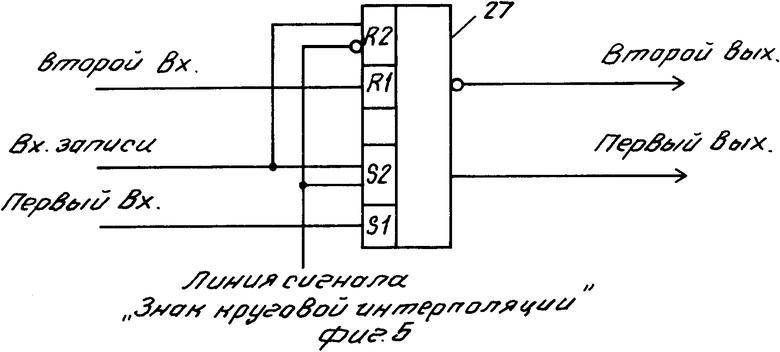

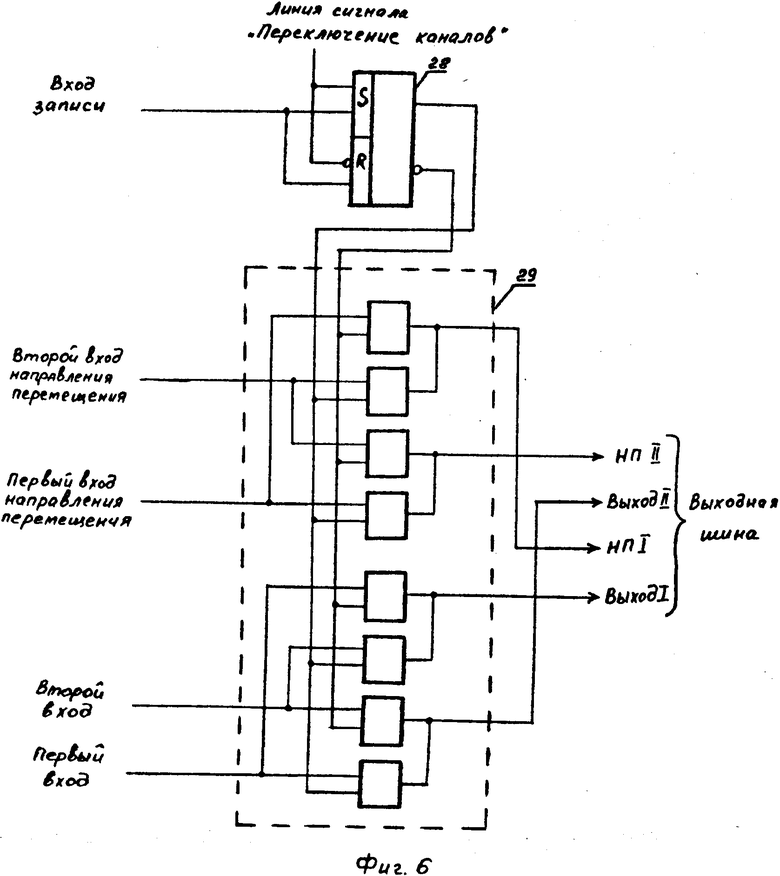

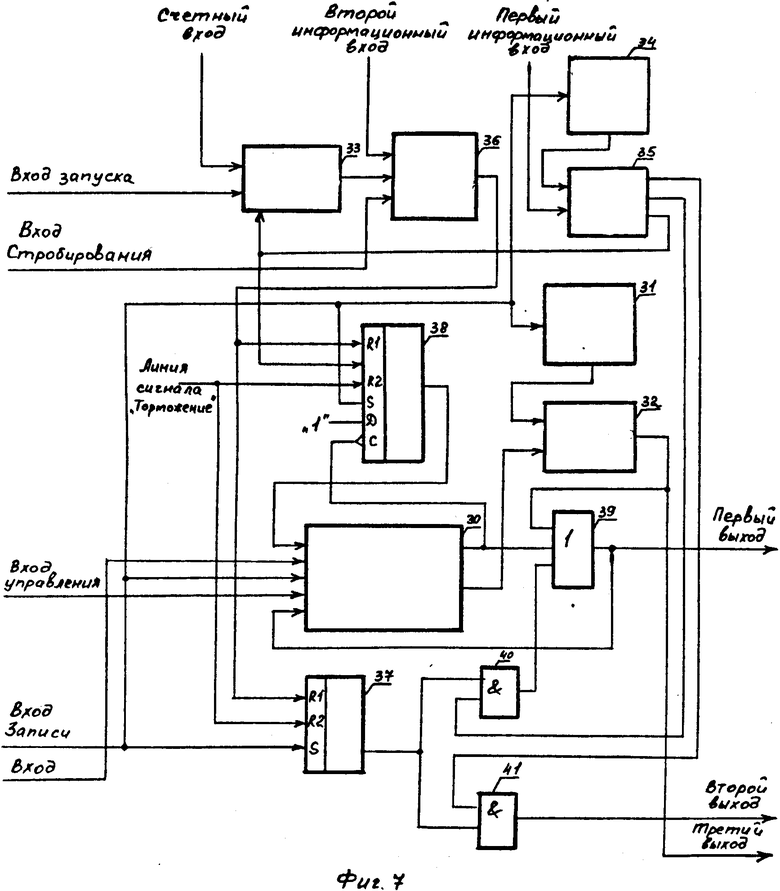

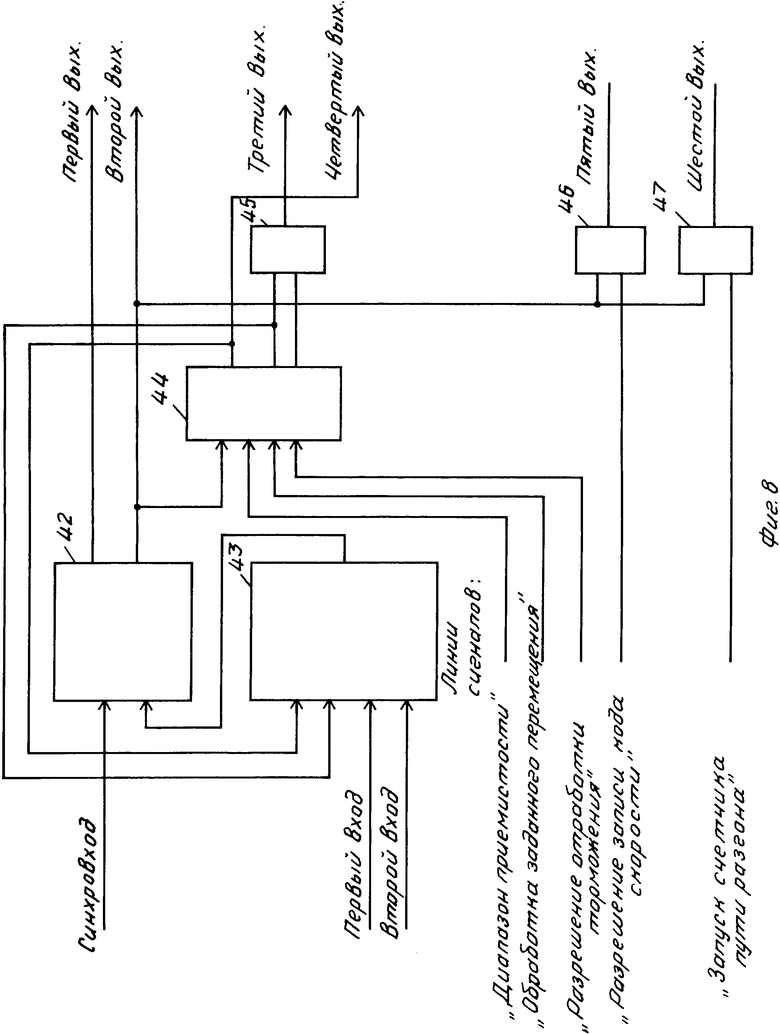

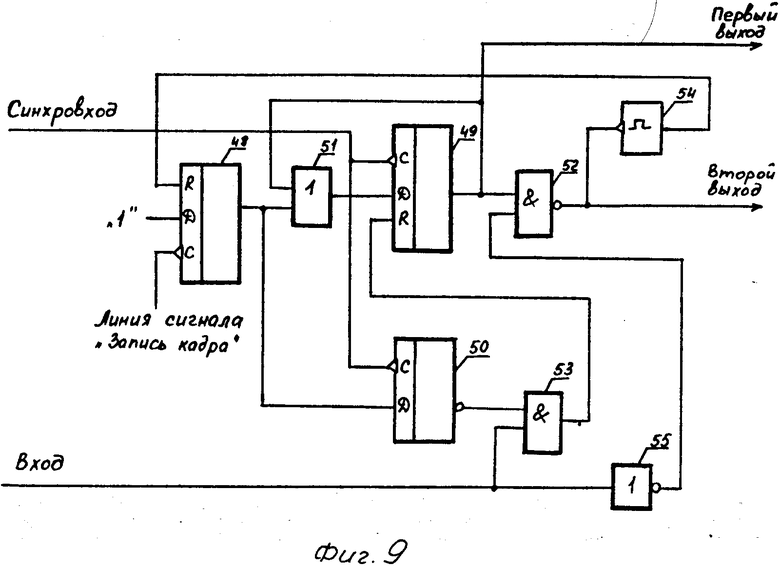

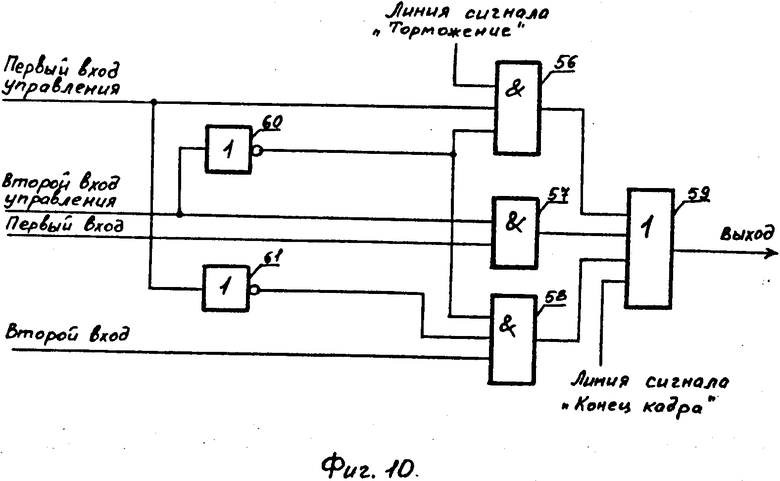

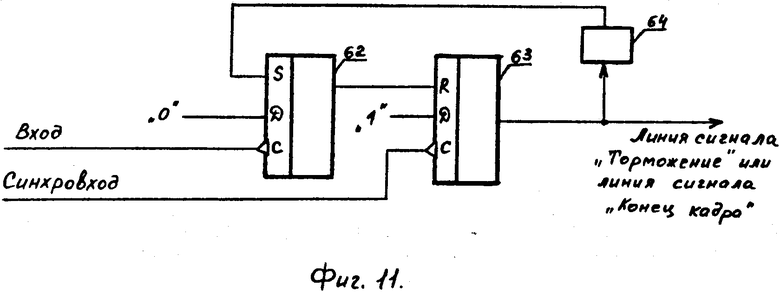

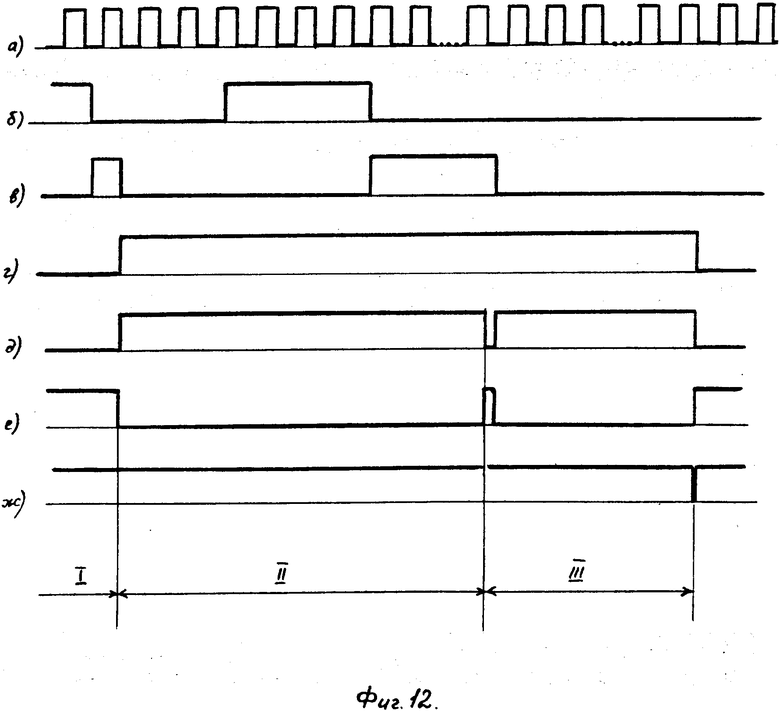

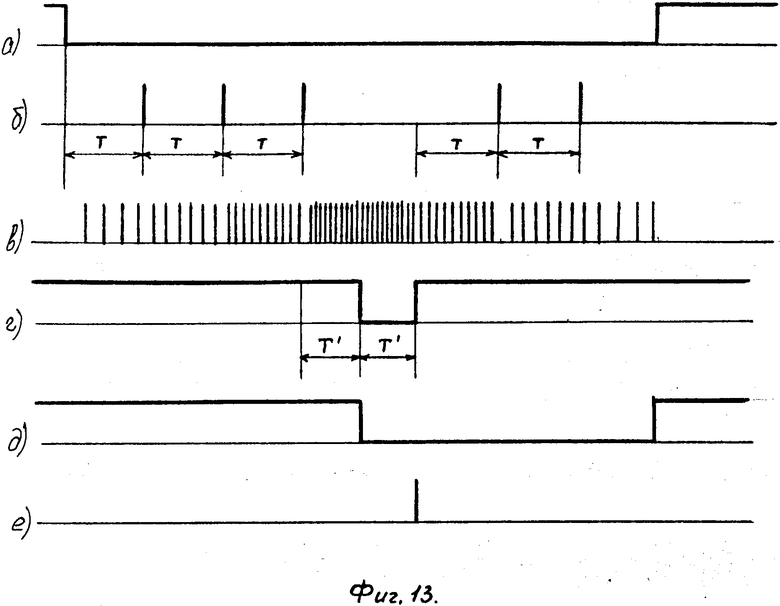

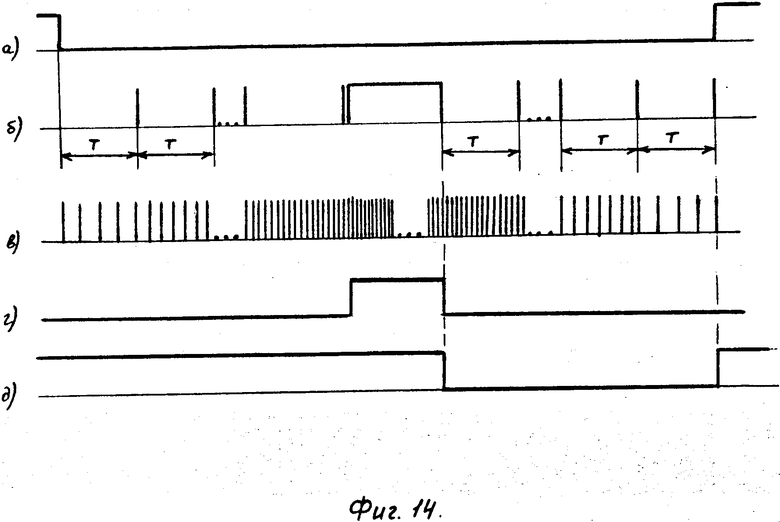

На фиг. 1 представлена блок-схема линейно-кругового интерполятора; на фиг. 2 - схема управляемого делителя частоты с дробным коэффициентом деления; на фиг. 3 - временные диаграммы сигналов, поясняющие работу управляемого делителя частота, где а - сигнал на входе управляемого делителя частоты, б - сигнал на входе блокировки преобразования, в, г - импульсы на выходе переполнения второго сумматора и выходе управляемого делителя частоты соответственно для случая наличия на первом и втором информационных входах кодов N = 3, Z = -7 соответственно, д, е - то же, что и в , г соответственно для случая наличия кодов N = 7, Z = -7; на фиг. 4 показана схема задатчика кода и направления перемещения для каждого канала линейно-кругового интерполятора; на фиг. 5 - схема формирователя сигнала знака интерполяции; на фиг. 6 - схема коммутатора; на фиг. 7 - схема формирователя сигналов сканирования кода скорости; на фиг. 8 - схема формирователя сигналов управления кода; на фиг. 9 - схема запуска отработки кадра; на фиг. 10 - схема формирователя сигнала конца кадра; на фиг. 11 - вариант схемы формирования сигналов для сигнальных линий "Конец кадра" или "Торможение"; на фиг. 12 - временные диаграммы сигналов, поясняющие работу формирователя сигналов управления кадра, где а - импульсы на синхровходе формирователя, б - сигнал на линии "Запись кадра" в схеме запуска отработки кадра, в, г, д - сигналы на прямых выходах первого, второго, третьего триггеров схемы запуска отработки кадра соответственно, е - сигнал на втором выходе формирователя управления кадра, ж - сигнал на выходе формирователя сигнала конца кадра, римскими цифрами обозначены временные интервалы: I - до отработки кадров задания перемещения, II, III - отработки первого и второго кадров; на фиг. 13, 14 - временные диаграммы сигналов, поясняющие работу формирователя сигналов сканирования кода скорости, причем фиг. 13 относится к случаю отработки интерполятором заданного перемещения, для которого не достигается максимальная заданная скорость, фиг. 14 - к случаю отработки интерполятором заданного перемещения, для которого достигается максимальная заданная скорость, на фиг. 13, 14 приведены эпюры сигналов: а - на входе записи формирователя б - на первом выходе формирователя, в - на выходе первого управляемого делителя частоты с дробным коэффициентом деления, д - на выходе триггера формирователя, г - фиг. 13 - на выходе второго триггера формирователя, е - фиг. 13 - на выходе переполнения при счете на вычитание реверсивного счетчика импульсов формирователя, г - фиг. 14 - на втором выходе равенства входных кодов первого блока сравнения кодов формирователя.

Линейно-круговой интерполятор (фиг. 1) содержит реверсивный счетчик 1 импульсов, информационным входом подключенный к первой информационной шине, управляемый делитель 2 частоты с дробным коэффициентом деления, два канала, в каждом из которых установлены задатчик 3 кода и направления перемещения, последовательно соединенные управляемый делитель 4 частоты с дробным коэффициентом деления, делители 5, 6 частоты с коэффициентами деления 2n1 и 2n2 соответственно, элемент И7, счетчик 8 импульсов, а также вне каналов регистр 9, формирователь 10 сигнала знака круговой интерполяции, генератор 11 импульсов, два элемента И 12, 13, коммутатор 14, выходы которого образуют выходную шину линейно-кругового интерполятора, формирователь 15 сигналов сканирования кода скорости, формирователь 16 сигналов управления кадра. Реверсивный двоичный счетчик 1 импульсов выходом соединен со сдвигом (n1 + n2) в сторону старших разрядов с первым информационным входом управляемого делителя 2 частоты, (n1 + n2) младших разрядов первого информационного входа которого подключены к нулевой информационной шине, выход соединен с входом управляемого делителя 4 частоты каждого канала. Вторая информационная шина каждого канала подключена к информационному входу задатчика 3 соответствующего канала со сдвигом n2 в сторону старших разрядов, к n2 младшим разрядам информационного входа задатчика 3 подключена нулевая информационная шина. Третья информационная шина соединена с входом регистра 9, выходом соединенного со сдвигом в сторону старших разрядов к второму информационному входу управляемого делителя 4 частоты каждого канала, n2 младшими разрядами второго информационного входа соединенного с нулевой информационной шиной. Четвертая информационная шина каждого канала соединена с информационным входом счетчика 8 импульсов соответствующего канала, выходом дешифрации нулевого состояния соединенного с вторым входом элемента И7. Выход делителя 5 частоты каждого канала соединен со счетным входом задатчика 3 противоположного канала. Формирователь 10 сигнала знака круговой интерполяции первым входом и первым выходом соединен с вторым выходом и входом направления счета задатчика 3 первого канала соответственно, вторым входом и вторым выходом - с вторым выходом и входом направления счета задатчика 3 второго канала соответственно. Генератор 11 импульсов выходом соединен с входами управляемого делителя 2 частоты и формирователя 15, синхровходом формирователя 16, первым и вторым входами соединенного с выходами элементов И 12, 13 соответственно, первым выходом - с входами блокировки преобразования управляемых делителей 2 и 4 каждого канала, вторым выходом - с входами записи задатчика 3, счетчика 8 каждого канала, регистра 9, формирователя 10, коммутатора 14, формирователя 15, третьим и четвертым выходами - с входами стробирования и управления формирователя 15 соответственно, пятым выходом - с входом записи реверсивного счетчика 1 импульсов, шестым выходом - с входом запуска формирователя 15, счетным входом соединенного с выходом элемента И7 первого канала, вторым информационным входом - с выходом счетчика 8 импульсов канала, первым информационным входом, первым и вторым выходами - с выходом, счетным входом и входом направления счета реверсивного счетчика 1 импульсов соответственно, третьим выходом - с первым входом элемента И13, вторым входом соединенного с выходом дешифрации минимального состояния реверсивного счетчика 1 импульсов. Элемент И12 входами соединен с выходами дешифрации нулевого состояния счетчика 8 импульсов каждого канала соответственно. Коммутатор 14 первым входом и первым входом направления перемещения с выходом элемента И7 и первым выходом задатчика 3 первого канала соответственно, вторым входом и вторым входом направления перемещения - с выходом элемента И7 и первым выходом задатчика 3 второго канала соответственно.

Управляемый делитель 2 частоты вторым информационным входом подключен к информационной шине задания обратного или дополнительного кода.

Реверсивный счетчик 1 импульсов выполнен с блокировкой счета на вычитание при установке в нем кода минимального состояния. Управляемые делители 2, 3 частоты с дробным коэффициентом деления выполнены по схеме, приведенной на фиг. 2, и содержат два регистра 17, 18 с тремя состояниями выходов, два сумматора 19, 20, триггер 21, инвертор 22. Регистры 17, 18 информационными входами подключены к выходам сумматоров 19, 20 соответственно, выходами - к второму входу сумматора 19, выходом подключенного к второму входу сумматора 20, выходом переполнения соединенного с входом установки триггера 21, выполненого с приоритетом установки состояния по сбросу, выходом, являющимся выходом управляемого делителя частоты, соединенного с входами разрешения чтения регистра 18 непосредственно, а регистр 17 через инвертор 22. Первый вход сброса триггера 21 соединен с входами сброса регистров 17, 18 и является входом блокировки преобразования, второй инверсный вход сброса триггера 21 соединен с синхровходами записи регистров 17, 18 и является входом управляемого делителя 2, 3 частоты, первые информационные входы сумматоров 19, 20 являются первым и вторым информационными входами соответственно.

При подаче на второй информационный вход управляемого делителя частоты обратного кода знаменателя коэффициента преобразования Z на вход переноса сумматора 20 подается сигнал переноса, чтобы получить вычитание кода Z.

Задатчик 3 кода и направления перемещения канала (фиг. 4) содержит реверсивный счетчик 23 импульсов, триггеры 24, 25 элемент И 26. Информационный вход реверсивного счетчика 23 импульсов является информационным входом, вход направления счета - входом направления счета, вход записи, соединенный с входами стробирования установкии и броса триггеров 24, 25 - входом записи, выход - информационным выходом, выход дешифрации нулевого состояния, соединенный с синхровходом триггера 25, - вторым выходом задатчика. Счетчик 23 входом соединен с выходом элемента И 26, первый вход которого является счетным входом задатчика, второй вход соединен с выходом триггера 24, входом установки и инверсным входом сброса соединенного с линией сигнала "Круговая интерполяция". Триггер 25 выполнен в виде делителя частоты на два, выход которого является первым выходом задатчика, входом установки и инверсным входом сброса подключен к линии сигнала "Направление перемещения канала".

Формирователь 10 сигнала знака круговой интерполяции (фиг. 5) выполнен в виде триггера 27, первые входы установки и сброса которого являются первым и вторым входами соответственно, входы стробирования вторых входов установки и сброса - входом записи, прямой и инверсный выходы - первым и вторым выходами соответственно формирователя 9, второй вход установки и второй инверсный вход сброса триггера 27 подключены к линии сигнала "Знак круговой интерполяции".

Коммутатор 14 (фиг. 6) содержит триггер 28 и блок буферных стробируемых элементов. Входы стробирования установки и сброса триггера 28 являются входом записи коммутатора 14, вход установки и инверсный вход сброса триггера 28 подключены к линии "Переключение каналов". Буферные элементы блока 29 выполнены с тремя состояниями выходов, подключение выхода каждого элемента осуществляется при установке сигнала логической единицы на входе стробирования. Все буферные элементы разбиты на пары, в каждой их которых объединены выходы буферных элементов. Вход стробирования первого элемента каждой пары подключен к инверсному выходу, второго элемента - к прямому выходу триггера 28, в зависимости от состояния которого сигналы с первых входа и входа направления перемещения, вторых входа и входа направления перемещения коммутатора 14 поступающих на соответствующие первые и вторые линии выходной шины линейно-кругового интерполятора или меняются местами.

Формирователь 15 сигналов сканирования кода скорости (фиг. 7) содержит реверсивный счетчик 30 импульсов, задатчик 31 кода ускорения, блок 32 совпадения кодов, первым входом соединенный с выходом реверсивного счетчика 30, вторым входом - с выходом задатчика 31, счетчик 33 импульсов, счетный вход которого является счетным входом, вход сброса - входом запуска формирователя 15, задатчик 34 кода максимальной скорости, первый блок 35 сравнения кодов, первый вход которого является первым информационным входом формирователя 15, второй вход соединен с выходом задатчика 34, второй блок 36 сравнения кодов, первый вход которого является вторым информационным входом, вход стробирования - входом стробирования формирователя 15, второй вход соединен с выходом счетчика 33 импульсов, триггеры 37, 38, элемент ИЛИ 39, два элемента И 40, 41. Счетный вход реверсивного счетчика 30 импульсов является входом, первый вход сброса - входом управления, второй вход сброса, соединенный с входами установки триггеров 37, 38, входами записи задатчиков 31, 34, - входом записи формирователя 15. Счетчик 30 направления счета соединен с выходом триггера 38, третьим входом сброса - с выходом элемента ИЛИ 39, выходом переполнения при счете на вычитание - с синхровходом установки триггера 38, первым входом элемента ИЛИ 39. Первые входы сброса триггеров 37, 38 соединены с выходом второго блока 39 сравнения кодов, вторые входы сброса триггеров 37, 38 подключены к линии сигнала "Торможение". Первый блок 35 сравнения кодов первым выходом соединен с первым входом элемента И 40, вторым выходом - с первым входом элемента И 41, третьим выходом - с входом блокировки счета счетчика 33 и входом блокировки сброса триггера 38. Триггер 37 выходом соединен с вторыми входами элементов И40, 41 блок 32 совпадения кодов выходом соединен с вторым входом элемента ИЛИ 39. Элемент И40 выходом соединен с третьим входом элемента ИЛИ 39, выход которого является первым выходом, выход элемента И 41 - вторым выходом, выход блока 32 совпадения кодов - третьим выходом формирователя 15. Задатчик 31 кода ускорения и задатчик 34 кода максимальной скорости могут быть выполнены в виде регистров, входами записи соединенных с входами записи задатчиков соответственно, информационными входами - с информационными шинами задания кода ускорения и кода максимальной скорости соответствено, а в случае отсутствия необходимости оперативного изменения управляющих кодов в процессе функционирования - в виде кодовых шин, задающих то или иное значение кода, например, при помощи перемычек или кодовых переключателей.

Формирователь 16 сигналов управления кадра (фиг. 8) содержит схему 42 запуска отработки кадра, формирователь 43 сигнала конца кадра, регистр 44, три элемента И45, 46, 47. Синхровход схемы 42 является синхровходом, первый и второй выходы - первым и вторым выходами формирователя 16 соответственно. Схема 42 соединена с выходом формирователя 43, вторым выходом - с входом записи регистра 44, первыми входами элементов И46, 47. Первый и второй входы 43 формирователя являются первым и вторым входами формирователя 16 соответственно, первый и второй входы управления соединены с первым и вторым выходами регистра 44 соответственно, первый, второй и третий входы которого подключены к линиям сигналов "Диапазон приемистости", "Отработка заданного перемещения", "Разрешение отработки торможения" соответственно, второй и третий выходы подключены к входам элемента И45, выход которого является третьим выходом, первый выход регистра 44 - четвертым выходом, выходы элементов И46, 47 - пятым и шестым выходами формирователя 16. Вторые входы элементов И 46 и 47 подключены к линии сигналов "Разрешение записи кода скорости" и "Запуск счетчика пути разгона" соответственно.

Схема 42 запуска отработки кадра (фиг. 9) содержит триггеры 48, 49, 50, элементы ИЛИ 51, элементы И52, 53 одновибратор 54, инвертор 55. Триггер 48 синхровходом установки соединен с линией сигнала "Запись кадра", входом сброса - с выходом одновибратора 54, выходом - D-входом триггера 50 и первым входом элемента ИЛИ 51. Синхровходы триггеров 49, 50 соединены и являются синхровходом первый вход элемента И53 соединен с входом инвертора 55 и является входом, инверсный выход триггера 49 является первым выходом, инверсный выход элемента И52 соединен с синхровходом одновибратора 54 и является вторым выходом схемы 42. Триггер 49 Д-входом подключен к выходу элемента ИЛИ 51, входом сброса - к выходу элемента И53, выходом - к вторым входам элементов ИЛИ51 и И52. Элемент И52 первым входом соединен с выходом инвертора 55.

Формирователь 43 сигнала конца кадра (фиг. 10) содержит три элемента И56, 57, 58, элемент ИЛИ 59, инверторы 60, 61. К первому входу элемента И56 подключена линия сигнала "Торможение", первый вход управления формирователя 43 подключен к вторым входам элемента И56 непосредственно, элемента И58 через инвертор 61, второй вход управления формирователя 43 подключен к второму входу элемента И57 непосредственно, а к третьим входам элементов И56, 58 через инвертор 60. Первый и второй входы формирователя 43 подключены к первым входам элементов И57 и 58 соответственно, элемент ИЛИ59, выход которого является выходом формирователя 43, тремя входами соединен с выходами элементов И56, 57, 58, а четвертым входом - с линией сигнала "Конец кадра".

Формирователи сигналов для линий "Торможение" или "Конец кадра" могут быть выполнены по однотипной схеме, приведенной на фиг. 11, содержащей триггер 62, синхровходом сброса соединенный с входом схемы, триггер 63, синхровходом установки соединенный с синхровходом схемы, соединенный в интерполяторе с выходом генератора 11 импульсов, элемент 64 задержки, выходом соединенный с входом установки триггера 62. Триггер 63, выход которого подключен к выходу схемы, выходом соединен с входом 64 задержки, а входом сброса - с выходом триггера 62.

Линейно-круговой интерполятор работает следующим образом.

В начале каждого кадра работы в интерполятор с информационных шин и сигнальных линий вводится необходимая информация, сопровождаемая импульсом записи с второго выхода схемы запуска отработки кадра, проходящего на второй выход или через элементы И46, 47 при наличии на их вторых входах сигналов логической "1" на пятый и шестой выходы формирователя 16 сигналов управления кадра.

С первой информационной шины в реверсивный счетчик 1 импульсов сигналом записи, поступающим с пятого выхода формирователя 16 на вход записи реверсивного счетчика 1 благодаря наличию на линии сигнала "Разрешение записи кадра скорости" в формирователе 16 уровня логической "1" переписывается код N контурной скорости перемещения. Если в кадре задается перемещение, осуществляемое на постояной скорости в диапазоне приемистости шагового двигателя, на линии сигнала "Диапазон приемистости" к моменту появления на выходе схемы 42 импульса записи имеет место сигнал логической "1", запоминаемый регистром 44 на время отработки кадра, с выхода которого сигнал поступает на вход управления формирователя 15 сигналов сканирования кода скорости, блокируя его работу, на реверсивный счетчик 1 не поступают счетные импульсы и записанный код N сохраняется на все время отработки кадра.

С начала отработки кадров за счет установки триггера 49 схемы 42 запуска снимается сигнал блокировки преобразования с соответствующего входа управляемых делителей частоты с дробным коэффициентом деления, выполняющих преобразование частоты входной последовательности импульсов. Первый управляемый делитель 2 частоты на выходе из импульсной последовательности на выходе генератора 11 частотой  формирует унитарный код N ˙2(n1+n2) на временном масштабе Z τ , частота которого соответствует заданной скорости перемещения, умноженной на коэффициент 2(n1+n2). Импульсная последовательность с выхода управляемого делителя 2 поступает на входы управляемых делителей 4 частоты каждого координатного канала, на первые информационные входы которых поступают коды с выходов задатчиков 3 каждого координатного канала, определяющие числители коэффициентов преобразрвания, на вторые информационные входы - код выхода регистра 9. В каждом канале с второй информацией шины в реверсивный счетчик 23 импульсов записи переписываются в случае задания линейной интерполяции коды ΔI, ΔII заданных перемещений по координатам I, II, а в случае круговой интерполяции коды координат начальной точки относительно центра интерполируемой окружности: VII - для координаты I, VI - для координаты II. С третьей информационной шины в регистр 9 переписывается в случае линейной интерполяции код величины l заданного отрезка перемещения, в случае круговой интерполяции код величины R заданного радиуса окружности. При линейной интерполяции триггер 24 сброшен, блокируя поступление на счетный вход реверсивного счетчика 23 импульсов и оставляли его состояние неизменным на все время во время отработки кадра. При круговой интерполяции триггер 24 установлен, разрешая прохождение на счетный вход реверсивного счетчика 23 импульсов с выхода делителя 5 частоты потивоположной координаты, частота следования которых превышает в 2n2 раз частоту следования выходных импульсов устройства, за счет чего, а также за счет увеличения кодов, поступающих на информационные входы управляемых делителей частоты, дискрета интерполяции уменьшается в 2n2 раза по сравнению с дискретой перемещения.

формирует унитарный код N ˙2(n1+n2) на временном масштабе Z τ , частота которого соответствует заданной скорости перемещения, умноженной на коэффициент 2(n1+n2). Импульсная последовательность с выхода управляемого делителя 2 поступает на входы управляемых делителей 4 частоты каждого координатного канала, на первые информационные входы которых поступают коды с выходов задатчиков 3 каждого координатного канала, определяющие числители коэффициентов преобразрвания, на вторые информационные входы - код выхода регистра 9. В каждом канале с второй информацией шины в реверсивный счетчик 23 импульсов записи переписываются в случае задания линейной интерполяции коды ΔI, ΔII заданных перемещений по координатам I, II, а в случае круговой интерполяции коды координат начальной точки относительно центра интерполируемой окружности: VII - для координаты I, VI - для координаты II. С третьей информационной шины в регистр 9 переписывается в случае линейной интерполяции код величины l заданного отрезка перемещения, в случае круговой интерполяции код величины R заданного радиуса окружности. При линейной интерполяции триггер 24 сброшен, блокируя поступление на счетный вход реверсивного счетчика 23 импульсов и оставляли его состояние неизменным на все время во время отработки кадра. При круговой интерполяции триггер 24 установлен, разрешая прохождение на счетный вход реверсивного счетчика 23 импульсов с выхода делителя 5 частоты потивоположной координаты, частота следования которых превышает в 2n2 раз частоту следования выходных импульсов устройства, за счет чего, а также за счет увеличения кодов, поступающих на информационные входы управляемых делителей частоты, дискрета интерполяции уменьшается в 2n2 раза по сравнению с дискретой перемещения.

С четвертых информационной шин каждого канала в счетчик 8 импульсов соответствующих каналов импульсом записи переписываются коды ΔI, ΔII заданных перемещений по координатам I, II которые считываются до нулевого кода импульсами координатных перемещений с выходов элементов И7. Сигналы дешифрации нулевого состояния счетчиков 8 поступают на элемент И12, установка уровня логической "1" на выходе которого свидетельствует об окончании отработки заданного перемещения.

Состояние сигнала направления перемещения по каждой координате с линии "направление перемещения" заносится в триггер 25, причем при круговой интерполяции состояние триггера 25 меняется на противоположное при установке на выходе дешифрации нулевого кода реверсивного счетчика 23 сигнала логической "1".

Направлением счета в процессе круговой интерполяции реверсивного счетчика 23 импульсов управляют триггер 27, принимающий начальное состояние с линии сигнала "Знак круговой интерполяции. " Установленное состояние триггера 27 вызывает пересчет на сложение реверсивного счетчика 23 канала I и переcчет на вычитание реверсивного счетчика 23 канала II, при этом достижение им нулевого состояния вызывает появление сигнала единичного логического уровня на втором входе формирователя 10, приводящего к сбросу триггера 27 и изменению направления счета реверсивных счетчиков 23 каналов I, II на противоположное. Достижение нулевого состояния реверсивным счетчиком 1 канала, для которого выполняется пересчет импульсов на вычитание, вызывает вновь установку триггера 27 сигналом, поступающим на его первый вход установки.

В управляемых делителях частоты с дробным коэффициентом деления в исходном состоянии на входе блокировки преобразования имеется уровень логической "1", регистры 17, 18 и триггер 21 сброшены, вследствие чего выход регистра 18 находится в третьем отключенном состоянии, а выход регистра 17 подключен к второму входу сумматора 19, на выходе которого присутствует код N, поступающий на первый информационный вход. На выходе сумматора 20 присутствует сумма кодов на выходе сумматора 19 и на втором информационном входе: N - Z.

Сигнал на входе блокировки преобразования управляемого делителя частоты по отрицательному фронту импульсной последовательности переходит на уровень логического "0", обуславливая начало преобразования, при этом очередным отрицательным фронтом входного импульса в регистры 17, 18 переписываются выходные коды сумматоров 19, 20 соответствено, после чего выходной код сумматора 19 становится равным 2N, а сумматора 20 - равным 2N -Z. Под воздействием каждого последующего отрицательного фронта импульса, поступающих на вход управляемого делителя частоты, на выходе сумматоров 19, 20 коды увеличиваются на величину N до тех пор, пока сумма на выходе сумматора 20 будет оставаться отрицательной.

При появлении на выходе сумматора 20 неотрицательного кода D, численно равного остатку от деления Z на N, на выходе переноса сумматора 20 одновременно возникает сигнал логической "1", вызывающий установку триггера 21 во время положительного полуимпульса входной последовательности после освобождения второго инверсного входа сброса триггера 21 от сигнала с уровнем логического "0". Установленное состояние триггера 21 соответствует формированию выходного импульса, при этом выход регистра 17 переводится в третье состояние и к второму выходу сумматора 20 подключается выход регистра 18, содержащий в это время код D.

Вышеописанный цикл работы управляемого делителя с дробным коэффициентом деления повторяется до появления на выходе сумматора 20 вновь неотрицательного кода, причем в каждом очередном цикле учитывается остаток от деления Z на N предыдущего цикла, так как на первом шаге цикла в регистры 17, 18 переписываются коды. При поступлении на вход управляемого делителя частоты Z импульсов на выход проходит N импульсов, код остатка равен нулю - устройство приходит к начальным условиям преобразования. Таким образом, на выходе управляемого делителя частоты на временном масштабе Z τ формируется N выходных импульсов, неравномерность следования которых не превышает периода следования τ на входной линии, а частота fвых определяется соотношением

fвых=  fвх=

fвх=  .

.

В соответствии с данным выражением формирует выходную последовательность импульсов управляемый делитель 2 частоты, при этом код N увеличен в 2(n1+n2), поэтому выходная частота определяется выражением

fвых =

=  .

.

Код Z выбирается такой величины, чтобы обеспечить минимальное значение Fмин рабочего диапазона частот интерполятора:

Fмин=  .

.

Максимальное значение частоты интерполятора

Fмакс=  = NмаксFмин.

= NмаксFмин.

Импульсная последовательность с выхода управляемого делителя 2 частоты, проходя через управляемые делители чатоты, преобразуется в импульсные последовательности, частоты которых соответствуют поекциями контурной скорости на координаты, увеличенные 2(n1+n2), а проходя через делители 5, 6 частоты приводятся к импульсным последовательностям с заданными коордиантными частотами, при лиенейной интерполяции

FI=  ·

·  ;

;

FII=  ·

·  ;

;

при круговой интерполяции

F =

=  ·

·  ;

;

F =

=  ·

·  .

.

Наличие в линейно-круговом интерполяторе делителей частоты 5, 6 с коэффициентом деления 2(n1+n2) позволяет во столько же раз понизить относительную неравномерность следования выходных импульсов устройства и использовать его на повышенных частотах, требующих реализации режима разгона-торможения, с помощью реверсивного счетчика 1 импульсов и формирователя 15 сигналов сканирования кода скорости.

Для запуска формирователя 15 регистр 44 на время отработки кадра считывает с линии сигнала "Диапазон приемистости" сигнал нулевого логического уровня, поступающий на вход управления формирователя 15, освобождая реверсивный счетчик 30 импульсов от принудительного сброса. В начале кадра импульсом записи в задатчики 31, 34 вводятся коды ускорения и максимальной скорости, устанавливаются триггеры 37, 38, обуславливающие установку счета на сложение реверсивных счетчиоков 1, 30.

Реверсивный счетчик 30 импульсов, пересчитывая тактовые импульсы с выхода генератора 11, через временный интервал, определяемый задатчиком 31 кода ускорения, и при помощи блока 32 совпадения кодов, выходной сигнал которого через элемент ИЛИ 39 поступает на третий вход сброса реверсивного счетчика 30 и на первый выход формирователя 15, вырабатывает импульсы, поступающие на счетный вход реверсивного счетчика 1 импульсов, возрастание состояния которого приводит к пропорциональному увеличению частоты следования выходных импульсов управляемого делителя 2 частоты вплоть до максимального значения, если блоком 36 сравнения кодов к этому моменту времени не выработаны сигналы, приводящие к реверсу ускорения. Состояние реверсивного счетчика 1 импульсов Nмакс выделяется блоком 35 сравнения кодов, на первый вход А которого поступает код состояния реверсивного счетчика 1, а на второй вход В - код от задатчика 34. Сигнал с первого выхода А-В блока 35 поступает на вход элемента И40 и блокирует формирование пересчетных импульсов, поддерживая реверсивный счетчик 30 в сброшенном состоянии.

Исходное состояние счетчика 33 импульсов нулевое, что обеспечивается приходом импульса на вход сброса в начале кадра. Счетчик 33, на счетный вход которого поступают импульсы перемещения с выхода элемента И7 первого канала, контролирует величину отработанного в кадре перемещения по координате, связанной с первым каналом, сраниваемого с кодом оставшегося для отработки в кадре перемещения, поступающим с выхода счетчика 8 импульсов. В режиме отработки в кадре заданного перемещения на вход стробирования блока 36 сравнения поступает сигнал единичного логического уровня, разрешающего формирование на выходе блока 36 сигнала сравнения входных кодов. В рассматриваемом случае, когда максимальная очастота Fмакс следования импульсов на выходе управляемого делителя 2 достигается раньше, чем вырабатывается сигнал А ≥ B на выходе блока 36, где А - код, поступающий с выхода счетчика 33, В - код, поступающий с выхода счетчика 8, появление на третьем выходе A ≥ B блока 35 сигнала единичного логического уровня приводит к блокировке счета счеточика 33, благодаря чему в нем фиксируется код пути разгона, а также к блокировке сброса триггера 38, поэтому в дальнейшем сохраняется направление счета на сложение для реверсивного счетчика 30 импульсов. Счетчик 8 продолжает считывание кода заданного перемещения по координате, контролируя оставшееся для отработки в кадре перемещение, и, когда величина остатка пути сравняется с величиной пути разгона, на выходе А ≥ В блока 36 появляется сигнал, сбрасывающий триггер 37, что вызывает перевод в состояние Nмакс - 1 реверсивного счетчика 1 и освобождение от сброса реверсивного счетчика 30, продолжающего после этого формирование счетных импульсов для реверсивного счетчика 1. Причем в связи со сброшенным состоянием триггера 37 счет выполняется на вычитание, в следствие чего состояние реверсивного счетчика 1 последовательно уменьшается, обуславливая реализацию фазы торможения при отработке заданного перемещения в кадре.

Если сигнал А ≥ В на выходе блока 36 вырабатывается раньше, чем достигается максимальная частота Fмакс, сбрасывается не только триггер 37, но и триггер 38, что вызывает реверс направления счета реверсивного счетчика 30, считывающего достигнутое им на момент смены направления счета состояние и импульсом переполнения при счете на вычитание возвращающего триггеру 38 установленное состояние. Таким образом, обеспечивается равенство времени перемещения на достигнутой максимальной скорости в фазах разгона и торможения, минимизируя в целом разницу времени отработки разгона и времени отработки торможения. Вместе с тем эта разница времен присутствует из-за отличия пути разгона и пути торможения на единицу дискреты перемещения, когда заданное перемещение выражено нечетным числом, а также вследствие того, что момент конца разгона не синхронизирован, в то время как момент начала торможения синхронизирован импульсами перемещения с выхода элемента И47. Поэтому в отличие от линейной интерполяции на постоянной заданной скорости, не имеющей погрешности интерполяции, линейная интерполяция, выполняемая с разгоном-торможением, обладает погрешностью, и для ее минимизации в первый канал, используемый для взаимодействия с формирователем 15, вводится исходная информация с информационных шин и сигнальных линий по той координате, для которой имеет место большая заданная величина Δ координатного перемещения, а необходимую перекоммутацию выходных линий каналов выполняет коммутатор 14, принимающий в начале кадра соответствующий сигнал с линии "Переключения каналов".

При задании в кадре безмерного перемещения на втором выходе регистра имеется уровень логического "0", вызывающий блокировку формирования выходного сигнала сравнения блока 36. В данном случае перевод формирователя 15 из фазы разгона в фазу торможения выполняется при помощи сигнала, поступающего по линии "Торможение", действие которого на триггеры 37, 38 аналогично действию сигнала А ≥ В на выходе блока 36 в режиме отработки заданного перемещения, а эквивалентность фазировки возникновения относительно тактовых импульсов на выходе генератора 11 обеспечивается при помощи схемы синхронизации, показанной на фиг. 11.

При отработке заданного или безразмерного перемещения в режиме разгона-торможения минимальная частота на выходе управляемого делителя 2, от которой начинатся разгон и завершается торможение, может в общем случае отличаться от частоты Fмин, определяющей дискрету смены частоты, что способствует минимизации погрешности линейной интерполяции, выполняемой с разгоном и торможением, а также повышает производительность работы интерполятора в этом режиме. Поэтому реверсивный счетчик 1 имеет выход дешифрации кода минимальной скорости торможения, активный сигнал которого блокирует счет на вычитание реверсивного счетчика 1 и разрешает прохождение через элемент И13 сигнала единичного логического уровня с выхода блока 32 совпадения кодов на второй вход формирователя 16, вызывающего завершение кадра отработки безразмерного перемещения.

При отработке безразмерного перемещения в случае необходимости изменения значений максимальной скорости перемещения без промежуточного торможения до минимальной скорости торможения на линии сигнала "Конец кадра" при помощи схемы синхронизации, аналогичной схеме на фиг. 11, формируется импульс, выполняющий перезапуск кадра с обновленным значением кода максимальной скорости, который может превосходить или быть меньше прежнего значения - в этом случае состояние второго выхода А < B блока 35 сравнения кодов регламентирует через элемент И41 направление счета реверсивного счетчика 1 импульсов.

Линии сигналов "Разрешение отработки торможения", "Разрешение записи кода скорости", "Запуск счетчика пути разгона" в формирователе 16 позволяют расширить функциональные возможности интерполятора. Например, наличие в пределах отработки текущего кадра сигнала нулевого логического уровня на третьем выходе регистра 44, принявшего сигнал с линии "Разрешение отработки торможения", и наличие в начале отработки последующего сигнала нулевого логического уровня на линии "Разрешение записи кода скорости" позволяют при отработке заданного перемещения в режиме разгона в текущем кадре предотвратить формирование сигнала на выходе блока 36 сравнения кодов, вызывающего переход в фазу торможения, а также предотвратить в последующем кадре запись данных в реверсивный счетчик 1, обеспечивая перемещение в начале последующего кадра на скорости, достигнутой в результате отработки предыдущего кадра. Таким образом, путем формирования последовательности кадров оказывается возможным устранение ограничения на величину отработки заданного перемещения в режиме разгон-торможение.

Дополнение приведенного режима работы интерполятора управлением по линии "Запуск счетчика пути разгона", устанавливающим на данной линии к началу очередного кадра сигнал нулевого логического уровня и предотвращающим перезапуск счетчика 33, контролирующего величину пути разгона, позволяет в последовательности кадров, имеющих разрывные фрагменты разгона, определить суммарный путь разгона и обеспечить корректную отработку фазы торможения в режиме отработки заданного перемещения.

Для запуска отработки интерполярного кадра после установки на информационных линиях и сигнальных данных отрицательным фронтом импульса на линии сигнала "Запись кадра" устанавливается триггер 48, после чего очередным отрицательным фронтом импульса на синхровходе схемы 42 запуска отработки кадра устанавливаются триггер 50 и триггер 49, поддерживающий установленное состояние при помощи элемента ИЛИ 51. Установка триггера 49 вызывает отрицательный перепад логического уровня на инверсном выходе элемента И52 и запуск одновибратора 54, выходным импульсом сбрасывающего триггер 48, что является основанием для внешней системы управления начать установку данных на информационных шинах и сигнальных линиях для запуска последующего кадра. Сброс триггера 48 вызывает возврат в нулевое состояние триггера 50.

В результате отработки текущего кадра от формирователя 43 сигнала конца кадра на вход схемы 42 поступает сигнал единичного логического уровня, который, если к этому моменту времени установлен триггер 50, проходит через инвертор 55 и элемент И 52 на второй выход схемы 42 в качестве импульса записи динных в регистры и задатчики интерполятора для отработки нового кадра. Импульс записи имеет длительность и сфазирован относительно выходной импульсной последовательности генератора 11 так, чтобы обеспечить завершение установки обновленных данных в регистрах и задатчиках интерполятора в пределах отрицательных полуимпульсов генератора 11 для корректного функционирования управляемых делителей частоты.

В том случае, когда триггер 50 сброшен, сигнал конца кадра проходит через элемент И53 на вход сброса триггера 49, завершая работу интерполятора установки сигналов единичного логического уровня на выходах схемы 42.

Формирователь 43 в зависимости от установленного в кадре режима работы по соответствующему признаку выставляет на выходе сигнал конца в виде единичного логического уровня. В кадре отработки заданного перемещения, которому соответствует присутствие сигнала логической "1" на втором входе управления формирователя 43, сигнал конца возникает под воздействием через элемент И57 сигнала завершения координатных перемещений с выхода элемента И12. В кадре отработки безразмерного перемещения на втором входе управления формирователя 43 присутствует сигнал нулевого логического уровня и сигнал конца кадра возникает в случае отработки перемещения с разгоном-торможением через элемент И58 под действием выходного сигнала элемента И13 после установления в счетчике 1 кода минимальной скорости, а в случае отработки перемещения без разгона-торможения на заданной скорости в диапазоне приемистости - под действием сигнала на линии "Торможение" через элемент И56. В отмеченном выше режиме, когда необходима безусловная смена кадров, сигнал с линии "Конец кадра" непосредственно поступает на элемент ИЛИ 59 и далее на выход формирователя 43.

При реализации предлагаемого линейно-кругового интерполятора, например, для управления двухкоординатным дискретным приводом на основании требования обеспечения значения максимальной выходной частоты Fмакс импульсов перемещения интерполятора и требований по обеспечению допустимой относительной погрешности неравномерности следования выходных импульсов выбираются значения суммарного коэффициента деления делителей 5,6 частоты координатных каналов K = 2(n1+n2) и значение частоты выходных импульсов генератора 11 f ≥K˙ Fмакс. На основании требования по обеспечению допустимой величины погрешности круговой интерполяции, например, по известным сотношениям выбирается коэфициент деления K2 = 2n2 делителя 6 частоты и соответствующий ему коэффициент деления K1 = 2n1 делителя 5 частоты, причем при нежестких требованиях к величине погрешности круговой интерполяции коэффициент деления К2 может быть выбран равным единице, т. е. делитель 6 частоты исключен из состава устройства. Если требования к допустимой величине погрешности круговой интерполяции соответствуют или превосходят требования к допустимой величине неравномерности следования выходных импульсов перемещения может быть взят К1 = 1 и исключен делитель 5 частоты.

Требования по обеспечению минимальной частоты Fмин выходных импульсов перемещения определяет максимальное состояние Nмаксреверсивного счетчика 1 импульсов: Nмакс=  , и, следовательно, его емкость, а также размерность и номинальное значение кода Z=

, и, следовательно, его емкость, а также размерность и номинальное значение кода Z=  , в соответствии с которым выбирается размерность регистров и сумматоров управляемого делителя 2 частоты. Определив размерности регистров и сумматоров управляемых делителей частоты, необходимо для выбранной элементной базы проверить условие их корректного функционирования: в каждом цикле преобразования в управляемых делителях частоты завершение установки данных на выходных сумматорах 19, 20 должно происходить до возникновения фронта записи регистры в 17, 18, и, если условие не выполняется, необходимо пересмотреть выбор элементной базы по крайней мере для элементов, определяющих быстродействие преобразования частоты.

, в соответствии с которым выбирается размерность регистров и сумматоров управляемого делителя 2 частоты. Определив размерности регистров и сумматоров управляемых делителей частоты, необходимо для выбранной элементной базы проверить условие их корректного функционирования: в каждом цикле преобразования в управляемых делителях частоты завершение установки данных на выходных сумматорах 19, 20 должно происходить до возникновения фронта записи регистры в 17, 18, и, если условие не выполняется, необходимо пересмотреть выбор элементной базы по крайней мере для элементов, определяющих быстродействие преобразования частоты.

Например, для управления приводом на базе шагового двигателя ШД-5 с максимальной частотой Fмакс = 8 кГц в интерполяторе при выборе частоты генератора 11 f = 1 250 кГц коэффициент деления К может быть выбран K = 128 <  . При Fмин = 8 Гц Nмакс=

. При Fмин = 8 Гц Nмакс=  = 1000, Z =

= 1000, Z =  = 156250. Двадцатиразрядный управляемый делитель 2 обеспечивает преобразование для максимального кода 128000, поступающего на первый информационный вход, и кода 156250, поступающего на второй информационный вход, и для выбранной частоты 1,25 МГц и позволяет получить корректное функционирование при выполнении на элементах среднего быстродействия, например, серии К555. Максимальная частота, поступающая на вход управляемого делителя 4, составляет 1024 кГц. Для максимального радиуса, составляющего, например, 3 ˙ 105 дискрет перемещения, и при выборе К1 = 1, К2 = 128 максимальные коды, поступающие на информационные входы управляемых делителей 4, равны 3,84 ˙ 107 и требуют его 28- разядной размерности и выполнения также на элементах среднего быстродействия, как и для управялемого делителя 2. (56) 1. Авторское свидетельство СССР N 1312530, кл. G 05 B 19/18, 1985.

= 156250. Двадцатиразрядный управляемый делитель 2 обеспечивает преобразование для максимального кода 128000, поступающего на первый информационный вход, и кода 156250, поступающего на второй информационный вход, и для выбранной частоты 1,25 МГц и позволяет получить корректное функционирование при выполнении на элементах среднего быстродействия, например, серии К555. Максимальная частота, поступающая на вход управляемого делителя 4, составляет 1024 кГц. Для максимального радиуса, составляющего, например, 3 ˙ 105 дискрет перемещения, и при выборе К1 = 1, К2 = 128 максимальные коды, поступающие на информационные входы управляемых делителей 4, равны 3,84 ˙ 107 и требуют его 28- разядной размерности и выполнения также на элементах среднего быстродействия, как и для управялемого делителя 2. (56) 1. Авторское свидетельство СССР N 1312530, кл. G 05 B 19/18, 1985.

2. Авторское свидетельство СССР N 477397, кл. G 05 B 19/18, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления электродвигателем | 1987 |

|

SU1472873A1 |

| УСТРОЙСТВО ДЛЯ СТАТИСТИЧЕСКОГО МОДЕЛИРОВАНИЯ СОСТОЯНИЯ ОБЪЕКТА ИСПЫТАНИЙ | 1991 |

|

RU2010323C1 |

| СПУТНИКОВАЯ СИСТЕМА СВЯЗИ "ТОМЬ" | 1992 |

|

RU2010434C1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТОР | 1984 |

|

SU1238702A1 |

| Устройство для формирования корректирующего воздействия через привод программного регулятора | 1987 |

|

SU1427329A1 |

| ТЕЛЕВИЗИОННОЕ СЛЕДЯЩЕЕ УСТРОЙСТВО | 1988 |

|

SU1574152A1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТОР | 1986 |

|

SU1412577A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РАДИОСТАНЦИИ ПОДВИЖНЫХ ОБЪЕКТОВ | 1991 |

|

RU2010436C1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТОР | 1987 |

|

SU1521242A1 |

| УСТРОЙСТВО ДЛЯ ТРАНСПОРТИРОВКИ ОПЕРАТОРА | 1990 |

|

RU2010340C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано, в частности, в системах контурного программного управления перемещениями исполнительных органов станков и технологического оборудования. Изобретение позволяет повысить точность интерпретации, снизить неравномерность следования выходных импульсов перемещения, обеспечив надежную работу на повышенных частотах управляемого интерполятором дискретного привода, расширить функциональные возможности. Линейно-круговой интерполятор содержит реверсивный счетчик импульсов, управляемый делитель частоты с дробным коэффициентом деления, два координатных канала, в каждом из которых имеются задатчик кода и направления перемещения, управляемый делитель частоты с дробным коэффициентом деления, делители частоты, элемент И, счетчик импульсов, кроме того, интерполятор содержит регистр, формирователь сигнала знака интерполяции, генератор импульсов, элементы И, коммутатор, формирователь сигналов сканирования кода скорости, формирователь сигналов управления кадра. 3 з. п. ф-лы, 14 ил.

Авторы

Даты

1994-03-30—Публикация

1991-12-23—Подача