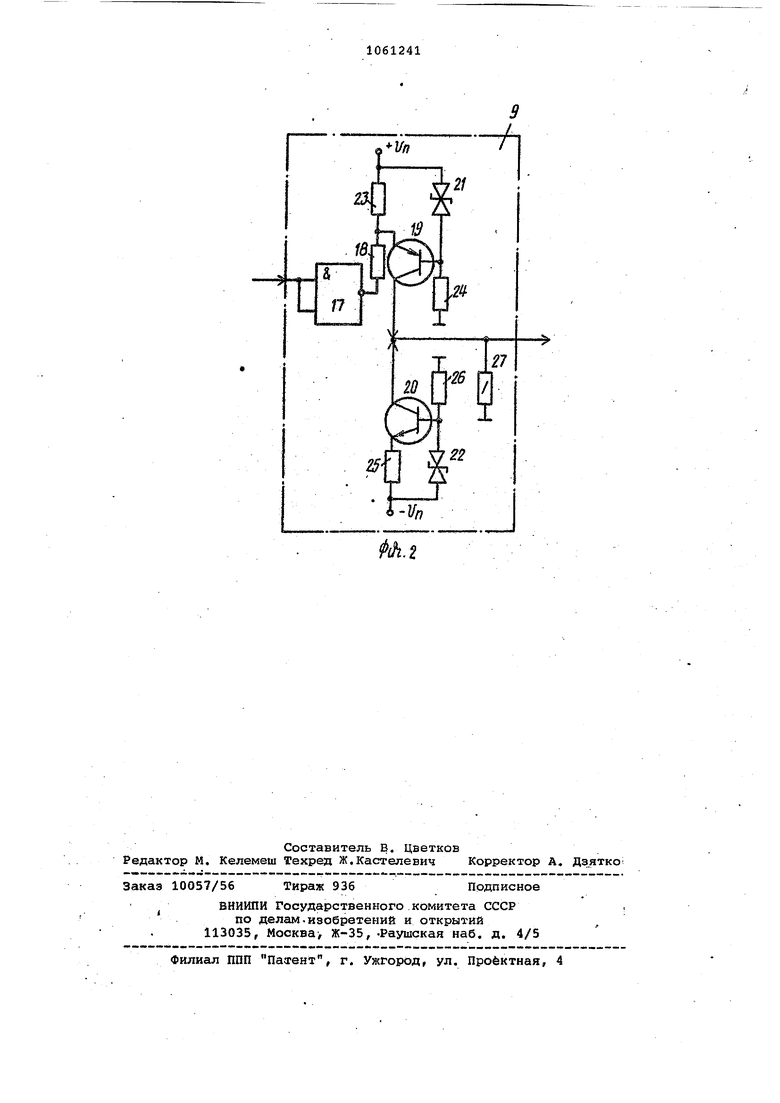

Изобретение относится к измерительной технике, спектрометрии и может быть использовано для частот.ного детектирования в широком диапа зоне частот при наличии во входном сигнале высокочастотных помех и шумов. Известен цифровой частотный, детек тор, содержащий ограничитель входных сигналов, сумматор по модулю два, делитель частоты, элемент И, тактовы генератор и фильтр нижних частот Г1; Известный частотный детектор характеризуется большой погрешностью детектирования, зависящей от формы входного сигнала; качества входного ограничителя- и от вида помех, а такж ограниченным частотным диапазоном. Наиболее близким к изобретению является цифровой частотный детектор содержащий входной формирователь,первый триггер,логический ключ,тактовый генератор, первый и второй счетчики дешифратор, переключатель детектируемой частоты и соединенные последова тельно выходной форм фователь и фильтр нижних частот, при этом выход входного формирователя соединен с R -вхо дом первого триггера, прямой выход которого подключен ко входу логического ключа, выход логического ключа соединен с выходом тактового генератора и со счетным входом первого счетчика, выходы которого подсоединены к первым входам дешифратора, вторые входы дешифратора подключены к переключателю детектируемой частоты, а выход дешифратора соединен со счетным входом второго счетчика 2. Данный цифровой чаСтотный детек- тор отличается невысокой помехозащищенностью и его целесообразно исполь зовать в устройствах с предварительной фильтрацией, либо в устройствах с малым уровнем помех. Цель изобретения - повышение поме хозащищенности. Для достижения цели в известный цифровой частотный детектор, содержащий входной формирователь, первый триггер, логический ключ, тактовый генератор, первый и второй счетчики, дешифратор, переключатель детектируемой частоты и соединённые последова тельно выходной формирователь и филь нижних частот, при этом выход входного формирователя соединен с R-входом первого триггера, прямой выход которого подключен ко входу логичес кого ключа, выход логического ключа соединен с выходом тактового генератора и со счетным входом первого счетчика, выходы которого подсоедине ны к nepBbiM входам дешифратора, втогрые входы дешифратора подключены к переключателю детектируемой частоты, а выход дешифратора соединен со счетным входом второго счетчика, в него введены последовательно соединенные первый инвертор и элемент И; второй инвертор и второй триггер, причем вход первого инвертора подключен к выходу входного, .формирователя, выход элемента И соединен с установочными входами первого и второго счетчиков, выход дешифратора подсоединен к счетному входу второго триггера, инверсный выход которого со динен со вторым входом элемента И, счетным входом первого триггера и входом выходного формирователя, а между выходом второго счетчика и R-входом второго триггера включен второй инвертор. На фиг. 1 представлена структурная схема предлагаемого цифрового частотного детектора) на фиг. 2 принципиальная схема выходного формирователя. Цифровой частотный детектор содержит вйодной формирователь 1, первый триггер 2, логический ключ 3, тактовый генератор 4, первый и второй счетчики 5 и б, дешифратор 7, переключатеЛь 8 детектируемой частоты, выходной формирователь 9, фильтр 10 нижних чайтот, первый инвертор 11, элемент И 12, второй инвертор 13, второй триггер 14, резисторы 15 и 16, при этом ВЫХОДНОЙ формирователь 9 содержит инвертор 17, резистор 18, транзисторы 19 и 20, стабилитроны 21 и 22, резисторы 23-27. Цифровой частотный детектор работает следующим образом. В момент перехода, входного сигнала из плюса в минус первый триггер 2 по установочному R-входу устанавливается в состояние О по прямому выходу. Логический ключ 3 раскорачивает х енератор 4 и разрешает прохождение тактовых импульсов на счетный вход первого счетчика 5. В это время второй триггер 14 находится в состоянии 1 по инверсному выходу. На выходе выходного формирователя 9 имеется потенциал -V.,,, . Дл появления перехода входного сигнала через нуль (из минуса в плюс) на обоих входах элемента И 12 имеется потенциал логической 1, следовательно, на его выходе и установочных J -входах ючетчиков 5 и б имеется потенциал логической 1, который запрещает счет. От момента появления импульса на выходе входного формирователя 1 до его рк энчания на выходе элемента И 12 устанавливается потенциал лог ического О, счетчик 5 начинает считать, а так как импульс на выходе формирователя 1 имеет длительность меньше , то на выходе дешифратора потенциал логической появляется, а в момент появления импульса исчетчики 5 и б устанавливаются в состояние

В момент появления переднего фронта импульса на выходе элемента И 12 появляется потенциал логического О, c ieT4hK 5 начинает считать и через время на выходе дешифратора 7 появляется потенциал логической 1, который устанавливает второй триггер 14 в состояние О по инверсному выходу. При этом на выходе выходного формирователя 9 появляется потенциал +Vg, , начинается выработка импульса длительностью TO/2. Так как триггер 14 по инверсному выходу находится в состоякии О форма входного сигнала не влияет на это сосзтоявие триггера 14 и на генерацию импульса длительностью Потенциалом Vg, на выходе формировафеля 9.

. В окончания генерации импульса длительностью Т(,/2 на выходе второго счетчика 6 появляется потеици ал логической 1, триггер 14 опрокидывается и на его инверсном вйходе появляется потенциал логической 1 который опрокидывает триггер 2 в состояние 1, закорачивает выход генератора 4, при этом на выходе выkOAHQfo формирователя 9 появляется потенциал -Vg , и устройство возвращается в исходное состояние. . В момент перехода входного сигнала Ччерёз нуль(из плюса в минус) першлй триггер 2 опрокидывается, логический ключ 3 раскорачивает выход генератора 4 и счетные импульсы начинают поступать на счетный вход счетчика 5. Однако .длительность последующих импульсов короче (воздействует помеха), чем необходимая длительность запускающего импульса, т.е. , следовательно,следующий цикл выработки импульса длительностью Тр/2 начинается в момент перехода входного сигнала через нуль (из кинуса в плюс) в следующем периоде Т,

Длительность положительного потенциала на выходе формирователя 9 равна половине периода выбранной детектируемой частоты Тр/2, длительность отрицательного потенциала на выходе формирователя 9 равна Т/- Тр/2, где T)j - период детектируемой частоты.

Потенциал полоясительного и отрицательного импульсов по модулю равны. Следовательно, сигнал на выходе фильтра 10 нижних частот линейно

пропорционален разности длительностей импульсов и описывается уравнени

V,

где V - максимальное напряжение на

м

выходе формирователя 9;

Tj,,f - период и частота тактового генератора 4/

T,f - период и частота входного сигнала.

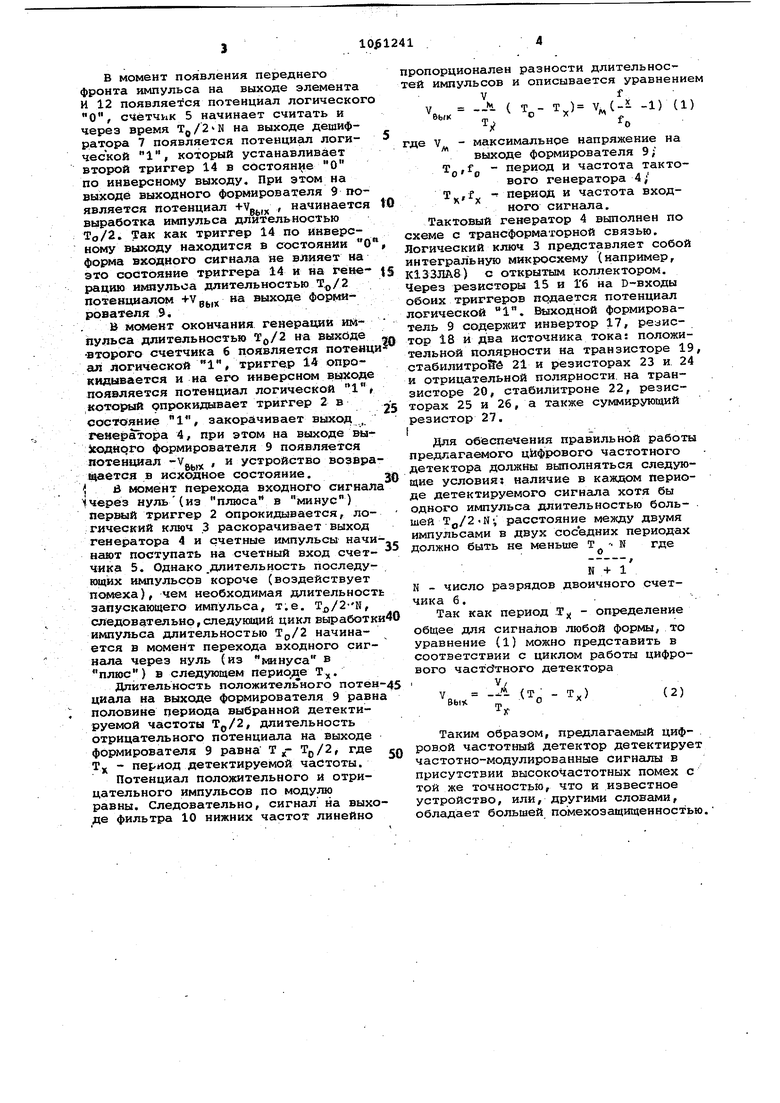

Тактовый генератор 4 выполнен по схеме с трансформаторной связью. Логический ключ 3 представляет собой интегральную микросхему (например, К133ЛА8) с открытым коллектором. Через резисторы 15 и Г6 на D-входы обоих триггеров подается потенциал логической 1. Выходной формирователь 9 содержит инвертор 17, резистор 18 и два источника тока: положительной полярности на транзисторе 19 стабилитройй 21 и резисторах 23 и 24 и отрицательной полярности, на транзисторе 20, стабилитроне 22, резисторах 25 и 26, а также суммирующий резистор 27. t- . .

Для обеспечения правильной работы предлагаемого цифрового частотного детектора должны выполняться следующие условия; наличие в каждом периоде детектируемого сигнала хотя бы одного импульса длительностью большей TQ/2N, расстояние между двумя импульсами в двух соседних периодах

должно быть не меньше Т

К

где

N + 1

N - число разрядов двоичного счетчика 6.

Так как период .Tj( - определение

общее для сигналов любой формы, то уравнение (1) можно представить в соответствии с циклом работы цифрового частотного детектора

ы. -;- с - х)

(2)

Tjc

Таким образом, предлагаемый циф- . розой частотный детектор детектирует частотно-модулированные сигналы в присутствии высокочастотных помех с той же точностью, что и известное устройство, или, другими словами, обладает большей помехозащищенностью.

Ifn

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотный детектор | 1978 |

|

SU841081A1 |

| Цифровой термометр | 1987 |

|

SU1571427A1 |

| СИНХРОННЫЙ ДЕТЕКТОР | 1997 |

|

RU2124804C1 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Устройство для цифрового измерения частоты медленно меняющихся процессов | 1987 |

|

SU1413542A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Устройство для цифрового измерения частоты | 1989 |

|

SU1666965A2 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Цифровой частотный детектор | 1985 |

|

SU1376226A1 |

ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕТЕКТОР, содержащий входной формирователь, первый триггер, логический ключ, тактовый генератор, первый и второй счетчики, дешифратор, переключатель детектируемой, частоты и соединенные последовательно выходной формирователь и фильтр нижних частот, при этом выход входного формирователя соединен с к -входом первого триггера, прямой выход которого подключен ко входу логического ключа, выход логического ключа соединен с выходом тактового генератора и со счетным входом первого счетчика, выходы которого подсоединены к первым входам дешифратора, вторые входы дешифратора подключены к переключателю детектируемой частоты, а выход дешифратора соединен со счетным, входом второго счетчика, отличающийся тем, что, с целью повышения помехозащищенности, в него введены последовательно соединенные первый инвертор и элемент И, второй инвертор и второй триггер, причем вход первого инвертора подключен к выходу входногоформироватёля, выход элемента И соединен с установочными входамипервого (П и второго счетчиков, выход дешифратора подсоединен к счетному входу второго триггера, инверсный выход которого соединен со вторым входом элемента: И, счетным входом первого триггера и входом выходного формирователя, а между выходом второго счет чика и R-вхЬдом второго триггера включен второй инвертор

Авторы

Даты

1983-12-15—Публикация

1982-04-26—Подача