вход/

е о

Ч1ЭУ hso g7

I-SB

(Л

4 4

сл

(

Изобретение относится к импульсной технике и предназначено для према ипреобразования кодовых сигналов (однополярных или двуполярных).

По основному авт.св. № 1003334 известен преобразователь биполярного кода в однополярный, содержащий два дифференциальные усилителя, два ключевьп элемента, четыре делителя, два фильтрующих конденсатора, элемент ИЛИ и выгСодной усилитель, причем к первому входу устройства подключены входы первого и второго делителя, к второму входу устройства подключены входы третьего и четвертого делителей, первый и второй фильтрующие конденсаторы включены соответствеино между входами перзого и второго дифференциальных усилителей, выходы первого и четвертого делителей с прямосмещенными входами соответственно первого и второго дифференциальных усилителей, обратносмещенные входы которых соединены с выходами соответственно третьего и второго делителей, выходы первог и второго дифференциальных усилителей соответственно через первый и вторЪй ключевые элементы соединены с входами элемента ИЛИ, выход которого соединен с выходом синхронизации устройства, выход ВТОрого ключевого элемента через выходной усилитель подключен к информационному выходу устройства.

Недостатком известного устройства является низкая помехозащищенность при работе устройства С; входными сигналами, близкими к порогу переключения, из-за появления на входах устройства дифференциального йапряжения близкого к порогу срабатьюакия, при этом дифференциальный усилитель переходит в линейный режим работы и под воздействием дестабилизирующих факторов: пульсаций напряжений питания, наводок в общей шине, парафазных помех на входе,- появляется высокочастотный звон, что ослняет работу последующих блоков. - Цель изобретения - повышение помехоустойчивости .

Поставленная цель достигается тем, что в преобразователь биполярного кода в однополярный, содержащий два дифференциальных усилителя, два ключевых элемента, четыр делителя, два фильтрующих конденсатора, элемент ИЛИ и выходной усилитель, причем к первому входу устройства- подключены входы первого и второго делителей, к второму входу устройства подключены входы третьего и четвертого делителей, первый и второй фильтрующие конденсаторы включены соответслвенно между входами первого и второго дифференциальных усилителей, выходы первого и четвертого делителей соединены с прямосмещенными

входами соответственно первого и второго -дифференциальных усилителей, обратносмещенные входы которых соединены с выходами соответственно третьего и второго делителей,

Q выходы первого и второго дифференциальных усилителей соответственно через первый и второй ключевые элементы соединены со входами элемэнта ИЛИ, выход которого является

выходом синхронизации устройства.

выход второго ключевого элемента через выходной усилитель.подключен к информационному выходу устррйств.а, введены два резистора, причем первый резистор включен меж0 ду выходом первого ключевого эле мента и обратносмещенным,входом первого дифференциального усилите- . ля, а второй резистор - между выходом второго ключевого элемента

5 и обратносмещенным входом второго дифференциального.усилителя.

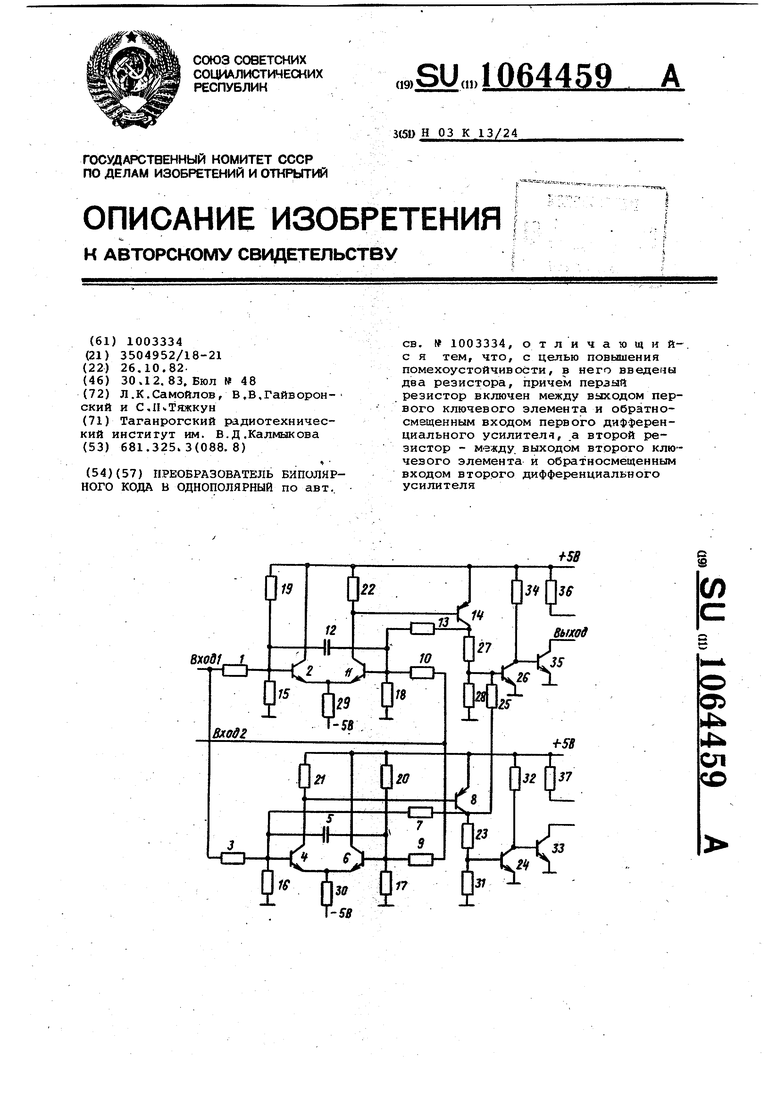

На чертеже изображена принципиальная схема устройства.

Первый вход устройства через ре0 зистор 1 соединен с базой транзи.стора 2, а через резистор 3 с базой транзистора 4, которая через фильтрующий конденсатор 5 соединена с базой транзистора 6, через ре5 зистор 7 соединена с коллектором ) транзистора 8, второй вход устройства через резистор 9 соединен с баэой транзистора б, а через ре- зистор 10 с базой транзистора Ну которая че)ез- фильтрующий конденсатрР .12 соединена с базой транзистора 2, а через резистор 13 с кол;лектором транзистора 14, базы тра.нзисторов 2, 4, б и 11 соединены с общей шиной соответственно ч.ерез

5 резисторы 15, 16, 17 и 18. Базы транзисторов 2 и б соединены с шиной источника питания и коллекторами этих транзисторов через резисто- . ры 19 и 20, коллектори транзисторов

0 и 11 соединены с шиной источника питания через резисторы 21 и 22 и с базами транзисторов 8 и 14, эмиттеры которых соединены с шиной источника Питания, коллектор тране зистора 8 через резистор 23 соединен с базой транзистора 24, а через резистор 25 с базой транзрстора 26, которая через резистор 27 соединена с коллектором транзистора 14, а через резистор 28 с

общей шиной. Эмиттеры транзисторов 2 и 11 соединены между собой и через резистор 29 соединены с другой шиной источника питания, эмиттеры транзисторов 4 и б соедине5 ны между собой и через резистор 30

также соединены с другой шиной источника питания, база транзистора ; 24 через резистор 31 соединена с ; общей шиной, а коллектор через резистор 32 соединен с шиной источ- , ника питания и с базой транзистора;-:33, колле стор которого является выходом информации устройства. Коллектор транзистора 26 через резистор 34 соединен с шиной источника питания и с базой транзистора 35, коллектор которого является выходом синхронизации устройства. Пре обрйзователь содержит резисторы 36 и 37,. - , . :- :,;,:

Первый дифференциальный усилитель реализован на транзисторах 2 и 11 и резисторах 19, 22 и 29, второй- на транзисторах 4 и 6 и резисторах 20, 21 и 30, Первый делитель содержит резисторы 1 и 15, второй - резисторы 3 и 16, третий трёзисторы 10 и 18, четвертый - резисторл 9 и 17, Первый ключевой Элемент выполнен на транзисторе 14,. второй ключевой элемент на транзисторе 8 tЭлемент ИЛИ содержит резисторы 25, 27, 34 ri 36, транзистора 26 и 35. Выходной усилитель состо-: ит из резисторов 23, 31,. 32 и 37 и транзисторов 24 и 33.

Устройство работает следующим образом /:

При дифференциальном напряжении между первым и вторым входс1ми по модулю 1леньше пороговой величины, , задаваемой резисторами 19, 15 и 20, 17 в первом и втором дифферейциальных усилителях, транзисторы 2 и 6 открыты, транзисторы 11 и 4 закрыты, закрыты транзистогжл 8, 14, 24 и 26, а транзистош 33 и 35 открыты и на Обоих вЫхода1Х устрой- . ства установлены сигналы, соответ-.: ств пощие низкому уровню. Резисторй

36 и 37 образуют внутреннюю нагрузку и при необходимости могут быть соединены с коллекторами транзисторов 35 и 33. , При синфазном изменении напряжения ( tlO В) на входах устройство остается в исходном состоянии, При изменении дифференциального напряжения на входах выше пороговpro уровня в зависимости от полярности входного напряжения либо откроются

0 транзисторы 8, 26 и 24 и на выходах появятся сигналы высоких уровней, либо откроются транзисторы-14 и 26 и на выходе синхронизации (транзисторе 35) установится высокий

5 уровень, а на выходе (транзисторе 33) - низкий, Резистивные делители входного напряжения совместно с конденсаторами 5 и 12 образуют интегрирующие звенья первого порядка,

0 выполняющие частичное подавление высокочастотных помех.

Включение в преобразователь резисторов 7 и 13 приводит к появле нию гистерезиса в ее передаточной

5 характеристике, что эквивалентн9 повышению помехозащищенности устройства .

При достижении дифференциальным входным сигналом порога Срабатыва0ния и отпирания .транзистора.14 или 8 порог срабатывания скачком меняется в сторону уменьшения (на величину напряжения, приведенного к входу устройства, 1,0-1,2 Б) 5 При уменьшении входного сигнала до нового порога переключения (задний - фронт импульса) запираются транзистор 8 или 14, а порог скачком увеличиваетс;я. Таким образом, суммарная величина дестабилизирующих

0 факторе, приведенная к входу менее 1,0-1,2 В, не вызывает ложных переключений в схеме.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь биполярного кода в однополярный | 1981 |

|

SU1003334A1 |

| Преобразователь биполярного кода в однополярный | 1988 |

|

SU1571770A2 |

| Пороговое устройство | 1981 |

|

SU1012432A1 |

| Ключевой стабилизатор постоянного напряжения | 1984 |

|

SU1233126A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU780048A1 |

| Стабилизированный источник питания с защитой | 1980 |

|

SU964606A1 |

| Импульсный стабилизатор напряжения постоянного тока | 1986 |

|

SU1410003A1 |

| Дифференциальный усилитель | 1983 |

|

SU1140227A1 |

| Реле времени | 1974 |

|

SU566273A1 |

| Стабилизатор напряжения | 2022 |

|

RU2793452C1 |

ПРЕОБРАЗОВАТЕЛЬ БИПОЛЯРНОГО КОДА В ОДНОПОЛ Я РНЫЙ по авт.. ев, № 1003334, отличающийс я тем, что, с целью повышения помехоустойчивости, в него введег ы два резистора, причем перзый резистор включен между выходом первого ключевого элемента и обратносмащенным входом первого дифференциального усилителе, .а второй резистор - между выходом второго ключевого элемента и обратносмещенным входом второго дифференциального усилителя

Авторы

Даты

1983-12-30—Публикация

1982-10-26—Подача