Изобретение относится к радиоэлектронике и может быть использо,вано в операционных усилителях и компараторах напряжения.

Известен дифференциальный усилитель, содержащий два входных транзистора, эмиттеры которых объединень1 и подключены к выходу токостабилизатора DlJ.

Однако при подаче на входы известного дифференциального усилителя больших переключающих или синфазных сигналов запирающей полярности происходит выключение входных транзисторов, длительность которого определяется током смещения дифференциального усилителя и величиной амплитуды входного сигнала, а причиной является выполнение токостабилизатора на транзисторе, включенном по схеме .с общей, базой, выход которого шунтируется паразитными емкостями.

. Наиболее близким к предлагаемому по технической сущности является дифференциальный усилитель, содержащий первьй и второй транзисторы, базы которых являются входами, коллекторы - выходами дифференциального усилителя, а в общей эмиттерной цепи включен управляемьш источник тока, выполненный на первом дополнительном транзисторе, база которого через источник напряжения смещения соединена с щиной источник питания, и на втором дополнительном транзисторе, коллектор которого непосредственно, а база через резистор соединены с шиной источника питания, причем структура второго дополнительного транзистора противоположна структурам первого и второг транзисторов 2.

Однако использование в известном дифференциальном усилителе (ДУ) управляемого источника тока, содержащего цепь обратной связи комбинированного типа - отрицательную по постоянному току и положительную .через паразитную емкость, шунтирующую вход и выход отражателя тока, приводит к сокращению допустимого входного синфазного диапазона ДУ. Кроме того, при высоких скоростях нарастания синфазного напряжения, поданного на входы ДУ, на выходе управляемого источника тока с комбинированной обратной связью наблюдается существенная неравномерность установления выходного тока.

Цель изобретения - расширение входного синфазного диапазона.

Поставленная цель достигается тем, что в дифференциальный усилитель, содержащий первый и второй транзисторы, базы которых являются входами, коллекторы - выводами дифференциального усилителя, а в общей эмиттерной цепи включен управляемый источник тока, выполненный на первом дополнительном транзисторе, база которого через источник напряжения смещения соединена с пшной источника питания, и на втором дополнительном транзисторе, коллектор которого непосредственно, а база через резистор соединены с щиной источника питания, причем структура второго дополнительного транзистора противоположна структурам первого дополнительного и первого и второго транзисторов, между эмиттером первого дополнительного транзистора и шиной источника питания введен резистивный делитель, отвод которого соединен с эмиттером второго дополнительного транзистора, между базой которого и коллектором первого дополнительного транзистора введен конденсатор, а между базой второго дополнительного транзистора и шиной источника питания введен прямо5 смещенный диод, причем коллектор первого дополнительного транзистора является выходом управляемого исто ;ника тока.

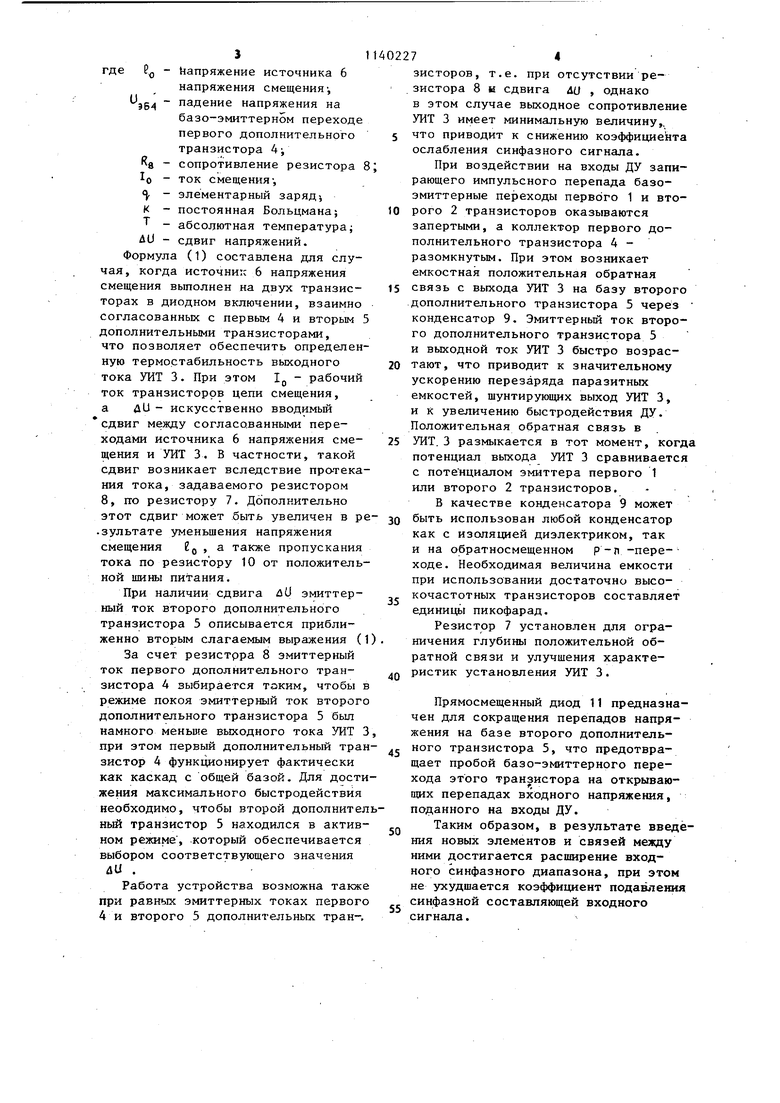

На чертеже представлена принципиальная электрическая схема дифференциального усилителя.

Дифференциапьньй усилитель содержит первый 1 и второй 2 транзисторы, управляемьш источник 3 тока (УИТ), первый 4 и второй 5 дополнительные транзисторы, источник 6 пряжения смещения, резистивный делитель на резисторах 7 и 8,конденсатор 9,резистор 10,прямосмещеннь1й диод 11.

Устройство работает следующим образом.

В режиме покоя, когда на входы ДУ поданы фиксированные потенциалы, выходной ток УИТ 3 определяется по е следующей приближенной формуле

Tf

0

(1)

ит

R

8

где Р - Напряжение источника 6

напряжения смещения-, 364 падение напряжения на

базо-эмиттерном переходе первого дополнительного транзистора 4;

сопротивление резистора 8; IG ток смещения-, - элементарный заряд j К - постоянная Больцмана; - абсолютная температураi Ди - сдвиг напряжений. Формула (1) составлена для случая, когда источник 6 напряжения смещения выполнен на двух транзисторах в диодном включении, взаимно согласованных с первым 4 и вторым 5 ополнительными транзисторами, что позволяет обеспечить определенную термостабильность выходного тока УИТ 3. При этом 1 - рабочий ток транзисторов цепи смещения, а ли - искусственно вводимьм сдвиг между согласованными переходами источника 6 напряжения смещения и УИТ 3. В частности, такой сдвиг возникает вследствие про-текания тока, задаваемого резистором 8, яо резистору 7. Дополнительно этот сдвиг может быть увеличен в результате уменьшения напряжения смещения Kj, , а также пропускания тока по резистору 10 от положительной шины питания.

При наличии сдвига лО эмиттерный ток второго дополнительного транзистора 5 описывается приближенно вторым слагаемым выражения (1)

За счет резистрра 8 эмиттерный ток первого дополнительного транзистора 4 выбирается таким, чтобы в режиме покоя эмиттерный ток второго дополнительного транзистора 5 был намного меньше выходного тока УИТ 3, при этом первый дополнительный транзистор 4 функционирует фактически как каскад с общей базой. Для достижения максимального быстродействия необходимо, чтобы второй дополнительный транзистор 5 находился в активном режиме , .который обеспечивается выбором соответствующего значения dU .

Работа устройства возможна также при равных эмиттерных токах первого 4 и второго 5 дополнительных тран-.

зисторов, т.е. при отсутствии резистора 8 к сдвига ди , однако в этом случае выходное сопротивление УИТ 3 имеет минимальную величину,,

что приводит к снижению коэффициента ослабления синфазного сигнала.

При воздействии на входы ДУ запирающего импульсного перепада базоэмиттерные переходы первого 1 и второго 2 транзисторов оказываются запертыми, а коллектор первого дополнительного транзистора 4 разомкнутым. При этом возникает емкостная положительная обратная

связь с выхода УИТ 3 на базу второго дополнительного транзистора 5 через конденсатор 9. Эмиттерный ток второго дополнительного транзистора 5 и выходной ток УИТ 3 быстро воэрас0 тают, что приводит к значительному ускорению перезаряда паразитных емкостей, шунтирующих выход УИТ 3, и к увеличению быстродействия ДУ. Положительная обратная связь в

5 УИТ. 3 размыкается в тот момент, когда потенциал выхода УИТ 3 сравнивается с потенциалом эмиттера первого 1 или второго 2 транзисторов.

В качестве конденсатора 9 может

0 быть использован любой конденсатор как с изоляцией диэлектриком, так и на обратносмещенном р-п -переходе. Необходимая величина емкости при использовании достаточно высокочастотных транзисторов составляет единиць пикофарад.

Резистор 7 установлен для ограничения глубины положительной обратной связи и улучшения характеQ ристик установления УИТ 3.

Прямосмещенный диод 11 предназначен для сокращения перепадов напряжения на базе второго дополнитель- ного транзистора 5, что предотвращает пробой базо-эмиттерного перехода этого транзистора на открывающих перепадах входного напряжения, поданного на входы ДУ.

Таким образом, в результате введения новых элементов и связей между ними достигается расширение входного синфазного диапазона, при этом не ухудшается коэффициент подаштения синфазной составляющей входного

сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференциальный усилитель | 1983 |

|

SU1146792A1 |

| Дифференциальный усилитель | 1983 |

|

SU1124427A1 |

| Дифференциальный усилитель | 1986 |

|

SU1427558A1 |

| Дифференциальный усилитель | 1983 |

|

SU1279050A1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439779C1 |

| УПРАВЛЯЕМЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2008 |

|

RU2384936C1 |

| Дифференциальный усилитель | 1982 |

|

SU1084963A1 |

| Дифференциальный усилитель | 1981 |

|

SU1104648A1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2439784C1 |

| Двухтактный усилитель | 1981 |

|

SU1020975A1 |

ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ, содержащий первый и второй транзисторы, базы которых являются входами, коллекторы - выходами JИффepeнциального усилителя, а в общей эмиттер ной цепи включен управляемый источник тока, выполненный на первом дополнительном транзисторе, база которого через источник напряжения смещения соединена с шиной источника питания, и на втором дополнительном транзисторе, коллектор которого непосредственно, а база через резистор соединены с шиной источника питания, причем структура второго дополнительного транзистора противоположна структурам первого дополнительного и первого и второго тран.зисторов, отличающийся тем, что, с целью расширения входного синфазного диапазона, между эмиттером первого дополнительного транзистора и шиной источника питания введен резистивный делитепь, отвод которого соединён с эмиттером второго дополнительного транзистора, между базой которого и коллектором первого дополнительного транзистора введен конденсатор, а между базой второго дополнительного транзистора и шиной источника питания введен прямосмещенный диод, причем коллектор первого дополнительного транзистора является выходом управьэ to ляемого источника тока.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кудряшов Б.П | |||

| Аналоговые интегральные микросхемы, и др | |||

| М., Радио и связь, 1981, с | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 3610269/18-09 | |||

Авторы

Даты

1985-02-15—Публикация

1983-09-28—Подача