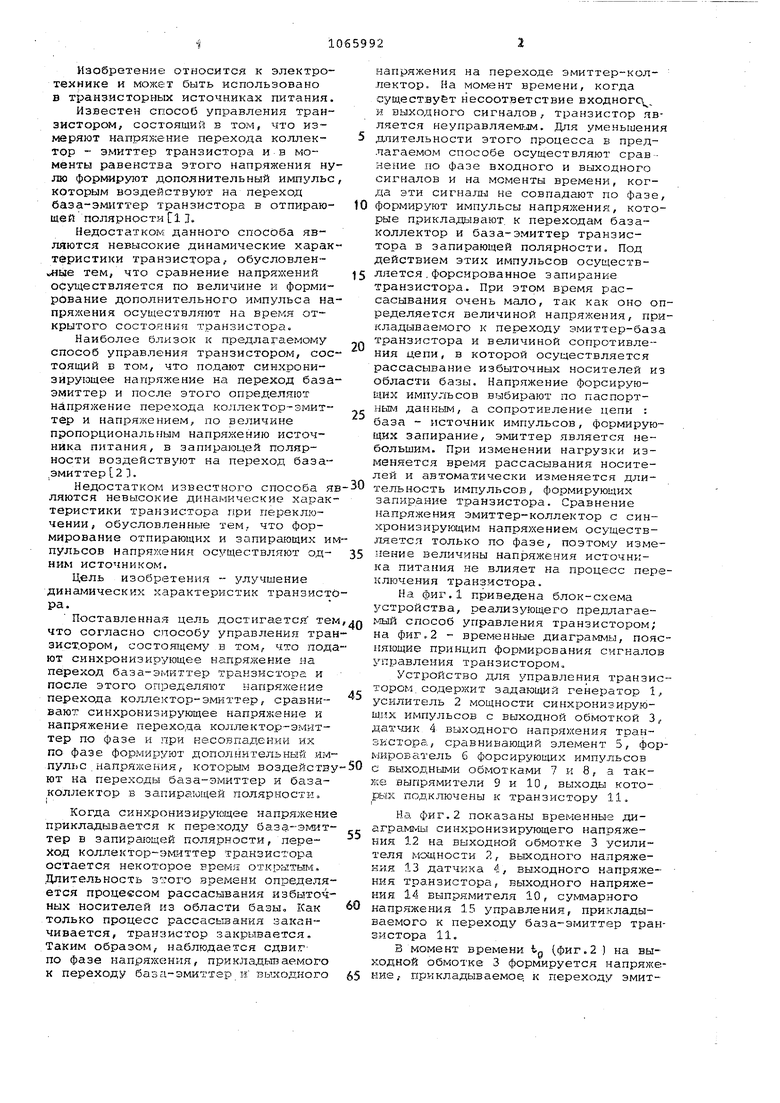

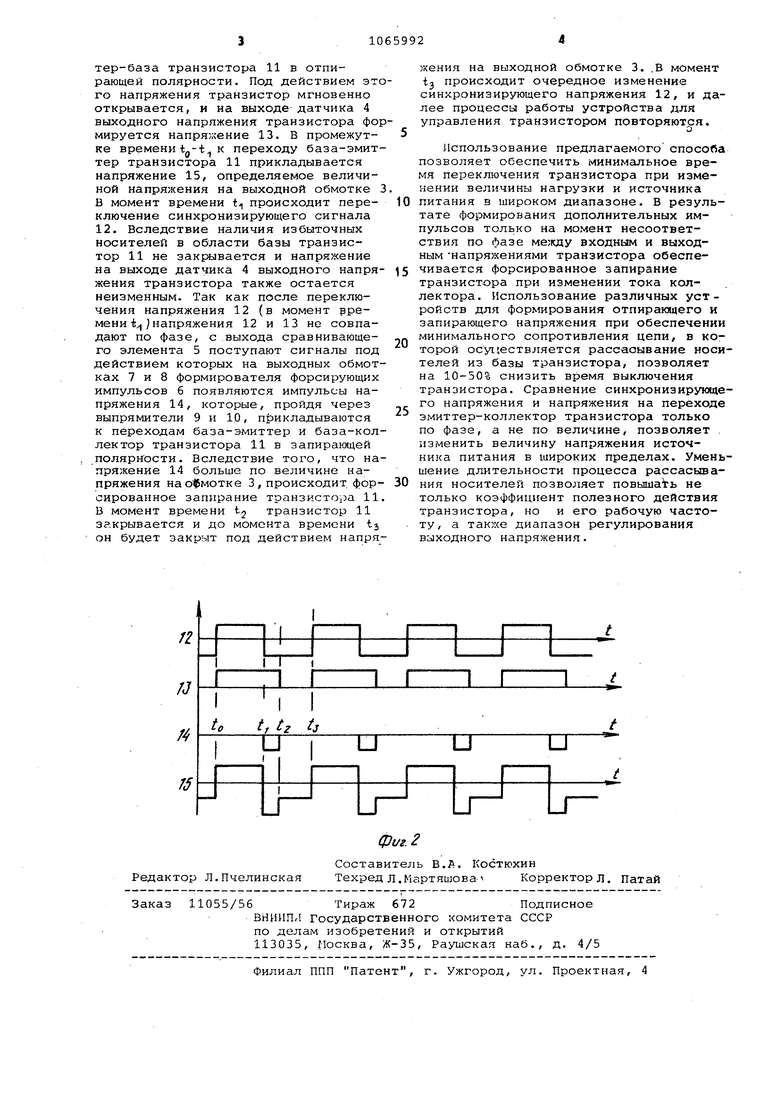

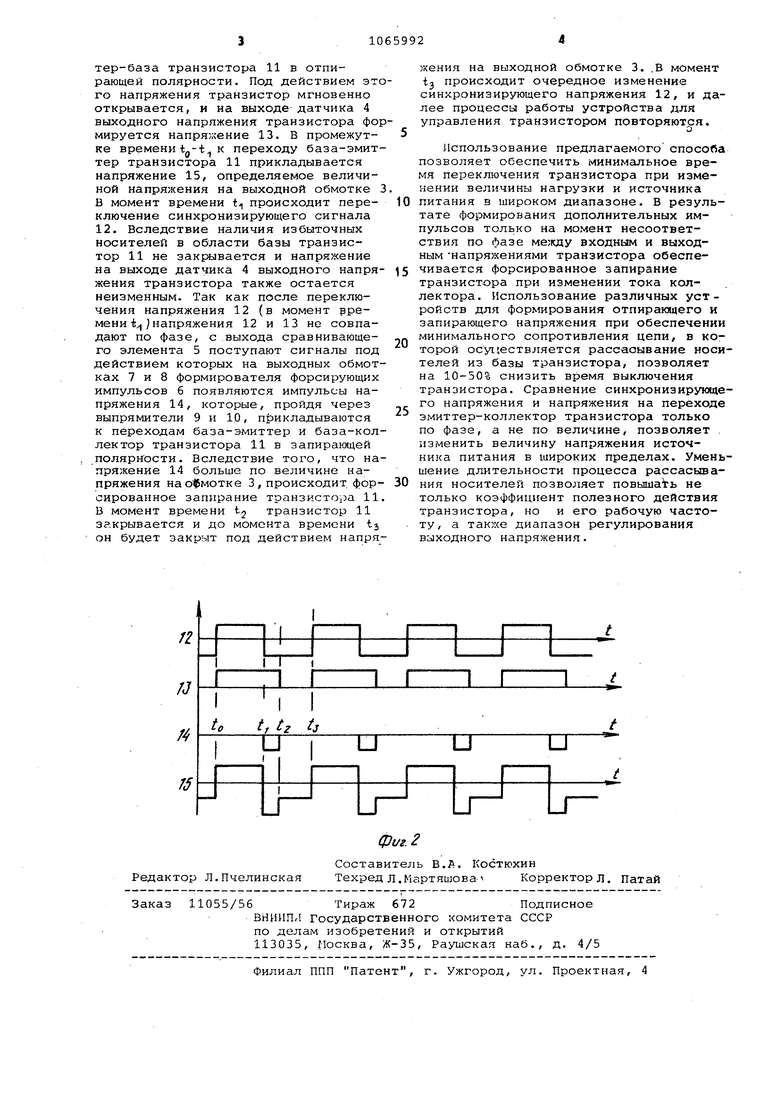

Изобретение относится к электротехнике и можб:г быть использовано в транзисторных источниках питания. Известен способ управления транзистором, состоящий в том, что измеряют напряжение перехода коллектор - эмиттер транзистора и в моменты равенства этого напряжения ну лю формируют дополнительный импульс которым воздействуют на переход база-эмиттер транзнстора в отпирающей полярности 1. Недостатком данного способа являются невысокие динамические харак теристики транзистора, обусловлен ные тем, что сравнение напряжений осутдествляется по величине и формирование дополнительного импульса на пряжения осуществляют на время открытого состоянргя транзистора. Наиболее близок к предлагаемому способ управления транзистором, сос тоящий Б том, что подают синхронизирующее напряжение на переход база эмиттер и после этого определяют напряжение перехода коллектор-эмиттер и напряжением, по величине пропорциональр ым напряжению источника питания, в запираюцей полярности воздействуют на переход база,эмиттер 2 . Недостатком известного способа я ляются невысокие динамические харак теристики транзистора при переключении, обусловленные тем, что формирование отпирающих и запирающих и пульсов напряжения осуществляют одним источником. Цель изобретения - улучшение динамических характеристик транзист ра. Поставленная цель достигается те что согласно способу управления тра зист.ором, состоящему в том, что под ют синхронизирующее напряжение на переход база-эмиттер транзистора и после этого определяют напряжение перехода коллектор-эмиттер, сравнивают синхронизирующее напряжение и напряжение перехода коллектор-эмиттер п-о фазе и при несовггадении их по фазе формируют дополнительный им пульс напряжения, которым воздейств ют на переходы база-эмиттер и базаколлектор в запирающей полярности. Когда синхронизирующее напряжени прикладывается к переходу база-эдлит тер в запиршс1дей полярности, переход коллектор-эмиттер транзистора остается некоторое время открытьп-д. .Длительность времени определя ется процеесом рассасывания избыточ ных носителей из области базы. Как только процесс рассасывания заканчивается, транзистор закрывается. Таким образом, наблюдается сдвигпо фазе напряжения, прикла,цьшаемого к переходу база-эмиттер и вьшодного напряжения на переходе эмиттер-коллектор. На момент времени, когда существует несоответствие входного. и выходного сигналов, транзистор является неуправляемым. Для уменьшения длительности этого процесса в предлагаемом способе осуществляют сравнение по фазе входного и выходного сигналов и на моменты времени, когда эти сигналы не совпадают по фазе, формируют импульсы напряжения, которые прикладывают, к переходам базаколлектор и база-эмиттер транзистора в запирающей полярности. Под действием этих импульсов осуществляется .форсированное запирание транзистора. При этом время рассасывания очень мало, так как оно определяется величиной напряжения, прикладываемого к переходу эмиттер-база транзистора и величиной сопротивления цепи, в которой осуществляется рассасывание избыточных носителей из области базы. Напряжение форсирующих импульсов выбирают по паспортным данным, а сопротивление цепи : база - источник импульсов, формирующих запирание, 3NmTTep является небольшим. При изменении нагрузки изменяется время рассасывания носителей и автоматически изменяется длительность импульсов, формирующих запирание транзистора. Сравнение напряжения эмиттер-коллектор с синхронизирующим напряжением осуществляется только по фазе, поэтому изменение величины напряжения источника питания не влияет на процесс переключения транзистора. На фиг.1 приведена блок-схема устройства, реализующего предлагае ый способ управления транзистором; на фиг.,2 - временные диаграммы, поясняющие принцип формирования сигналов управления транзистором. Устройство для управления транзистором, содержит задающий генератор 1, усилитб:ль 2 мощности синхронизирующ.-ux импульсов с выходной обмоткой 31, датчик 4 выходного напряжения транзистора, сравнивающий элемент 5, формировггтель 6 форсирующих импульсов с выходными обмотками 7 и 8, а также выпрямители 9 и 10, выходы которБК-: подключены к транзистору 11, На фиг.2 показаны временные диагра.ммы синхронизирующего напряжения 12 на выходной обмотке 3 усилителя мощности 2, выходного напряжения 13 датчика 4, выходного напряжения транзистора, выходного напряжения 14 выпрямителя 10, суммарного напряжения 15 управления, прикладываемого к переходу база-эмиттер транзистора 11. В момент времени tg (фиг.2 ) на выходной обмотке 3 формируется напряжение, прикладываемое, к переходу эмиттер-база транзистора 11 в отпирающей полярности. Под действием этого напряжения транзистор мгновенно открывается, и на выходе датчика 4 выходного напряжения транзистора формируется напря кение 13. В промежутке времени tg-t к переходу база-эмиттер транзистора 11 прикладывается напряжение 15, определяемое величиной напряжения на выходной обмотке 3 В момент времени t., происходит переключение синхронизирующего сигнала 12. Вследствие наличия избыточных носителей в области базы транзистор 11 не закрывается и напряжение на выходе датчика 4 выходного напряжения транзистора также остается неизменным. Так как после переключения напряжения 12 (в момент рремениt)напряжения 12 и 13 не совпадают по фазе, с выхода сравнивающего элемента 5 поступают сигналы под действием которых на выходных обмотках 7 и 8 формирователя форсирующих импульсов б появляются импульсы напряжения 14, которые, пройдя через выпрямители 9 и 10, прикладываются к переходам база-эмиттер и база-коллектор транзистора 11 в запирающей полярности. Вследствие того, что напряжение 14 больше по величине напряжения нао рмотке 3, происходит, форсированное запирание транзистора 11 В момент времени tj транзистор 11 закрывается и до момента времени tj он будет закрыт под действием напряжения на выходной обмотке 3. .В момент tj происходит очередное изменение синхронизирующего напряжения 12, и далее процессы работы устройства для управления транзистором повторяются,

О

Использование предлагаемого onocofia позволяет обеспечить минимальное время переключения транзистора при изменении величины нагрузки и источника питания в широком диапазоне. В результате формирования дополнительных импульсов только на момент несоответствия по фазе ме;кду входным и выходным напряжениями транзистора обеспечивается форсированное запирание транзистора при изменении тока коллектора. Использование различных устройств для формирования отпирающего и запирающего напряжения при обеспечении минимального сопротивления цепи, в которой осуществляется рассасывание носителей из базы транзистора, позволяет на 10-50% снизить время выключения транзистора. Сравнение синхронизирующего напряжения и напряжения на переходе эмиттер-коллектор транзистора только по фазе, а не по величине, позволяет . изменить величину напряжения источника питания в широких пределах. Уменьшение длительности процесса рассасывания носителей позволяет повышать не только коэффициент полезного действия транзистора, но и его рабочую частоту, а также диапазон регулирования выходного напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный транзисторный инвертор | 1982 |

|

SU1084933A1 |

| Инвертор | 1981 |

|

SU1015476A1 |

| Полумостовой преобразователь постоянного напряжения | 1986 |

|

SU1394379A1 |

| Устройство для управления транзисторным инвертором | 1986 |

|

SU1415387A1 |

| Преобразователь постоянного напряжения | 1987 |

|

SU1504771A1 |

| Двухтактный преобразователь постоянного напряжения | 1988 |

|

SU1636974A1 |

| Устройство для управления запираемым тиристором | 1991 |

|

SU1786610A1 |

| Устройство для управления силовым транзисторным ключом | 1980 |

|

SU951704A1 |

| Устройство для управления силовым транзисторным ключом | 1985 |

|

SU1288840A1 |

| Однотактный преобразователь постоянного напряжения | 1988 |

|

SU1536490A1 |

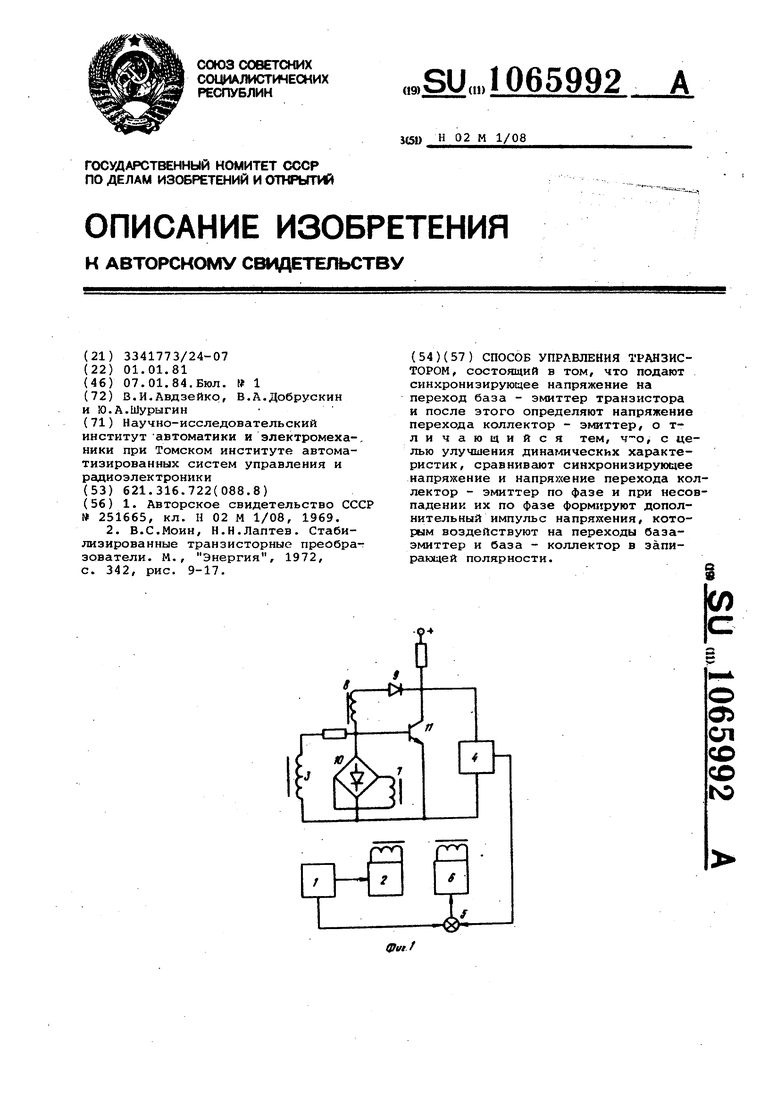

СПОСОБ УПРАВЛЕНИЯ ТРАНЗИСТОРОМ, состоящий в том, что подают синхронизирующее напряжение на переход база - эмиттер транзистора и после этого определяют напряжение перехода коллектор - эмиттер, о тличающийся тем, , с целью улучшения динамических характеристик, сравнивают синхронизирующее напряжение и напряжение перехода коллектор - эмиттер по фазе и при несовпадении их по фазе формируют дополнительный импульс напряжения, которым воздействуют на переходы базаэмиттер и база - коллектор в запирающей полярности. сь ел СО ю

Авторы

Даты

1984-01-07—Публикация

1981-01-01—Подача