элемента и и к первому входу первого триггера, выход первого триггера подключен к второму входу второго элемента И, выход которого подключен к второму входу счетчика с коэффициентом пересчета пик второму входу сдвигающего регистра, а первый вход второго элемента И подключен к выходу генератора тактовых импульсов и к входу делителя, выход делителя

подключен к входу кольцевого счетчика с коэффициентом пересчета гт , к третьему входу измерителя выходного сигнала и к второму входу первого элемента И, выход первого элемента И подключен к второму входу второго буферного регистра, выходы которого подключены к входам первого дешифратора и к вторым входам измерителя выходного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный аналого-цифровойАНАлизАТОР СпЕКТРА | 1978 |

|

SU834572A1 |

| Анализатор гармоник электрической сети | 1985 |

|

SU1352393A1 |

| Параллельный анализатор спектра | 1979 |

|

SU813312A1 |

| Анализатор случайных процессов | 1979 |

|

SU813474A1 |

| Калибратор параметров качества трехфазной цепи | 1980 |

|

SU957184A1 |

| Анализатор спектра | 1985 |

|

SU1287033A1 |

| Устройство для автоматического регулирования температуры | 1988 |

|

SU1645945A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Анализатор частотного спектра | 1980 |

|

SU900209A1 |

| Генератор случайных чисел | 1979 |

|

SU798770A1 |

ПАРАЛЛЕЛЬНЫЙ АНАЛИЗАТОР СПЕКТРА, содержащий К параллельно включенных избирательных каналов, каждый из которых состоит из последовательно соединенного полосового фильтра, детектора, интегратора и ключа, а также общий для всех каналов измеритель выходного сигнала, подключенный к выходам ключей, о тличающийс я тем, чтс/, с целью повышения точности и быстродействия измерения путем введения зависш ых от центральных частот избирательных каналов циклов из опроса, избирательные каналы в нем объединены в п октавных групп, каждая из которых состоит из m избирательных каналов, и он снабжен кольцевым счетчиком с коэффициентом пересчета гп , дешифратором последнего состояния, кольцевого счетчика, формирователем короткого импульса, генератором тактовых импульсов , .делителем, двумя элементами И, блоком цифрового дифференциального анализатора, состоящего из сдвигающего регистра, сумматора и линии задержки, а также счет.чиком с коэффициентом пересчета п, дешифратором последнего состояния счетчика, первым триггером, генератором одиночного импульса, элементом иЛИ, вторым.триггером, третьим элементом И, первым буферным регистром, вторым буферным регистром, первым дешифратором, имеющим п выходов, и г вторыми дешифраторами, имеющими ГП выходов, которые подключены к управляющим входам ключей соответствующих октавных групп, при этом первые входы вторых дешифраторов подключены к выходам первого дешис ратора, а вторые входы подключены к выходам кольцевого счетчика с коэффициентом пересчета m , к первым входам измерителя выходного сигнала и к входам дешифратора последнего состояния кольцевого счетчика, выход которого подключен к первому входу первого элемента И и к входу формирователя короткого импульса,выход которого подключен к первому входу счетчика с коэффициен- tg том Пересчета Y , к второму входу (Л первого триггера, к первому входу генератора одиночного импульса, к второму входу второго триггера и к второму входу сумматора, причем первый вход сумматора подключен к выходу сдвигающего регистра, а его третий вход подключен к выходу линии задержки, вход которой подключен к 35 30 второму выходу сумматора, первый выход сумматора подключен к первсаду входу Сдвигающего регистра и к втоэо рому входу генератора одиночного импульса, выход которого подключен :о ел к второму входу элемента ИЛИ и к первому входу второго триггера,- выход этого триггера подключен к второму входу третьего элементами, выкод которого подключен к первому входу элемента ИЛИ, выход элемента ИЛИ подключен к.второму входу первого буферного регистра, выходы которого подключены к первым входам второго буферного регистра, а первые входы подключены к выходам Счетчика с коэффициентом пересчета пик входам дешифратора последнего состояния счетчика, выход которого подключен к первому входу третьего

Изо6ре,тение относится к радиоизмерительной технике и предназначено для анализа спектров электрических сигналов.

Известны анализаторы спектра, содержащие избирательные каналы в составе полосового фильтра, детектора, интегратора, коммутатора, выходного измерителя и блока управления СП.

Недостатком устройств является низкое быстродействие.

Наиболее, близким к изобретению является анализатор спектра, содержащий параллельно включенные избирательные каналы, каждый из которых состоит из последовательно соединенных фильтра, детектора, интегратора и ключа, а также блок управления и измеритель выходного сигнала С21.

Недостатком известного анализатора является низкаяточность измерений при большом числе избирательных каналов.

Цель изобретения - повышение точности и быстродействия измерения путем введения зависимых от центральных частот избирательных каналов циклов их опроса.

Йоставленная цель достигается тем, что в параллельном анализаторе спектра, содержащем к параллельно включенных избирательных каналов, каждый из которых состоит из последовательно соединенного полосового фильтра, детектора, интегратора и ключа, а также общий для всех KaiHa,лов измеритель выходного сигнала, подключенный к выходам ключей, избирательные каналы объединены в п октавных групп, каждая из которых состоит из г«1 избирательных каналов, и он снабжен кольцевым счетчиком с коэффициентом пересчета п , дешифратором последнего состояния кольцевого счётчика, формирователем короткого импульса, генератором тактовых импульсов, делителем, двумя элементами И, блоком цифрового дифференд.1,иального анализатора, состоящего

из сдвигающего регистра, сумматора и линии задержки, а также счетчиком с коэффициентом пересчета гу , дешифратором последнего состояния счет5 чика, первым триггером, генератором одиночного импульса, элементом ИЛИ, вторым триггером, третьим элементом И, nepBbuvi буферным регистром, вторым буферным регистром, первым дешифраO тором, имеющим t выходов, и П вторы-, ми дешифраторами-, имеющими tvA выходов, .которые подключены к управляющим входам ключей соответствующих октавных групп, при этом первые входы вторых дешифраторов подключены к вы-; ходам первого дешифратора, а вторые входы подключены к выходам кольцевого счетчика с коэффициентом пересчета т, к первым.входам измерителя выходного сигнала и к входам дешиф0 ратора последнего состояния кольцевого счетчика, выход которого подключен к первому входу первого элемента И и к входу формирователя короткого импульса, выход которого

5 подключен к первому входу счетчика . с коэффициентом пересчета п , к второму входу первого триггера, к первому входу генератора одиночного иМпульса, к второму входу второго

0 триггера и к второму входу сумматора, причем первый вход сумматора подключен к выходу сдвигающего регистра, а его третий вход подключен к выходу линии задержки, вход кото5 рой подключен к второму выходу сумматора, первый выход сумматора подключен к первому входу сдвигающего .регистра и к второму входу генератора одиночного импульса, выход которого подключен к второму входу элемента ИДИ и к первому входу второго триггера, выход этого триггера подключен к -второму входу третьего элемента И, выход которого подключен к первомувходу элемента ИЛИ, выход

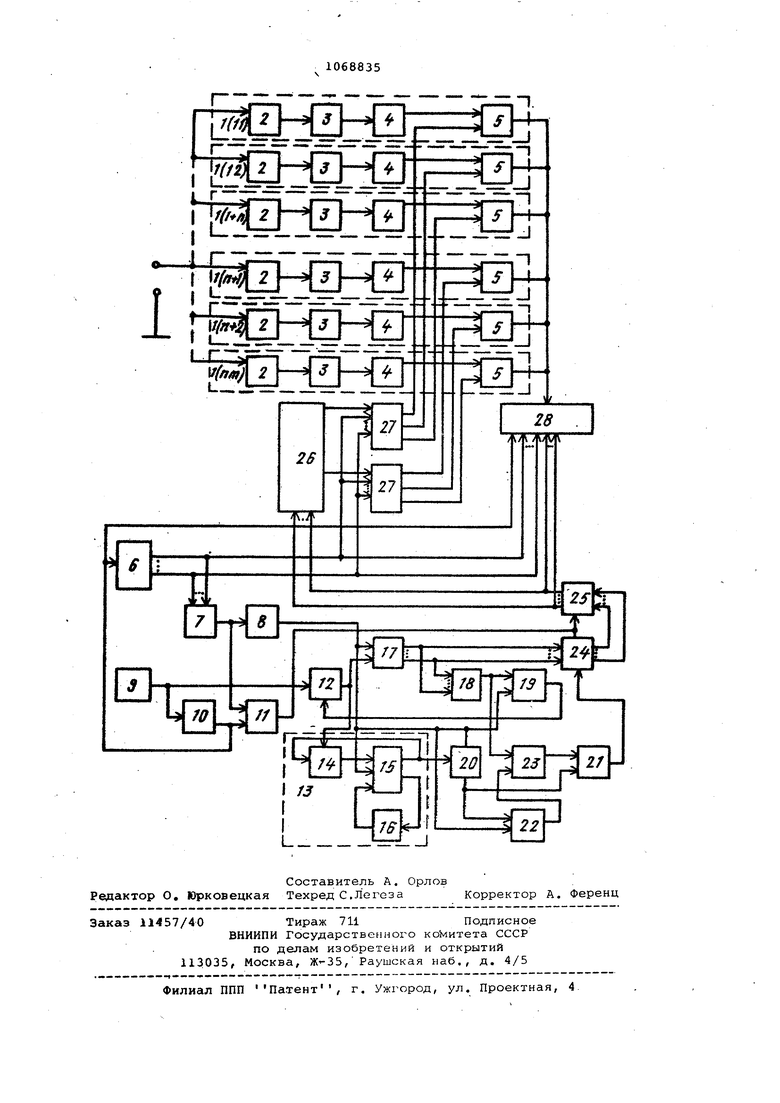

5 элемента ИЛИ подключен к второму входу первого буферного регистра, выходы которого подключены.к первым входам второго буферного регистра,а первые входы подключены к выходам счетчика с коэффициентом пересчета |fV и к входам дешифратора последнего состояния счетчика, выход которого подключен к первому входу третьего элемента И и к первому входу первого триггера, выход первого триггера под ключен к второму входу второго элемента И, выход которого подключен к второму входу счетчика с коэффициентом пересчета Пик второму входу сдвигающего регистра, а первый вход второго элемента И подключен к выходу генератора тактовых импульсов и к входу делителя, выход делителя подключен к входу кольцевого счетчик с коэффициентом пересчета fn , к третьему входу измерителя выходного сигнала и к второму входу первого элемента И, выход первого элемента И подключен к второму входу второго буферного регистра, выходы.которого подключены к входам первого дешифра тора и к вторым входам измерителя выходного сигнала. На чертеже представлена структур ная схема анализатора. Устройство содержит избирательные каналы 1, состоящие из полосово фильтра 2 с одинаковой для всех кан лов относительной полосой пропускания, детектора 3, интегратора 4, ключа 5, а также кольцевой счетчик 6 с коэффициентом пересчета гп , дешифратор 7 последнего состояния кольцевого счетчика, формирователь короткого импульса, генератор 9 тактовых импульсов, делитель 10, пе вый элемент И 11, второй элемент И 12/ блок 13 цифрового дифференциального анализатора, состоящий из сдвигающего регистра 14, сумматора 15 и линии 16 задержки, счетчик 17, с коэффициентом пересчета п , дешифратор 18 последнего состоАния счетчика, первый триггер 19, генера тор 20 одиночного имц ульса, элемент ИЛИ 21, второй триггер 22, третий элемент И 23, первый буферный регис 24, второй буферный регистр 25, пер вый дешифратор 26, второй дешифратор 27, измеритель 28 .выходного сиг нала. Параллельный анализатор спектра работает следующим образом. ИсследуемЬй сигнал подается на параллельно соединенные избирательные каналы 1, объединенные в 1Л октав ных групп, каждая из которых содерж m избирательных каналов 1, выходы которых подключены к входу измерите ля 28 выходного сигнала. Так как для исключения потери информации вр мя цикла опроса канала должно быть близко к времени анализа, время цик ла опроса избирательных каналов не должно быть одно и то же для каждо,,го из них и должно зависе,ть от их полосы пропускания. Для этого избирательные каналы разделены на октавные группы и их ко(утация осуществляется по определенному закону.I Генератор 9 тактовых импульсов вьарабатывает тактовые импульсы, поступающие на вход второго элемента И 12 и на вход делителя 10. Делитель 10 производит деление тактовой частоты, причем не менее, чем в П раз. С выхода делителя 10 тактовые импуль сы поступают на счетный вход кольцевого счетчика с коэффициентом пересчета m и для синхронизации процесса измерения на входы измерителя 28 выходного сигнала. После счета m импульсов на выходе дешифратора 7 последнего состояния кольцевого счетчика образуется уровень логической , который поступает на первый вход первого элемента И 11 и подготавливает его к открыванию, а также на вход формирователя 8 короткого импульса. На выходе формирователя 8 короткого импульса образуется импульс подготовки, который поступает на вход установки в ноль счетчика 17.с коэффициентом пересчета г. и устанавливает на его выходах код 00...00, на единичные входы первого триггера 19 и второго триггера 22, устанавливая на их прямых выходах уровень логической , на первый вход генератора 20 одиночного импульса, устанавливая на его выходе сигнал логического О, на первый вход слагаемого сумматора IS. Сумматор 15 вместе со сдвигающим регистром 14 и линией 16 задержки работают по схеме блока 13 цифрового дифференциального анализатора. На nepBCW входе слагаемого сумматора 15 находится уровень логического О , поступающий с выхода rv -разрядного сдвигающего регистра 14, так как содержимое регистра 14 - 00...00. В результате суммирования на выходе сумматора 15 образуется уровсзнь логической , поступающий на вход сдвигающего регистра 14 и на второй вход генератора 20 одиночного импульса. На выходе генератора 20 одиночного импульса образуется одиночный импульс логической . Этот импульс, поступая на нулевой ход второго триггера 22, переводит состояние на его прямом выходе в логический О, а также, поступая на ВТОРОЙ вход элемента ИЛИ 21, образует на его выходе импульс логической , который, поступая на вход разрешения записи первого буфер ного регистра 24, разрешает запись кода счетчика 17 с коэффициентом пересчета П. В этот момент код 00...00. С выходов первого буферного регистра 24 этот код поступает на вхсды второго буферного регистра 25 Когда на выходе делителя 10 появится w-t-l импульс, он пройдет через первый элемент И 11, так как на первом входе первого элемента И 11 уровень логической , поступающий с дешифратора 7 последнего состояния кольцевого счетчика. С выхо да первого элемента И 11 импульс ло гической «I поступает на вход ра решения записи второго буферного ре гистра 25. Во второй буферный регистр 25 перепишется код с первого буферного регистра 24. Код с выходо буферного регистра 25 поступает на входы первого дешифратора 26. При коде 00...00 на первом выходе перво го дешифратора 26 вырабатывается ур вень логической и производитс выб-орка первого из вторых дешифрато ров 27. На вторые входы вторых де-г. шифраторов 27 поступает код кольцевого счетчика 6 с коэффициентом пересчета гп. С изменением этого кода последовательно вырабатываются сигналы логической на выходах выбранного второго дшиифратора 27, поочередно открывающие ключи 5 первой октавной группы. Уров-ень логической , поступающий с прямого выхода первого триггера 19, разрешает прохождение тактовых импульсов с выхода генератора 9 тактовых импульсов через вто рой элемент И 12 на счетный вход счетчика 17 с коэффициентом пересче та п и на вход сдвига сдвигающего регистра 14 до тех пор, пока счетчи 17 с коэффициентсим пересчета tt не просчитает п импульсов, после чего на выходе двиифратора 18 последнего состояния счетчика образуется уровень логической , который, дей ствуя на нулевой вход первого триггера 19, изменяет состояние его прямого выхода в логический и запрещает дальнейшее прохождение тактовых импульсов. Так как в первсни из п тактов на выходе суммы сумматора 15 был уровень логической , то после сдв га на г тактов содержимое сдвигающего регистра 14 будет 00...01. После того,. как на выходе формирователя 8 короткого импульса появится следующий импульс, схема сработает аналогично, причем на первом входе слагаемого сумматора 15 находится уровень логической , поступакяций с выхода сдвигающего регистра 14. Поэтому на выходе сумматора 15 будет уровень логического d, а уровень логической i появится на выходе переноса сумматора 15, и на выходе суммы сумматора 15 уррвень логической .появится, задержанный на такт линией 16 задержки. Этот уровень логической , поступая на второй вход генератора 20 одиночного импульса, вызовет на его выходе появление уровня логической , и на выходе эле- мента ИЛИ 21 также появится уровень логической . Этот сигнал, поступая на вход разрешения записи первого буферного регистра 14, разрешит запись кода счетчика 17 с коэффициентом пересчета п , который будет в этот момент 00. ..01. Когда на выходе делителя 10.появится очередной импульс, произойдет запись этого кода во второй буферный регистр 25. По этому коду на первом дешифраторе 26 сигнал логической Ч образуется на следующем выходе и осуществится опрос следующей октавной группы. В работе схемы возможен момент, когда содержимое сдвигакицего регистра 14 будеу 11... 11. При этом генератор 20 одиночного импульса не сможет отработать одиночный импульс логической . В таком случае, когда на выходе дацифратора 18 последнего состояния счетчика образуется уровень логичесэтот уровень поступит на первый вход третьего элемента И 23, на втором входе третьего элемента И 23 также будет уровень логической , поступающий с прямого выхода второго триггера 22, так как генератор 20 одиночного импульса, не отработав логической не перебросит состояние его {инверсного выхода. На выходе третьего элемента И 23 образуется уровень логической , поступающий на первый вход элемента ИЛИ 21.. На выходе элемента ИЛИ 21 появится уровень логической , который разрешит запись в первый буферный регистр 24. При этом код будет 111...11. После того, как этот код перепишется.во второй буферный регистр 25, произойдет опрос последней а-и октавной группы. Так как работа всей схемы определяется работой блока 13 цифрового дифференциального анализатора, то следуюцей опрашиваться будет первая октавная группа и т.д. Для синхронизации процесса измерения и привязки результата измерения к соответствующему избирательному каналу на входам измерителя 28 выходного сигнала подаются коды кольцевого счетчика 6 с коэффициентом пересчета т, второго буферного регистра 25, а также сигнал с выхода делителя 1 О . Применение изобретения позволяет повыси1ь точность измерений за счет уменьшения времени на цикл onроса высокочастотных избирательных каналов при не влияющем на точность измерения некотором увеличении времени цикла опроса низкочастотных избирательных каналов. Так, при опросе 45 избирательных каналов третьоктавного анализатора спектра в диапазоне частот от 1 Гц до 25 кГц, объе диненных в 15 октавных групп при времени одного такта опроса 2 мс (0,66 мс время измерения на одном избирательном канале) время цикла опроса самой высокочастотной октавной группы составляет 4 мс (соответственно такой, же цикл и для каждого

избирательного канала этой группы), а самой низкочастотной - 33 с.

При опросе избирательных каналов последовательно один за другим, в известно устройстве, время цикла

опроса для всех каналов одинаково и составляет (при времени измерения на один канал 0,66 мс) 29,7 мс, что много для высокочастотных каналов, и в то же время излишне так часто

опрёииивать низкочастотные. Таким образом, для данного случая при применении предлагаемЬго устройства время цикла опроса высокочастотных каналов уменьшается в 7,4 раза.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Третьоктавный анализатор спектра в реальном времени, модель 3347 | |||

| Каталог фирмы Брюль и Къер, Дании, 1976 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Автоматический спектроанализатор | 1974 |

|

SU588504A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-01-23—Публикация

1981-04-24—Подача