4

OfS

со

Изобретение относится к вычислительной технике и может быть применено для группового управления манипуляторами и монтажно-сборочным оборудованием в системах реального масштаба времени.

Цель изобретения - сокращение аппаратурных затрат.

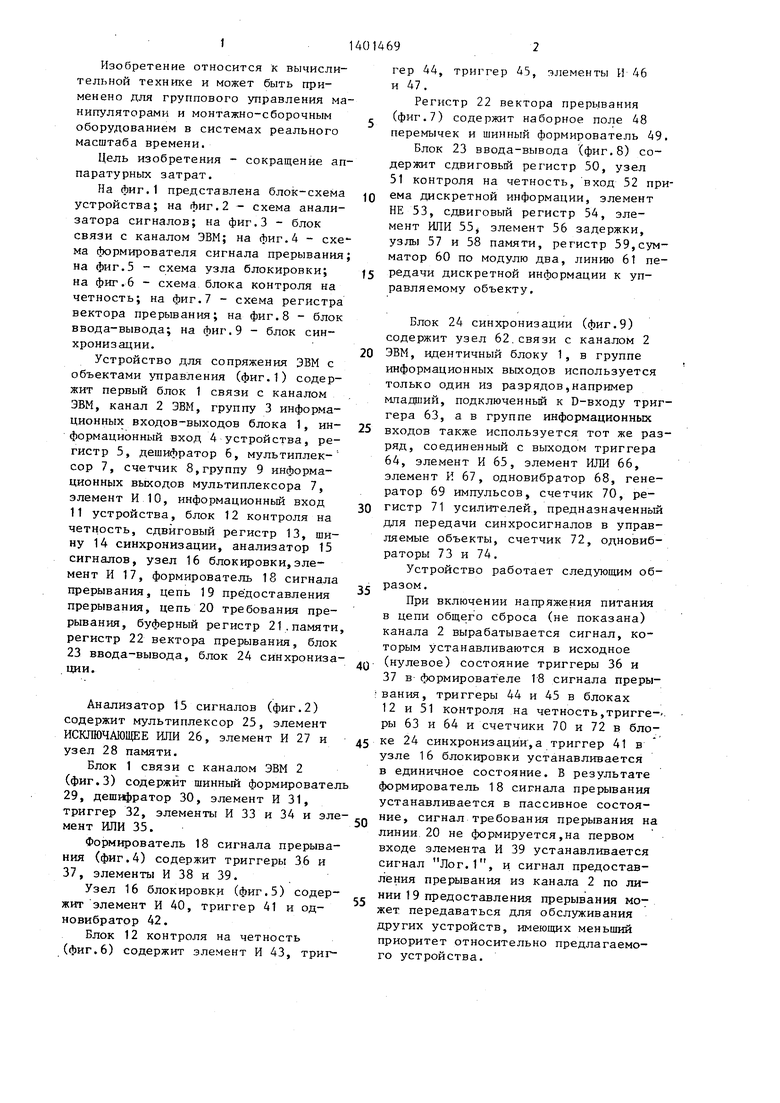

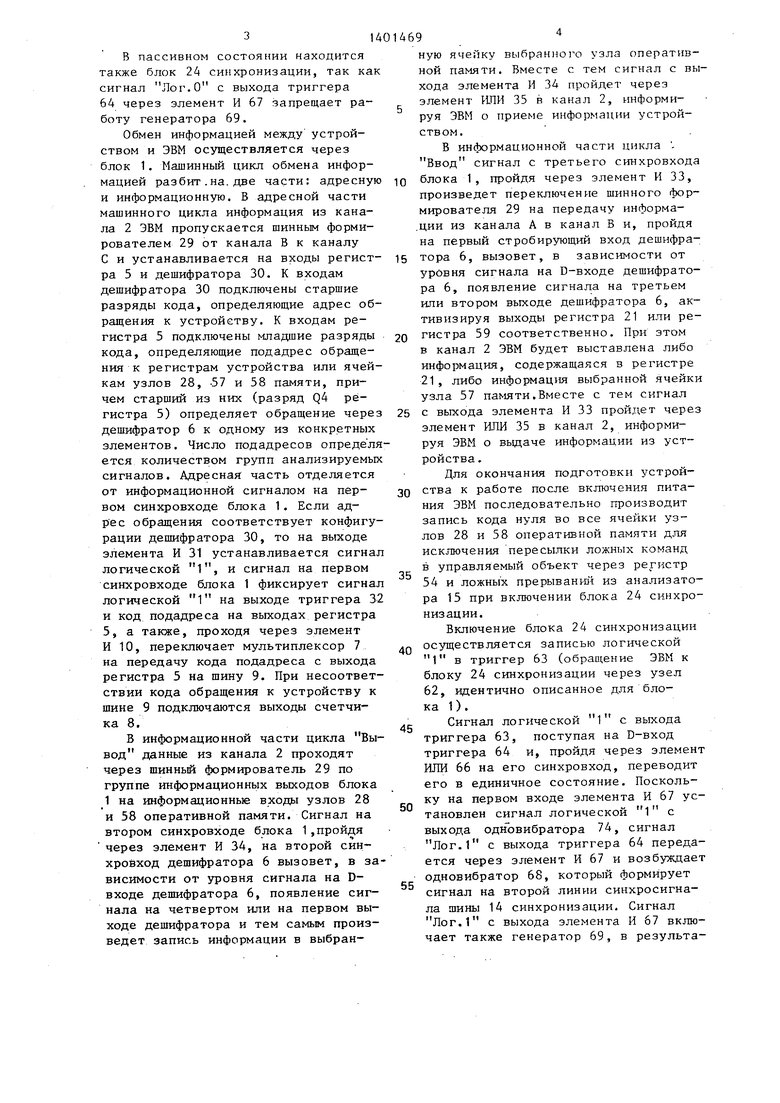

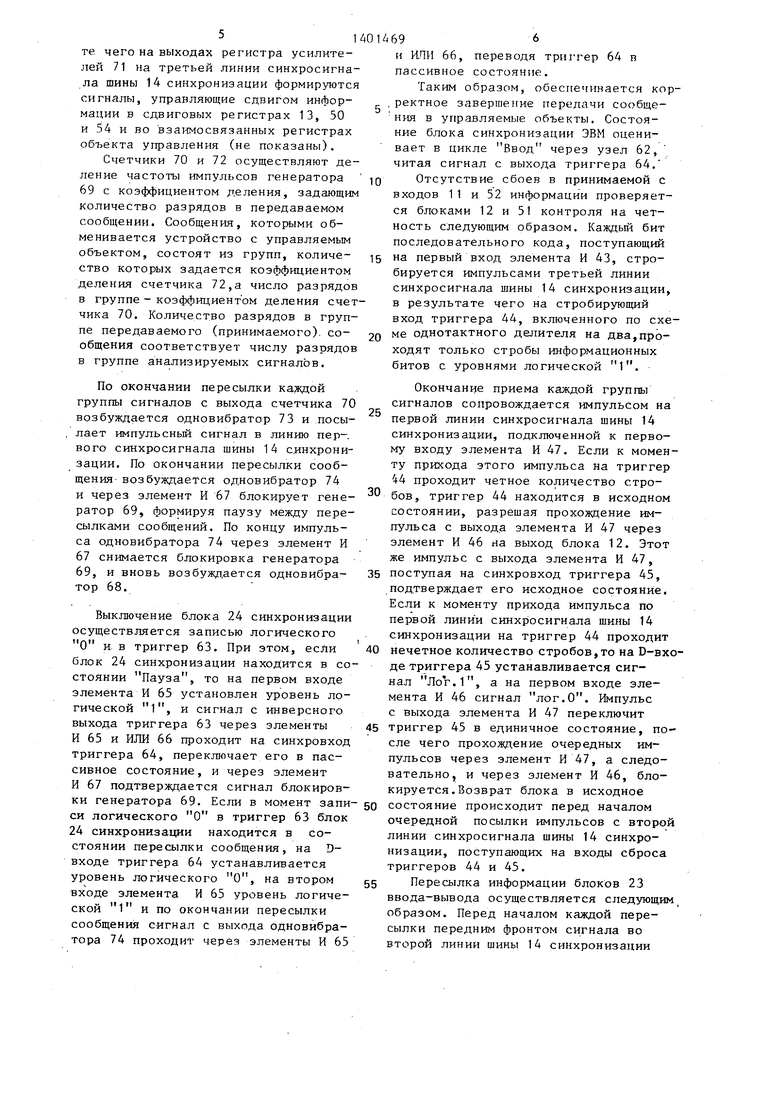

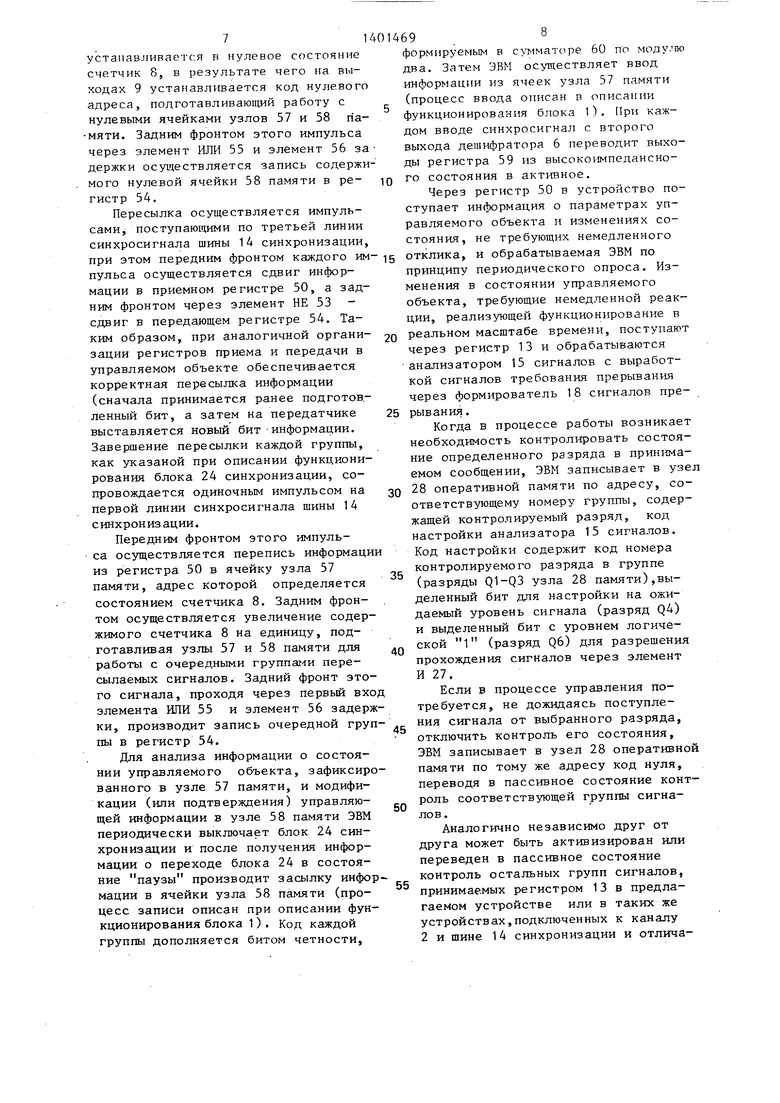

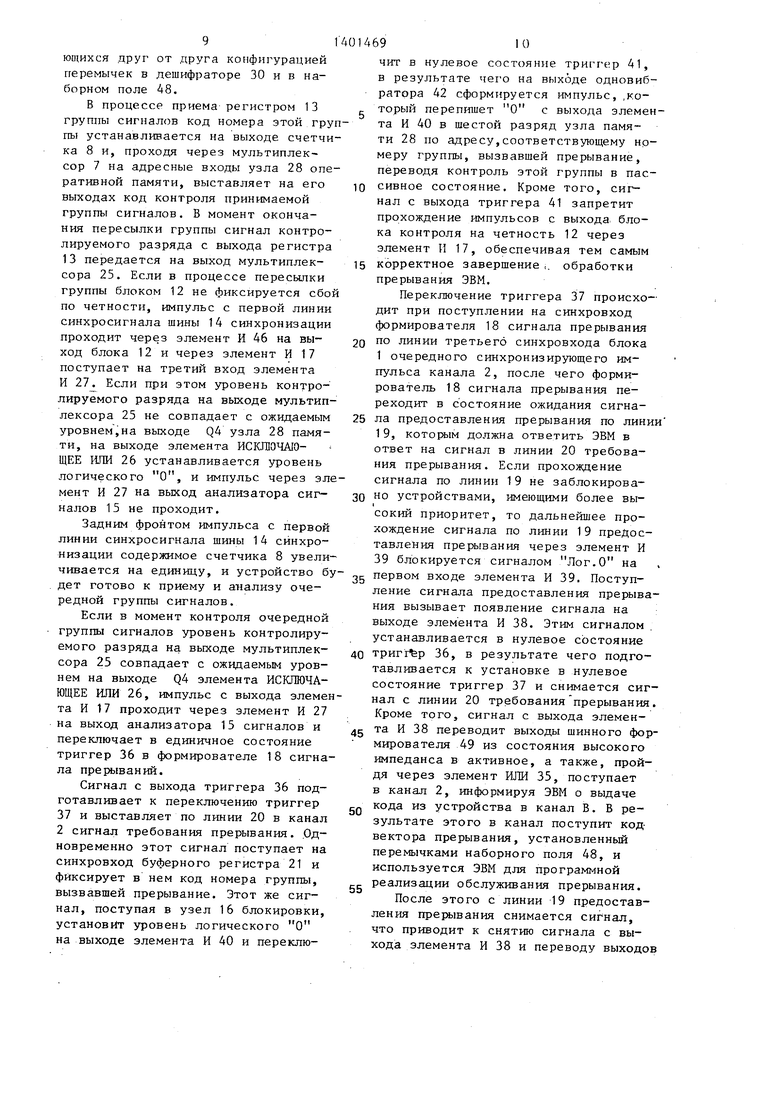

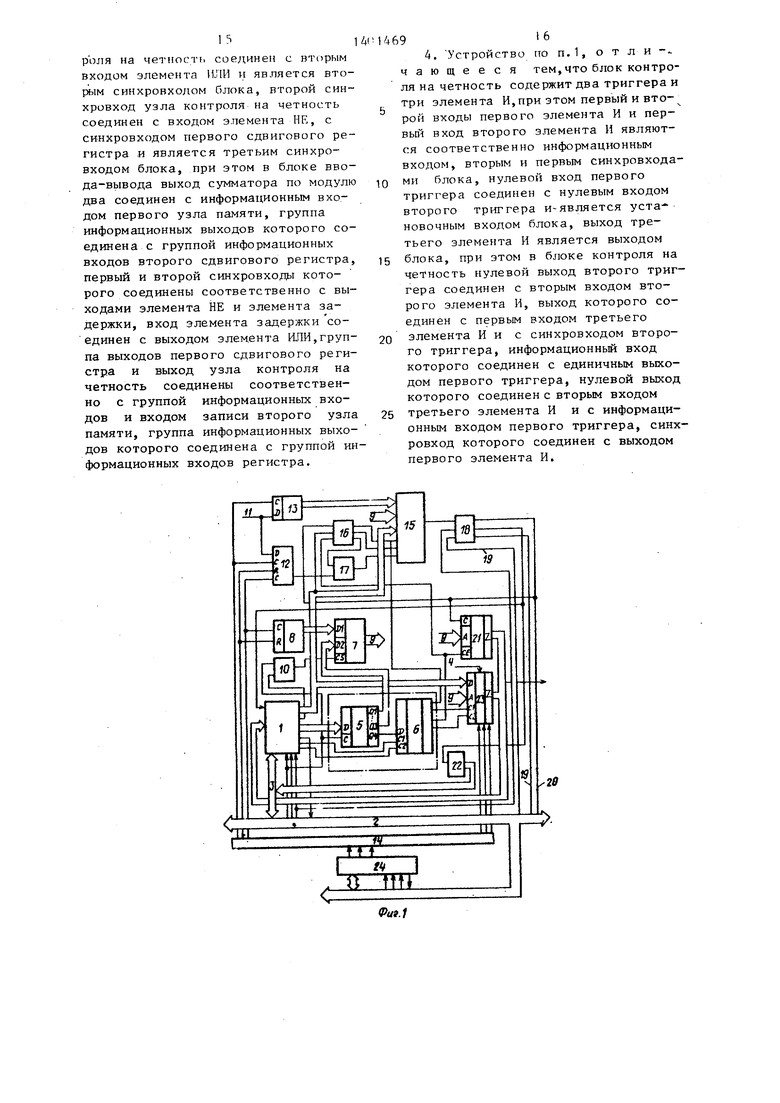

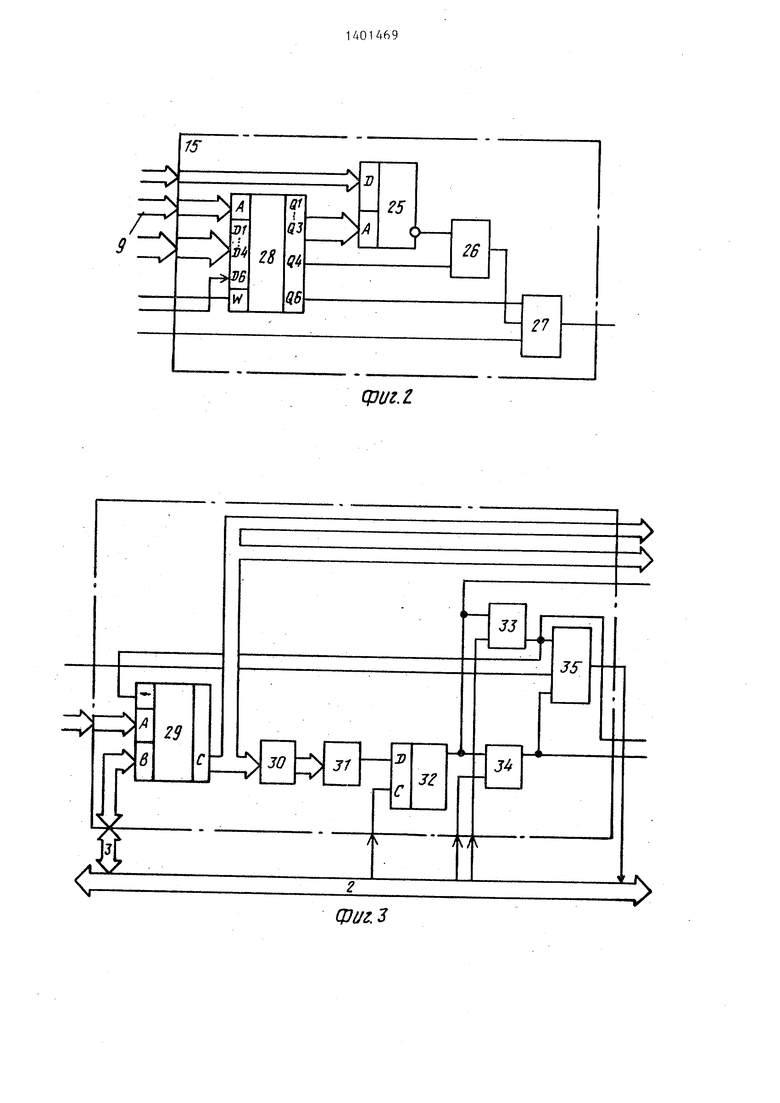

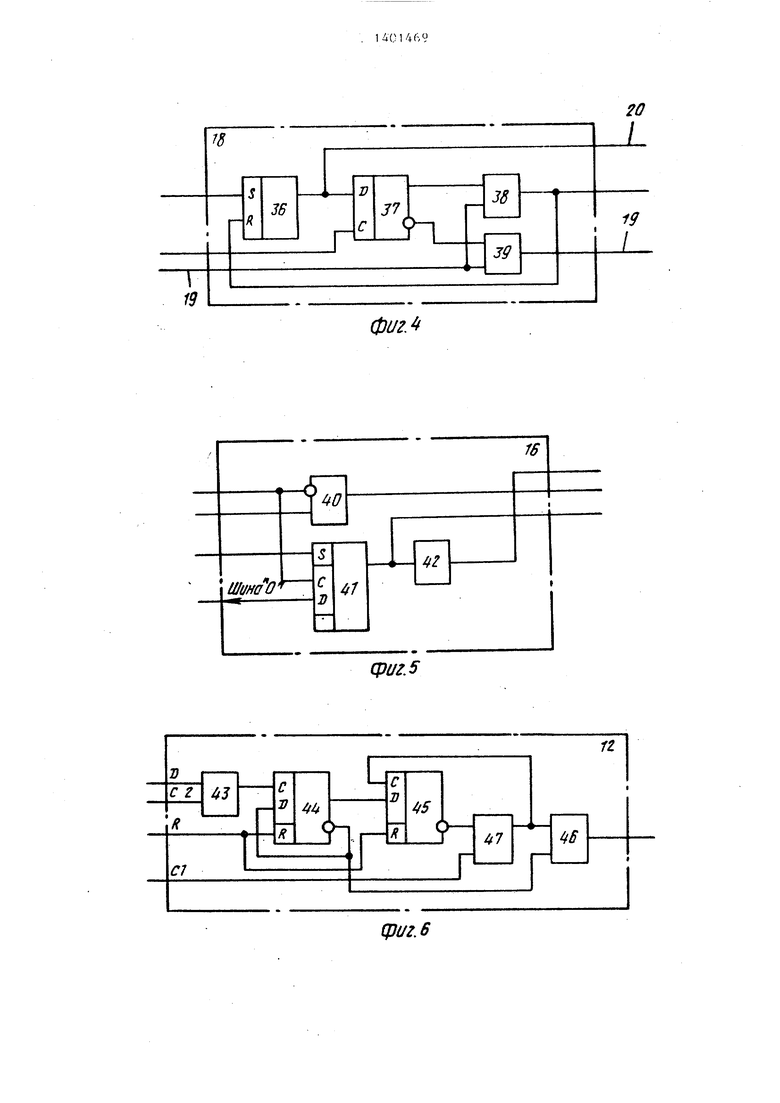

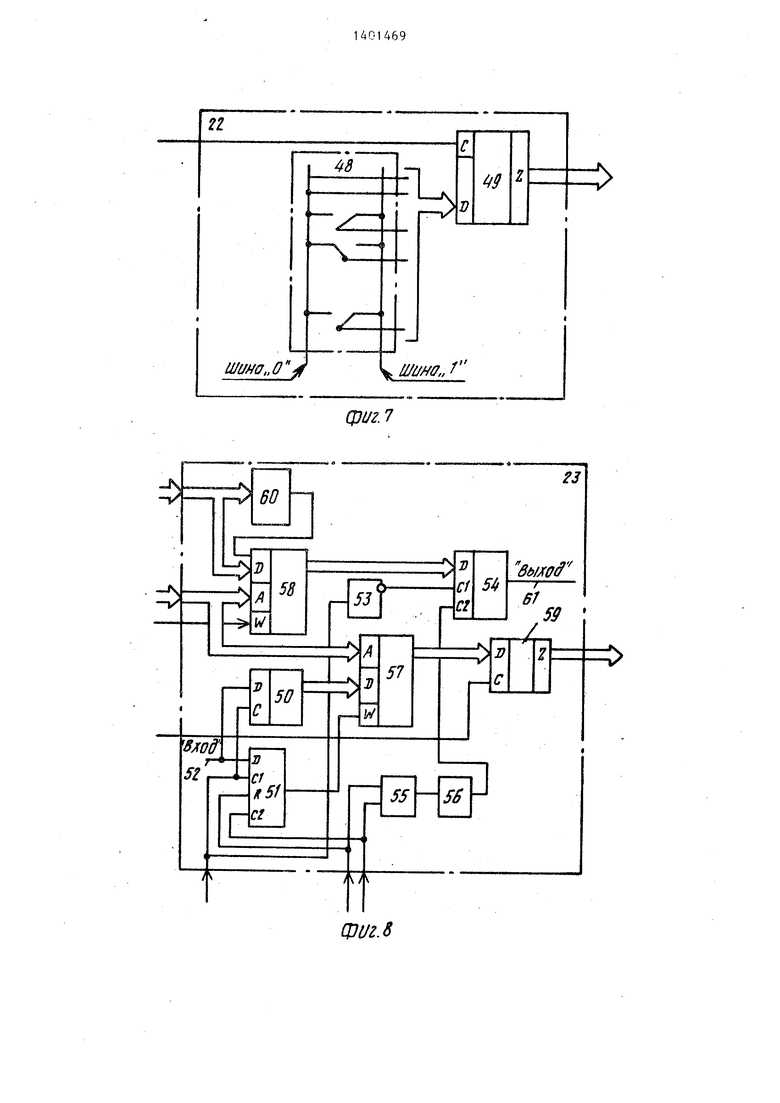

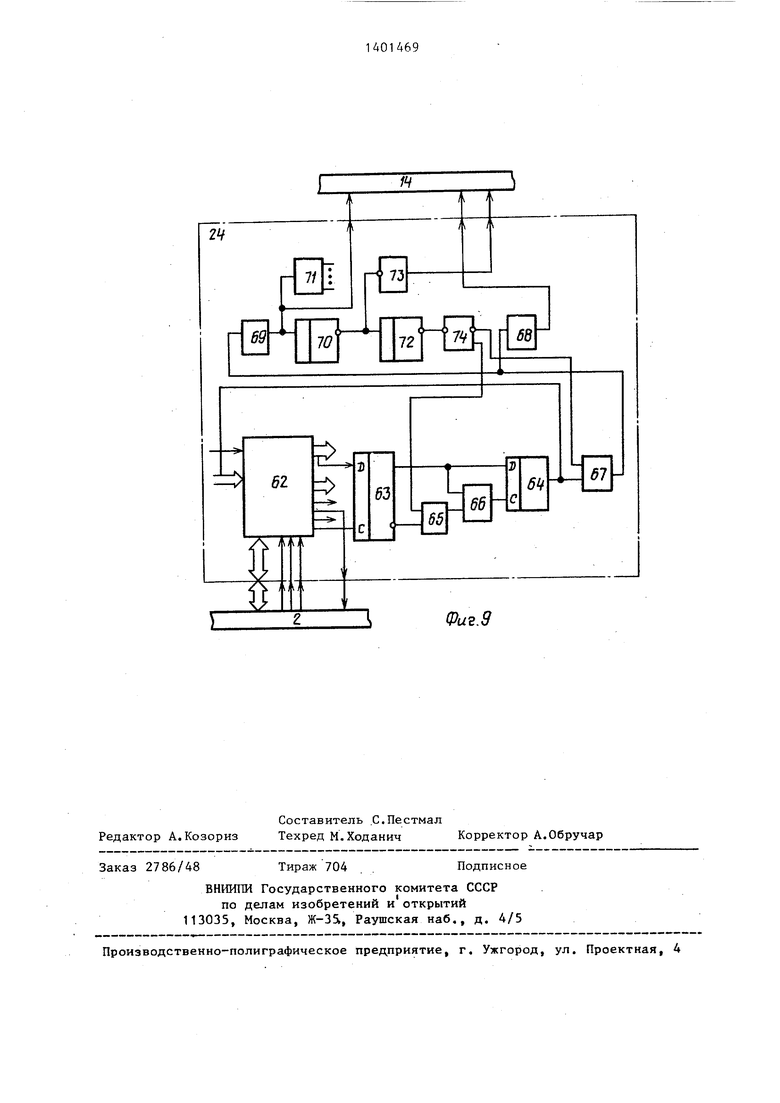

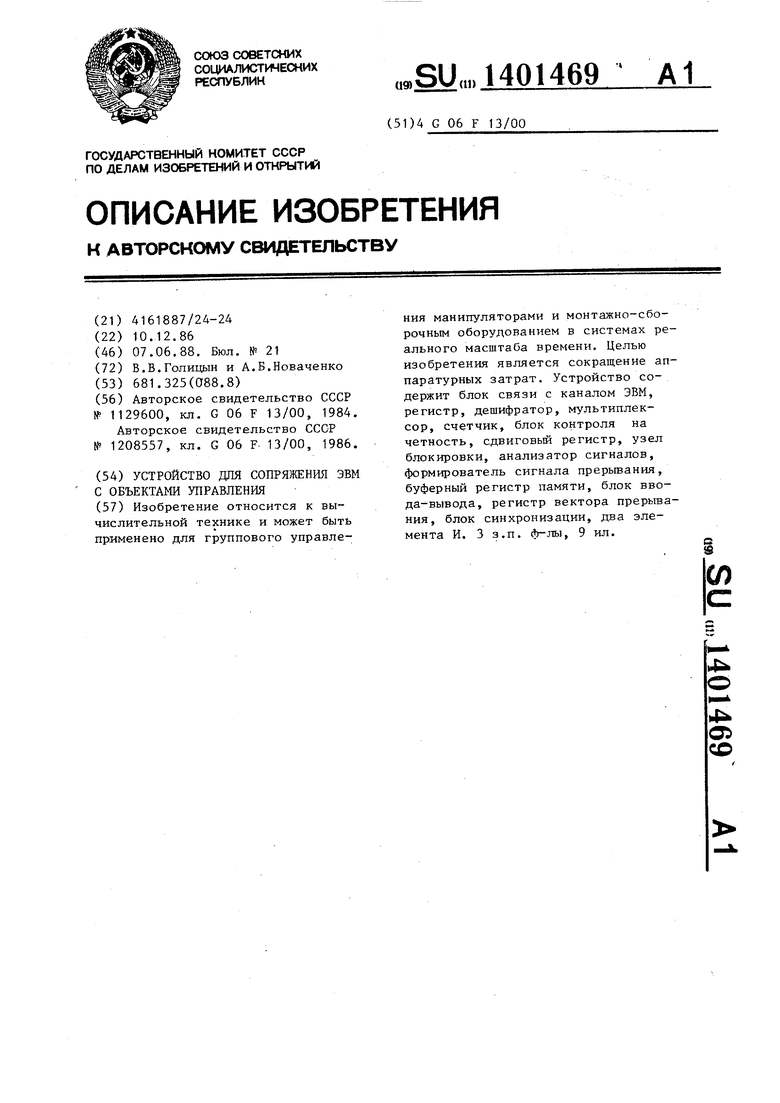

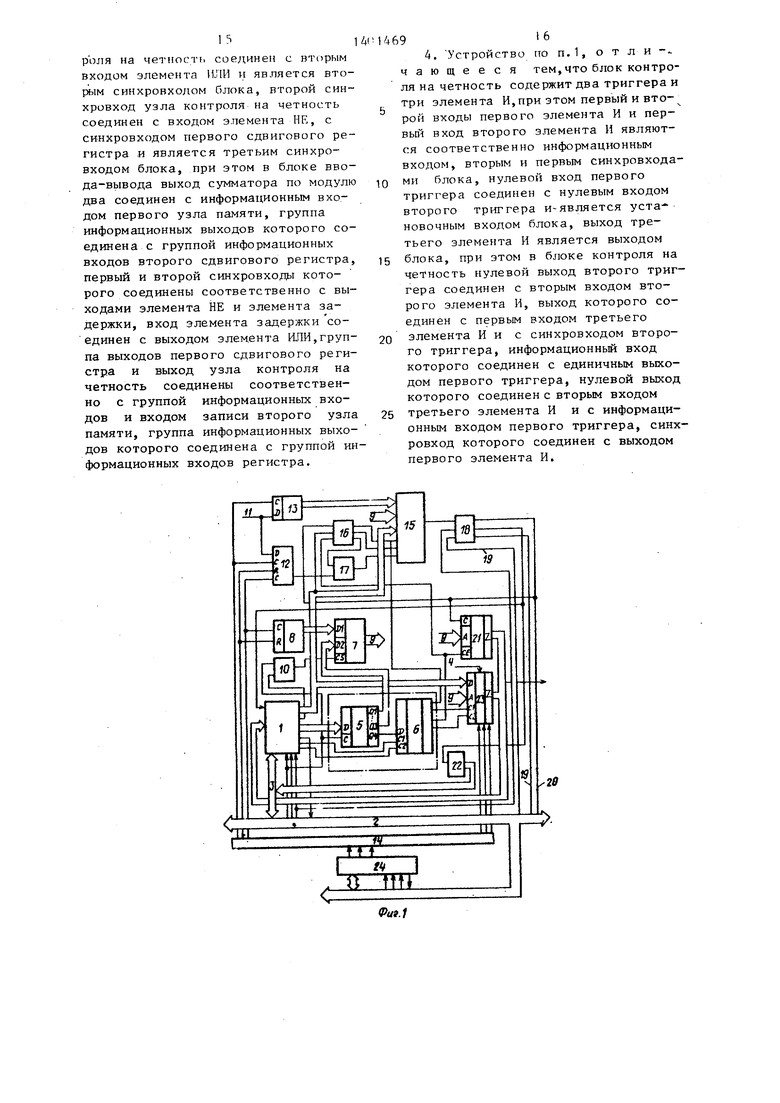

На фиг.1 представлена блок-схема устройства; на фиг.2 - схема анализатора сигналов; на фиг.З - блок связи с каналом ЭВМ; на фиг.4 - схема формирователя сигнала прерывания на фиг.З - схема узла блокировки; на фиг.6 - схема блока контроля на четность; на фиг.7 - схема регистра вектора прерывания; на фиг.8 - блок ввода-вывода; на фиг.9 - блок синхронизации.

Устройство для сопряжения ЭВМ с объектами управления (фиг.1) содержит первый блок 1 связи с каналом ЭВМ, канал 2 ЭВМ, группу 3 информационных входов-выходов блока 1, ин- формационный вход 4 устройства, регистр 5, дешифратор 6, мультиплек-° сор 7, счетчик 8,группу 9 информационных выходов мультиплексора 7, элемент И 10, информационньй вход 11 устройства, блок 12 контроля на четность, сдвиговый регистр 13, шину 14 синхронизации, анализатор 15 сигналов, узел 16 блокировки,элемент И 17, формирователь 18 сигнала прерывания, цепь 19 предоставления прерывания, цепь 20 требования прерывания, буферный регистр 21,памяти регистр 22 вектора прерывания, блок 23 ввода-вывода, блок 24 синхронизации.

Анализатор 15 сигналов (фиг.2) содержит мультиплексор 25, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 26, элемент И 27 и узел 28 памяти.

Блок 1 связи с каналом ЭВМ 2 (фиг.З) содержит шинный формировател 29, дешифратор 30, элемент И 31, триггер 32, элементы И 33 и 34 и элемент ИЛИ 35.

Формирователь 18 сигнала прерывания (фиг.4) содержит триггеры 36 и 37, элементы И 38 и 39.

Узел 16 блокировки (фиг.5) содержит элемент И 40, триггер 41 и од- новибратор 42.

Блок 12 контроля на четность (фиг.6) содержит элемент И 43, триг

Q 5 0

g

0

0

5

5

гер 44, триггер 45, элементы И 46 и 47.

Регистр 22 вектора прерывания (фиг.7) содержит наборное поле 48 перемычек и шинный формирователь 49.

Блок 23 ввода-вывода (фиг.8) содержит сдвиговый регистр 50, узел 51 контроля на четность, вход 52 приема дискретной информации, элемент НЕ 53, сдвиговый регистр 54, элемент ИЛИ 55, элемент 56 задержки, узлы 57 и 58 памяти, регистр 59,сумматор 60 по модулю два, линию 61 передачи дискретной информации к управляемому объекту.

Блок 24 синхронизации (фиг.9) содержит узел 62.связи с каналом 2 ЭВМ, идентичный блоку 1, в группе информационных выходов используется только один из разрядов,например младший, подключенньй к D-входу триггера 63, а в группе информационных входов также используется тот же разряд, соединенный с выходом триггера 64, элемент И 65, элемент ИЛИ 66, элемент И 67, одновибратор 68, генератор 69 импульсов, счетчик 70, регистр 71 усилителей, предназначенный для передачи синхросигналов в управляемые объекты, счетчик 72, одновиб- раторы 73 и 74.

Устройство работает следующим образом.

При включении напряжения питания Б цепи общего сброса (не показана) канала 2 вырабатывается сигнал, которым устанавливаются в исходное (нулевое) состояние триггеры 36 и 37 в формирователе 18 сигнала преры- вания, триггеры 44 и 45 в блоках 12 и 51 контроля на четность,тригге-- ры 63 и 64 и счетчики 70 и 72 в блоке 24 синхронизации , а триггер 41 в узле 16 блокировки устанавливается в единичное состояние. В результате формирователь 18 сигнала прерывания устанавливается в пассивное состояние, сигнал требования прерывания на линии 20 не формируется,на первом входе элемента И 39 устанавливается сигнал Лог.1, и сигнал предоставления прерывания из канала 2 по линии 1 9 предоставления прерывания может передаваться для обслуживания других устройств, имеющих меньший приоритет относительно предлагаемого устройства.

31А

В пассивном состоянии находится также блок 24 синхронизации, так как сигнал Лог.О с выхода триггера 64 через элемент И 67 запрещает работу генератора 69.

Обмен информацией между устройством и ЭВМ осуществляется через блок 1. Машинный цикл обмена информацией разбит.на. две части: адресную и информационную. В адресной части машинного цикла информация из канала 2 ЭВМ пропускается шинным формирователем 29 от канала В к каналу С и устанавливается на входы регистра 5 и дешифратора 30. К входам дешифратора 30 подключены старшие разряды кода, определяющие адрес обращения к устройству. К входам регистра 5 подключены младшие разряды кода, определяющие подадрес обращения к регистрам устройства или ячейкам узлов 28, -57 и 58 памяти, причем старший из них (разряд Q4 регистра 5) определяет обращение через дешифратор 6 к одному из конкретных элементов. Число подадресов определяется количеством групп анализируемых сигналов. Адресная часть отделяется от информационной сигналом на первом синхровходе блока 1. Если ад- р ес обращения соответствует конфигурации дешифратора 30, то на выходе элемента И 31 устанавливается сигнал логической 1, и сигнал на первом синхровходе блока 1 фиксирует сигнал логической 1 на выходе триггера 32 и код подадреса на выходах регистра 5, а также, проходя через элемент И 10, переключает мультиплексор 7 на передачу кода подадреса с выхода регистра 5 на шину 9. При несоответствии кода обращения к устройству к щине 9 подключаются выходы счетчика 8.

В информационной части цикла Вывод данные из канала 2 проходят через щинньй формирователь 29 по группе информационных выходов блока 1 на информационные входы узлов 28 и 58 оперативной памяти. Сигнал на втором синхровходе блока 1,пройдя через элемент И 34, на второй син- хровход дешифратора 6 вызовет, в зависимости от уровня сигнала на D- входе дешифратора 6, появление сигнала на четвертом или на первом выходе дешифратора и тем самым произведет запись информации в выбран469

ную ячейку выбраююго узла оперативной памяти. Вместе с тем сигнал с выхода элемента Н 34 пройдет через элемент ИЛИ 35 в канал 2, информируя ЭВМ о приеме информации устройством.

В информационной части цикла - Ввод сигнал с третьего синхровхода

Q блока 1, пройдя через элемент И 33, произведет переключение шинного формирователя 29 на передачу информа- .ции из канала А в канал В и, пройдя на первый стробирзлощий вход дешифра5 тора 6, вызовет, в зависимости от урбвня сигнала на D-входе дешифратора 6, появление сигнала на третьем или втором выходе дешифратора 6, активизируя выходы регистра 21 или ре0 гистра 59 соответственно. При этом в канал 2 ЭВМ будет выставлена либо информация, содержащаяся в регистре 21, либо информация выбранной ячейки узла 57 памяти,Вместе с тем сигнал

5 с выхода элемента И 33 пройдет через элемент ИЛИ 35 в канал 2, информируя ЭВМ о выдаче информации из устройства .

Для окончания подготовки устрой0 ства к работе после вк.пючения питания ЭВМ последовательно производит запись кода нуля во все ячейки узлов 28 и 58 оперативной памяти для исключения пересылки ложных команд в управляемый объект через регистр 54 и ложных прерываншЧ из анализатора 15 при включении блока 24 синхронизации.

Ввслючение блока 24 синхронизации

Q осуществляется записью логической 1 в триггер 63 (обрап;ение ЭВМ к блоку 24 синхронизации через узел 62, идентично описанное для блока 1) .

Сигнал логической 1 с выхода триггера 63, поступая на D-вход триггера 64 и, пройдя через элемент ИЛИ 66 на его синхровход, переводит его в единичное состояние. Поскольку на первом входе элемента И 67 ус0U tr 4 ti

тановлен сигнал логической 1 с

выхода одновибратора 74, сигнал Лог.1 с выхода триггера 64 передается через элемент И 67 и возбуждает одновибратор 68, который формирует сигнал на второй линии синхросигнала шины 14 синхронизации. Сигнал Лог.Г с выхода элемента И 67 включает также генератор 69, в результа5

5

5

514

те чего на выходах регистра усилителей 71 на третьей линии синхросигнала шины 1Д синхронизации формируются сигналы, управляющие сдвигом информации в сдвиговых регистрах 13, 50 и 54 и во взаимосвязанных регистрах объекта управления (не показаны).

Счетчики 70 и 72 осуществляют деление частоты импульсов генератора 69 с коэффициентом деления, задающим количество разрядов в передаваемом сообщении. Сообщения, которыми обменивается устройство с управляемым объектом, состоят из групп, количе- ство которых задается коэффициентом деления счетчика 72,а число разрядов в группе - коэффициентом деления счетчика 70. Количество разрядов в группе передаваемого (принимаемого), со- общения соответствует числу разрядов в группе анализируемых сигналов.

По окончании пересылки ка;ждой группы сигналов с выхода счетчика 70 возбуждается одновибратор 73 и посылает импульсный сигнал в линию пер-, вого синхросигнала шины 14 с.инхрони- зации. По окончании пересылки сообщения- возбуждается одновибратор 74 и через элемент И 67 блокирует генератор 69, формируя паузу между пересылками сообщений. По концу импульса одновибратора 74 через элемент И 67 снимается блокировка генератора 69, и вновь возбужд.ается одновибра- тор 68.

Выключение блока 24 синхронизации осуществляется записью логического О и в триггер 63. При этом, если блок 24 синхронизации находится в состоянии Пауза, то на первом входе элемента И 65 установлен уровень логической 1, и сигнал с инверсного выхода триггера 63 через элементы И 65 и ИЛИ 66 проходит на синхровход триггера 64, переключает его в пассивное состояние, и через элемент И 67 подтверждается сигнал блокировки генератора 69. Если в момент запи си логического О в триггер 63 блок 24 синхронизации находится в состоянии пересылки сообщения, на D- входе триггера 64 устанавливается уровень логического О, на втором вх оде элемента И 65 уровень логической 1 и по окончании пересылки сообщения сигнал с выхода одновибратора 74 проходит через элементы И 65

Q g о

5

0

5

0 5 0 5

696

и НИИ 66, переводя триггер 64 в пассивное состояние.

Таким образам, обеспечивается корректное завершение передачи сообще- Н1-Ш в управляемые объекты. Состояние блока синхронизации ЭВМ оценивает в цикле Ввод через узел 62, читая сигнал с выхода триггера 64.

Отсутствие сбоев в принимаемой с входов 11 и 52 информации проверяется блоками 12 и 51 контроля на четность следующим образом. Каждый бит последовательного кода, поступающий на первый вход элемента И 43, стро- бируется импульсами третьей линии синхросигнала шины 14 синхронизации, в результате чего на стробирующий вход триггера 44, включенного по схеме однотактного делителя на два,проходят только стробы информационных битов с уровнями логической 1.

Окончание приема каждой группы сигналов сопровождается импульсом на первой линии синхросигнала щины 14 синхронизации, подключенной к первому входу элемента И 47. Если к моменту прихода этого импульса на триггер 44 проходит четное количество стробов, триггер 44 находится в исходном состоянии, разрешая прохождение импульса с выхода элемента И 47 через элемент И 46 на выход блока 12. Этот же импульс с выхода элемента И 47, поступая на синхровход триггера 45, подтверждает его исходное состояние. Если к моменту прихода импульса по первой лини и синхросигнала шины 14 синхронизации на триггер 44 проходит нечетное количество стробов,то на D-BXO- де триггера 45 устанавливается сигнал .1, а на первом входе элемента И 46 сигнал лог.О. Импульс с выхода элемента И 47 переключит триггер 45 в единичное состояние, после чего прохождение очередных импульсов через элемент И 47, а следовательно, и через элемент И 46, блокируется. Возврат блока в исходное состояние происходит перед началом очередной посылки импульсов с второй линии синхросигнала шины 14 синхронизации, поступающих на входы сброса триггеров 44 и 45.

Пересылка информации блоков 23 ввода-вывода осуществляется следующим образом. Перед началом каждой пересылки передним фронтом сигнала во второй линии шины 14 синхронизации

устапав.11ивае-1ч;я в нулевое состояние счетчик 8, в результате чего на выходах 9 устанавливается код нулевого адреса, подготавливающий работу с нулевыми ячейками узлов 57 и 58 па- мяти. Задним фронтом этого импульса через элемент ИЛН 55 и элемент 56 задержки осуществляется запись содержимого нулевой ячейки 58 памяти в регистр 54.

Пересылка осуществляется импульсами, поступающими по третьей линии синхросигнала шины 14 синхронизации,

формируемым в с т-1мат(.1ре 60 по моду. по два. Затем ЭВМ ос тдествляет ввод информации из ячеек узла 57 памяти (процесс ввода описан в описании функционирования блока 1). При каждом вводе синхросигнал с второго выхода дешифратора 6 переводит выходы регистра 59 из высокоимпедансно- го состояния в активное.

Через регистр 50 в устройство поступает информация о параметрах управляемого объекта и изменениях состояния, не требующих немедленного

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения датчиков с ЭВМ | 1983 |

|

SU1129600A1 |

| Устройство для сопряжения датчиков с электронной вычислительной машиной | 1984 |

|

SU1208557A2 |

| Устройство для сопряжения датчиков с ЭВМ | 1985 |

|

SU1282108A1 |

| Устройство для управления обменом данными между ЭВМ и абонентами по общей шине | 1988 |

|

SU1543412A1 |

| СИГНАТУРНЫЙ АНАЛИЗАТОР | 1991 |

|

RU2017209C1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для сопряжения электронных вычислительных машин | 1984 |

|

SU1257653A2 |

| Устройство для обмена информацией | 1985 |

|

SU1334151A1 |

| УСТРОЙСТВО БУФЕРИЗАЦИИ И СИНХРОНИЗАЦИИ ДЛЯ ОБРАБОТКИ НЕПРЕРЫВНОГО СИГНАЛА | 1990 |

|

SU1812885A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

Изобретение относится к вычислительной технике и может быть применено для группового управления манипуляторами и монтажно-сбо- рочным оборудованием в системах реального масштаба времени. Целью изобретения является сокращение аппаратурных затрат. Устройство содержит блок связи с каналом ЭВМ, регистр, дешифратор, мультиплексор, счетчик, блок контроля на четность, сдвиговый регистр, узел блокировки, анализатор сигналов, формирователь сигнала прерьюания, буферный регистр памяти, блок ввода-вывода, регистр вектора прерывания, блок синхронизации, два элемента И. 3 з.п. ф-лы, 9 ил.

при этом передним фронтом каждого им- ig отклика, и обрабатываемая ЭВМ по

пульса осуществляется сдвиг информации в приемном регистре 50, а задним фронтом через элемент НЕ 53 - сдвиг в передающем регистре 54. Таким образом, при аналогичной организации регистров приема и передачи в управляемом объекте обеспечивается корректная пересылка информации (сначала принимается ранее подготовленный бит, а затем на передатчике выставляется новый бит-информации. Завершение пересылки каждой группы, как указаной при описании функционирования блока 24 синхронизации, сопровождается одиночным импульсом на первой линии синхросигнала щины 14 синхронизации.

Передним фронтом этого импульса ос-уществляется перепись информаци из регистра 50 в ячейку узла 57 памяти, адрес которой определяется состоянием счетчика 8. Задним фрон- том осуществляется увеличение содержимого счетчика 8 на единицу, подготавливая узлы 57 и 58 памяти для работы с очередными группами пересылаемых сигналов. Задний фронт этого сигнала, проходя через первый вхо элемента ИЛИ 55 и элемент 56 задержки, производит запись очередной группы в регистр 54.

Для анализа информации о состоянии управляемого объекта, зафиксированного в узле 57 памяти, и модификации (или подтверждения) управляющей информации в узле 58 памяти ЭВМ периодически выключает блок 24 синхронизации и после получения информации о переходе блока 24 в состояние паузы производит засылку инфор мации в ячейки узла 58 памяти (процесс записи описан при описании функционирования блока 1) . Код каждой группы дополняется битом четности.

0

5

0

5

0

5

0

5

принципу периодического опроса. Изменения в состоянии управляемого объекта, требующие немедленной реакции, реализующей функционирование в реальном масштабе времени, поступают через регистр 13 и обрабатываются анализатором 15 сигналов с выработкой сигналов требования прерывания через формирователь 18 сигналов прерывания.

Когда в процессе работы возникает необходимость контролировать состояние определенного разряда в принимаемом сообщении, ЭВМ записывает в узел 28 оперативной памяти по адресу, соответствующему номеру группы, содержащей контролируемый разряд, код настройки анализатора 15 сигналов. Код настройки содержит код номера контролируемого разряда в группе (разряды Q1-Q3 узла 28 памяти),выделенный бит для настройки на ожидаемый уровень сигнала (разряд Q4) и выделенный бит с уровнем логической 1 (разряд Q6) для разрешения прохождения сигналов через элемент И 27.

Если в процессе управления потребуется, не дожидаясь поступления сигнала от выбранного разряда, отключить контроль его состояния, ЭВМ записывает в узел 28 оперативной памяти по тому же адресу код нуля, переводя в пассивное состояние контроль соответствующей группы сигналов .

Аналогично независимо друг от друга может быть активизирован или переведен в пассивное состояние контроль остальных групп сигналов, принимаемых регистром 13 в предлагаемом устройстве или в таких же устройствах,подключенных к каналу 2 и шине 14 синхронизации и отличающихся друг от друга конфигурацией перемычек в дешифраторе 30 и в наборном поле 48.

В процессе приема регистром 13 группы сигналов код номера этой группы устанавливается на выходе счетчика 8 и, проходя через мультиплек- сор 7 на адресные входы узла 28 оперативной памяти, выставляет на его выходах код контроля принимаемой группы сигналов, В момент окончания пересылки группы сигнал контролируемого разряда с выхода регистра 13 передается на выход мультиплексора 25. Если в процессе пересылки группы блоком 12 не фиксируется сбой по четности, импульс с первой линии синхросигнала шины 14 синхронизации проходит через элемент И 46 на выход блока 12 и через элемент И 17 поступает на третий вход элемента И 27. Если при этом уровень контролируемого разряда на выходе мультиплексора 25 не совпадает с ожидаемым уровнем,на выходе Q4 узла 28 памяти, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26 устанавливается уровень логического О, и импульс через элемент И 27 на выход анализатора сигналов 15 не проходит.

Задним фронтом импульса с первой линии синхросигнала шины 14 синхронизации содержимое счетчика 8 увеличивается на единицу, и устройство бу- первом входе элемента И 39. Поступдет готово к приему и анализу очередной группы сигналов.

Если в момент контроля очередной группы сигналов уровень контролируемого разряда на выходе мультиплексора 25 совпадает с ожидаемым уровнем на выходе Q4 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26, импульс с выхода элемента И 17 проходит через элемент И 27 на выход анализатора 15 сигналов и переключает в единичное состояние триггер 36 в формирователе 18 сигнала прерываний.

Сигнал с выхода триггера 36 подготавливает к переключению триггер 37 и выставляет по линии 20 в канал 2 сигнал требования прерывания. Одновременно этот сигнал поступает на синхровход буферного регистра 21 и фиксирует в нем код номера группы, вызвавшей прерывание. Этот же сигнал, поступая в узел 16 блокировки, установит уровень логического О на выходе элемента И 40 и переклю40

ление сигнала предоставления прерыва ния вызывает появление сигнала на выходе элемента И 38. Этим сигналом устанавливается в нулевое состояние триггер 36, в результате чего подготавливается к установке в нулевое состояние триггер 37 и снимается сиг нал с линии 20 требования прерывания Кроме того, сигнал с выхода элемен- g та И 38 переводит выходы шинного фор мирователя 49 из состояния высокого импеданса в активное, а также, пройдя через элемент ИЛИ 35, поступает в канал 2, информируя ЭВМ о выдаче кода из устройства в канал В. В результате этого в канал поступит код- вектора прерывания, установленный перемычками наборного поля 48, и используется ЭВМ для программной реализации обслуживания прерывания.

После этого с линии 19 предоставления црерязшания снимается сигнал, что приводит к снятию сигнала с выхода элемента И 38 и переводу выходо

50

55

чит в нулевое состояние триггер 41, в результате чег о на выходе одновиб- ратора 42 сформируется импульс,.который перепишет О с выхода элемента И 40 в шестой разряд узла памяти 28 по адресу,соответствующему номеру группы, вызвавшей прерывание, переводя контроль этой группы в пассивное состояние. Кроме того, сигнал с выхода триггера 41 запретит прохождение импульсов с выхода: блока контроля на четность 12 через элемент Н 17, обеспечивая тем самым

корректное завершение ,. обработки прерывания ЭВМ.

Переключение триггера 37 происходит при поступлении на синхровход формирователя 18 сигнала прерывания

по линии третьего синхровхода блока 1 очередного синхронизирующего импульса канала 2, после чего формирователь 18 сигнала прерывания переходит в состояние ожидания сигнала предоставления прерывания по линии 19, которым должна ответить ЭВМ в ответ на сигнал в линии 20 требования прерывания. Если прохождение сигнала по линии 19 не заблокировано устройствами, имеющими более высокий приоритет, то дальнейшее прохождение сигнала по линии 19 предоставления прерывания через элемент И 39 блокируется сигналом Лог.О на

0

ление сигнала предоставления прерывания вызывает появление сигнала на выходе элемента И 38. Этим сигналом устанавливается в нулевое состояние триггер 36, в результате чего подготавливается к установке в нулевое состояние триггер 37 и снимается сигнал с линии 20 требования прерывания. Кроме того, сигнал с выхода элемен- g та И 38 переводит выходы шинного формирователя 49 из состояния высокого импеданса в активное, а также, пройдя через элемент ИЛИ 35, поступает в канал 2, информируя ЭВМ о выдаче кода из устройства в канал В. В результате этого в канал поступит код- вектора прерывания, установленный перемычками наборного поля 48, и используется ЭВМ для программной реализации обслуживания прерывания.

После этого с линии 19 предоставления црерязшания снимается сигнал, что приводит к снятию сигнала с выхода элемента И 38 и переводу выходов

0

5

n1

ш иниого формироват ля 49 в состояние высокого импеданса. При поступлении по линии третьего синхровхода блока 1 очередного синхронизирующего импульса происходит установка триггера 37 в нулевое состояние,и формирователь 18 сигнала прерывания возвращается в исходное состояние.

Для выхода в нужную подпрограмму ЭВМ осуществляет дополнительное обращение к регистру 21. Сигнал, формирующийся на третьем выходе дешифратора 6, активизирует выходы регистра 21 , а также устанавливает в единичное состояние триггер 41 в узле 16 блокировки. На первом входе элемента И 17 устанавливается сигнал, разрешающий прохождение через элемент И 17 сигналов с выхода блока 12 контроля на четность на вход разрешения анализатора 15 сигналов .

Формула изобретения

146912,

рываиия формирователя сиг-на.иа прерывания является выходом устройства для подключения к входу предоставления прерывания ЭВМ, разрешающий вход формирователя сиг нала прерывания является входом устройства для подключения к выходу предоставления прерывания ЭВМ, информационный вход

1Q сдвигового регистра соединен с информационным входом блока контроля на четность и является входом устройства для подключения к первому информационному выходу объекта уп-.

15 равления, при этом информационный вход дешиЬратора соединен с информационным выходом регистра, группа информационных входов которого соединена с первой группой информационных выходов блока связи с каналом ЭВМ, вторая группа информационных выходов которого соед1шена с первой группой информационных входов анализатора сигнала, вторая группа ин25 формационных входов которого соединена с группой информационных выходов сдвигового регистра, выход анализатора сигналов соединен с входом запуска формирователя сигналов прео„ рывания,о тличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит узел блокировки, мультиплексор, блок ввода- вывода, регистр вектора прерывания, счетчик, блок синхронизации, два элемента И, причем информационные вход и выход блока ввода-вывода является соответственно входом и выходом устройства для подключения

Q к второму информационному выходу и к информационному входу объектов управления, при этом группа информационных выходов регистра вектора прерывания и группа входов режима и выходов состояния блока синхронизации соединены с группой информационных входов-выходов блока связи с каналом ЭВМ, первый, второй, третий синхровход и тактовый выход блока синхронизации являются соответственно входами и выходами устройства для подключения к первому, второму, третьему синхровыходам и первому синхровходу ЭВМ, второй.и третий синхровыходы блока связи с каналом ЭВМ соединены соответственно с первым и вторым стробирующими входами дешифратора, первый и второй выходы котооого соединены сорт35

45

0

5

ветственно со входами записи и чтения блока ввода-вывода, группа информационных выходов которого соединена с г руппой информационных выходов буферного регистра памяти и с группой информационных входов блока связи с каналом ЭВМ, вход запуска которого соединен с входом чтения регистра вектора прерывания и с выходом запуска формирователя сигнала прерывания, выход требования прерывания которого соединен с входом разрешения узла блокировки и с входом записи буферного регистра памяти, вход чтения которого соединен с установочным входом узла блокировки и с третьим выходом дешифратора, четвертый выход которого соединен с тактовым выходом узла блокировки и с входом записи анализатора сигналов, информационный вход которого соединен с информационным выходом узла блокировки, информационный вход которого соединен со старшим разряом вто рой группы информационных выходов блока связи с каналом ЭВМ, четвертый синх ровыход которого соединен с первым входом первого элеента И, второй вход которого содинен с синхровходом регистра, группа информационных выходов которого соединена с первой группой инормационных входов мультиплексора, группа информационных выходов котоого соединена с группой информацинных входов буферного регистра паяти, с группой адресных входов анаизатора сигналов и с группой адресых входов блока ввода-вывода,группа информационных входов которого

соединена с второй группой информационных выходов блока связи с канаом ЭВМ, выход первого элемента И соединен с управляющим входом мультиплексора, вторая группа информационных: входов которого соединена с группой выходов счетчика, счеттп 1й , вход которого соединен с первыми синхровходами блока контроля на четность и блока ввода-выво да и с первым синхровыходом блока синхронизации, второй синхровьгход которого соединен с синхровходом блока ввода-вывода, с установочным входом счетчика и с установочным входом блока контроля на четность, второй син- хровход которого соединен с тактовым входом сдвигового регистра, с тре

5

0

5

0

5

0

5

0

5

тьим синхронходом б.иока ввода-вывода и с третьим синхровыходом блсжа синхронизации, разрешающий вход анализатора сигналов соединен с выходом второго элемента И, первьш и второй входы которого соединены соответственно с разрешающим выходом узла блокировки и с выходом блока контроля на четность.

I группой адресных входов второго узла памяти и образует группу адресных входов блока,вход записи первого узла памяти и синхровход регистра являются соответственно входами записи и чтения блока, информационный вход первого, сдвигового регистра соединен с информационным входом узла контроля на четность и является информационным входом узла, выход второго . сдвигового регистра и группа выходов регистра являются соответственно информационным выходом и группой информационных выходов блока, первый синхровход узла контроля на четность соединен с первым входом элемента ИЛИ и является первым синхровходом блока, установочный вход узла контр оля на четность соединен с вторым входом элемента ИЛИ и является вторым синхровходом блока, второй син- хровход узла контроля на четность соединен с входом элемента НЕ, с синхровходом первого сдвигового регистра и является третьим синхровходом блока, при этом в блоке ввода-вывода выход сумматора по модулю два соединен с информационным входом первого узла памяти, группа информационных выходов которого соединена с группой информационных входов второго сдвигового регистра, первый и второй синхровходы которого соединены соответственно с выходами элемента НЕ и элемента задержки, вход элемента задержки со- единен с выходом элемента ИЛИ,группа выходов первого сдвигового регистра и выход узла контроля на четность соединены соответственно с группой информационных входов и входом записи второго узла памяти, группа информационных выходов которого соединена с группой информационных входов регистра.

5

10

(446916

15

20

25

(pui.i

Шино О

4г7

фиг.

ери г. 5

цл/г.6

U/UW..O

фигЛ

-A -V

Ib

s

58

Шино„

It

23

67

59

и)и I. В

| Устройство для сопряжения датчиков с ЭВМ | 1983 |

|

SU1129600A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения датчиков с электронной вычислительной машиной | 1984 |

|

SU1208557A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-07—Публикация

1986-12-10—Подача