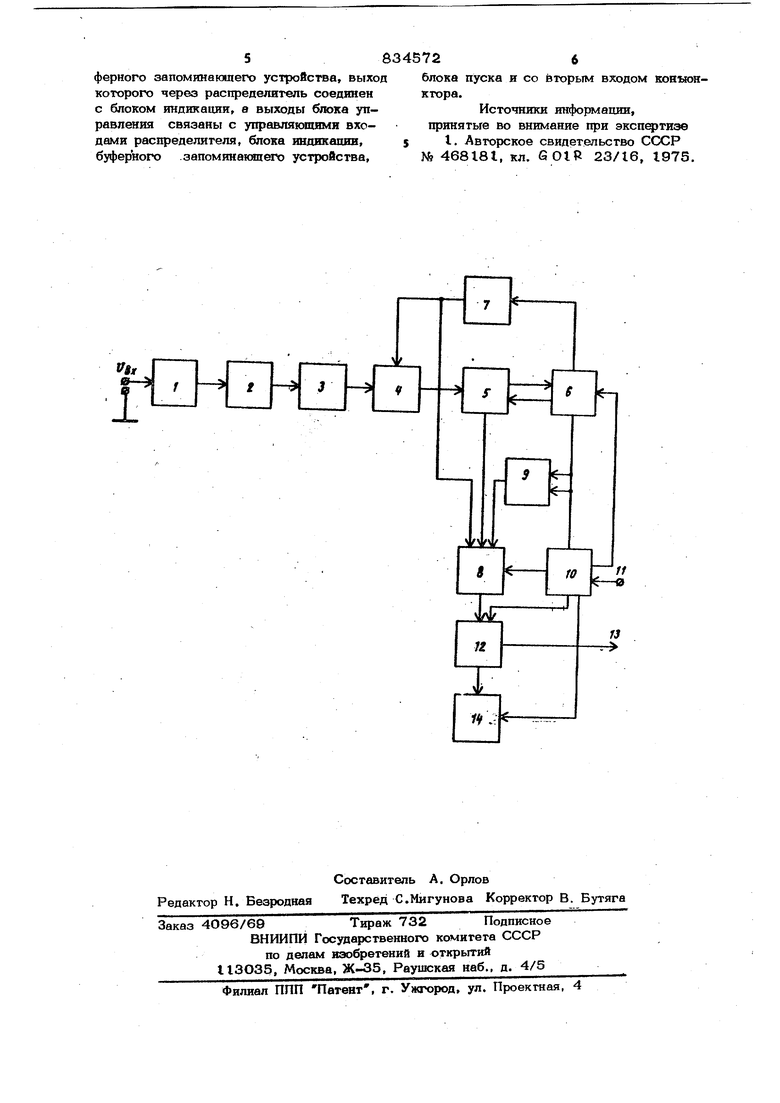

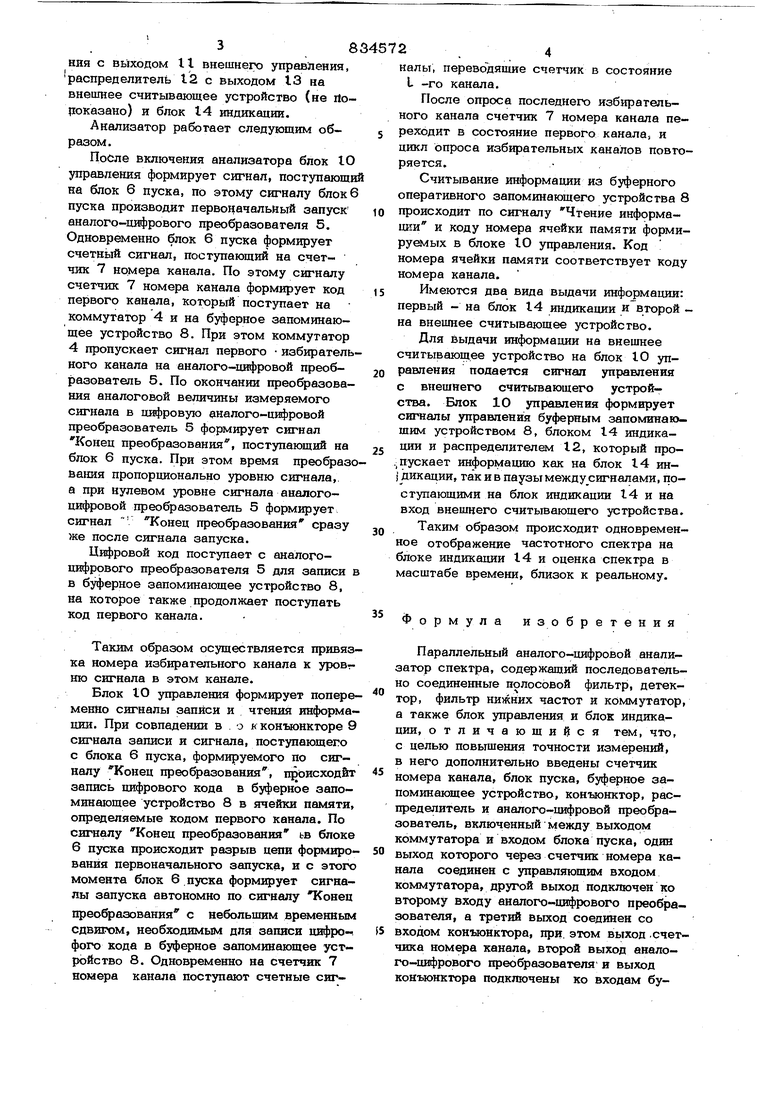

(54) ПАРАЛЛЕЛЬНЫЙ АНАГОЛО-ДИФРОВОЙ АНАЛИЗАТОР СПЕКТРА ния с выходом 11 внешнего управления, распределитель 12 с выходом 13 на внешнее считывающее устройство (не Поцоказано) и блок 14 индикации. Анализатор работает следующим образом. После включения анализатора блок Ю управления формирует сигнал, поступающи на блок 6 пуска, по этому сигналу блок 6 пуска производит первоначальный запуск аналого-цифрового преобразователя 5. Одновременно блок 6 пуска формирует счетный сигнал, поступающий на счетчик 7 номера канала. По этому сигналу счетчик 7 номера канала формирует код первого канала, который поступает на коммутатор 4 и на буферное запоминающее устройство 8. При этом коммутатор 4 пропускает сигнал первого избирательного канала на аналого-цифровой преобразователь 5. По окончании преобразования аналоговой величины измеряемого сигнала в цифровую аналого-цифровой преобразователь 5 формирует сигнал Конец преобразования, поступающий на блок 6 пуска. При этом время преобразо Ва1шя пропорционально уровню сигнала,, а при нулевом уровне сигнала аналогоцифровой преобразователь 5 формирует сигнал Конец преобразования сразу же после сигнала запуска. Цифровой код поступает с аналогоцифрового преобразователя 5 для записи в буферное запоминающее устройство 8, на которое также продолжает поступать код первого канала. Таким образом осуществляется привяз ка номера избирательного канала к уровню сигнала в этом канале. Блок to управления формирует попере менно сигналы записи и чтения информа ции. При совпадении в о кконъюнкторе 9 сигнала записи и сигнала, поступающего с блока 6 пуска, формируемого по сигналу Конец преобразования, происходит запись цифрового кода в буферное запоминающее устройство 8 в ячейки памяти определяемые кодом первого канала. По сигналу Конец преобразования ьв блоке б пуска происходит разрыв цепи формиро вания первоначального запуска, и с этог момента блок 6 пуска формирует сигналы запуска автономно по сигналу Конец преобразования с небольшим временным сдвизгом, необходимым для записи цифрофого кода в буферное запоминающее устройство 8. Одновременно на счетчик 7 номера канала поступают счетные сигналы, переводящие счетчик в состояние t -го канала. После опроса последнего избирательного канала счетчик 7 номера канала перехсдит в состояние первого канала, и цикл опроса избирательных канаЛов повторяется. Считывание информации из буферного оперативного запоминающего устройства 8 происходит по сигналу Чтение информащ и и коду номера ячейки памяти формируемых в блоке 10 управления. Код . номера ячейки памяти соответствует коду номера канала. Имеются два вида выдачи информации: первый - на блок 14 индикации и второй на внешнее считывающее устройство. Для выдачи информации на внешнее считывающее устройство на блок 10 управления подается сигнал управления с внешнего считывающего устройства. Блок 10 управления формирует сигналы управления буферным запоминающим устройством 8, блоком 14 индикации и распределителем 12, который про., пускает информацию как на блок 14 инi дикации, так и в паузы между сигналами, поступающими на блок индикации 14 и на вход внешнего считывающего устройства. Таким образом происходит одновремен- ное отображение частотного спектра на блоке индикации 14 и оценка спектра в масштабе времени, близок к реальному. Формула изобретения Параллельный аналого-цифровой анализатор спектра, содержащий последовательно соединенные полосовой фильтр, детектор, фильтр нижних частот и коммутатор, а также блок управления и блок индикации, отличающийся тем, что, с целью повышения точности измерений, в него дополнительно введены счетчик номера канала, блок пуска, буферное запоминающее устройство, конъюнктор, распределитель и аналого-цифровой преобразователь, включенный между выходом коммутатора и входом блока пуска, один выход которого через счетчик номера канала соединен с управляющим входом коммутатора, другой выход подключен ко второму входу аналого-цифрового преобразователя, а третий выход соединен со входом конъюнктора, при. этом выход .счетчика номера канала, второй выход аналого-цифрового преобразователя и выход конъюнктора подключены ко входам буферного запоминающегч) устройства, выхо которого через распределитель соединен с блоком индикации, а выходы блока управления связаны с управлякшшми входами распределителя, блока индикадин, буферного запоминакядего устройства. 72 блока пуска и со вторым входом кояконктора. Источники информации, принятые во внимание при экспе тпае 1. Авторское свидетельство СССР № 468181, кл. б OtP 23/16, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный анализатор спектра | 1981 |

|

SU1068835A1 |

| Устройство для автоматического регулирования температуры | 1988 |

|

SU1645945A1 |

| Устройство сбора данных для цифрового анализатора сигналов | 1990 |

|

SU1751683A1 |

| Анализатор спектра | 1985 |

|

SU1287033A1 |

| Анализатор гармоник электрической сети | 1985 |

|

SU1352393A1 |

| Устройство для контроля канала связи | 1987 |

|

SU1478351A1 |

| Аналого-цифровой анализатор спектра | 1973 |

|

SU486281A1 |

| Способ итерационной коррекции аналого-цифрового преобразования | 1989 |

|

SU1732468A1 |

| Устройство для преобразования перемещения в код | 1981 |

|

SU978174A1 |

| Многоканальная система для анализаэКСТРЕМуМОВ | 1977 |

|

SU842826A1 |

Vi

t

10 -о

гз

J2 -

Авторы

Даты

1981-05-30—Публикация

1978-03-20—Подача