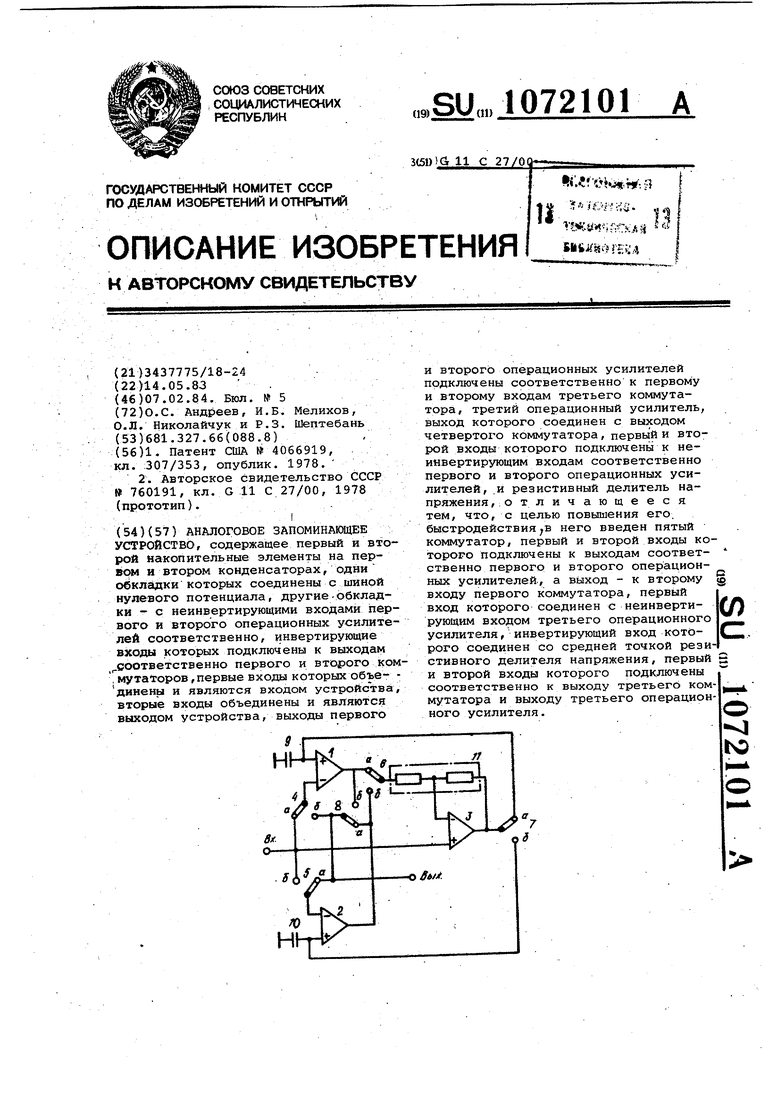

Изобретение относится к вычислительной технике и предназначено для использования в аналого-цифровых пр образователях. Известно аналоговое запоминающее устройство, содержащее два идентичных запоминающих элемента, подключаемых к входу и выходу устройства поочередно. Каждый из запоминающих элементов содержит первый усилитель выход которого соединен с одной обкладкой конденсатора, другая обклад ка которого соединена с входом втор го усилителя, выход которого через ключи связан с собственным входом и входом первого усилителя 1 . Недостатком известного устройств является низкие быстродействие и то ность, обусловленные тем, что при переключении каждого из запоминающих элементов в режим хранения, . напряжение -на его выходе изменяется от нулевого значения до значения запомненного напряжения. В режиме хранения цепью обратной связи охватываются два последовательно включенных усилителя запоминающего элемента. .Это приводит к значительному переходному процессу и затягиванию времени установления выходного напр жения, что снижает быстродействие устройства. Кроме того, наличие ключей, не охваченных цепью стабили зирующей обратной связи, между выходом устройства и выходами запоминающих элементов приводит к появлению дополнительной погрешности в вы ходном сигнале. Наиболее близким по технической сущности к предлагаемому является аналоговое запоминающее устройство, содержащее первый и второй накопительные элементы на первом и втором конденсаторах, одни обкладки которы соединены с шиной нулевого потенциала, другие обкладки - с неинвертирующими входами первого и второго операционных усилителей соответстве но , инвертирующие входы которых под ключены к выходам соответственно пер вого и второго коммутатора, первые входы которых объединены и являются входом устройства, вторые входы объе динены и являются выходом устройств выходы первого, и второго операционных усилителей подключены соответственно к первому и второму входу третьего коммутатора, выход которого со единен с входом инвертирующего усили теля на третьем операционном усилите ле , выход которого соединен с выходо четвертого коммутатора, первый и вто рой входы которого подключены к инвертирующим входам соответственно перво го и второго операционных усилителей выходы которых соединены соответстве но с первым и вторым входами резисти ного делителя напряжения, средняя точка которого подключена к вторым входам первого и второго коммутаторов. Напряжение смещения нуля используемых в устройстве операционных усилителей компенсируется и не влияет на точность устройства 2. Недостатком устройства является низкое быстродействие, вызванное тем, что при каждом переключении коммутаторов выходное напряжение первого и второго операционных усилителей изменяется от значения входного напряжения до нуля или наоборот. При этом на установление напряжения на выходе устройства с заданной точностью затрачивается значительное время. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее первый и второй накопительные элементы на первом и втором конденсаторах, одни обкладки которых соединены с шиной нулевого потенциала, другие обкладки - с неинвертирующими входами первого и второго операционных усилителей соответственно, инвертирующие входы которых подключены к выходам соответственно первого и второго коммутаторов , первые входы которых объединены- и являются входом устройства, вторые входы объединены и являются выходом устройства, выходы первого и второго операционных усилителей подключены соответст;венно к первому и второму входам третьего коммутатора, третий операционный усилитель, выход которого соединен с выходом четвертого коммутатора, первый и второй входы которого -подключены к неинвертирующим входам соответственно первого и второго операционных усилителей, и резистивный делитель напряжения, введен пятый коммутатор, первый и второй входы которого подключены к выходам соответственно первого и второго операционных усилителей, а выход к второму входу первого коммутатора, первый вход которого соединен с неинвертирующим входом третьего операционного усилителя, инвертирующий вход которого соединен со средней точкой резистивного делителя напряжения, первый и второй входы которого подключены соответственно к выходу третьего коммутатора и выходу третьего операционного усилителя. На чертеже представлена схема предлагаемого устройства. Устройство, содержит операционные усилители 1-3, коммутаторы 4-8, конденсаторы 9 и 10, и резистивный делитель 11 напряжения. Устройство работает следующим образом.

коммутаторы 4-8 одновременно переключаются из положения а в положение 5 и наоборот. При указанном на чертеже положении коммутаторов нй1ряжение на входе устройства будет записано на конденсатор 9. При этом на выходе первого операционного усилителя 1 установится напряжение, равное входному, поскольку только в этом случае разность напряжений, приложенных между инвертирующим и неинвертирующим входами в каждом из операционных усилителей 1 и 3,-близка к нулю. Напряжение на выходе устройства в это время равно напряжению, сохраняемому вторым конденсатором 10 и передаваемому на выход устройства вторым операционным усилителем 2, охваченным обратной связью через коммутаторы 5 и 8.

При переключении коммутаторов в положение б первый 1 и второй 2 операционные усилители по выполняемым функциям меняются местами. Напряжение на выходе устройства становится равным выходному напряжению первого операционного, усилителя 1, т.е. сохраняющему на первом конденсаторе 9 тому значению напряжения на входе устройства, которое оно имело в момент переключения ключей. Текущее значение входного напряжения отслеживается на вьоходах второго 2 и третьего 3 операционных усилителей и на втором конденсаторе 10.

Устройство характеризуется компенсацией напряжения смещения нуля

используемых операционных усилите- . лей. Однако при переключении,коммутаторов напряжение на выходе усилителя, подключенного к выходу устройства изменяется лишь на величину, обусловленную напряжением смещения нуля усилителя и падением напряжения на коммутаторе 8, через который протекает ток на выход устройства. Полученный перепад напряжения не превышает нескольких десятков милливольт,

0 и время, необходимое для установления выходного напряжения, не превышает де :ятков наносекунд. В известнвк устройствах выходное напряжение усилите5 лей изменяется на величину равную выходному напряжению - 5-10 В. При этом время установления напряжения на выходе устройства составляет несколько микросекунд.

Аналоговое запоминающее устройство,

0 выполненное на микросхемах К544УД1А и К590КН4 по предлагаемой схеме, позволяет АЦП с временем преобразования 5 МКС обрабатывать сигнал с амплитудой 5 В и частотой до 100 кГц.

5 При этом время установления выходного напряжения устройства составляет 100 НС, а период переключения ключей - 5 МКС. Устройство, построенное по схеме прототипа на анало0гичных Микросхемах, имеет время установления 3 МКС, что с учетом времени, необходимого для обработки сигнала, ограничивает частоту обрабатываемых сигналов на уровне 63 кГц. Полученный виигрыш по быстродействию приве5дет к значительному экономическому эффекту.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1986 |

|

SU1334181A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1019496A1 |

| Аналоговое запоминающее устройство | 1987 |

|

SU1494042A1 |

| Аналоговое запоминающее устройство | 1989 |

|

SU1695392A1 |

| Аналоговое запоминающее устройство | 1985 |

|

SU1320847A1 |

| Многоканальный коммутатор | 1980 |

|

SU907800A1 |

| Аналоговое запоминающее устройство | 1987 |

|

SU1529292A1 |

| Аналоговое запоминающее устройство | 1986 |

|

SU1348910A1 |

| Аналоговое запоминающее устройство | 1989 |

|

SU1674266A1 |

| Устройство для определения логарифма отношения двух напряжений | 1982 |

|

SU1103249A1 |

АНАЛОГОВОЕ ЗАПОМИНАЩЕЕ УСТРОЙСТВО, содержащее первый и второй накопительные элементы на первом и втором конденсаторах, одни обкладки которых соединены с шиной нулевого потенциала, другие-обкладки - с неинвертирующими входами первого и второго операционных усилителей соответственно, инвертирующие входы которых подключены к выходам соответственно первого и второго ком мутаторов,первые входы которых объе- динены и являются входом устройства, вторые входы объединены и являются выходом устройства, выходы первого н и второго операционных усилителей подключены соответственно к первому и второму входам третьего коммутатора, третий операционный усилитель, выход которого соединен с выходом четвертого коммутатора, первый и второй входы которого подключены к неинвертирующим входам соответственно первого и второго операционных усилителей, и резистивный делитель напряжения ,:Отличающееся тем, что, с целью повышения его. быстродействия в него введен пятый коммутатор, первый и второй входы которого подключены к выходам соответственно первого и второго операционных усилителей., а выход - к второму § входу первого коладутатора, первый (Л вход которого соединен с неинвертирующим входом третьего операционного усилителя, инвертирующий вход которого соединен со средней точкой резистивного делителя напряжения, первый S и второй входы которого подключены соответственно к выходу третьего коммутатора и выходу третьего операционного усилителя. - IND

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4066919, кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР 760191, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| , I | |||

Авторы

Даты

1984-02-07—Публикация

1983-05-14—Подача