входу которой подключен выход второго компаратора, а выход является вторым выходом для регулирования частоты и соединен с вторым входом логической схемы ИЛИ, выход которой подключен к первому входу второй двухвходовой логической схемы- И указанного логического блока, к второму входу которой подключен выход логической схемы ограничения максимальной скорости, а выход соединен с входом формирователя выходных импульсов.

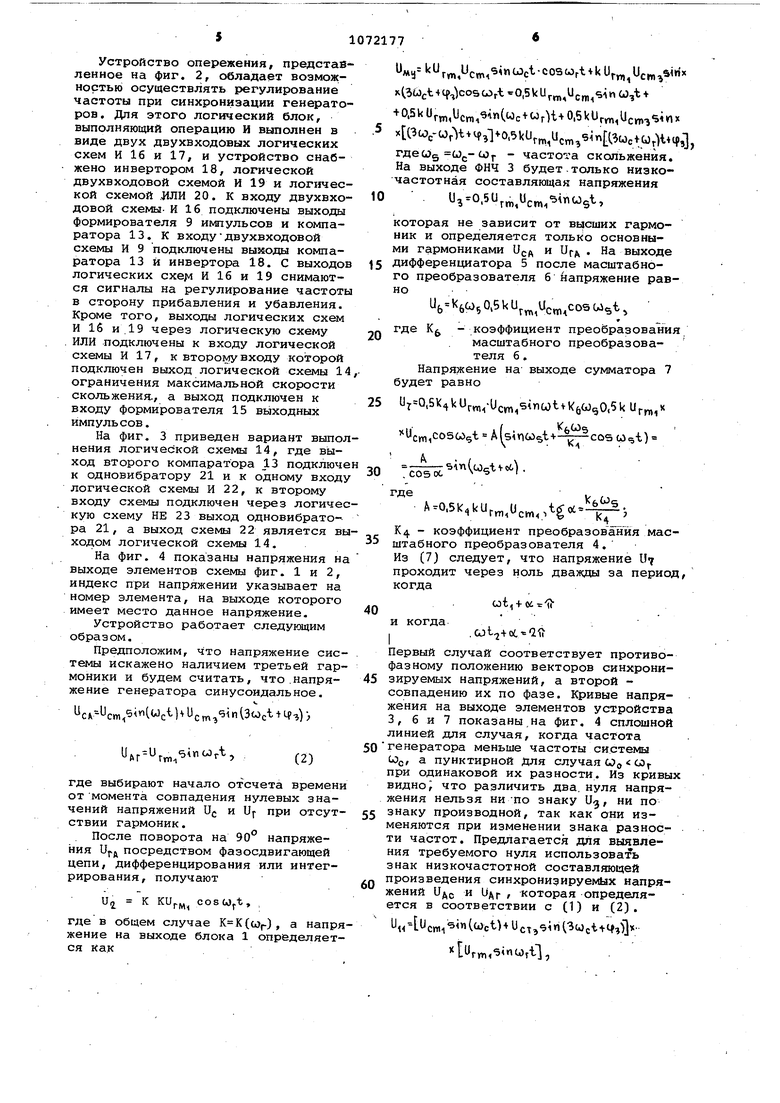

4. Устройство по п.1,3, о т ли чающееся тем, что логическая схема ограничения максимальной скорости скольжения состоит из логической схемы И, логической схемы НЕ и одновибратора, вход которого подключен к выходу второго компаратора, а выход через логическую схему НЕ подключен к одному входу логической схемы И, к второму входу которой подключен выход .второго компаратора, а выход является выходом логической схемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронизатор с постоянным временем опережения | 1990 |

|

SU1820442A1 |

| Автоматический синхронизатор с постоянным временем опережения | 1979 |

|

SU888269A2 |

| Устройство для отключения электрической цепи при нарушении синхронизма между двумя частями энергосистемы | 1981 |

|

SU983890A1 |

| Импульсный синхронизатор | 1990 |

|

SU1774433A2 |

| Автоматический синхронизатор спОСТОяННыМ углОМ ОпЕРЕжЕНия | 1979 |

|

SU838897A1 |

| Автоматический синхронизатор с постоянным временем опережения | 1981 |

|

SU995200A1 |

| Автоматический синхронизатор с постоянным углом опережения | 1982 |

|

SU1065957A2 |

| Устройство для автоматической синхронизации | 1978 |

|

SU746815A1 |

| Синхронизатор с постоянным временемОпЕРЕжЕНия | 1979 |

|

SU817861A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОЙ СИНХРОНИЗАЦИИ СИНХРОННЫХ ГЕНЕРАТОРОВ | 1991 |

|

RU2014707C1 |

1. УСТРОЙСТВО ОПЕРЕЖЕНИЯ СИНХРОНИЗАТОРА, содержащее фильтр низких частот, к выходу которого подключены последовательно соединенные масштабный преобразователь, сумматор и компаратор, а также вход дифференциатора, выход которого через другой масштабный преобразователь подключен к второму входу сумматора, логическую схему ограничения максимальной скорости скольжения и формирователь выходных импульсов, отличающееся тем, что, с целью повышения точности, оно снабжено блокс1ми умножения, вторым фильтром низких частот, формирователем импульсов, логическим блоком, выполняющим операцию И, и вторым компаратором, причем входы первого блока умножения подключены к зажимам для подключе(|ия на напряжение одного источника синхронизируемых напряжений и на напряжение второго источника синхронизируемых напряжений, сдвинутое относительно напряжения одноименного напряжения первого источника на 90., входы второго блока умножения подключены к зажимс1м для подключения на одноименные напряжения указанных источников синхронизируемых напряжений, выход первог.о блока умножения подключен к входу первого фильт-ia низких частот, выход первого компаратора через формирователь импульсов подключен к входу логического блока, вьшолн5пощего операцию И, к второму входу которого подключен выход второго компаратора, вход которого через второй фильтр низких частот подключен к выходу второго блока умножения, к третьему входу логического блока, выполняющего операцию,И, подключен выход логической схемы ограничения максимальной скорости скольжения, а выход логического блока, выполняющего операцию И, связан с формирователем выходных импульсов. 0) 2.Устройство по п.1, о т л и чающееся тём что формирователь импульсов выполнен юднополяр, ным. 3.Устройство по nil, отлич аюсцееся тем, что, с целью расширения функциональных возможностей путем ос5ацествления регулирования частоты при синхронизации генераторов, оно снабжено инвертором, логической схемы ИЛИ и двухвходовой логической схемой И, формирователь импульсов выполнен двухполярным, а логический блок, выполняющий операцию И, выполнен в виде двух двухвходовых логических схем И, причем выход формирователя импульсов подключен к первому входу первой логической схемы И указанного логического блока, к второму .входу которой псяключен выход йторого компаратора, а выход является первым выходом для регулирования частоты и соединен с первым входом логической схемы ИЛИ, выход формирователя импульсов через инвертор подключен к первому входу дополнительно введенной двухвходовой логической схемы И, к второму

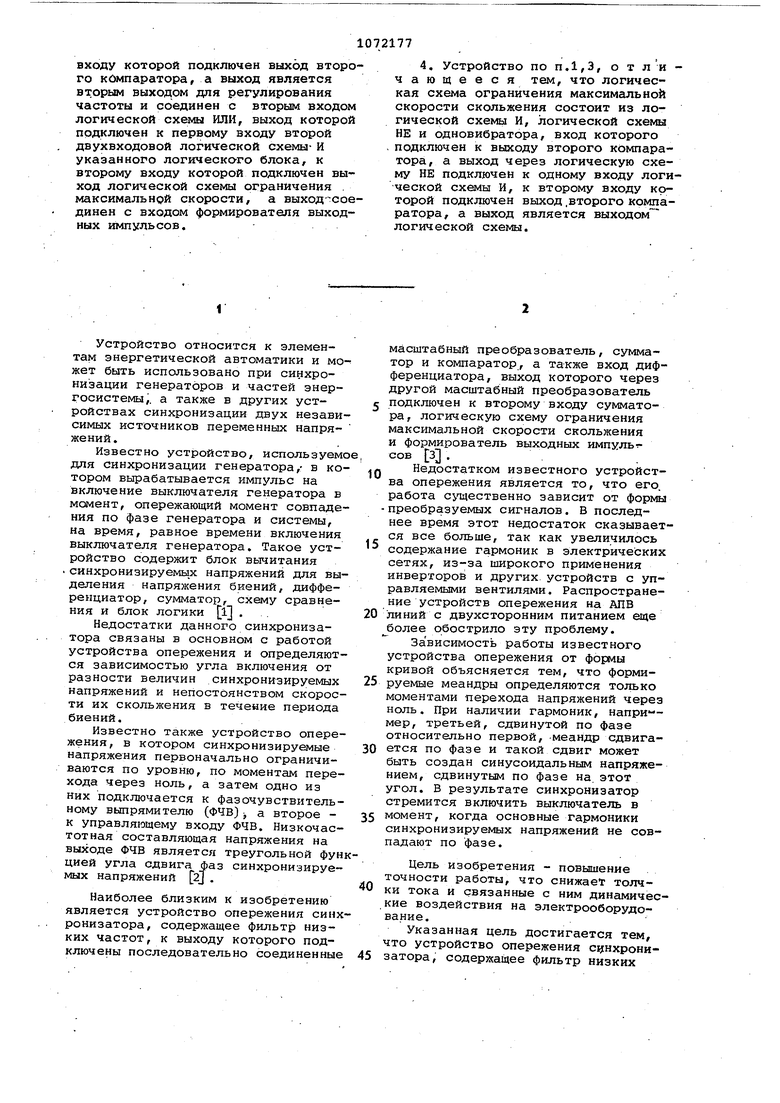

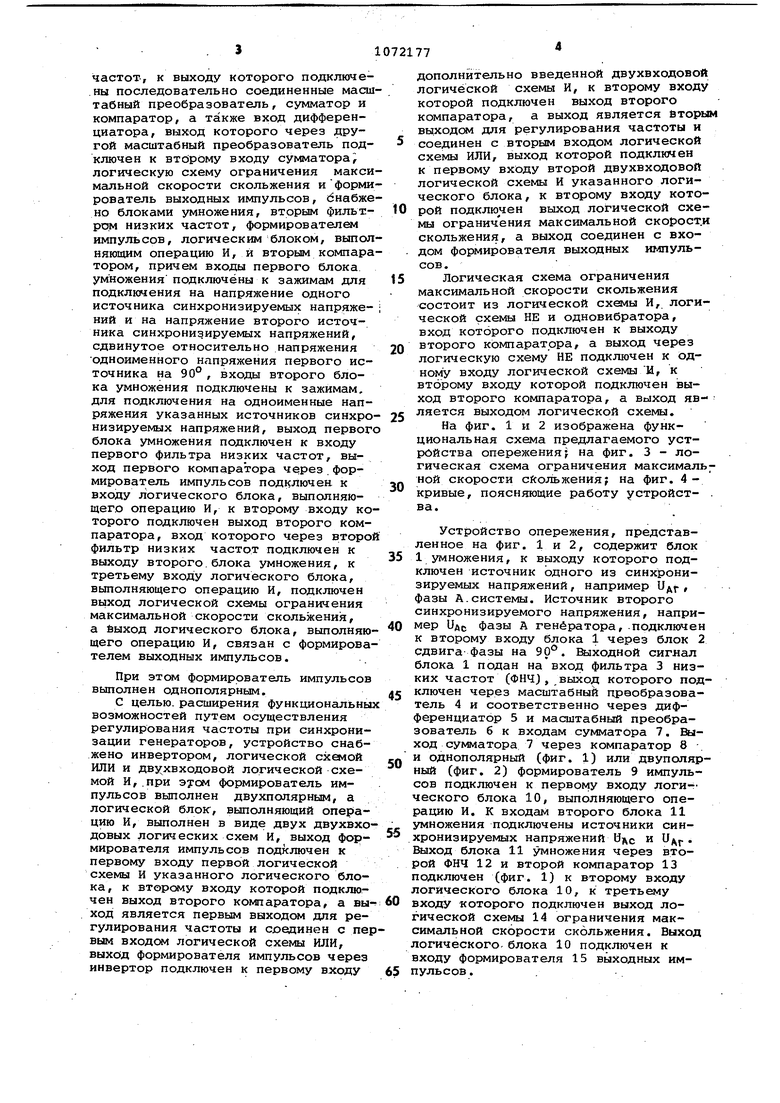

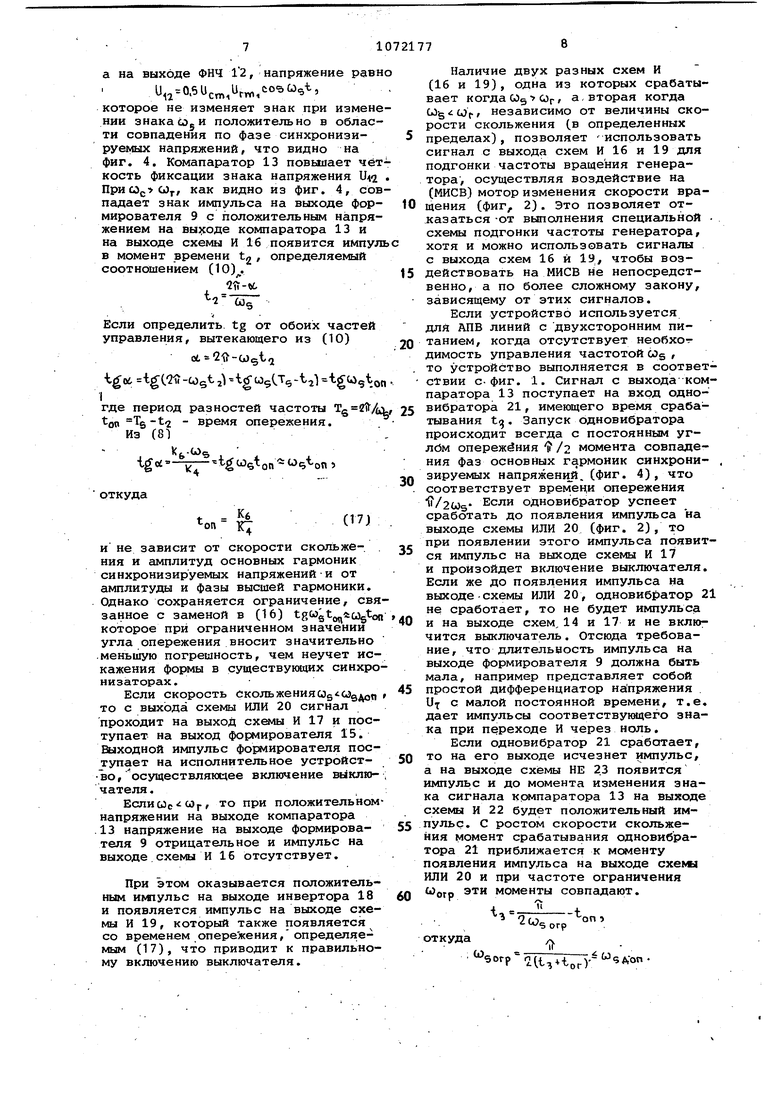

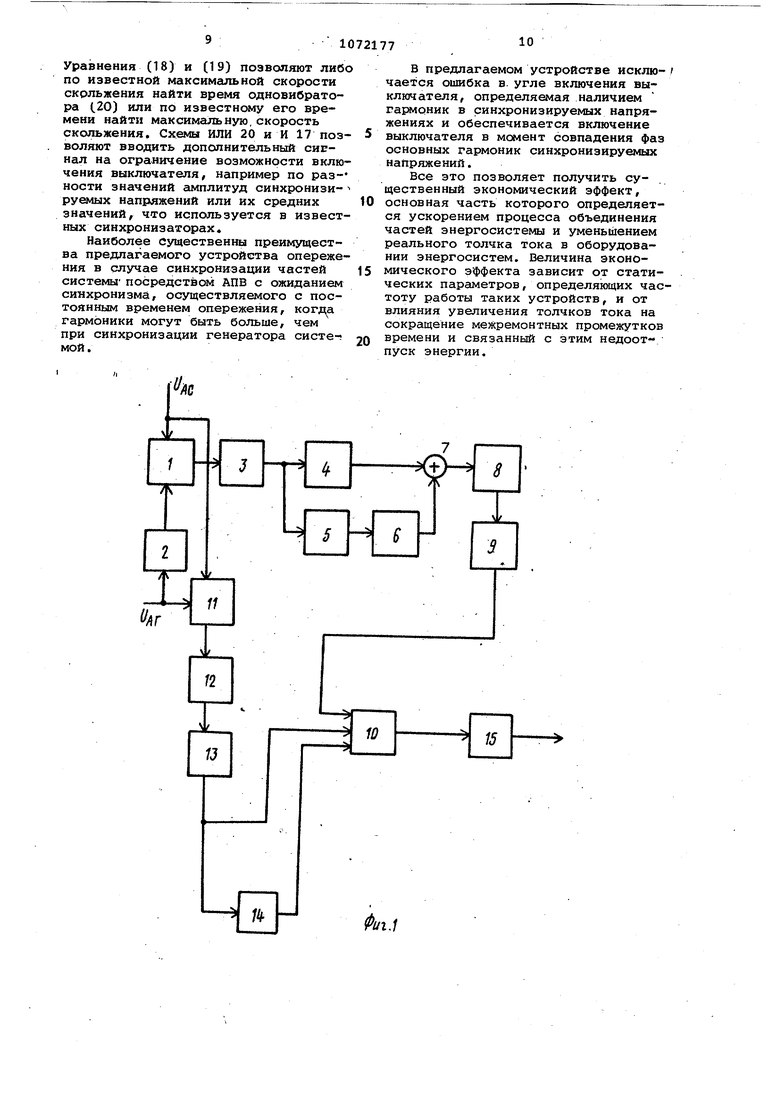

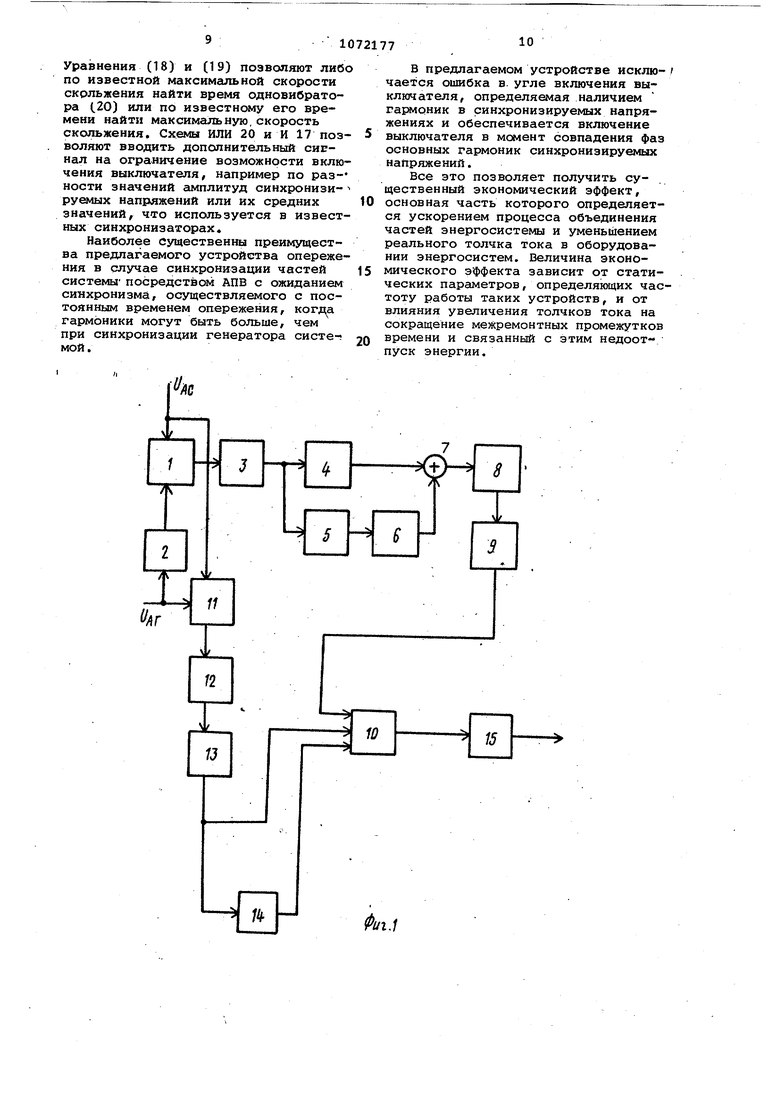

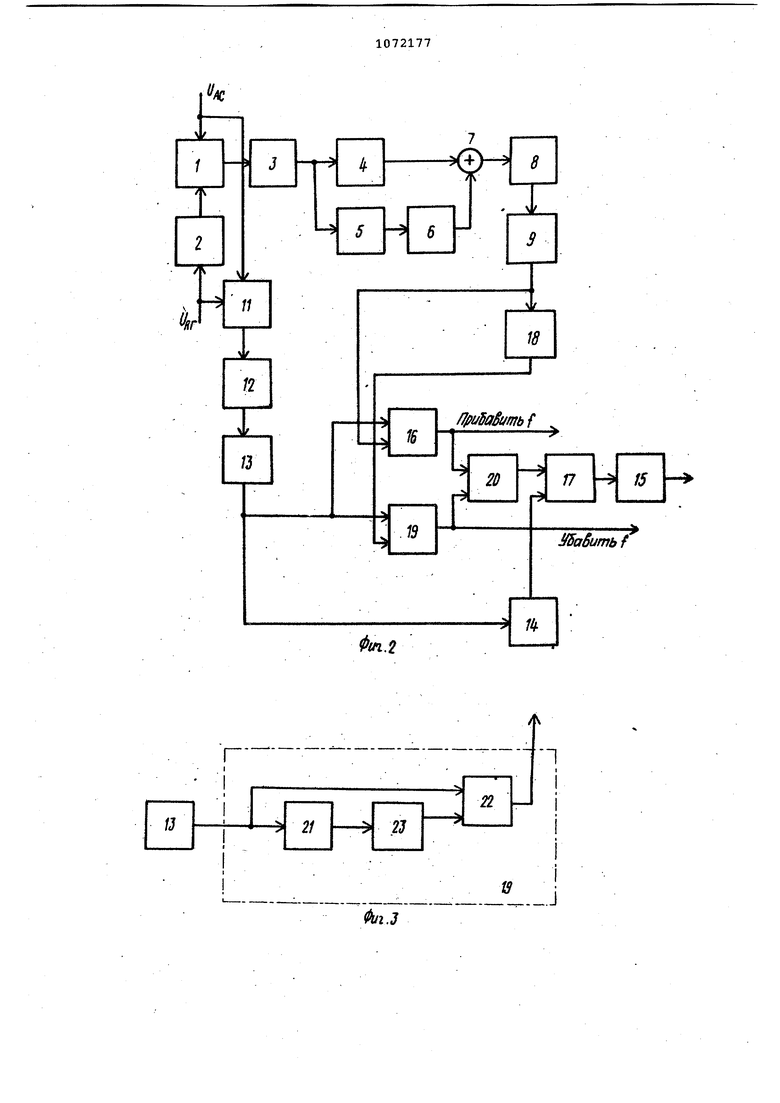

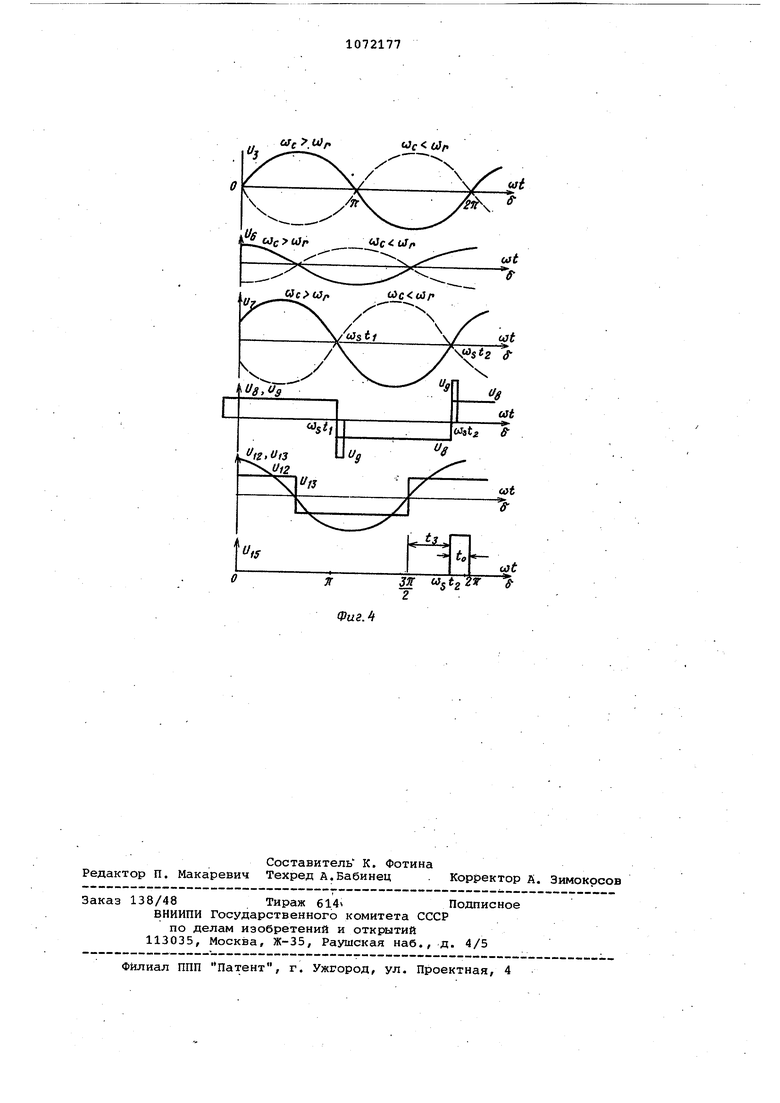

Устройство относится к элементам энергетической автоматики и мо жет быть использовано при синхронизации генераторов и частей энергосистемы,, а также в других устройствах синхронизации двух незави симых источников переменных напряжений. Известно устройство, используем для синхронизации генератора,- в ко тором вырабатывается импульс на включение выключателя генератора в момент, опережающий момент совпаде ния по фазе генератора и системы, на время, равное времени включения выключателя генератора. Такое устройство содержит блок вычитания . синхронизируемы х напряжений для вы деления напряжения биений, дифференциатор, сумматор, схему сравнения и блок логики l . . Недостатки данного синхронизатора связаны в основном с работой устройства опережения и определяют ся зависимостью угла включения от разности величин синхронизируемых напряжений и непостоянством скорости их скольжения в течение периода биений. Известно также устройство опере жения, в котором синхронизируемые напряжения первоначально ограничиваются по уровню, по моментам перехода через ноль, а затем одно из них подключается к фазочувствительному выпрямителю (ФЧВ) , а второе к управляющему входу ФЧВ. Низкочастотная составляющая напряжения на выходе ФЧВ является треугольной фун цией угла сдвига фаз синхронизируемых напряжений 2J . Наиболее близким к изобретению является устройство опережения синх ронизатора, содержащее фильтр низких частот, к выходу которого подключены последовательно соединенные масштабный преобразователь, сумматор и компаратор, а также вход дифференциатора, выход которого через другой масштабный преобразователь подключен к второму входу сумматора, логическую схему ограничения максимальной скорости скольжения и формирователь выходных импулысов З . Недостатком известного устройства опережения является то, что его. работа с тдественно зависит от формы преобразуемых сигналов. В последнее время этот недостаток сказывается все больше, так как увеличилось содержание гармоник в электрических сетях, из-за широкого применения инверторов и других устройств с управляемыми вентилями. Распространение устройств опережения на АПВ линий с двухсторонним питанием еще более обострило эту проблему. Зависимость работы известного устройства опережения от формы кривой объясняется тем, что формируемые меандры определяются только моментами перехода напряжений через ноль. При наличии гармоник, напри-мер, третьей, сдвинутой по фазе относительно первой, -меандр сдвигается по фазе и такой сдвиг может быть создан синусоидальным напряжением, сдвинутым по фазе на. этот угол. В результате синхронизатор стремится включить выключатель в момент, когда основные гармоники синхронизируемых напряжений не совпадают по фазе. Цель изобретения - повышение точности работы, что снижает толчки тока и связанные с ним динамические воздействия на электрооборудование. Указанная цель достигается тем, что устройство опережения сунхронизатора, содержащее фильтр низких частот, к выходу которого подключе.ны последовательно соединенные масш табный преобразователь, сумматор и компаратор, а также вход дифференциатора, выход которого через другой масштабный преобразователь подключей к второму входу сумматора логическую схему ограничения макси Мсшьной скорости скольжения и форми рователь выходных импульсов, бнабже но блоками умножения, вторым фильтром низких частот, формирователем импульсов, логическим блоком, выпол няющим операцию И, и вторым компара тором, причем входы первого блока умноженияподключены к зажимам для подключения на напряжение одного источника синхронизируемых напряжеНИИ и на напряжение второго источника синхронизируемых напряжений, сдвинутое относительно напряжения одноименного напряжения первого источника на 90°, входы второго блока умножения подключены к зажимам, для подключения на одноименные напряжения указанных источников синхро низируемых напряжений, выход первог блока умножения подключен к входу первого фильтра низких частот, выход первого компаратора через формирователь импульсов подключен к входу логического блока, выполняющего операцию И, к второму входу ко торого подключен выход второго компаратора, вход которого через В|торо фильтр низких частот подключен к выходу второго.блока умножения, к третьему входу логического блока, выполняющего операцию И, подключен вцход логической схемы ограничения максимальной скорости скольжения, а йыход логического блока, выполняю щего операцию И, связан с формирова телем выходных импульсов. При этом формирователь импульсов вьтолнен однополярным. С целью, расширения функциональны возможностей путем осуществления регулирования частоты при синхронизации генераторов, устройство снабжено инвертором, логической схемой ИЛИ и двухвходовой логической схемой И,.при эусм формирователь импульсов выполнен двухполярным, а логической блок, выполняющий onepiaцию И, выполнен в виде двух двухвхо довых логических схем И, выход формирователя импульсов подключен к первому входу первой логической схемы И указанного логического блока, к второму входу которой подключен выход второго компаратора, а вы ход является первым выходом для регулирования частоты и соединен с пе вым входом логической схемы ИЛИ, выход формирователя импульсов через инвертор подключен к первому входу дополнительно введенной двухвходовой логической схемы И, к второму входу которой подключен выход второго компаратора, а выход является вторым выходе для регулирования частоты и соединен с вторым входом логической схемы ИЛИ, выход которой подключен к первому входу второй двухвходовой логической схемы И указанного логического блока, к второму входу которой подключен выход логической схемы ограничения максимальной скорост.и скольжения, а выход соединен с входом формирователя выходных шлпульсов. Логическая схема ограничения максимальной скорости скольжения состоит из логической схемы И, логической схемы НЕ и одновибратора, вход которого подключен к выходу второго компаратора, а выход через логическую схему НЕ подключен к одному входу логической схемы И, к второму входу которой подключен выход второго компаратора, а выход яв- ляется выходом логической схемы. На фиг. 1 и 2 изображена функциональная схема предлагаемого устройства опережения; на фиг. 3 - логическая схема ограничения максималь НОЙ скорости скольжения; на фиг. 4кривые, поясняющие работу устройст- . ва. Устройство опережения, представленное на фиг. 1 и 2, содержит блок 1 умножения, к выходу которого подключен источник одного из синхронизируемых напряжений, например Уд, фазы А.системы. Источник второго синхронизируемого напряжения, например фазы А генератора,.подключен к второму входу блока 1 через блок 2 сдвига фазы на 90°. Шходной сигнал блока 1 подан на вход фильтра 3 низких частот (ФНЧ, выход которого подключен через масштабный преобразователь 4 и соответственно через дифференциатор 5 и масштабный преобразователь б к входам сумматора 7. Выход сумматора 7 через компаратор 8 и однополярный (фиг. 1) или двуполярный (фиг. 2) формирователь 9 импульсов подключен к первому входу логи- ческого блока 10, выполняющего операцию И, К входам второго блока 11 умножения подключены источники синхронизируемых напряжений Иде и U/vj- Выход блока 11 умножения через второй ФНЧ 12 и второй компаратор 13 подключен (фиг. 1) к второму входу логического блока 10, к третьему входу которого подключен выход логической схемы 14 ограничения максимальной скорости скольжения. Выход логического.блока 10 подключен к входу формирователя 15 выходных импульсов . Устройство опережения, представленное на фиг. 2, обладает возможностью осуществлять регулирование частоты при синхронизации генераторов. Для этого логический блок, выполняющий операцию И выполнен в виде двух двухвходовых логических схем И1би17, и устройство снабжено инвертором 18, логической двухвходовой схемой И 19 и логической схемой .ЛЛИ 20. К входу двухвходовой схемы- И 16 подключены выходы формирователя 9 И1 п1ульсов и компаратора 13. К входудвухвходовой схемы И 9 подключены выходы компаратора 13 и инвертора 18. С выходов логических И 16 и 19 снимаются сигналы на регулирование частоты в сторону прибавления и убавления. Кроме того, выходы логических схем И 16 и .19 через логическую схему ИЛИ подключены к входу логической схемы И 17 , к второму входу которой подключен выход логической схемы 1 ограничения максимальной скорости скольжения., а выход подключен к входу формирователя 15 выходных импульсов. На фиг. 3 приведен вариант выпол нения логической схемы 14, где выход второго компаратора 13 подключе к одновибратору 21 и к одному входу логической схемы И 22, к второму входу схемы подключен через логичес кую схему НЕ 23 выход одновибратора 21, а выход схемы 22 является вы ходом логической схемы 14. На фиг. 4 показаны напряжения на выходе элементов схемы фиг. 1 и 2, индекс при напряжении указывает на номер элемента, на выходе которого имеет место данное напряжение. Устройство работает следующим образом. Предположим, что напряжение сиетемы искажено наличием третьей гармоники и будем считать, что .напряжение генератора синусоидальное. ,)Ucfn.jgin( + Lp) Uftr- rr. где выбирают начало отсчета времени отмомента совпадения нулевых значений напряжений U и Uf при отсутствии гармоник. После поворота на 90 напряжения и,.д посредством фазосдвигающей цепи, дифференцирования или интегрирования, получают Uj К cosWft, , где в общем случае () , а напря жение на выходе блока 1 определяется как (OctcostOrt + ,Uc„, 5iл)ct f oscOrt «-O. CJ,t + + 0.5kUr,lJc«,6an(Wc + .5kUr,Ucw, 4C3Wc-Wr)bcf,o.5kUr,Uc sin C3Uctco,),, гдесод cOg-03 - частота скольжения. На выходе ФНЧ 3 будет.только ниэкочастотная составляющая напряжения U,-0.(Ogt, которая не зависит от вцсших гармоник и определяется только основными гармониками Ucft и Uj- . На выходе дифференциатора 5 после масштабного преобразователя 6 напряжение равно,5kU,Uc cosW5, где К - коэффициент преобразования масштабного преобразователя 6. Напряжение на выходе сумматора 7 будет равно .SX kUr -Uc stnwttK(,(OgO,5kUrm, / cm. Alsincost+- -cos Q-si) Ч Л in(). .5tc,kU,U,,,tgc. K4 - коэффициент преобразов1Гния масштабного преобразователя 4. Из (7) следует, что напряжение U7 проходит через ноль дважды за период, когда coi, и когда .CJi-z+oflft Первый случай соответствует противофазному положению векторов синхронизируемых напряжений, а второй совпадению их по фазе. Кривые напряжения на выходе элементов устройства 3, 6 и 7 показаны,на фиг. 4 сплошной линией для случая, когда частота генератора меньше частоты системы cOg, а пунктирной для случая СОо w при одинаковой их разности. Из кривых видной что различить два. нуля напряжения нельзя ниПо знаку U, ни по знаку производной, так как они изменяются при изменении знака разности частот. Предлагается для выявления требуемого нуля использовать знак низкочастотной составляющей произведения синхронизируемых напряжений Цдс и Одг / которая определяется в соответствии с (1) и (2). U« LlJcmi(ctbUcT,5in(3(Octi-i)lx; l rrrn-Sincovt, а на выходе ФНЧ 12, напряжение рав Чm,r«,, U,,j 0.5Uf которое не изменяет знак при измен нии знакасОдИ положительно в облас ти совпадения по фазе синхронизируемых напряжений, что видно на фиг. 4, Комапаратор 13 повыиает чет кость фиксации знака напряжения Щ ПрисОс сОт/ как видно из фиг. 4, сов падает знак импульса на выходе формирователя 9 с положительным напряжением на компаратора 13 и на выходе схемы И 16 появится импул в момент времени tg, определяемый соотношением (Ю) . , 2fl-«t 1л -г:- Если определить tg от обоих частей управления, вытекающего из (10) i ot tg;C2f -coetjb-tgW5CT -t2b-tg(Ogto I где период разностей частоты ( onTfi-t - время опережения. Из (81 откуда t - Кб Чп- -R и не зависит от скорости скольжения и амплитуд основных гармоник синхронизируемых напряжений и от амплитуды и фазы высшей гармоники. Однако сохраняется ограничение, свя занное с заменой в (16) tgtOgt ftcOgton которое при ограниченном значении угла опережения вносит значительно .меньшую погрешность, чем неучет искажения формы в существующих синхро низаторах. Если скорость скольжениясодлсоддоп то с выхода схемы ИЛИ 20 сигнал проходит на выход схемы И 17 и поступает на выход формирователя 15. Выходной импульс формирователя поступает на исполнительное устройство,осуществляющее включение вЫключателя. ЕсписОс Ui-, то при положительном напряжении на выходе компаратора .13 напряжение на выходе формирователя 9 отрицательное и импульс на выходе схемы И 16 отсутствует. При этом оказывается положительным импульс на выходе инвертора 18 и появляется импульс на выходе схемы И 19 , который также появляется со времен.ем опережения, определяемым (17), что приводит к правильному включению выключателя. Наличие двух разных схем И (16 и 19), одна из которых срабатывает когда СОд- Qf, а, вторая когда COs We, независимо от величины скорости скольжения (в определенных пределах), позволяет использовать сигнал с выхода схем И 16 и 19 для подгонки частоты вращения генератора, осуществляя воздействие на (МИСВ) мотор изменения скорости вращения (фиг, 2). Это позволяет отказаться -от выполнения специальной схемы подгонки частоты генератора, хотя и можно использовать сигналы с выхода схем 16 и 19, чтобы воздействовать на МИСВ не непосредственно, а по более сложному закону, зависящему от этих сигналов. Если устройство используется для АПВ линий с двухсторонним питанием, когда отсутствует необхо-г димость управления частотой сОд, то устройство выполняется в соответствии с-фиг. 1. Сигнал с выхода компаратора 13 поступает на вход одновибратора 21, имеющего время срабатывания t.j. Запуск одновибратора происходит всегда с постоянным углЬм опережения 1 /2 момента совпадения фаз основных гармоник синхрони- . зируемых напряжений, (фиг. 4), что соответствует времени опережения fl/2(g. Если одновибратор успеет сработать до появления импульса на выходе схемы ИЛИ 20 (фиг. 2), то при появлении этого импульса появится импульс на выходе схемы И 17 и произойдет включение выключателя. Если же до появления импульса на выходе-схемы ИЛИ 20, одновибратор 21 не сработает, то не будет импульса и на выходе схем, 14 и 17 и не включится выключатель. Отсюда требование, что длительность импульса на выходе формирователя 9 должна быть мала, например представляет собой простой дифференциатор напряжения и с малой постоянной времени, т.е. дает импульсы соответствующего знака при переходе И через ноль. Если одновибратор 21 сработает, то на его выходе исчезнет импульс, а на выходе схемы НЕ 2.3 появится мпульс и до момента изменения знака сигнала компаратора 13 на выходе хемы И 22 будет положительный имульс. С ростом скорости скольжения момент срабатывания одновибраора 21 приближается к моменту оявления импульса на выходе схемы ЛИ 20 и при частоте ограничения эти моменты совпадают. We огр ткуда « -p°za,tot-)

Уравнения (18) и (19) позволяют либо по известной максимсшьной скорости скольжения найти время одновибратора (.20) или по известному его времени найти максимальную,скорость скольжения. Схемы ИЛИ 20 и И 17 позВОЛЯЮТ вводить дополнительный СИЕнал на ограничение возможности включения выключателя, например по раз- ности значений амплитуд синхронизируемых напряжений или их средних значений, что используется в известных синхронизаторах.

Наиболее существенны преимущества предпагаемого устройства опережения в случае синхронизации частей системы посредством АПВ с ожиданием синхронизма, осуществляемого с постоянным временем опережения, когда гармоники могут быть больше, чем при синхронизации генератора системой.

В предлагаемом устройстве исключается ошибка в. угле включения выключателя, определяемая наличием гармоник в синхронизируемых напряжениях и обеспечивается включение выключателя в момент совпадения фаз основных гармоник синхронизируемых напряжений.

Все это позволяет получить существенный экономический эффект, основная часть которого определяется ускорением процесса объединения частей энергосистемы и уменьшением реального толчка тока в оборудовании энергосистем. Величина экономического эффекта зависит от статических параметров, определяющих частоту работы таких устройств, и от влияния увеличения толчков тока на сокращение межремонтных промежутков времени и связанный с этим недоотпуск энергии.

....j

Фиг.2

Uf W/.

л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| БеркоВич М.А | |||

| и др | |||

| Основы автоматики энергосистем | |||

| М., Энергия, 1968, с | |||

| Гидравлический способ добычи торфа | 1916 |

|

SU206A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Электричество, 1981, № 1, с | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

Авторы

Даты

1984-02-07—Публикация

1982-07-16—Подача