и

дг

t

fm

ж г

Изобретение относится к электротехнике и может быть использовано в системах дискретного электропривода с шаговым двигателем.

Известно устройство для управления шаговым двигателем с электрическим дроблением шага, содержащее магнитную память, запоминающие регистры, токовые ключи, дешифраторы двоичный реверсивный счетчик, стробируищее устройство, элементы задержки и логические элементы С17.

Недостатками этого устройства являются сложность и низкая надежность .

Наиболее близким к изобретению по технической сущности является устройство для управления т-фазным шаговым двигателем с электрическим дроблением шага, содержащее m ключевых усилителей мощности, коммутирующих соответствугацие фазы двигателя, и образующие блок дробления шага:одноразрядное постоянное запоминающее устройство с матрицей запоминающего массива и дешифраторами строк и столбцов; реверсивньтй двоичный счетчик, подключенный входами к соответствунщим шинам реверса и низкочастотных импульсов тактирования, а разрядными выходами к входам дешифратора строк запоминающего устройства; нереверсивный счетчик, подключенный входом к шине высокочастотных импульсов тактирования, а разрядными выходами к входам дешифратора столбцов запоминающего устройства. Оно содержит также распределитель импульсов и m логических двухвходовых элементов И,подключенных своими выходами к входам ключев1-к усилителей мощности, первыми входами - непосрественно и через элемент НЕ к выходу запоминакщего устройства, а вторыми входами - к выходам распределителя импульсов, связанного управляющими входами с шинами реверса и установки в исходное состояние, а тактирующим входом - с входом автоматического реверса дво.ичного реверсивного счетчика и одновременно с выходом логического эле. мента ИЛИ, подключенного входами к выходам заема и переноса двоич.ного реверсивного счетчика t2.

Недостатками этого устройства являются сложность (большой объем аппаратуры) и низкая надежность (склонность к нару1чению синхронности работы между распределителем импульсов и запоминающим устройством из-за случайных сбоев в распределителе импульсов или в двоичных счетчиках).

Целью изобретения является упрощние и повышение надежности устройства

Поставленная цель достигается тем, что в устройстве для управления m -фазным шаговым двигателем с электрическим дроблением шага, содержащем m ключевых усилителей мощности, коммутиругадих соответствующие фазы двигателя, и блок дробления шага, включающий в себя первое одноразрядное постоянное запоминающее устройство с матрицей запоминающего массива и дешифраторами строк и столбцов, реверсивный двоичный счетчик, подключенный входами к соответствующим шинам реверса и низкочастотных импульсов тактирования, а разрядными выходами - к входам дешифратора строк первого одноразрядного постоянного запоминакгдего устройства, и нереверсивный двоичный счетчик, подключенный входом к шине высокочастотных импульсов тактирования, а разрядными выходами - к входам дешифратора столбцов первого одноразрядного постоянного запоминающего устройства, блок дробления шага дополнительно снабжен т-1 дополнительными одноразрядными постоянными запоминающими устройствами, идентичных первому, входы дешифраторов строк и С-толбЦов которых объединены и подключены к аналоговым входам первого одноразрядного постоянного запоминающего устройства, а выходы матриц запоминающих массивов с первого по hi одноразрядных постоянных запоминающих устройств непосредственно подключены соответственно к входам с первого по m ключевых усилителей мощности,

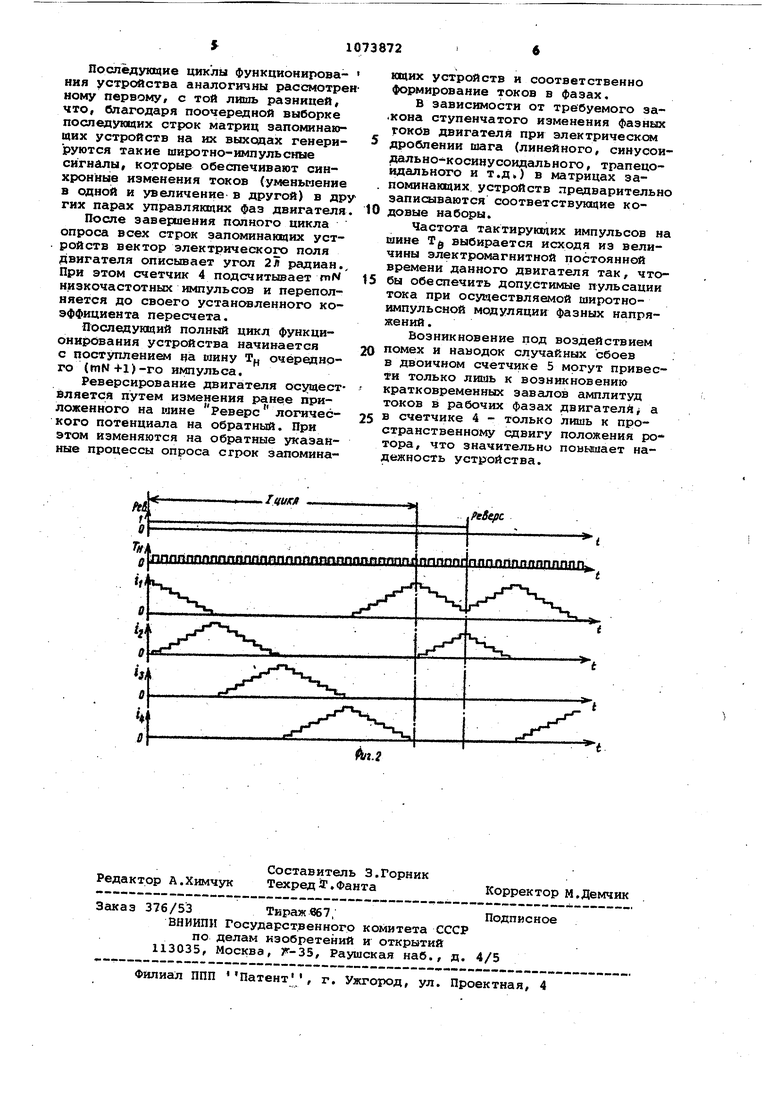

На фиг, 1 приведена функциональная схема предлагаемого устройства; на фиг, 2 - временные диаграммы, поясняющие работу схемы,

стройство (фиг,1) содержит одноразрядные постоянные запоминаюгчие устройства 1,1-1т по числу каналов усилителя мощности, ключевые усилители 2,1-2т мощности, коммутирующие фазы 3,1-3m двигателя, реверсивный двоичный счетчик 4 и нереверсивный двоичный счетчик 5,

Входы внутренних дешифраторов строк всех запоминающих устройств 1,1-1 т, объединены и подключены к соответствугацим разрядным выходам реверсивного двоичного счетчика 4, а входы внутренних дешифраторов столбцов этих запоминающих устройст объединены и подключены к соответствующим разрядным выходам нереверсивного двоичного счетчика 5, Выходы запоминающих устройств 1,1-lm непосредственно подключены соответственно к входам ключевых усилителей 2,1,2т мощности. Тактовый вход нереверсивного двоичного счетчика 5 соединен с шиной высокочастотных, импульсов тактирования Tg, а тактовый вход реверсивного двоичного счетчика 4 - с шиной низкочастотных импульсов тактирования Тц. Вход задания направления пересчета реверсивного двоичного счетчика 4 соединен с шиной реверсирования (задания направления вращения) двигателя Реверс , а его вход обнуления - к шине установки в исходное нулевое состояние цУст. Устройство работает следугачим образом. В первоначальном состоянии на шину УСТ.о устройства (фиг.1) подается сигнал установки в исходное состояние. При этом счетчик 4 устанавливается в нулевое исходное состояние и через внутренние дешифраторы строк запоминающих устройств 1.1-1m выбираются первые строки их матриц. В соответствии с требуемым направлением вращения двигателя к шине уРеверс прикладывается единичный или нулевой уровни потенциалов. При подаче на шину Т„ высокочастотных импульсов тактирования в двоичном счетчике 5 (фиг.1) происхо дит потактный подсчет импульсов. При этом через внутренние дешифраторы, столбцов матриц всех запоминающих устройств осу1:1ествляется поочередное считывание записанных в ячейках первых строк матриц кодовых комбинаций. В первом такте Tg на вы ход каждого из запоминающих устройс выдается информация его первой ячей ки, во втором такте - второй ячейки и т.д. до N-ой ячейки, где N- крат ность дробления. В результате этого в исходном состоянии устройства на выходе запоминающего устройства 1.1 возникае постоянный единичный потенциал (иззаписанных единиц во всех ячейках первой строки его матрицы), а на вы ходах остальных запоминавших устройств 1.2-1гп возникают постоянные нулевые потенциалы (из-за записанных нулей во всех ячейках первых строк их матриц). Эти потенциалы от запоминающих устройств поступают на входы соответствующих ключевых усилителей мся ности, в результате чего в фазе 3. шагового двигателя в исходном сост янии обеспечивается протекание ток номинального значения 3 ,. при нуле вых токах в остальных фазах ( фиг.2) . При поступлении на шину Т первого низкочастотного тактирующего импульса в двоичном счетчике 4 записывается единица, в результате чего Ч(ерез внутренние дешифраторы строк запоминающих устройств выбираются вторые строки их матриц. При этом в такт поступления на шину Т. (фиг.2) тактирующих импульсов происходит высокочастотное периодическое считывание информации всех ячеек вторых строк матриц запоминающих устройств. Благодаря этому на выходе запоминаквдего устройства 1.1 возникает генерация высокочастотных импульсов со скважностью N/N-1 (из-за записанных единиц и одного нуля в ячейках второй строки его матрицы), а на выходе устройства 1.2 возникает генерация аналогичных импульсов, но со скважностью N (из-за записанной одной единицы и N-1 нулей в ячейках второй строки его матрицы). На выходах остальных запоминающих устройств возникают постоянные нулевые потенциалы. Эти импульсы, поступая на входы усилителей 2.1-2tTi, создают токи величуной М-1/МЭ - в первой фазе и 1/N 3, - во второй фазе (при нуевых токах в остальных фазах). В последующих тактах поступления импуль,сов на шину T/i, аналогично указанному первому такту, через реверсивный счетчик 4 происходит дальнейшая порчередная выборка последующих строк матриц запоминающих устройств. В соответствии с этим поочередно формируются периодические высокочастотные импульсы со скважностью N/N-2, N/N-3N - на выходе устройства 1.1 ч со скважностью N/2, N/3 ......N/N-1 - на выходе устройства 1.2. Это приводит к линейноступенчатому уменьшению тока t4-2/N Зц N-S/NJj - в фазе 3.1 двигателя и его увеличению 2NDH 3/N Зн Ы-1/МЭц в.фазе 3.2 (фиг.2). В последнем N-OM такте этого цикла в фазе 3.2 двигателя устанавливается номинальное значение тока JH (при нулевых значениях токов во всех остальных фазах). При указанном цикле работы устройства (применительно к четырехЛазному двигателю) за N тактов поступления низкочастотных импульсов на шину T в первых двух фазах двигателя осуществляется линейное N-стуу пенчатое изменение тока (уменычение в первой фазе и одновременное увеличение во второй фазе). Ступенчатое изменение токов в смежных фазах двигателя приводит к ступенчатому повороту суммарного вектора электромагнитного момента и соответственно ротора. В результате ротор отрабатывает N дробных шагов, величиной AP-fT .величина основного шага.

Последующие циклы функционирования устройства аналогичны рассмотренному первому, с той лишь разницей, что, благодаря поочередной выборке последующих строк матриц запоминающих устройств на их выходах генерируются такие широтно-импульсные сигналы, которые обеспечивают синхронные изменения токов (уменьшение в одной и увеличение в другой) в дру гих парах управлякщих фаз двигателя.

После завершения полного цикла опроса всех строк запоминаюдих устройств вектор электрического поля двигателя описывает угол 2л радиан.. При этом счетчик 4 подсчитывает mN низкочастотных импульсов и переполняется до своего установленного коэффициента пересчета.

Последупщий полный цикл функционирования устройства начинается с поступлением на шину Т очёреас ного {mN+i)-ro импульса.

Реверсирование двигателя осуществляется путем изменения paHSie приложенного на шине Реверс логического потенциала на обратный. При этом изменяются на обратные указанные процессы опроса строк запомина.

М

Tff.

pnnrinnnnnnnnnnnnлпппястппг№ягтппш{nnnnnrjnлnnfinnnnnлnnn

кхцих устройств и соответственно формирование токов в фазах.

В зависимости от требуемого за.кона ступенчатого изменения фазных ГОКОВ двигателя при электрическом дроблении шага (линейного, синусоидально косинусоидального, трапецоидального и т.д.) в матрицах запоминающих устройств предварительно записываются соответствующие кодовые наборы.

Частота тактирукщих импульсов на шине Tg выбирается исходя из величины электромагнитной постоянной времени данного двигателя так, чтобы обеспечить допустимые пульсации тока при осуществляемой широтноимпульсной модуляции фазных напряжений .

Возникновение под воздействием помех и наводок случайных сбоев в двоичном счетчике 5 могут привести только лишь к возникновению кратковременных завалов амплитуд токов в рабочих фазах двигатели а в счетчике 4 - только лишь к пространственному сдвигу положения ротора, что значительно повышает надежность устройства.

feStfc

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления @ -фазным шаговым двигателем с дроблением шага | 1986 |

|

SU1372589A1 |

| Устройство для программного управления четырехфазным шаговым двигателем с насыщенной магнитной системой | 1989 |

|

SU1702340A1 |

| Устройство для программного управления четырехфазным шаговым двигателем | 1989 |

|

SU1649513A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1983 |

|

SU1149367A2 |

| Устройство для управления шаговым двигателем с дроблением шага | 1982 |

|

SU1061230A1 |

| Устройство для программного управления четырехфазным шаговым двигателем | 1988 |

|

SU1531072A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1989 |

|

SU1679598A1 |

| Устройство для программного управления @ -фазным шаговым двигателем | 1990 |

|

SU1718187A1 |

| Устройство для управления @ - фазным шаговым двигателем | 1988 |

|

SU1647841A1 |

| Устройство для управления @ -фазным шаговым двигателем | 1987 |

|

SU1443116A1 |

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ №-ФАЗНИМ ШАГОВЫМ ДВИГАТЕЛЕМ С электрическим дроблением шага, содержащее m ключевых усилителей мощности, коммутирующих соответствую- щие фазы двигателя, и блок дробления шага, включающий в себя первое одноразрядное постоянное запоминающее устройство с матрицей запоминакхце1х массива и дешифраторами строк и столбцов, реверсивный двог ичный счетчик, подключенный, входами к соответствующим шинам реверса и низкочастотнык импульсов тактирования, а разрядньоли выходами к входам дешифратора строк первого одноразрядного постоянного запоминающего устройства, и нереверсивный счегчик, подключенный входом к шине высокочастотных импульсов тактирования, а разрядными входами - к входам дешифратора столбцов первого одноразрядного постоянного запоминающего устройства, о т л и чающееся тем что, с целью упрощения и повышения надежности устройства, блок дробления шага дополнительно содержит т-1 дополнитель. них одноразрядных постоянных запоминахщих устройств, идеитичнкх первому, входы дешифраторов строк и столбсл цов которых объединены и подключены к аналогичным входам первого одноразрядного постоянного запоминающего устройстйа, а выходы матриц запо минающих массивов с первого по m одноразрядных запоминающих устройств непосредственно подключены соответственно к входам с первого по m ключевых усилителей мощности. J.I . 3-tn I fO I i EZIfe

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гумен в,Ф,, Калининская Т.В, Принципы построения схем управления шаговыми двигателями в режиме дробления основного шага,-в кн.: Электромашинные средства автоматики, Киев, 1975, с, 51-56, 2 Авторское свидетельство СССР по заявке 3344558/07, кл, Н 02 Р 8/00, 1981, | |||

Авторы

Даты

1984-02-15—Публикация

1982-12-13—Подача