вход каждого -го разряда регистра ($ i 4 f ) Соединен с выходом соответствующего элемента ИЛИ второй группы, единичный выход первого триггера через формирователь импульса соединен с первым входом третьего элемента ИЛИ, выход которого соединей с вторым входом счетчика, выходы которого являются старшими разрядами 97 группы выходов устройства, выход каждого i -го элемента И первой группы (1 V соединен с вторым 2 -)- -) -го разряда нулев)1м входом ( регистра и соответствующим входом третьего элемента ИЛИ, выход второго элемента ИЛИ является выходом конца счета устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения двоичныхчиСЕл | 1979 |

|

SU822178A1 |

| Устройство для сравнения чисел | 1979 |

|

SU809168A1 |

| Устройство для сравнения двоичных чисел | 1976 |

|

SU664170A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Устройство для сортировки чисел | 1986 |

|

SU1310803A1 |

| Устройство для определения количества единиц в двоичном числе | 1985 |

|

SU1261121A1 |

| Двоичный счетчик | 1983 |

|

SU1150758A1 |

| Устройство для определения количества единиц в двоичном числе | 1988 |

|

SU1547072A2 |

| Устройство для определения количества единиц в двоичном числе | 1986 |

|

SU1322480A1 |

| Генератор последовательности чисел | 1981 |

|

SU999032A1 |

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЛИЧЕСТВА ЕДИНИЦ В ДВОИЧНОМ ЧИСЛЕ, содержащее регистр, два элемента ИЛИ, два триггера, первую группу элементов ИЛИ и первую группу элементов И, причем выход первого элемента ШШ соединен со сч-етным входом первого, триггера, единичный выход которого является младшим разрядом группы выходов устройства, единичный выходкаждого разряда регистра соединен с прямым входом соответствующего элемента И первой группы и соответствующим входом второго элемента ИЛИ, выход которого соединен с единичным входом второго триггера, нулевой вход которого является входом запуска устройства, единичные выходы всех разрядов регистра, кроме 1 -го (И - разрядность регистра), соединены с первыми входами соответствуюпщх элементов ИЛИ первой группы, выход каждого 4 -го элемента И первой группы

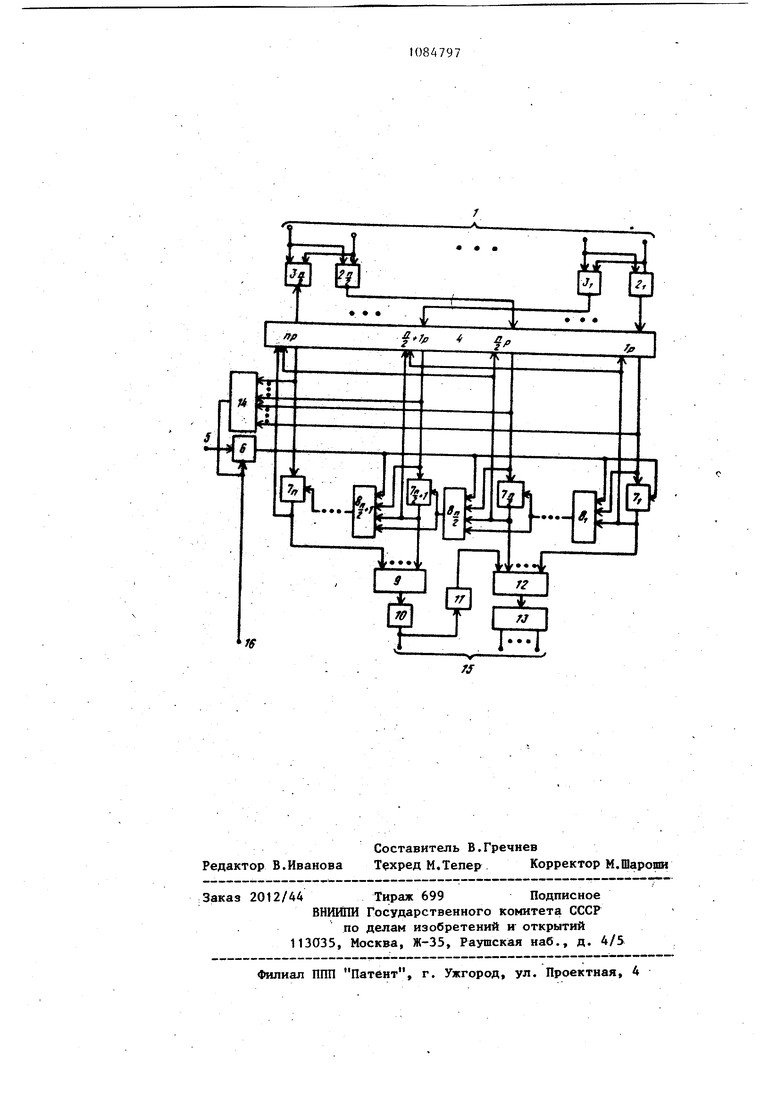

Изобретение относится к вычислительной технике и может быть исполь зовано для проверки двоичных кодов на tsTHocTb или в декодирующих устройствах для определения веса в код вых комбинациях корректирующих кодов, принимаемых в параллельном вид Известно устройство для определе ния количества единиц в двоичном чи ле, содержащее триггер, два элемента И и элемент ИЛИ для каждого из И ра рядов контролируемого числа, счетчик элемент И-НЕ и два элемента И . Недостатком данного устройства является недостаточно высокое быстродействие, обусловленное использованием тактовых импульсов для подсчета количества единиц, Наиболее близким по технической сущности к изобретению является устройство, содержащее регистр, первый и второй элементы ИЛИ, первый и втЪроТй триггеры, группу элементов ИЛИ и группу элементов И, причем единичные входы разрядов регистра образуют группувходов устройства, выход первого элемента ИЛИ соединен со счетным входом первого триггера, выход которого является выходом устройства, единичный выход каждого разряда регистра соединен с соответствующим входом второго элемента ИЛИ, выход которого соединен с единичным входом второго триггера и с управляющим входом первого триггера, нулевой вход второго триггера является управляющим входом устройства, единичный выход каждого разряда регистра соединен с первым входом соответствующего элемента И группы и входом соответствующего элемента ИЛИ группы, а выход каждого элемента И группы соединен с соответствующим входом первого элемента ИЛИ, с нулевым входом соответствующего разряда регистра и входом соответствующего элемента ИЛИ группы, нулеврй выход второго триггера соединен с соответствующими входами всех элементов ИЛИ группы и с инверсным входом первого элемента И группы, выход 1 элемента ИЛИ группы соединен с инверсным входом 1+1 элемента И группы и с соответствующим входом i + 1 элемента ИЛИ группы 2j. Недостатком известного устройства также является недостаточное быстродействие. Цель изобретения - повьш1ение быстродействия устройства. Поставленная цель достигается тем, что в устройство для определеления количества единиц в двоичном числе, содержащее регистр, два элемента ИЛИ, два триггера, первую группу элементов ИЛИ и первую групру элементов И, причем выход первого элемента РШИ соединен со счетным .входом первого триггера, единичный выход которого является младшим разрядом ГРУППЫ выходов устройства, единичный выход каждого разряда регистра соединен с прямым входом соответствующего элемента И первой группы и соответствующим входом второго элемента ИЛИ, вькод которого соединен с единичным входом второго триггера, нулевой вход которого является входом запуска устройства, единичные выходы всех разрядов регистра, кроме ц -го ( п - разрядность регистра), соединены с первуми входами соответствующих элементов ИЛИ первой группы, выход каждого ;-i-ro элемента И первой группы ( 1 -f - - соединен с нулевым входам -го разряда регистра и вторым входом .1-го элемента ИЛИ первой группы выход каждого J -го элемента И первой группы ( ii ) соединен с первым нулевым входом j -го разряда регистра и соответствующим входом первого элемента ИЛИ, выход каждого k-го элемента И первой группы ( : k И - 1) соединен с вторым входом k -го элемента ИЛИ первой груп пы, единичньй выход второго триггера соединен с третьими входами всех элементов ИЛИ первой группы и инверсным входом первого элемента И первой группы, выходкаждого m-го элемента ИЛИ первой группы (liwt - 2) соединен с инверсным входом ( HI + 1)-го элемента И первой группы и четвертым входом (Ш + 1)-го элемента И первой группы и четвертым входом (m + 1)-го элемента ИЛИ первой группы, выход ( и - 1)-го элемента ИЛИ первой группы соединен с инверсным входом и -го элемента И первой группы, введены третий элемент ИЛИ, формирователь импульса, счетчик, вторая группа элементов ИЖ и вторая группа элементов И, при чем первый и второй входы каждого t-ro элемента И второй группы ( S 2 соединены соответственно с пер вым и вторым входами t -го элемента ИЛИ второй группы и являются информационными входами устройства, единичный вход каждого -го разряда регистра ( -г) соединен с выхо дом соответствующего элемента И второй группы, единичный вход каждого 4 -го разряда регистра ( 1 , ; „ ) -- J 6 г соединен с выходом соответствующего элемента ИЛИ второй группы, единичный выход первого триггера через фор- 0 мирователь импульса соединен с первым входом третьего элемента ИЛИ, выход которого соединен с вторым входом счетчика,выходы которого являются старшими разрядами группы вы-55 ходов устройства, выход кaждoг „J-го элемента И первой (1 V & Л) 2 соединен с вторым нулепым входом ( 1 -)-го разряда регистра и соответствующим входом третьего элемента ИЛИ, выход второго элемента ИЛИ является выходом конца счета устрой.ства. На чертеже приведена функциональная схема устройства для определения количества единиц в двоичном числе. Устройство содержит информационные входы 1 устройства, вторую группу элементов И 2, вторую группу элементов ИЛИ 3 регистр 4, вход 5 запуска устройства, второй триггер 6, первую группу элементов И- 7, первую группу элементов ИЛИ 8, первый элемент ИЛИ 9, первый триггер 10, формирователь 11 импульса, третий элемент ИЛИ 12, счетчик 13, второй элемент ИЛИ 14, группу 15 выходов устройства, выход 16 конца счета устройства. В качестве формирователя 11 импульса можно использовать ждущий мультит вибратор, запускаемый при переходе входного сигнала из единичного в .нулевое состояние. Длительность импульса на его выходе должна быть равной длительности импульса на выходе элемента И 7 первой группы. Цепи начальной установки устройства на чертеже не показаны. Устройство работает следующим образом. После начальной установки триггер находится в единичном состоянии, триггер 10 и счетчик 13 в нулевом, Входная двоичная информация посту входы 1 в параллельном коде и каждые из нее 2 - 1 и разрядов преобразуются элементами И и ИЛИ 3 таким образом, что в 1 -и разряд регистра записывается конъюнк+ - -и разряд - дизъюнкция содержимого 2- - 1 и 2 разрядов контролируемого числа. После окончания записи информации триггер 6 управляющим сигналом с входа 5 запуска устройства переводится в нулевое состояние. При этом снимается единичный запрещающий сигнал с входов элементов ИЛИ 8 первой группы и инверсного входа первого элемента И 7 первой группы. Если в первом разряде регистра записана 1, то после снятия запреп1ающего сигнала с входа первого элемента ИЛИ 8 пер вой группы, его выход удерживается в единичном состоянии сигналом с ед ничного выхода первого разряда регистра и задерживает обработку более старших разрядов. Нулевой сигнал, поданный на инверсньй вход пер вого элемента И 7 первой группы, вы зывает появление на его выходе еди1ИЧНОГО сигнала, который через треий элемент ИЛИ 12 поступает на четчик 13, этот же сигнал вызывает :тирание единиц в первом и Л + 1 разрядах регистра и поддерживает запрещающий сигнал на выходе первого элемента ИЛИ 8/ первой группы. После стирания 1 в первом разряде только после окончайия импульса на выходе первого элемента И 7 первой группы снимается запрещающий сигнал на выходе первого элемента ИЛИ первой группы и разрешается опрос второго разряда регистра. Если там содержится 1, то все происходит аналогично описанному, если же, О то на выходе второго элемента ИЛИ 8 первой группы появится сигнал нулев го уровня и будет разрешен опрос Следующего третьего разряда и т.д. Если в младшем ( 1 6 i Л) регистра обнаруживается 1, это оз начает наличие пары единиц в 2 И 2 i разрядах контролируемого числа, поэтому в счетчик,,чей младший разряд является вторым разрядом кода числа единиц, заносится 1. Единица в 1+2 разряде регистра, образованная дизъюнкцией той же пары единиц, при этом стирается. Комбинации вида 01 и 10 в контролируемом коде дают 1 ы соответствующих старших разрядах регистра. Сигналы опроса этих единА; через соответствующие элементы И 7 первой группы и элемент ИЛИ 9 попадают на счетный триггер 10, являющийся младшим разрядом кода подсчитываемых единиц.На выходе формирователя 11 появляется импульс в момент перехода триггера 10 из 1 в О. Момент оканчания счета единиц в коде определяется эленентом ИЛИ 14, который срабатывает при обнулении регистра 4, устанавливает триггер 6 в 1 и формирует сигнал на выходе 16 конца счета устройства. Устройство можно использовать также для контроля четности, используя в качестве выхода устройства выход триггера 10. Таким образом, предлагаемое устройство позволяет -уменьшить время подсчета количества единиц двоичного числа за счет того, что время обработки двух единиц, расположенных в разрядах и 2 - 1 контролируемого числа, оказывается равным времени обработки одной единицы.

л Т

Авторы

Даты

1984-04-07—Публикация

1982-12-27—Подача