112

Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля.

Цель изобретения - повьпнение быстродействия и упрощение устрой- ства.

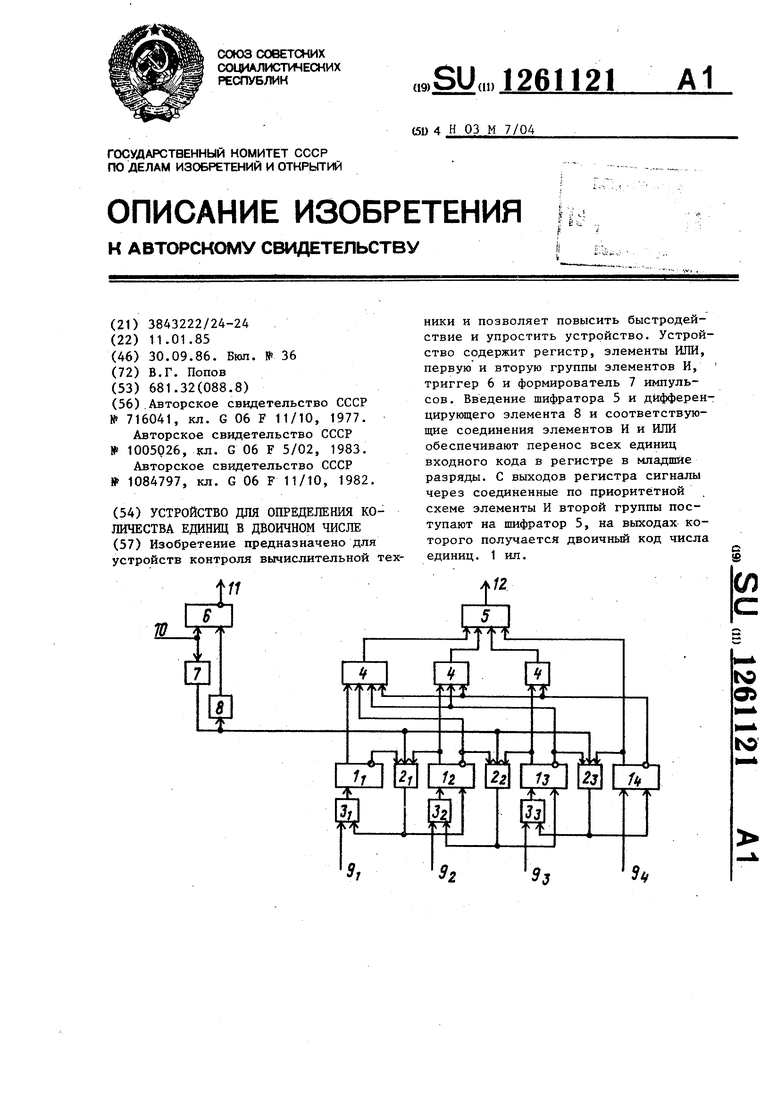

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство для определения количества единиц в двоичном числе со- держит регистр 1, состоящий из п разрядов, II-1 элементов 2И первой группы, п-1 элементов 3 ИЛИ, п-1 элементов 4 И второй группы, шифратор 5, триггер 6, формирователь 7 импульсов и дифференцирующий элемент 8. Информационные входы 9 устройства, кроме п-го, соединены с первыми входами соответствующих элементов 3 ИЖ, выходы которых и п-й информационный йход 9 устройства подключены к информационным входам соответствующих разрядов регистра 1. Прямой выход йервого разряда регистра 1 подключен к первому входу первого элемента 4 И второй группы. Прямой выход i-ro разряда (,3,...,п-1) регистра 1 соединен с первым входом соответствующего элемента 4 И второй группы и с первым входом (i-l)-ro элемента 2 И первой группы. Прямой выход п-го регистра 1 соединен с соответствующим входом шифратора 5 и с первым входом (п-1)-го элемента 2 И первой группы. Выход i-ro элемента

2И первой группы подключен к второму входу соответствующего элемента

3ИЛИ и обнуляющему входу (i+1)-ro разряда регистра 1. Вторые входы элементов 2 И первой группы объеди- йены с входом дифференцирующего элемента 8 и подключены к выходу формирователя 7 импульсов, вход которого объединен с первым входом триггера 6 и подключен к входу 10 запуска устройства. Выход дифференцирующего элемента 8 соединен с вторым входом триггера 6, выход которого является управляющим выходом 11 устройства. Инверсный выход первого разряда ре- гистра 1 подключен к третьему входу первого элемента 2 И первой группы, инверсный выход i-ro (,3,...,п-1) разряда регистра 1 соединен с третьим входом соответствующего элемента 2 И первой группы и одним иэ входов j-ro () элемента 4 И второй группы. Инверсный выход п-го разряда под

5 0

0 5

0

12

ключен к последним входам всех элементов 4 И второй группы, выходы которых соединены с соответствующими входами шифратора 5, выходы которого являются информационными выходами 12 устройства.

На чертеже вход 10 запуска устройства соединен с входом установки триггера 6 в единицу, а выход дифференцирующего элемента 8 - с входом установки 6 в ноль, при этом инверсный выход триггера 6 является управляющим выходом 11 устройства. При другом выборе логических уровней указанные входы триггера 6 меняются местами, а к управляющему выходу 11 подключается прямой выход триггера 6.

Устройство работает следующим образом.

Исходное состояние устройства характеризуется тем, что триггер 6 установлен в состояние О (не показано), а по входам 9 через элементы 3 ИЛИ в регистр 1 принят анализируемый двоичный код числа. Работа устройства начинается по сигналу пуска, которьй поступает на вход 10, устанавливает триггер 6 в состояние 1, запуская формирователь 7. Пусть в регистр 1 принят двоичный код 1010. При этом элемент И 2 закрыт, а элемент И 2 открыт по первому и третьему входам. По импульсу формирователя 7 единичным сигналом с выхода И 2 разряд 1 устанавливается . в состояние О, а разряд - в состояние 1 через элемент ИЛИ 3. При этом в регистре 1 фиксируется код 1100. Для любых кодов, принятых в регистр 1, по импульсу формирователя 7 производится последовательный сдвиг единиц в сторону младших первых разрядов регистра 1. При этом максимальная длительность импульса формирователя 7, во время действия которого обеспечивается преобразование кода, выбирается исходя из длительности переходных процессов при наличии только одной единицы в старшем разряде регистра 1.

Номер разряда регистра 1, где оказьшается крайняя правая единица, отражает количество единиц в двоичном коде. Определение этого разряда, выполняется второй группой элементов 4 И, подключенных к выходам разрядов регистра 1 по приоритетной схеме. Так, для приведенного примера

единичными сигналами с нулевых выходов разрядов Ц и 1, открыты элемент и42И, а нулевым сигналом с нулевого выхода разряда 1 закрыт элемент 4, И. Таким образом, на выходах элементов 4 И формируется унитарный код вида 0100, поступающий на входы шифратора 5. Ввиду того, чт единичный сигнал присутствует на втором входе шифратора 5, то на его выходах 12 формируется двоичный код числа 2, означающий наличие двух единиц в анализируемом двоичном коде числа.

Посредством дифференцирующего элемента 8 формируется по заднему фронту импульса формирователя 7 сигнал, устанавливающий триггер 6 в нулевое состояние. Единичный сигнал с нулевого выхода триггера 6, поступающий на управляющий выход 11 устройства, используется как сигнал завершения работы устройства. По этому сигналу с выходов 12 устройства дво- ичный код количества единиц передается в систему контроля.

Для очередного цикла работы по входам 9 в регистр 1 записывается анализируемый код числа, а по входу 10 подается сигнал запуска.

Формула изобретения

Устройство для определения количества единиц в двоичном числе, содержащее регистр, состоящий из п разрядов, п-1 элементов ИЛИ, две группы по п-1 элементов И, формирователь импульсов и триггер, первый вход.которого является входом заРедактор С. Лисина

Составитель О. Ревинский

Техред И.Попович Корректор В. Синицкая

Заказ 5245/58 Тираж 816Подписное

ВНИШ1И Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

пуска устройства, информационные входы устройства, кроме п-го, соединены с первыми входами соответствующих элементов ИЛИ, выходы которых подключены к информационным входам соответствующих разрядов регистра, выход i-ro разряда которого кроме первого, соединен с первым входом (i-1)-ro элемента И первой группы, выход которого подключен к обнуляю- . щему входу i-ro разряда регистра, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства, в него введены шифратор и дифференцирующий элемент, выход которого подключен к второму входу триггера, выход которого является управляющим выходом устройства, а первый вход объединен с входом формирователя импульсов, выход которого подключен к входу дифференцирующего элемента и вторым входам элементов И первой группы, выход каждого из которых соединен с вторым входом соответствующего элемента ИЛИ, информационный вход п-го разряда регистра является п-м входом устройства, прямые выходы разрядов регистра, кроме п-го, соединены с первыми входами соответствующих элементов И второй грзтпы, инверсный выход i-ro разряда регистра подключен к третьему входу соответствующего элемента И первой группы и к одному из входов j-ro элемента И второй группы, , выходы элементов И вто- рой группы и прямой выход п-го разряда регистра соединены с соответствующими входами шифратора, выходы которого являются информационными выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Устройство для моделирования систем массового обслуживания | 1988 |

|

SU1552196A1 |

| Устройство для определения положения числа на числовой оси | 1986 |

|

SU1335978A1 |

| Преобразователь двоично-К-ичного кода в двоичный код | 1990 |

|

SU1783618A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Устройство для сортировки двоичных чисел | 1982 |

|

SU1049900A1 |

| Устройство для сравнения чисел | 1981 |

|

SU1023321A1 |

| Устройство для определения количества единиц в двоичном коде | 1986 |

|

SU1309029A1 |

| Устройство для определения количества единиц в двоичном числе | 1982 |

|

SU1084797A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

Изобретение предназначено для устройств контроля вычислительной техники и позволяет повысить быстродействие и упростить устройство. Устройство содержит регистр, элементы ИЛИ, первую и вторую группы элементов И, триггер 6 и формирователь 7 импульсов. Введение шифратора 5 и дифференцирующего элемента 8 и соответствующие соединения элементов И и ИЛИ обеспечивают перенос всех единиц входного кода в регистре в младшие разряды. С выходов регистра сигналы через соединенные по приоритетной схеме элементы И второй группы поступают на шифратор 5, на выходах которого получается двоичный код числа единиц. 1 ил. (Л ю Од

| Устройство для определения количества едениц в двоичном числе | 1977 |

|

SU716041A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения количества единиц в двоичном коде N-разрядного числа | 1981 |

|

SU1005026A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения количества единиц в двоичном числе | 1982 |

|

SU1084797A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-30—Публикация

1985-01-11—Подача