(К+1)-го регистра результата, прямой выход триггера старшего разряда группы счетных триггеров, которые соединены последо.вательно, (К+1)-го регистра результата соединен с управляющим входом (К+1)-го блока вычисления последующего кода, инверсный выход триггера старшего разряда группы

младших разрядов (К+1)-го регистра результата соединен с синхронизирующим входом параллельного регистра старших разрядов К+1-ГО регистра результата. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный счетчик | 1984 |

|

SU1261107A1 |

| Многоканальный десятичный счетчик | 1979 |

|

SU824443A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1132289A1 |

| Устройство для извлечения корня третьей степени | 1983 |

|

SU1129609A1 |

| Интегро-дифференциальный вычис-лиТЕль | 1979 |

|

SU798902A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Цифровой генератор функций | 1981 |

|

SU1035594A1 |

| Электропривод постоянного тока | 1983 |

|

SU1100697A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU997038A1 |

ДВОИЧНЫЙ СЧЕТЧИК, содержа. щий первьй регистр результата, выходы которого являются выходами счетчика, а вход младшего разряда, который выполнен в ввде счетного триггера, - входом счетчика, и первый блок вычисления последующего кода, выходы которого соединены с входами всех разрядов первого регистра результата, кроме входа младшего разряда, прямой выход триггера младшего разряда первого регистра результата соединен с управляющим входом первого блока вычисления последующего кода, отличающийс я тем, что, с целью уменьшения времени регистрации, первый регистр результата во всех разрядах кроме младшего, выполнен в виде параллельного регистра, синхронизирующий вход которого соединен с инверсным выходом счетного триггера младшего разряда первого регистра результата, первый блок вычисления последующего кода содержит второй регистр результата, младшие разряды которого выполнены в виде группы счетных триггеров, которые соединены последовательно, а старшие разряды - в виде параллельного регистра, выходы второго регистра результата являются выходами первого блока вычисления последующего кода, а вход младшего разряда второго регистра результата управляющим входом первого блока вь числения последующего кода, второй блок вычисления последующего кода, выходы которого соединены с входами старших разрядов второго регистра результата, прямой выход триггера старшего разряда группы счетных триггеров второго регистра результата соединен с управляющим входом второго блока вычисления последующе(Л го кода, инверсньй выход триггера с старшего разряда группы счетных триг-, геров второго регистра результата соединен с синхронизирующим входом параллельного регистра старших разрядов второго регистра результата, последующий К-й блок, вычислеСП ния последующего кода, который содержит (К+1)-й регистр результата, ел младшие разряды которого вьшолнены в виде последовательно соединенной Об группы счетньк триггеров, а старшие разряды - в виде параллельного регистра, выходы ()-го регистра результата являются выходами К-го блока вычисления последующего кода, а вход младшего разряда (К+1)-го регистра результата - управлйющим входом К-го блока вычисления после.дующего кода, (К+1)-й блок вычисления последующего кода, выходы которого соединены с входами параллельного регистра старших разрядов

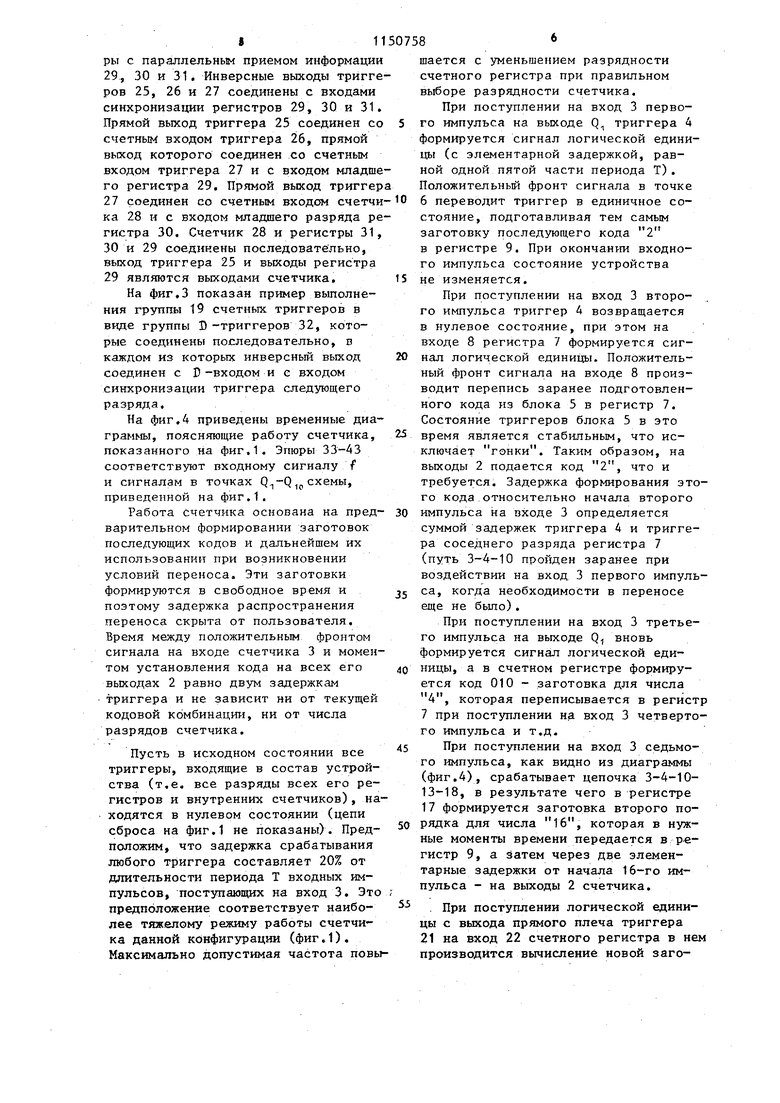

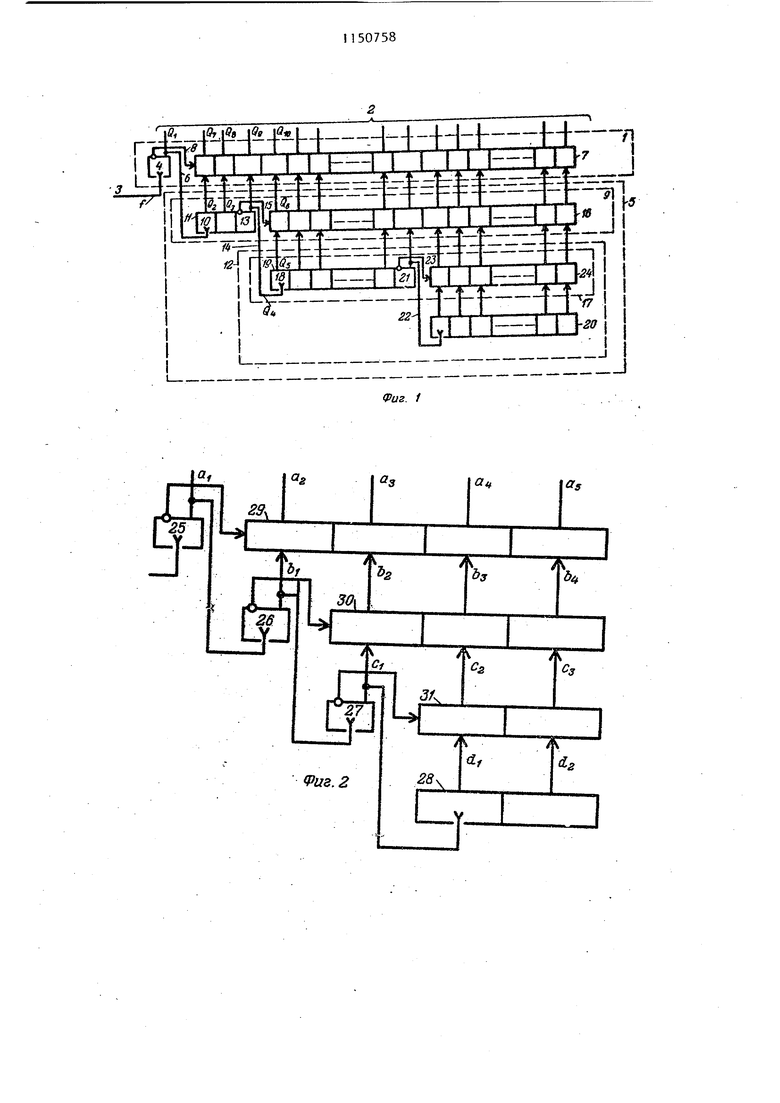

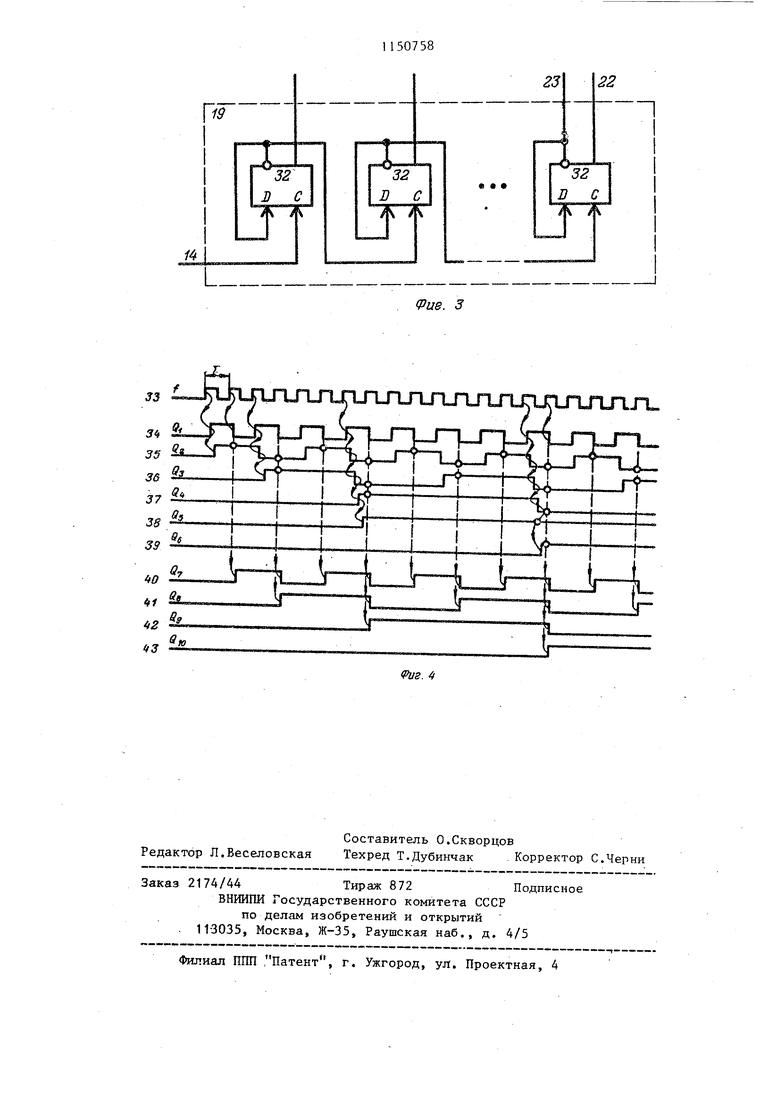

Изобретение относится к импульсной технике, в частности к двоичным счетным устройствам. Известен двоичный счетчик со сквозным переносом, содержащий в каждом разряде 3-К триггер с объединенными 3-К входами, вход счетчика соединен со всеми входами синхронизации D-K триггеров, 3-К вход триггера любого разряда, кроме млад шего, соединены с выходом соответствующего элемента И, .входы которого соединены с выходами всех предыдущих разрядов, начиная с младшего, J-K входы триггера младшего разряда соединены с шиной единичного логического сигнала 1. Недостатком этого счетчика является линейная зависимость числа вхо дов элементов И и нагрузки на выход младших разрядов от разрядности сче чика. Это Приводит к необходимости каскадирования элементов ИиуМощнения сигналов, что, в свою очередь приводит к снижению максимально допустимой частоты работы счетчика и к увеличению времени регистрации. Известен двоичньй счетчик, содер жащий регистры результата, каждый из которых содержит счетные триггер которые соединены последовательно, и регистры, синхронизирующие входы которых соединены с управляюш ш вхо дом регистра результата, выход кото рого является выходом регистра, вхо которого соединены с выходами счетных триггеров 1. Недостатком этого двоичного счет чика является сравнительно большое время регистрации, равное задержке появления кода на выходе после поступления входного импульса. Наиболее близким по технической сущности к предпагаемому является двоичный счетчик, содержащий регист т результата и блок вьиисления последующего кода, регистр результата выполнен на счетных триггерах, входтриггера младшего разряда является входом счетчика, выходы счетных триггеров являются выходами счетчика, выходы всех триггеров, за исключением выхода триггера старшего разряда, соединены с входами блока вычисления последующего кода, вьтолненного на двухвходовых элементах И по схеме группового переноса 3. Недостатком этого двоичного счетчика является большое время регистрации. Цель изобретения - уменьшение времени регистрации счетчика. Поставленная цель достигается тем, что в двоичном счетчике, содержащем первьй регистр результата, выходы которого являются выходами счетчика, а вход младшего разряда, выполненного в виде счетного триггера,- входом счетчика, и первый блок вычисления последующего кода, выходы которого соединены с входами всех разрядов первого регистра результата, кроме входа младшего разряда, прямой выход триггера мпадшего разряда первого регистра результата соединен с управляющим входом первого блока вычисления последующего кода, первый регистр результата во всех разрядах, кроме младшего, вьтолнен в виде параллельного регистра, синхронизирующий вход которого соединен с инверсным выходом счетного триггера младшего разряда первого регистра результата, первьй блок вычисления последующего кода содержит второй регистр результата, младшие разряды которого выполнены в виде группы счетных триггеров, которые соединены последовательно, а старшие разряды - в виде параллельного регистра, выходы вто3рого регистра результата являются выходами первого блока вычисления последующего кода, а вход младшего разряда второго регистра результата управляющим входом первого блока вы числения последующего кода, второй блок вычисления последующего кода, выходы которого соединены с. входами старших разрядов второго регистра результата, прямой выход триггера старшего разряда группы счетных три геров второго регистра результата соединен с управляющим входом второ го блока вычисления последующего кода, инверсный выход триггера стар шего разряда группы счетных триггеров второго регистра результата соединен . с синхронизирующим входом параллельного регистра старших разрядов второго регистра результата, последующий К-й блок вычисления последующего кода, который содержит (К+1)-й регистр результата, младшие разряды которого выполнены в виде последовательно соединенной группы счетных триггеров, а старшие разряды - в виде параллельного регистра, выходы (K+D-ro регистра результата являются выходами К-го блока вычисления последующего кода, а вход младшего разрядаСК+1)-го регистра результата - управляющим входом К-г блока вьмисления последующего кода, (К+1)-й блок вычисления последующег кода, выходы которого соединены с входами параллельного регистра стар ших разрядов (К+1)-го регистра результата, прямой выход триггера ста шего разряда группы счетных триггеров, которые соединены последовател но, (К+1)-го регистра результата соединен с управляющим входом (К+1) го блока вычисления последующего кода, инверсньй выход триггера старшего разряда группы мпадших разрядов (К+1)-го регистра результата соединен с синхронизирующим эходом, параллельного регистра старших разрядов (К+1)-го регистра результата. На фиг.1 и 2 представлены примеры вьшолнения предлагаемого двоичного счетчика; на фиг.З - пример вы полнения последовательного счетчика на В -триггерах; на фиг.4 - временная диаграмма работы двоичного счетчика. Двоичный счетчик (фиг.1) содержи первый регистр 1 результата, выходы 584 2 которого являются выходами счетчика, а вход 3 младшего разряда, выполненного на счетном триггере 4,входом счетчика. Устройство содержит также первьй блок 5 вычисления последующего кода, выходы которого соединены с входами всех разрядов регистра 1, кроме входа 3 младшего разряда. Выход прямого плеча триггеpa 4 соединен с управляющим входом 6 блока 5. Регистр 1 результата во всех разрядах, кроме младшего, выполнен в виде параллельного регистра 7, синхронизирукщий вход 8 которого соединен с выходом нулевого плеча триггера 4. Блок 5 содержит второй регистр результата 9, выходы которого являются выходами блока 5, а вход младшего разряда 10 группы счетных триггеров регистра 11, которые соединены последовательно - входом 6 блока 5. Блок 5 содержит второй блок 12 вычисления последующего кода, ьыхбды которого соединены с входами всех разрядов регистра 9, кроме входов группы 11 счетных триггеров этого регистра. Прямой выход триггера 13 старшего разряда группы регистра 11 соединен с управляющим входом 14 блока 12. Инверсньй выход триггера 13 соединен с синхронизирующим входом 15 параллельного регистра 16 остальных разрядов регистра 9. Блок 12 содержит третий регистр результата 17, выходы которого являются выходами блока 12, а вход младшего разряда 18 группы 19 счетнь1х триггеров этого регистра, которые соединены последовательно,- входом 14 блока 12. Блок 12 содержит третий блок вычисления последующего кода, вьтолненный по схеме счетчика 20 с последовательным переносом, выкоды которого соединены с входами всех разрядов регистра 17, кроме входа последовательно соединенной груп- пы 19 счетных триггеров этого регистра. Прямой выход триггера старшего разряда 21 группы 19 соединен со счетным входом 22 счетчиг а 20. Инверсный выход триггера 21 соединен с синхронизирующим; входом 23 параллельного регистра 24 остальных разрядов регистра 17. Счетчик (фиг.2) содержит счетные триггеры 25, 26 и 27, последовательый двухзарядный счетчик 28 и регистры с параплельньм приемом информации 29, 30 и 31. Инверсные выходы триггеров 25, 26 и 27 соединены с входами синхронизации регистров 29, 30 и 31. Прямой выход триггера 25 соединен со счетным входом триггера 26, прямой выход которого соединен со счетным входом триггера 27 и с входом младшего регистра 29. Пряной выход триггера 27 соединен со счетным входом счетчи-О

ка 28 и с входом младшего разряда регистра 30. Счетчик 28 и регистры 31, 30 и 29 соединены последовательно, выход триггера 25 и выходы регистра 29 ЯВЛ5ПОТСЯ выходами счетчика.

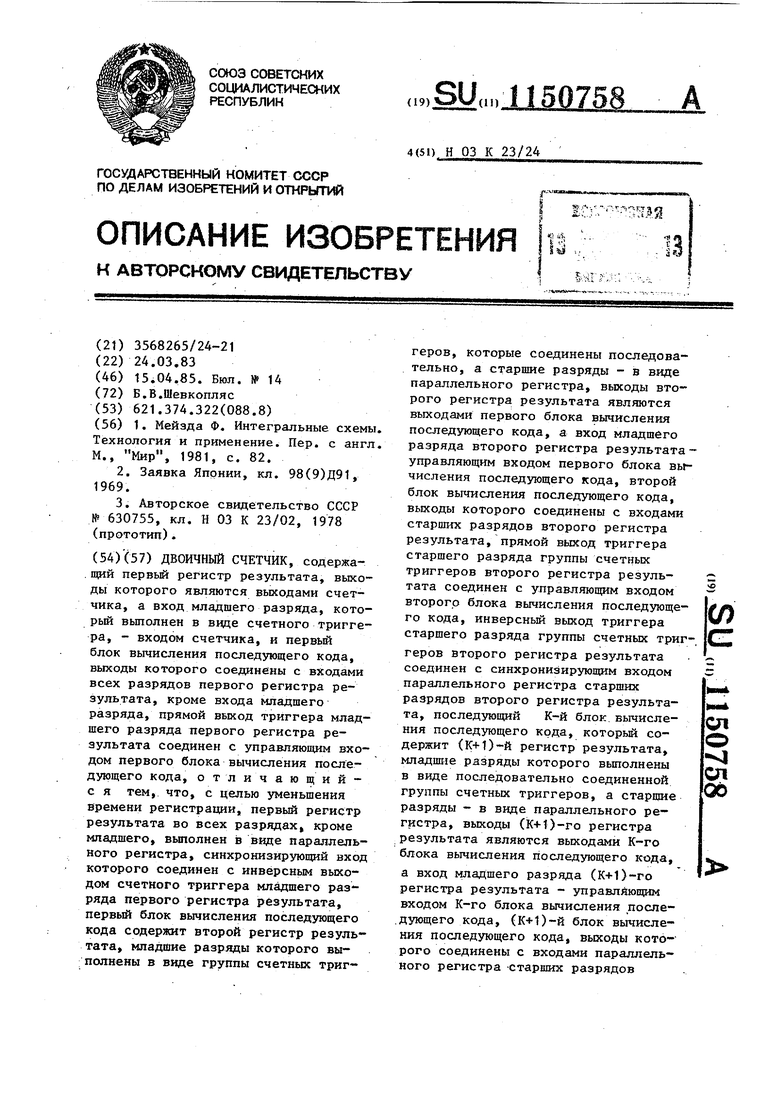

На фиг.З показан пример выполнения группы 19 счетных триггеров в виде группы D -триггеров 32, которые соединены похгпедовательно, в каждом из которых инверсный выход соединен с D-входом и с входом синхронизации триггера следующего разряда.

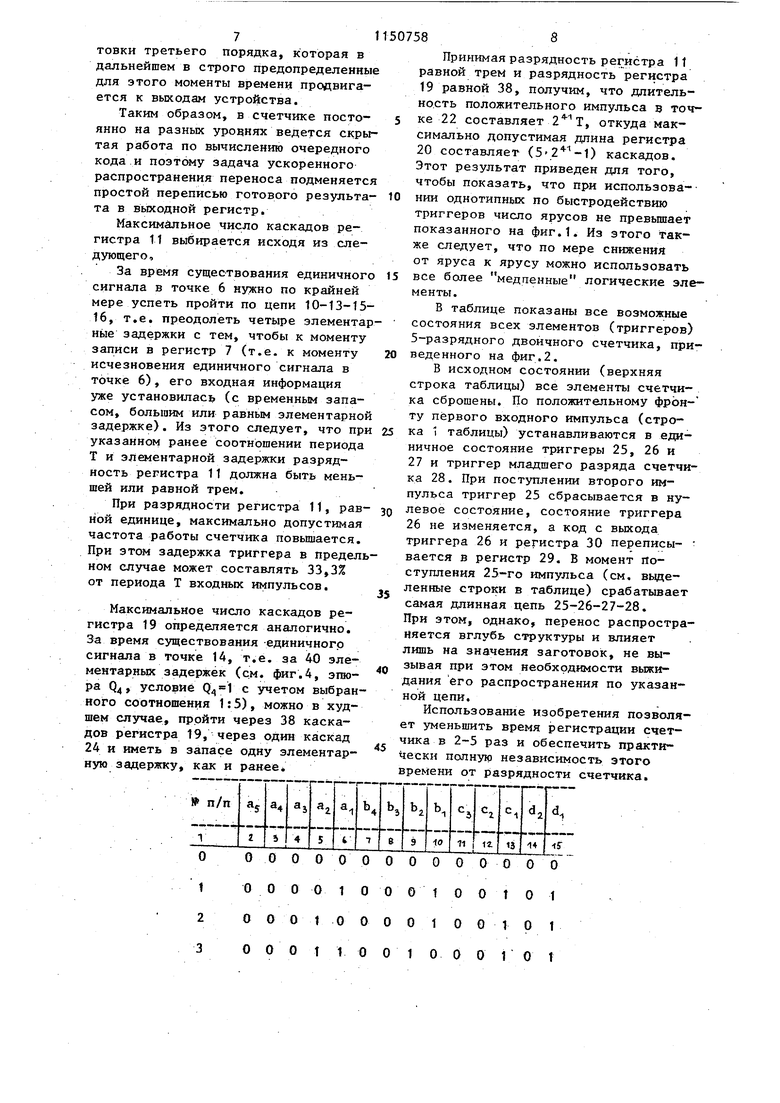

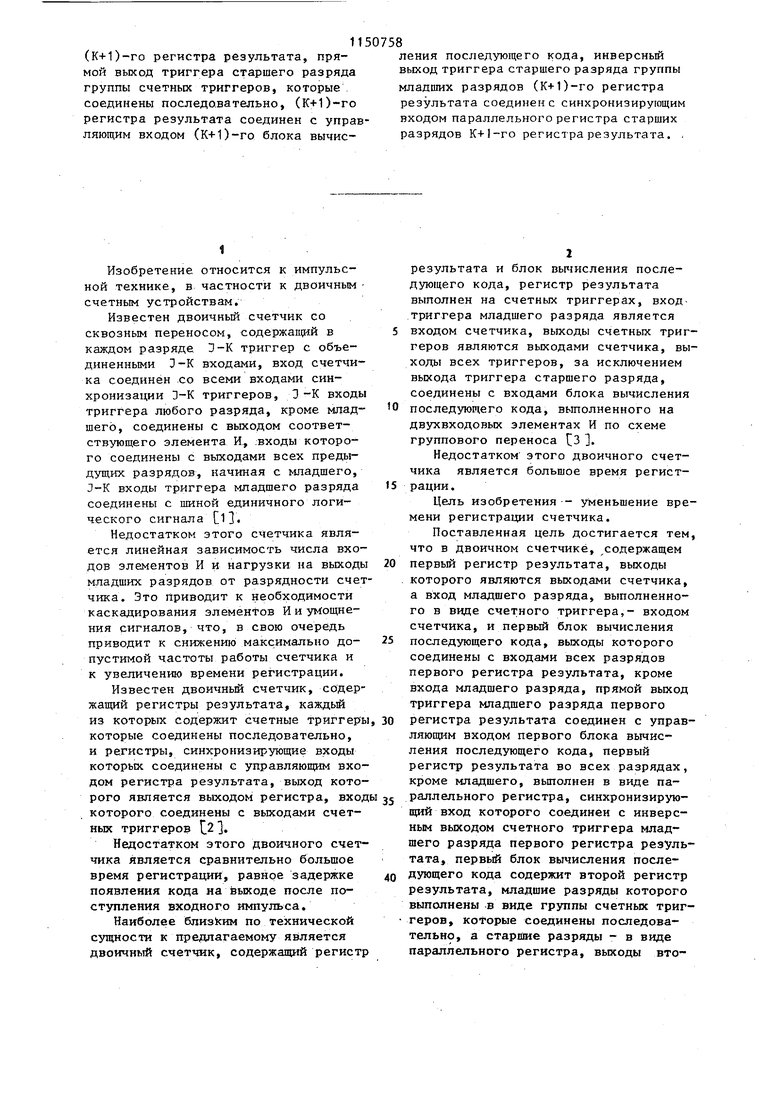

На фиг.4 приведены временные диаграммы, поясняющие работу счетчика, показанного на фиг.1. Эпюры 33-43 соответствуют входному сигналу f и сигналам в точках Q -Q схемы, приведенной на фиг,1.

Работа Счетчика основана на предварительном формировании заготовок последующих кодов и дальнейшем их использовании при возникновении условий переноса. Эти заготовки формируются в свободное время и поэтому задержка распространения переноса скрыта от пользователя. Время между положительным фронтом сигнала на входе счетчика 3 и моментом установления кода на всех его выходах 2 равно двум задержкам триггера и не зависит ни от текущей кодовой комбинации, ни от числа разрядов счетчика.

Пусть в исходном состоянии все триггеры, входящие в состав устройства (т.е. все разряды всех его регистров и внутренних счетчиков), находятся в нулевом состоянии (цепи сброса на фиг.1 не показаны). Предположим, что задержка срабатывания любого триггера составляет 20% от длительности периода Т входных импульсов, поступающих на вход 3. Это предположение соответствует наиболее тяжелому режиму работы счетчика данной конфигурации (фиг.1). Максимально допустимая частота повышается с уменьшением разрядности счетного регистра при правильном выборе разрядности счетчика.

При поступлении на вход 3 первого импульса на выходе Q триггера 4 формируется сигнал логической единицы (с элементарной задержкой, равной одной пятой части периода Т). Положительный фронт сигнала в точке

стояние, подготавливая тем самым заготовку последующего кода 2 в регистре 9. При окончан ш входного импульса состояние устройства не изменяется.

При поступлении на вход 3 второго импульса триггер 4 возвращается в нулевое состояние, при этом на входе 8 регистра 7 формируется сигнал логической единицы. Положительный фронт сигнала на входе 8 производит перепись заранее подготовленного кода из блока 5 в регистр 7. Состояние триггеров блока 5 в это время является стабильным, что исключает гонки. Таким образом, на выходы 2 подается код 2, что и требуется. Задержка формирования этого кода относительно начала второго импульса на входе 3 определяется суммой задержек триггера 4 и триггера соседнего разряда регистра 7 (ПУТЬ 3-4-10 пройден заранее при воздействии на вход 3 первого импульса, когда необходимости в переносе еще не было).

При поступлении на вход 3 третьего импульса на выходе Q вновь формируется сигнал логической единицы, а в счетном регистре формируется код 010 - заготовка для числа 4, которая переписывается в регистр 7 при поступлении на вход 3 четвертого импульса и т.д.

При поступлении на вход 3 седьмого импульса, как видно из диаграммы (фиг.4), срабатывает цепочка 3-4-1013-18, в результате чего в регистре 17 формируется заготовка второго порядка для числа 16, которая в нужные моменты времени передается в регистр 9, а затем через две элементарные задержки от начала 16-го импульса - на выходы 2 счетчика.

3

При поступлении логической единицы с выхода прямого плеча триггера 21 на вход 22 счетного регистра в нем производится вычисление новой заго6 переводит триггер в единичное со7

тонки третьего порядка, которая в дальнейшем в строго предопределенные для этого моменты времени продвигается к выходам устройства.

Таким образом, в счетчике постоянно на разных уровнях ведется скрытая работа по вычислению очередного кода и поэтому задача ускоренного распространения переноса подменяется простой переписью готового результата в выходной регистр.

Максимальное число каскадов регистра 11 выбирается исходя из следующего,

За время существования единичного сигнала в точке 6 нужно по крайней мере успеть пройти по цепи 10-13-15- 16, т.е. преодолеть четыре элементарные задержки с тем, чтобы к моменту записи в регистр 7 (т.е. к моменту исчезновения единичного сигнала в точке 6), его входная информация уже установилась (с временным запасом, большим или равным элементарной задержке). Из этого следует, что при указанном ранее соотношении периода Т и элементарной задержки разрядность регистра 11 должна быть меньшей или равной трем.

При разрядности регистра 11, равной единице, максимально допустимая частота работы счетчика повышается. При этом задержка триггера в предельном случае может составлять 33,3% от периода Т входных импульсов.

Максимальное число каскадов регистра 19 определяется аналогично, За время существования единичного сигнала в точке 14, т.е. за 40 элементарньк задержек (с.м. фиг.4, эпюра Рд, условие Qi) 1 с учетом выбранного соотношения 1:5), можно в худшем случае, пройти через 38 каскадов регистра 19, через один каскад 24 и иметь в запасе одну элементарную задержку, как и ранее

00 о сор о о о о 00 00

00001000100101

00010000100101

о о о т 1 о о 1 о о о 1 о 1

50738S

Принимая разрядность регистра 11 равной трем и разрядность регистра

19равной 38, получим, что дпительно.сть положительного импульса s точке 22 составляет , откуда максимально допустимая длина регистра

20составляет (52-1) каскадов. Этот результат приведен для того, чтобы показать, что при использова-НИИ однотипньк по быстродействию триггеров число ярусов не превьшгает показанного на фиг.1. Из этого также следует, что по мере снижения

от яруса к ярусу можно использовать все более медпенные логические элементы.

В таблице показаны все возможные состояния всех элементов (триггеров) 5-разрядного двоичного счетчика, приведенного на фиг.2.

В исходном состоянии (верхняя строка таблицы) все элементы счетчика сброшены. По положительному фронту первого входного импульса (строка 1 таблицы) устанавливаются в единичное состояние триггеры 25, 26 и 27 и триггер младшего разряда счетчика 28. При поступлении второго импульса триггер 25 сбрасывается в нулевое состояние, состояние триггера 26 не изменяется, а код с выхода триггера 26 и регистра 30 переписы- вается в регистр 29. В момент поступления 25-го импульса (см. вьщеленные строки в таблице) срабатывает самая длинная цепь 25-26-27-28. При этом, однако, перенос распространяется вглубь структуры и влияет лишь на значения заготовок, не вызывая при этом необходимости выжидания его распространения по указанной цепи.

Использование изобретения позволяет уменьшить время регистрации счетчика в 2-5 раз и обеспечить практически полную независимость этого времени от разрядности счетчика.

If

-vfeyfrN -frhi-4-l-+H-f-f-l--

rr .

гм

l I 1-H И

f

L

-/1

t

I i Ii LH

I

22

MI I1 I г.

Os

I.

. 3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Мейзда Ф | |||

| Интегральные схемы | |||

| Технология и применение | |||

| Пер | |||

| с англ | |||

| М., Мир, 1981, с | |||

| Машина для разделения сыпучих материалов и размещения их в приемники | 0 |

|

SU82A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

Авторы

Даты

1985-04-15—Публикация

1983-03-24—Подача