мента И, второй выход - с первым входом первого элемента И, третий выход соединен с входом дешифратора, первый выход которого соединен с первым входом первого элемента ИЛИ, вторые выходы дешифратора соединены с первыми входами элементов И, объединенных в группу, выходы .которых соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с входом элемента НЕ, первый информационный канал, содержащий элементы И, регистр, дешифратор, группа элементов И, элемент ИЛИ и элемент НЕ, выход первого элемента И соединен с выходом регистра, йервый выход которого соединен с первым входом второго элемента И, второ выход подключен к первому входу первого элемента И, третий выход регистра соединен с входом дешифратора, первый выход которого соединен с первым входом элемента ИЛИ, второй выход дешифратора соединен с первыми входами элементов И, объединенных в группу, выходы которых соединены с вторыми входами элемента ИЛИ, выход которого соединен с входо элемента НЕ и вторым входом третьего элемента И, последний информационный канал содержит элементы И, регистр, дешифратор, выход первого элемента И соединен с входом регистра, первый выход которого соединен с первым входом второго элемента И, второй выход - с первым входом первого элемента И, третий с входом дешифратора, второй вход первого элемента И каждого информационного канала является соответствующим входом блока приоритетного ввода сообщений, выход элемента ИЛИ первого информационного канала соединен с вторым входом второго элемента ИЛИ второго информационного канала, выход второго элемента ИЛИ каждого информационного канала, кроме последнего, соединен с вторым входом второго элемента .ИЛИ последующего информационного канала, выход элемента НЕ каждого информационного канала, кроме последнего, соединен с вторым входом второго элемента И последнего информационного канала, выходы вторых элементов И всех информационных каналов, кроме последнего, и выход второго элемента И последнего информационного канала являются соответствующими выходами блока приоритетного ввода сообщений, первый и вторые выходы дешифратора всех информационных каналов соединены с соответствующими первыми входами соответствующих элементов ИЛИ, выход элемента ИЛИ каждого предьщущего информационного канала соединен с вторым входом элемента ИЛИ каждого последующего информационного канала и через соответствующий элемент НЕ соединен с вторыми входами соответствующих элементов И объединенных в группу каждого информационного канала, кроме последнего.

3. Коммутатор по п. 1, отличающийся тем, что, узел управления содержит блок фиксации вводимых сообщений, элемент ИЛИ, группу последовательно соединенных элементов ИЛИ,первую и вторую группу элементов И, группу элементов НЕ, блоки управления ячейкой памяти, генераторы тактовых импульсов, первый выход первого генератора тактовых импульсов подключен к первому входу блока фиксации вводимых сообщений, выходы которого подключены к соответствующим первым объединенным входам блоков управления ячейкой памяти, вторые и третьи входы которых соответственно объединены и подключены к второму и третьему вьрсодам первого генератора тактовых импульсов, четвертый выход которого соединен с объединенными первыми входами первых элементов И, первый выход второго генератора тактовых импульсов подключен к объединенным четвертым входам блоков управления ячейкой памяти, второй выход подключен к объединенным пятым входам блоков управления ячейкой памяти и к второму входу блока фиксации вводимых сообщений, первые выходы блоков управления соединены с соответствующими входами первого элемента ИЛИ, первый выход первого блока управления ячейкой памяти соединен с вторым входом первого элемента И первой группы, шестым входом первого блока управления ячейкой памяти и входом первого элемента НЕ группы и первым входом элемента ИЛИ группы, первый выход остальных блоков управления ячейкой памяти подключен первым входам соответствующих элеентов И второй группы и вторым входам соответствующих элементов ИЛИ группы, выходы которых соединены через соответствующий элемент НЕ группы с вторыми входами соответствующих элементов НЕ второй группы, выходы которых подключены к шестым входам соответствующих блоков управления ячейкой памяти и вторым входам соответствующих элементов И первой группы, выходы элементов И первой группы и выходы блоков управления ячейкой памяти являются соответственно первым, вторым и третьим выходами узла управления, третьи входы блока фиксации вводимых сообщений, вход первого генератора тактовых импульсов и вход второго генератора тактовых импульсов являются соответственно первыми, вторыми и третьими входами узла управления.

4. Коммутатор по п. 3, отличающийся тем, что блок фиксации вводимых сообщений содержит дешифраторы, реверсивные счетчики, группы элементов И, группы элементов ИЛИ, группы элементов НЕ, выход первого элемента И первой группы соединен с первым входом первого счетчика и первым входом первого элемента ИЛИ первой группы, выход каждого предыдущего элемента ИЛИ первой группы соединен с первым входом последующего элемента ИЛИ первой группы и первым входом соответствующего реверсивного счетчика, выходы остальных элементов И первой группы соединены с вторыми входами соответствующих элементов ИЛИ первой группы, выходы реверсивного счетчика соединены с входами соответствующих дешифраторов, первые выходы которых соединены с соответствующими первыми входами соответствующих элементов И второй группы, выходы элементов И второй группы соответственно соединены с первыми входами соответствующих элементов ИЛИ второй группы, выход каждого элемента ИЛИ второй группы, кроме последнего, соединен с вторыми входами последующего элемента ИЛИ второй группы, второй выход каждого дешифратора через соответствующий элемент НЕ соединен с первым входом соответствующего элемента И третьей группы, выход которого соединен с вторым входом соответствующего реверсивного счетчика, второй вход первого элемента ИЛИ второй

10

/

группы и выходы всех элементов ИЛИ второй группы являются соответствующими выходами блока фиксации вводимых сообщений, объединенные первые входы элементов И первой группы, объдиненные вторые входы элементов И третьей группы и соответственно объединенные вторые входы элементов И первой и второй групп являются соответственно первым, вторым и третьими входами блока фиксащ1И вводимых сообщений.

5. Коммутатор по п. 3, отличающийся тем, что каждый блок управления ячейкой памяти содержит триггер, генератор импульсов, элементы ИЛИ, элемент НЕ, реверсивный счетчик, дешифратор, элементы И, группу элементов И, выход первого элемента И подключен к первому входу триггера, выход которого подключен к первому входу второго элемента И, второй вход которого подключен к выходу генератора импульсов, выход второго элемента И подключен к первому входу первого элемента ИЛИ, выход которого подключен к первому входу реверсивного счетчика, выходы которого подключены к входам дешифратора, первый выход дешифратора подключен через элемент НЕ к первому входу третьего элемента И, вькод которого подключен к второму входу реверсивного счетчика, остальные выходы дешифратора подключены к первым входам соответствующих элементов И группы, выходы элементов И группы подключены к соответствующим входам второго элемента ИЛИ, выходы которого подключены к второму входу триггера и первому входу четвертого элемента И, второй выход дешифратора подключен к первому входу пятого элемента И, вторые входы .элементов И группы, второй вход четвертого элемента И, первый вход первого элемента И, второй вход пятого элемента И, второй вход третьего элемента И и второй вход первого элемента И подключены соответственно к первому, второму, третьему, четвертому, пятому и шестому вводам блока управления ячейкой,памяти, перьый выход дешифратора и выход пятого элемента И подключены соответственно к первому и второму выходам блока управления ячейкой памяти.

Изобретение относится к устройствам техники связи, а именно к аппаратуре передачи данных.

Известны коммутаторы сообщений, содержащие накопители информации, блоки управления кoм fyтaциeй, распределительные устройства, логические схемы переключения t13 и .

Известные устройства характеризуются большой величиной среднего времени задержки сообщений высших категорий срочности при передаче неод- нородных по категориям срочности сообщений по параллельным каналам передачи разной производительности.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее источники-информации, блок предварительной коммутации, элемент ИЛИ, элементы И,.блок управления коммутацией, общий накопитель, блок ввода пороговых значений, канальные накопители, блок выбора свободного канала и соответствующие связи Сз 3Недостатком данного устройства является большая величина среднего времени задержки сообщений высших категорий срочности при передаче неоднородных по категориям срочности сообщений по параллельным каналам передачи разной производительности.

Цель изобретения - повышение быстродействия многоканального коммутатора.

Поставленная цель достигается тем, что в многоканальный коммутатор содержащий элемент ИЛИ, вьгход которого подключен к первому входу первого элемента И, второй элемент И,выход которого подключен к первому входу блока управления коммутацией, вторые входы которого подключены к соответствующим выходам блока задания пороговых значений, первые выходы блока управления коммутацией подключены к первым выходам соответствующи третьих элементов И, вторые входы которых объединены и подключены к выходу блока памяти, выходы третьих элементов И подключены к выходам соответствующих элементов памяти, первые выходы которых через блок выбора свободного канала подключены к третьим выходам блока управления коммутацией, вторые выходы элементов памят являются выходами многоканального коммутатора, введены узел управления, дешифратор, четвертый элемент И буферный регистр, элемент НЕ, блок приоритетного ввода сообщений, входы которого являются информационными входами устройства, выходы блока приоритетного ввода сообщения подключены к входам элемента ИЛИ, первый выход буферного регистра подключен через элемент НЕ к первым входам второго и четвертого элемента И и непосредственно к второму входу первого элемента И, выход которого подключен к входу буферного регистра, второй выход которого подключен к второму входу четвертого элемента И, выход которого через дешифратор подключен к первым входам узла управления, первый выход которого соединен с вторым входом второго элемента И, второй и третий выходы узла управления соединены с первым и вторым входами блока памяти, второй вход которого подключен к третьему выходу буферного регистра, второй и третий выходы блока управления коммутацией соединены соответственно с вторым и третьим входами узла управления.

Q Блок приоритетного ввода сообщений содержит элементы ИЛИ, элементы НЕ и информационные каналы в каждом из которых, кроме первого и последнего содержатся первый и второй элементы И, регистр, дешифратор, группа элементов И, первый и второй элементы ИЛИ и элемент НЕ, выход первого элемента И соединен с первым входом регистра первый выход

которого соединен с первым входом второго элемента И, второй выход с первым входом первого элемента И, третий выход соединен с входом дешифратора, первый выход которого соединен с первым входом первого элемента ИЛИ, вторые выходы дешифратора соединены с первыми входами элементов И, объединенных в группу, выходы которых соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с входом элемента НЕ, первый информационный канал, содержащий элементы И, регистр, дешифратор, группу элементов И, элемент ИЛИ и элемент НЕ, выход первого элемента соединен с выходом регистра, перJ10вый выход которого соединен с первым входом второго элемента И, второй выход подключен к первому входу первого элемента И, третий выход регистра соединен с входом дешифратора, первый выход которого соединен с первым входом элемента ИЛИ, второй выход дешифратора соединен с первыми входами элементов И, объединенных в группу, выходы которых соединены с вторыми входами элемента ИЛИ, выход которого соединен с входом элемента НЕ и вторым входом третьего элемента И, последний информационньй канал содержит злементы И, регистр, дешифратор, вьрсод первого элемента И соединен с входом регистра, первый выход которого соединен с первым входом второго элемента И, второй выход - с первым входом первого элемента И, третий выход с входом дешифратора, второй вход первого элемента И каждого информационного канала является соответствующим входом блока приоритетного .ввода сообщений, выход элемента ИЛИ первого информационного канала соединен с вторым входом второго элемента ИЛИ второго информационного канала, выход второго элемента ИЛИ каждого информационного кана ла, кроме последнего, соединен с вторым входом второго элемента ИЛИ последующего информационного канала выход элемента НЕ каждого информа ционного канала-, кроме последнего, соединен с вторым входом второго элемента И последнего информационно канала, выходы вторых.элементов И всех информационных канашов, кроме последнего, и выход второго элемента И последнего информационного канала являются соответствующими выхо дами блока приоритетного ввода сооб щений, первый и вторые выходы дещифратора всех информационных.каналов соединены с соответствующими первыми входами соответствующих эл ментов ИЛИ, выход элемента ИЛИ каж дого предьщущего информационного кана ла соединен с вторым входом элемента И каждого последующего информационного канала и через соответствующий элемен НЕ соединен с вторыми входами соответствуклцих элементов И, объединенных в группу каждого информаи юнного канала кроме последнего. Узел управления содержит блок фи сации вводимых сообщений, элемент ИЛИ, группу последовательно соединенных элементов ИЛИ, первую и вторую группу элементов И, группу элементов НЕ, блоки управления ячейкой памяти, генераторы тактовых импульсов, первый выход первого генератора тактовых импульсов подключены к первому входу блока фиксации вводимых сообщений, выходы которого подключены к соответствующим первым объединенным входам блоков управления ячейкой памяти, вторые и третьи входы которого соответственно объединены и подключены к второму и третьему выходам первого генератора тактовых импульсов, четвертый выход которо- , го соединен с объединенными первыми входами первых элементов И, первый выход второго генератора тактовых импульсов подключен к объединенным четвертым входам блоков управления ячейкой памяти, второй выход подключен к объединённым пятым входам блоков управления ячейкой памяти и. к второму входу блока фиксации вводимых сообщений, первые выходы блоков управления соединены с .соответствующими входами первого элемента ИЛИ, первый выход первого блока управления ячейкой памяти соединен с вторым входом первого элемента И первой группы, шестым входом первого блока управления ячейкой памяти, входом первого элемента НЕ группы и первым входом элемента ИЛИ группы, первый выход остальных блоков управления ячейкой памяти подключен к первым входам соответствующих элементов И второй группы и вторым входам соответствующих элементов ИЛИ группы, выходы которых соединены через соответствующий элемент НЕ группы с вто рыми входами соответствующих элементов НЕ второй группы, выходы которых подключены к шестым входам соответствующих блоков управления ячейкой памяти и вторым входам соответствующих элементов И первой группы, выходы элементов И первой группы и выходы блоков управления ячейкой памяти являются соответственно первым, вторым и третьим выходами узла управления, третьи входы блока фиксации вводимых сообщений, вход первого генератора тактовых импульсов и вход второго генератора тактовых импульсов являются соответственно первыми, вторыми и третьими входами узла управления.

Блок фиксации вводимых сообщений содержит дешифраторы, реверсивные счетчики, группы элементов И, группы элементов ИЛИ, группы элементов НЕ, выход первого элемента И первой группы соединен с первым входом первого счетчика и первым входом первого элемента ИЛИ первой группы, выход каждого предьщуще-го элемента ИЛИ первой группы соединен с первым входом последующег элемента ИЛИ первой группы и первым входом соответствующего реверсивного счетчика, выходы остальных элементов И первой группы соединены с вторыми входами соответствующих .элементов ИЛИ первой группы., выходы реверсивного счетчика соединены с входами соответствующих дешифраторов первые выходы которых соединены с соответствующими первыми входами соответствующих элементов И второй группы, вькоды элементов И второй группы соответственно соединены с первыми входами соответствующих элементов ИЛИ второй группы, выход каждого элемента ИЛИ второй группы, кроме последнего, соединен с вторыми входами последующего элемента ИЛИ второй группы, второй выход каждого дешифратора через соответствующий элемент НЕ соединен с первым входом соответствующего элемента И третьей группы, выход которого соединен с вторым входом соответствующего реверсивного учетчика, второй вход первого элемента ИЛИ второй группы и выходы всех элементов ИЛИ второй группы являются соответствующими выходами блокафиксащш вводи мых сообщений, объединенные первые входы элементов И первой группы, объединенные вторые входы элементов И третьей группы и соответственно объединенные вторые входы элементов И первой и второй группы являются соответственно первым, вторым и третьими входами блока фиксации вводимых сообщений.

т,

Блок управления ячейкой памяти

содержит триггер, генератор импyль сов, элементы ИЛИ, элемент НЕ, реверсивный счетчик, дешифратор, элементы И, группы элементов;. И, выход первого элемента И подключен к первог му входу триггера, выход которого подключен к первому входу второго элемента И, второй вход которого подключен к выходу генератора импульсов, выход второго элемента И подключен к первому входу первого элемента ИЛИ выход которого подключен к первому входу реверсивного счетчика, выходы которого подключены к входам дешифратора, первый выход дешифратора подключен череэ элемент НЕ к первому входу третьего элемента И, выход которого подключен к второму входу реверсивного счетчика, остальные выходы дешифратора подключены к первым входам соответствующих элементов И группы, выходы элементов И группы подключены к соответствующим входам второго элемента ИЛИ, выходы которого подключены к второму входу триггера и первому входу четвертого элемента И, второй выход дешифратора подключен к первому входу пятого элемента И, вторые входы третьих элементов И группы, второй вход четвертого элемента И, первьш вход первого элемента И, второй вход пятого элемента И, второй вход третьего элемента И и второй вход первого элемента И подключены соответственно к первому, второму, третьему, четвертому, пятому и шестому входам блока управления ячейкой памяти, первый выход дешифратора и выход пятого элемента И подключены соответственно к первому и второму выходам блока управления ячейкой памяти.

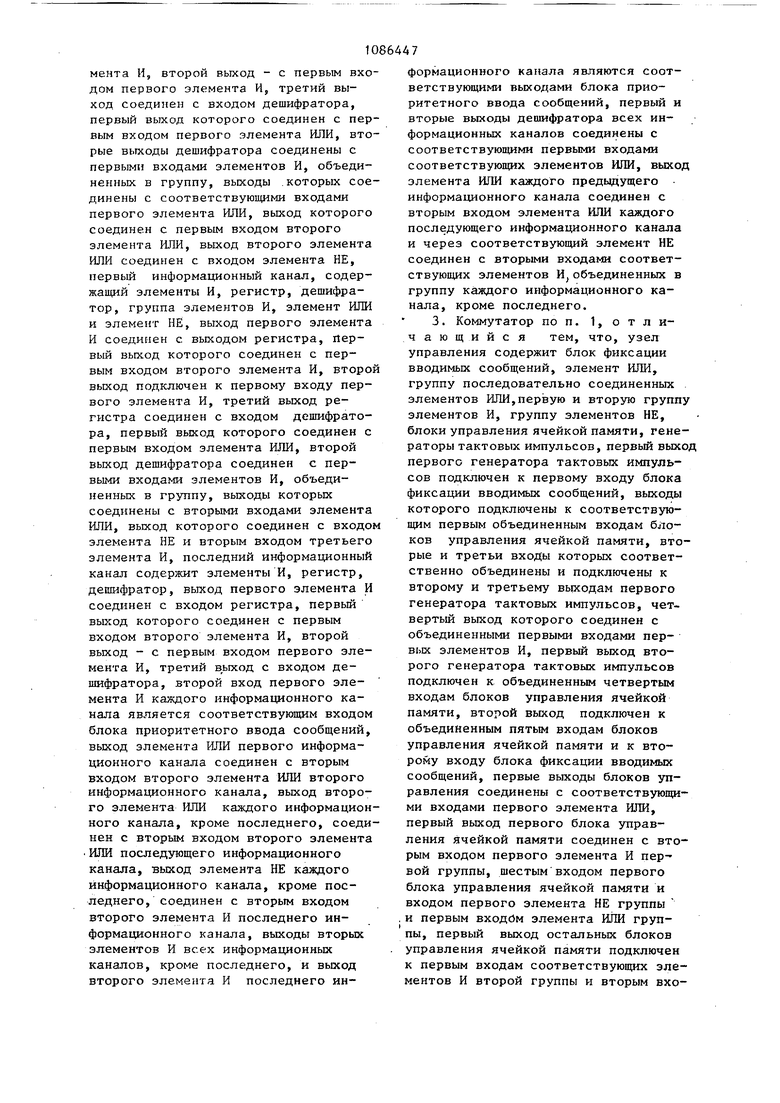

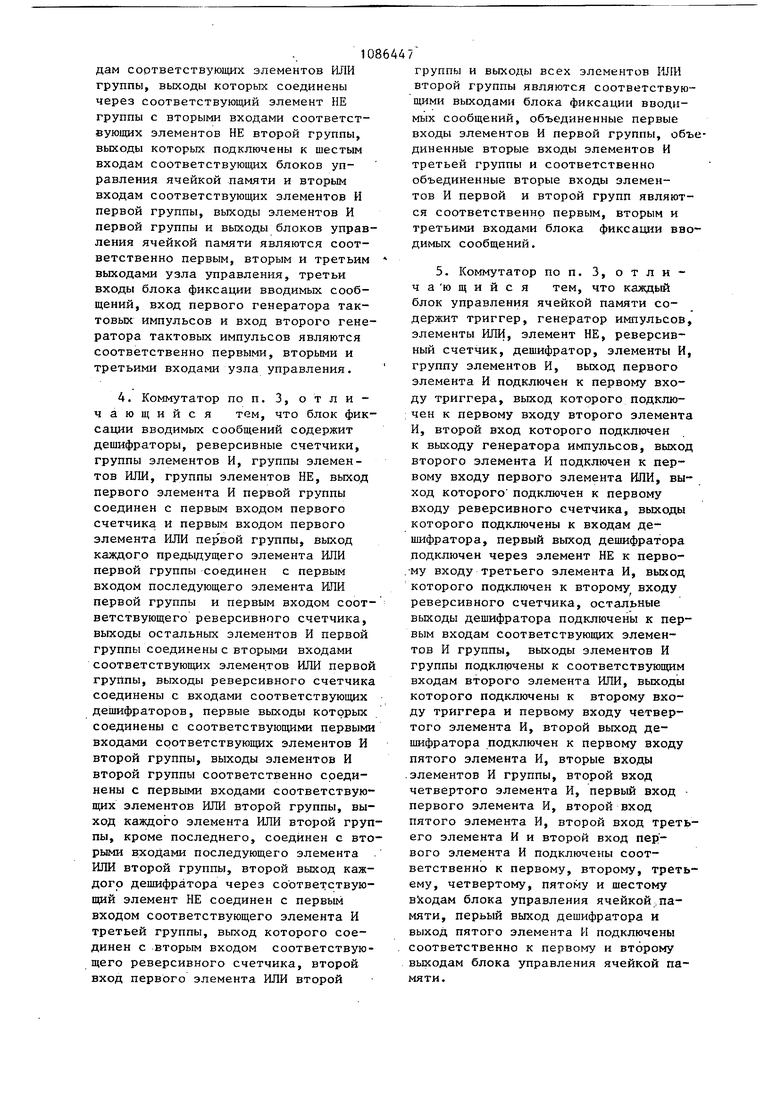

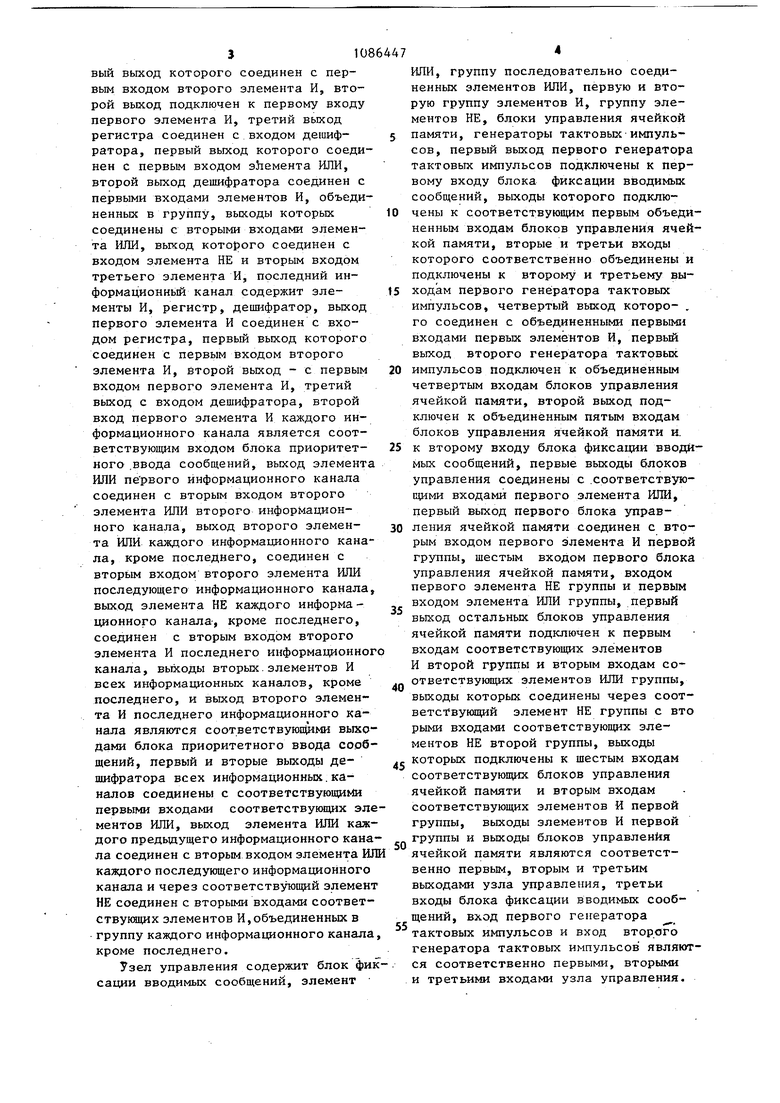

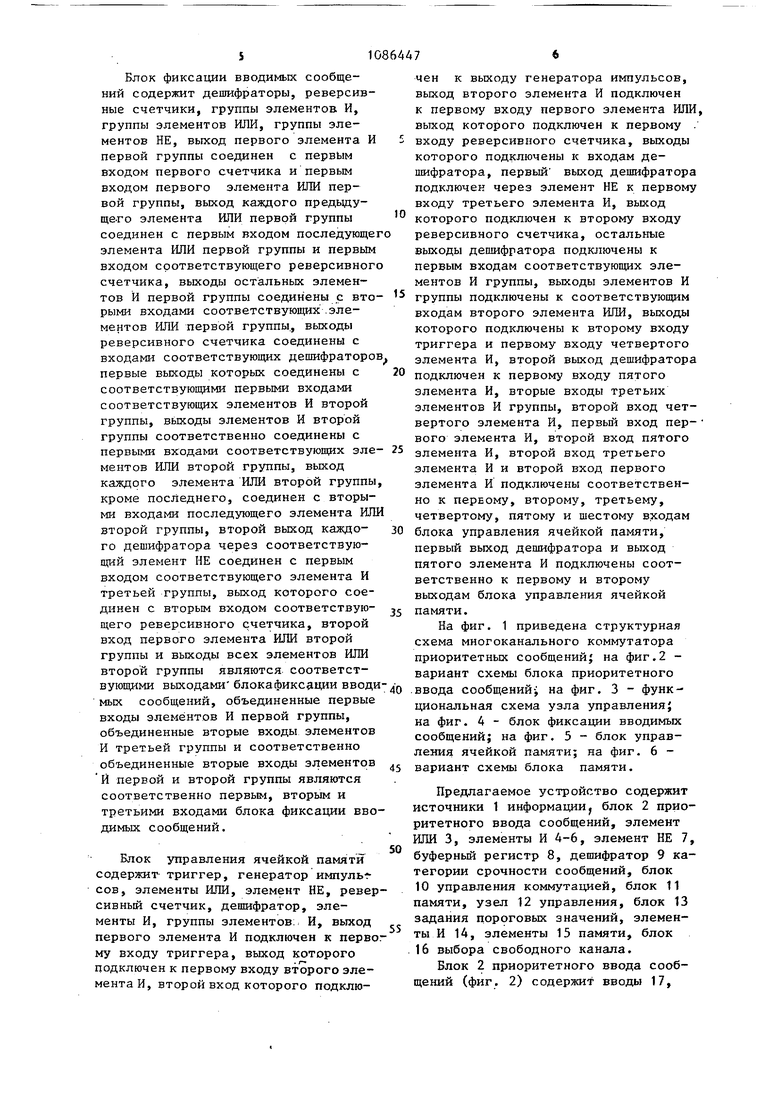

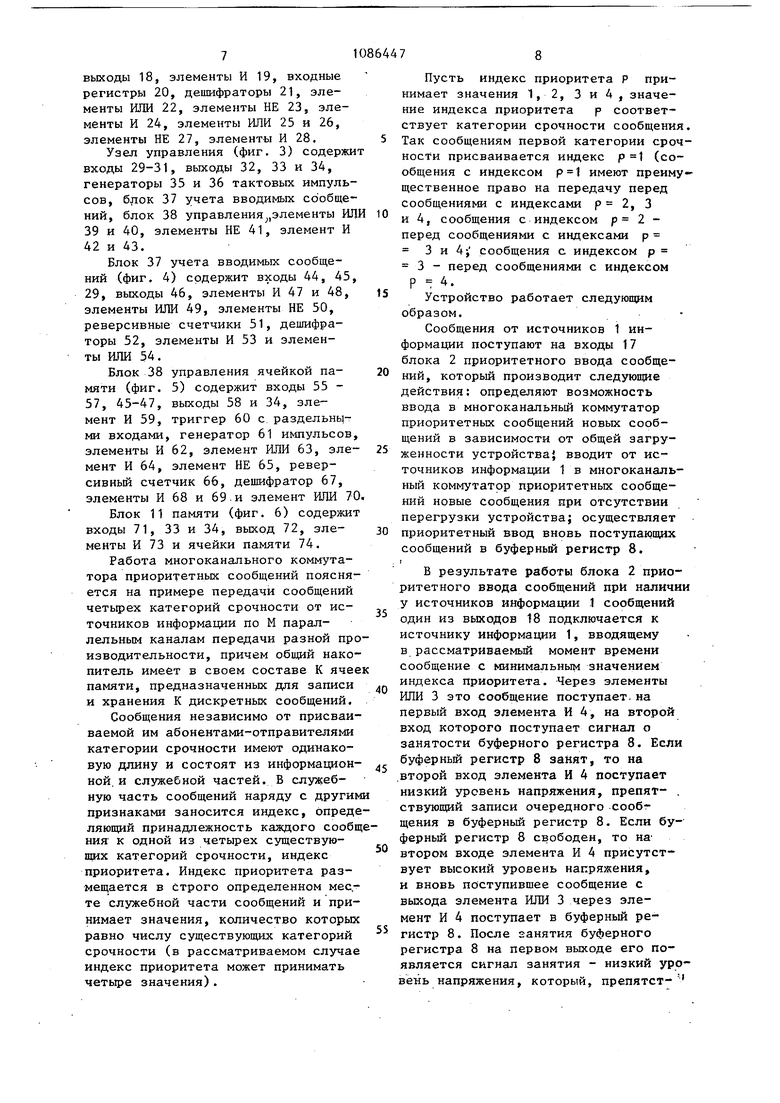

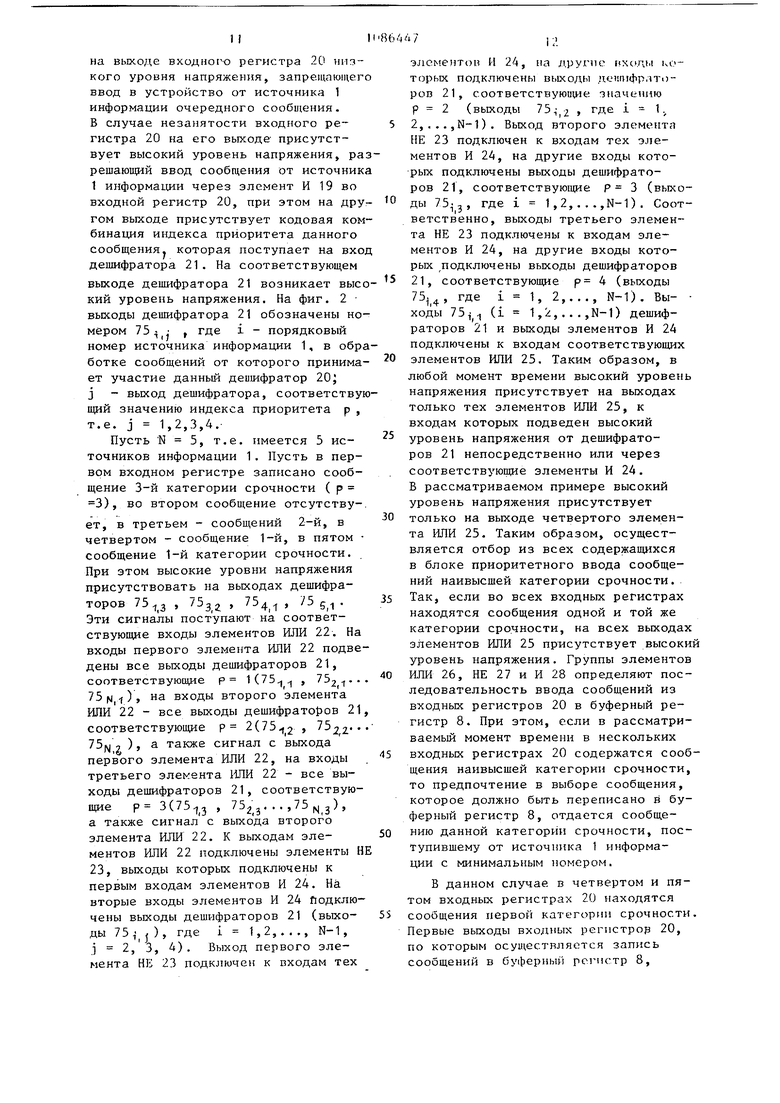

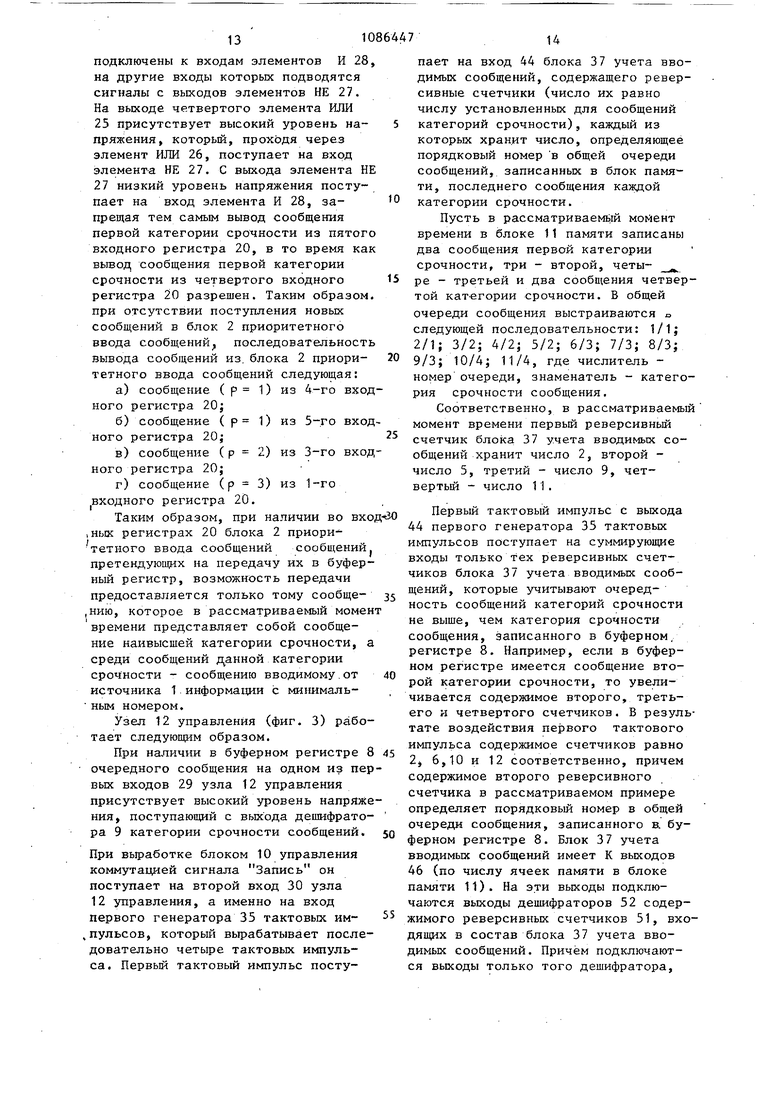

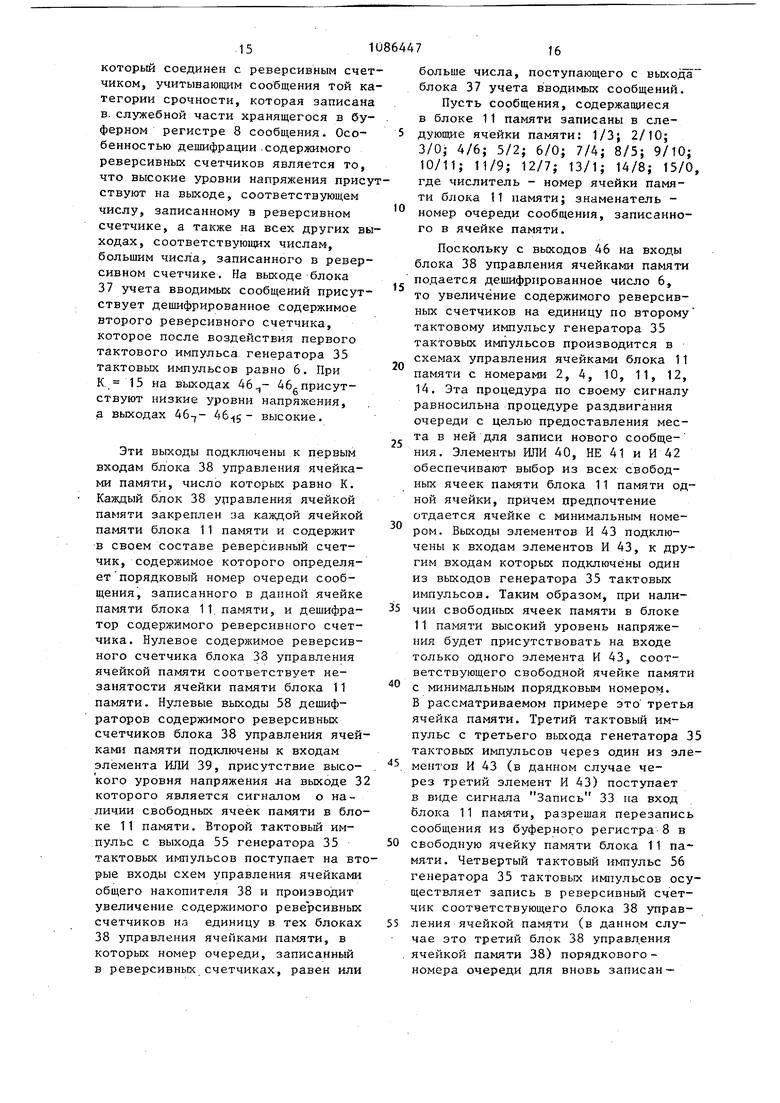

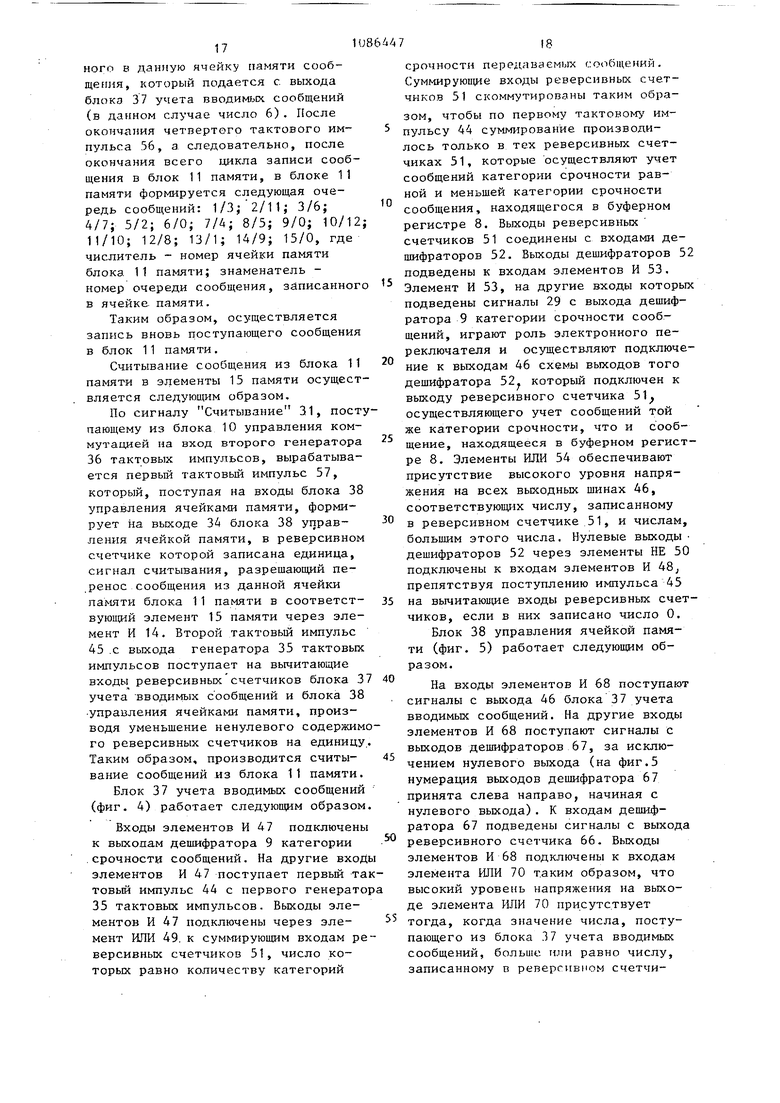

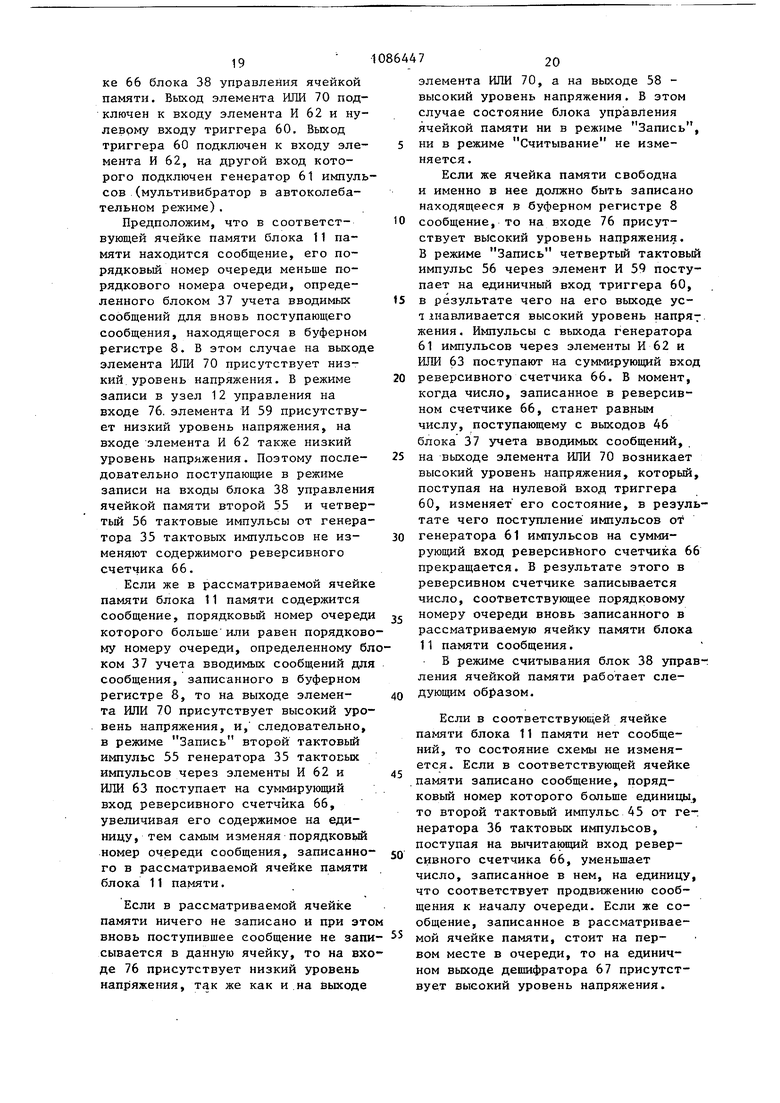

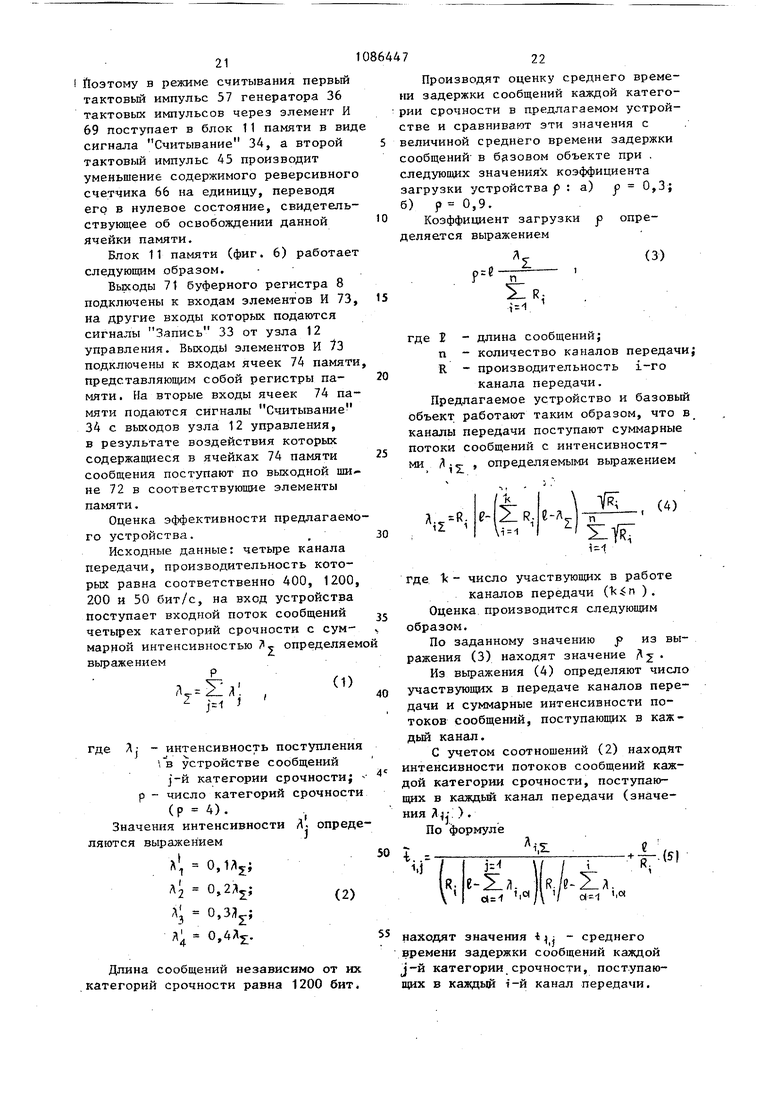

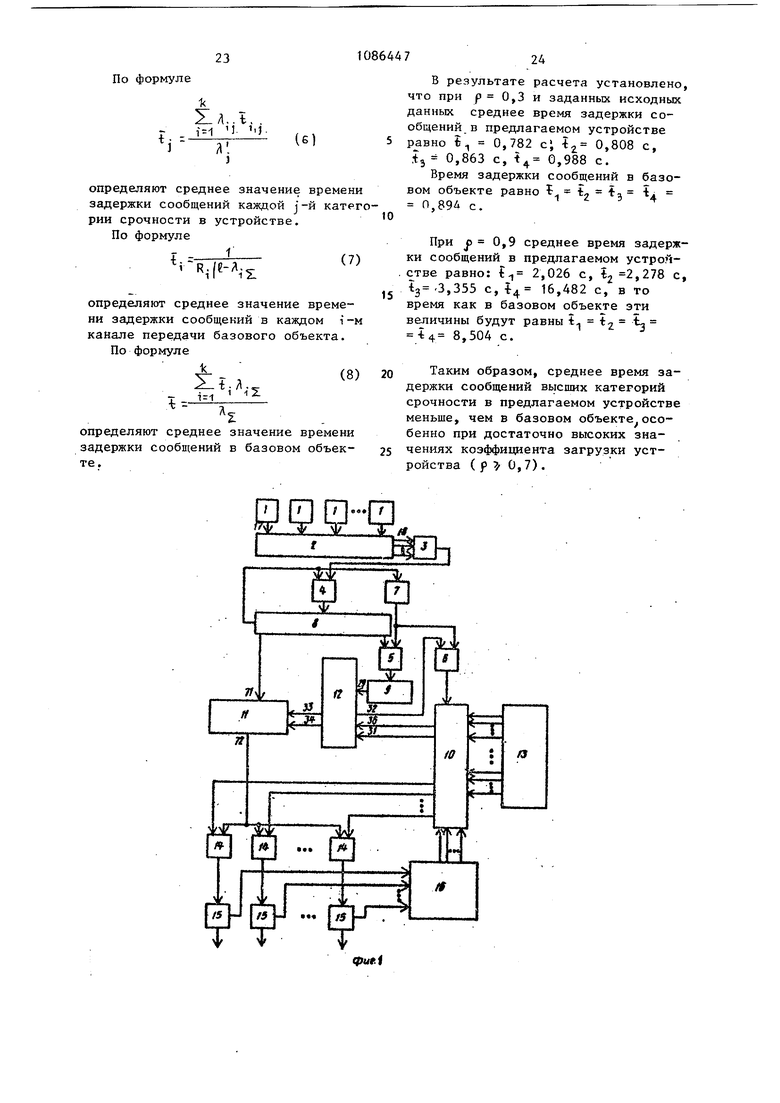

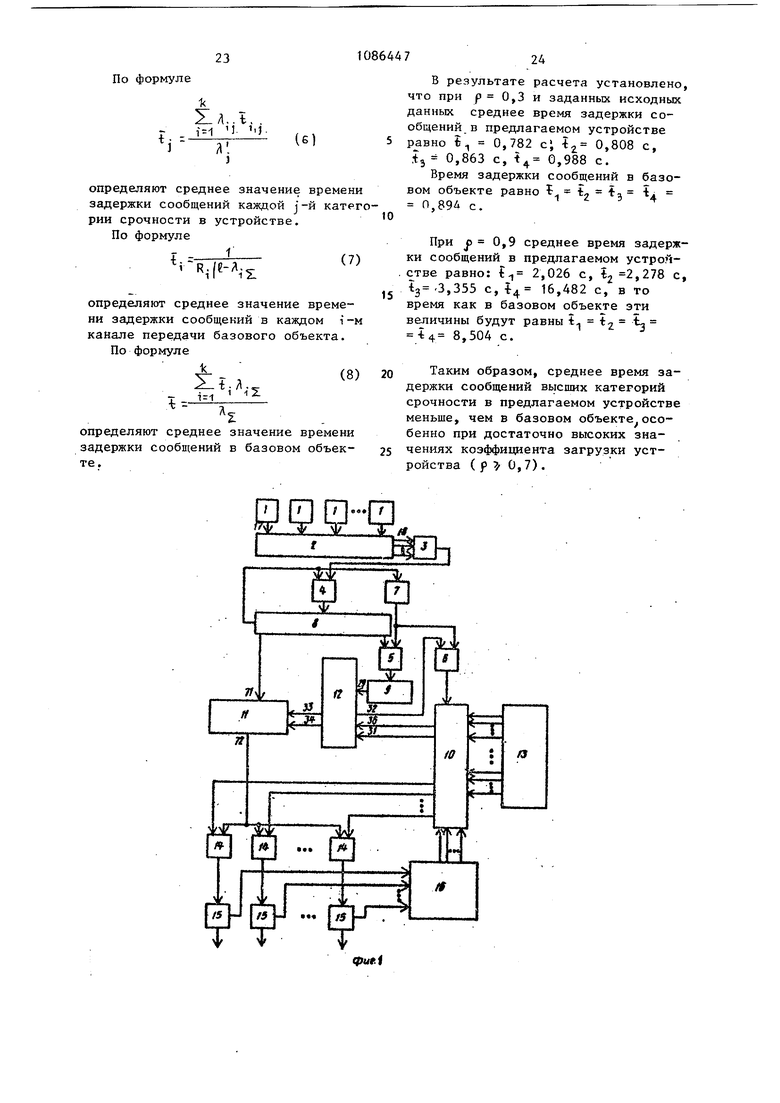

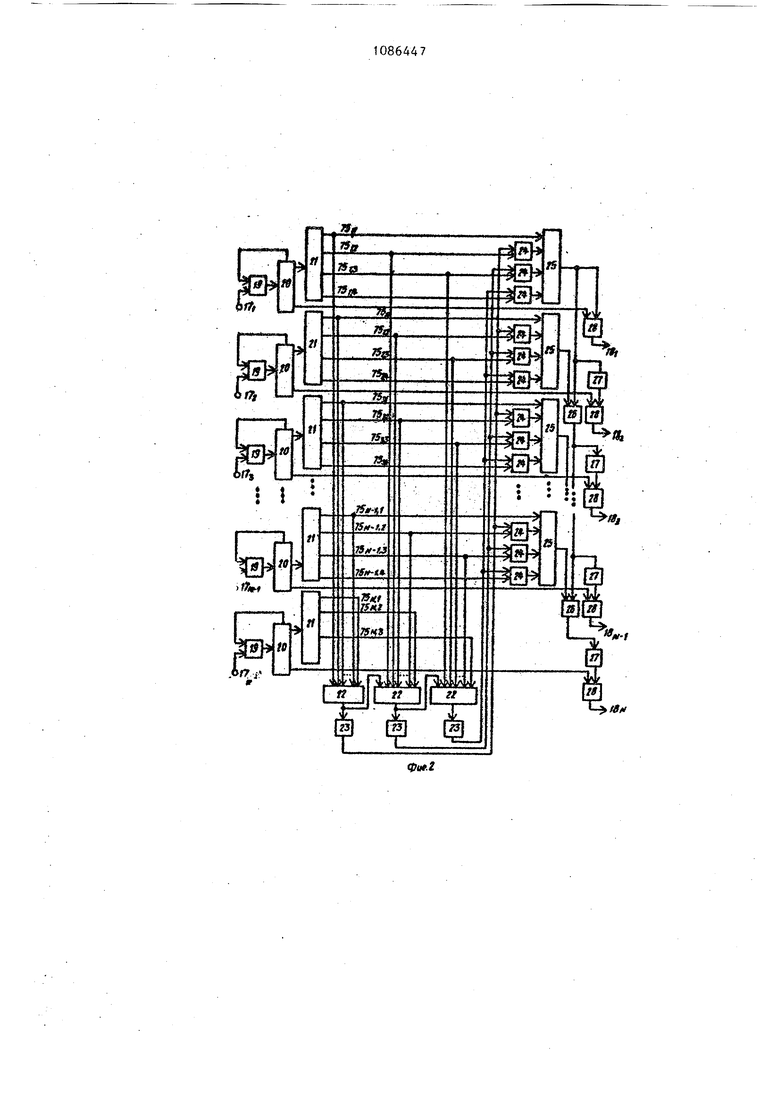

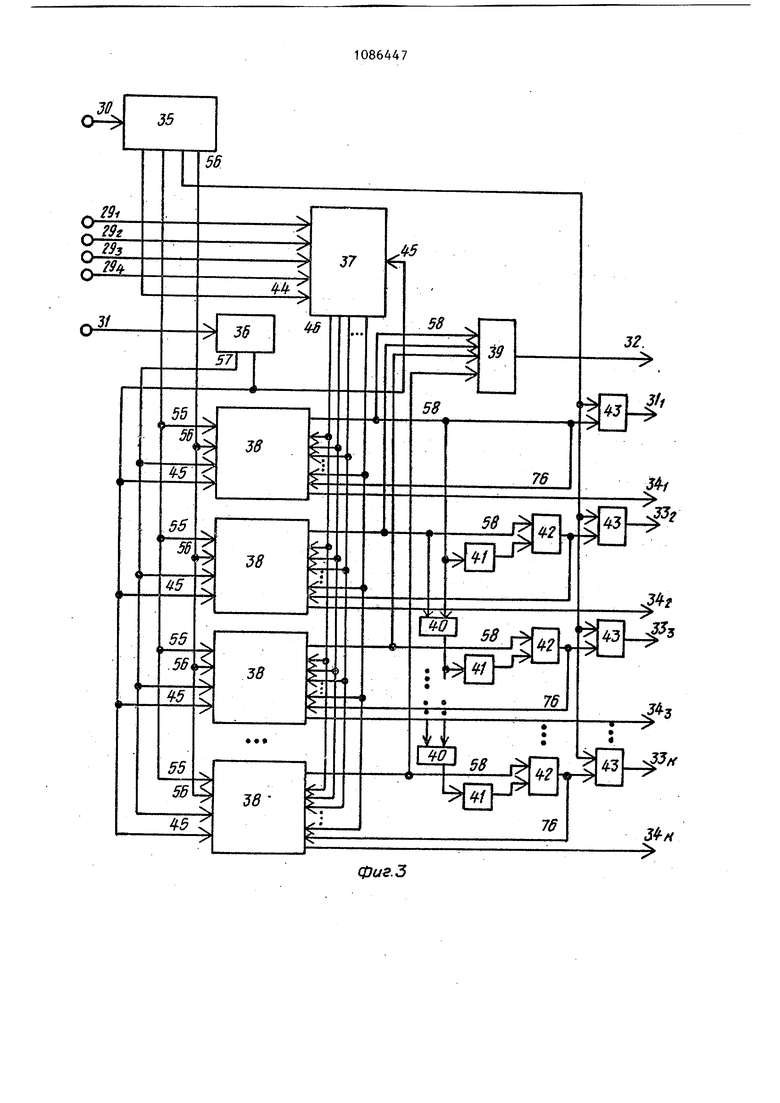

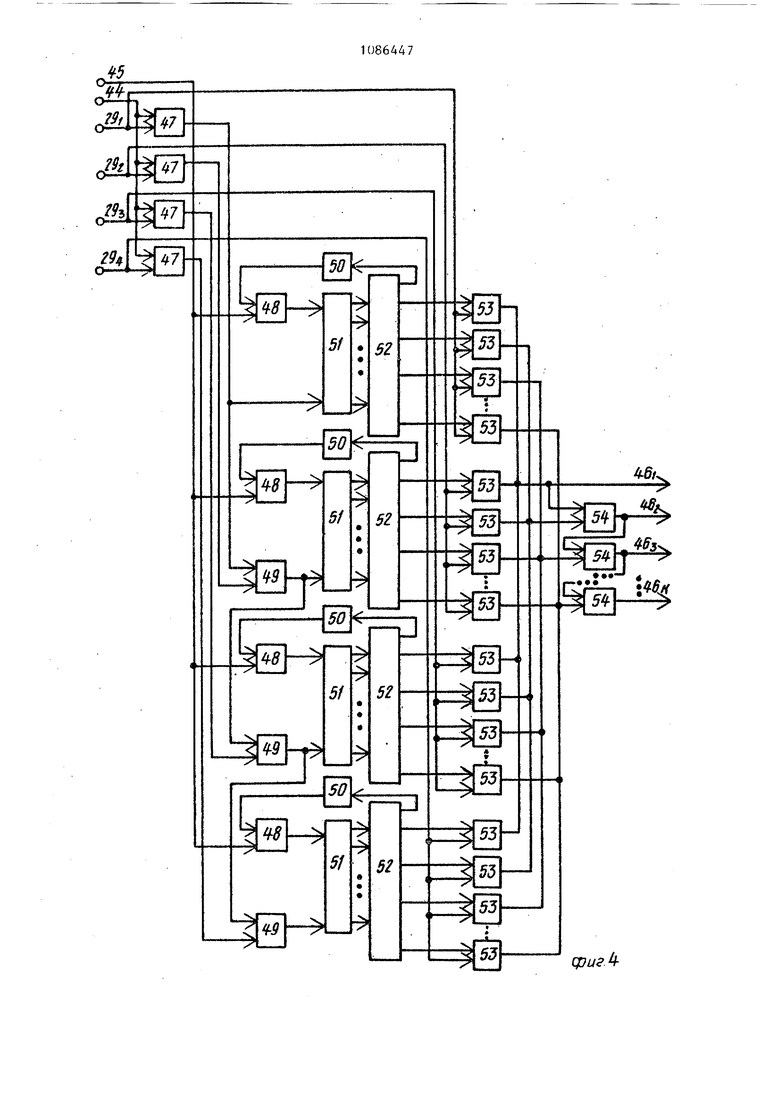

На фиг. 1 приведена структурная схема многоканального коммутатора приоритетных сообщений; на фиг.2 вариант схемы блока приоритетного ввода сообщений-; на фиг. 3 - функциональная схема уэла управления; на фиг. 4 - блок фиксации вводимых сообщений; на фиг. 5 - блок управления ячейкой памяти; на фиг. 6 вариант схемы блока памяти.

Предлагаемое устройство содержит источники 1 информацииJ блок 2 приоритетного ввода сообщений, элемент ИЛИ 3, элементы И 4-6, элемент НЕ 7, буферный регистр 8, дешифратор 9 категории срочности сообщений, блок 10 управления коммутацией, блок 11 памяти, узел 12 управления, блок 13 задания пороговых значений, элементы И 14, элементы 15 памяти, блок 16 выбора свободного канала.

Блок 2 приоритетного ввода сообщений (фиг. 2) содержит вводы 17, выходы 18, элементы И 19, входные регистры 20, дешифраторы 21, элементы ИЛИ 22, элементы НЕ 23, элементы И 24, элементы ИЛИ 25 и 26, элементы НЕ 27, элементы И 28. Узел управления (фиг. 3) содержи входы 29-31, выходы 32, 33 и 34, генераторы 35 и 36 тактовых импульсов, блок 37 учета вводимых сообщений, блок 38 управлениЯдЭлементы ИД 39 и 40, элементы НЕ 41, элемент И 42 и 43. Блок 37 учета вводимых сообщений (фиг, 4) содержит входы 44, 45, 29, выходы 46, элементы И 47 и 48, элементы ИЛИ 49, элементы НЕ 50, реверсивные счетчики 51, дешифраторы 52, элементы И 53 и элементы ИЛИ 54. Блок 38 управления ячейкой памяти (фиг. 5) содержит входы 55 57, 45-47, выходы 58 и 34, элемент И 59, триггер 60 с раздельными входами, генератор 61 импульсов, элементы И 62, элемент ИЛИ 63, элемент И 64, элемент НЕ 65, реверсивный счетчик 66, дешифратор 67, элементы И 68 и 69.и элемент ИЛИ 70 Блок 11 памяти (фиг. 6) содержит входы 71, 33 и 34, выход 72, элементы И 73 и ячейки памяти 74. Работа многоканального коммутатора приоритетных сообщений поясняется на примере передачи сообщений четьгрех категорий срочности от источников информации по М параллельным каналам передачи разной про изводительности, причем общий накопитель имеет в своем составе К ячее памяти, предназначенных для записи и хранения К дискретных сообщений. Сообщения независимо от присваиваемой им абонентами-отправителями категории срочности имеют одинаковую длину и состоят из информационной, и служебной частей. В служебную часть сообщений наряду с другим признаками заносится индекс, опреде ляющий принадлежность каждого сообщ ния к одной из четырех существующих категорий срочности, индекс приоритета. Индекс приоритета размещается в строго определенном месте слз жебной части сообщений и принимает значения, количество которых равно числу существующих категорий срочности (в рассматриваемом случае индекс приоритета может принимать четыре значения). 1 78 Пусть индекс приоритета р принимает значения 1,2, 3 и 4 , значение индекса приоритета р соответствует категории срочности сообщения. Так сообщениям первой категории срочности присваивается индекс р 1 (сообщения с индексом имеют преимущественное право на передачу перед сообщениями с индексами р 2, 3 и 4, сообщения с индексом р 2 перед сообщениями с индексами р 3 и 4-, сообщения с индексом р 3 - перед сообщениями с индексом Р 4. Устройство работает следующим образом. Сообщения от источников 1 информации поступают на входы 17 блока 2 приоритетного ввода сообщений, который производит следующие действия: определяют возможность ввода в многоканальньй коммутатор приоритетных сообщений новых сообщений в зависимости от общей загруженности устройства} вводит от источников информации 1 в многоканальный коммутатор приоритетных сообщений новые сообщения при отсутствии перегрузки устройства; осуществляет приоритетный ввод вновь поступающих сообщений в буферный регистр 8. В результате работы блока 2 приоритетного ввода сообщений при наличии у источников информации 1 сообщений один из выходов 18 подключается к источнику информации 1, вводящему в рассматриваемый момент времени сообщение с минимальным значением индекса приоритета. Через элементы ИЛИ 3 это сообщение поступает.на первый вход элемента И 4, на второй вход которого поступает сигнал о занятости буферного регистра 8, Если буферный регистр 8 занят, то на второй вход элемента И 4 поступает низкий уровень напряжения, препят- . ствующий записи очередного сообг щения в буферный регистр 8, Если буферный регистр 8 свободен, то навтором входе элемента И 4 присутствует высокий уровень напряжения, и вновь поступившее сообщение с выхода элемента ИЛИ 3 через элемент И 4 поступает в буферный регистр 8, После занятия буферного регистра 8 на первом выходе его появляется сигнал занятия - низкий уровень напряжения, который, препятст- вуя записи следующего сообщения в буферный регистр 8 через элемент И 4, поступает на вход элемента НЕ 7. С выхода элемента НЕ 7 высоким уров нем напряжения этот сигнал поступае на входы элементов И 5 и 6. К входа элемента И 5 подключены вторые выхо ды буферного регистра 8, на которые выводится кодовая комбинация присвоенного записанному в буферном регистре 8 сообщению индекса приори тета. Через элемент И 5 эта кодовая комбинация поступает на входы дешифратора 9 категории срочности сообщений. При наличии в бЛоке 11 памяти свободных ячеек памяти с пер вого выхода 32 узла 12 управления на вход элемента И 6 поступает высокий уровень напряжения, в результате чего на выходе элемента И 6 возникает высокий уровень напряжения, который, поступая в блок 10 управления коммутацией, формирует в нем сигнал Запись. Этот сигнал с выхода 30 блока 10 управления ком мутацией поступает на вход узла 12 управления, который осуществляет постановку поступающих сообщений в очередь в соответствии с присвоен ными им индексами приоритета и выби рает ячейку памяти, в которую должн быть записано сообщение, находящеес в буферном регистре 8-. Узел 12 управления выдает на один из входов высокий уровень напряжения, разрешающий перезапись сообщения из буферного регистра 8 по выходу 71 в выбранную ячейку памяти общего накопителя. После этого буферный регистр 8 освобождается, и при наличи сообщений у источников 1 информации происходит запись следующего сообщения в блок 11 памяти. Сигнал с выхода элемента И б.кроме формирующего сигнал Запись в блоке управления коммутацией 10, поступае на суммирующий вход реверсивного счетчикаJ увеличивая его содержимое на единицу. Этот счетчик, находящийся в блоке 10 управления комму. тацией, учитьшает количество сообщений, йаходящихся в блоке 11 памяти. На входы блока 10 управления коммутацией поступают пороговые значения для каждого канала пер.едачи, вырабатываемые с учетом производительности каждого канала передачи блоком 13.задания пороговых значений. Блок 10 управления коммутацией производит сравнение содержимого реверсивного счетчика с пороговыми значениями. В результате этого сравнения принимается решение о необходимости включения того или иного канала передачи в процесс передачи сообщений,- т.е. на соответствующих первьк выходах блока 10 управления коммутадаей появляются высокие уровни .напряжения. Считывание сообщений из блока 11 памяти в элементы 15 памяти .осуществляется следующим образом. При наличии свободных элементов 15 с их выходов на входы блока 16 выбора свободного канала поступают высокие уровни напряжения. Блок 16 выбора свободного канала производит выбор из всех свободных и участвующих в процессе передачи сообщений канала, обладающего максимальной производительностью. В результате этого на одном из выходов блока 16 выбора сво- бодного канала присутствует высокий уровень напряжения. Высокий уровень напряжения на одном из третьих входов блока 10 управления коммутацией и ненулевое содержимое реверсивного счетчика, определяющего количество сообщений, записанных в блоке 11 памяти, формируют сигнал Считывание, который высоким уровнем напряжения с выхода 31 блока 10 управления коммутацией поступает на вход узла 12 управления. Одновременно на вычитающий вход реверсивного счетчика, расположенного в блоке 10 управления коммутацией, поступает сигнал, по которому содержимое счетчика уменьшается на единицу. Сигнал Считывание, поступающий на вход узла 12 управления, вырабатьшает в нем сигнал, разрешающий считьгеание сообщения, записанного в блоке 11 памяти и стоящего в рассматриваемьй момент времени впереди других записанных в блоке 11 памяти сообщений. Этот сигнал представляет собой высокий уровень напряжения на одном из выходов 34 узла 12 управления. Сообщение с выхода блотса 11 памяти через соответствующий элемент И 14 записывается в элемент 15 памяти выбранного канала передачи. Блок 2 приоритетного ввода сообщений (фиг. 2) работает следующим образом. Присутствие во входном регистре 20 сообщения инициирует присутствие на выходе входного регистра 20 inr5кого уровня напряжения, запре1цаю| 1ег ввод в устройство от источника 1 информации очередного сооби1ения. В случае незанятости входного регистра 20 на его выходе присутствует высокий уровень напряжения, ра решающий ввод сообщения от источник 1 информа1ши через элемент И 19 во входной регистр 20, при этом на дру гом выходе присутствует кодовая ком бинация индекса приоритета данного сообщения, которая поступает на вхо дешифратора 21. На соответствующем выходе дешифратора 21 возникает выс кий уровень напряжения. На фиг. 2 выходы дешифратора 21 обозначены но мером 75 , где i - порядковый номер источника информации 1, в обр ботке сообщений от которого принима ет участие данный деишфратор 20; j - выход дешифратора, соответству щий значению индекса приоритета р , т.е. j 1,2,3,4.Пусть N 5, т.е. имеется 5 источников информации 1. Пусть в первом входном регистре записано сообщение 3-й категории срочности ( р 3), во втором сообщение отсутствует, в третьем - сообщений 2-й, в четвертом - сообщение 1-й, в пятом сообщение 1-й категории срочности. При этом высокие уровни напряжения присутствовать на выходах дешифраторов 75 3 3,г ,1 5,1 Эти сигналы поступают на соответствующие входы элементов ИЛИ 22. На входы первого элемента ИЛИ 22 подве дены все выходы дешифраторов 21, соответствующие р 1(75 , 75щ), на входы второго элемента ИЛИ22 - все выходы дешифрато1)ов 21 соответствующие р 2( ,2 75nj , ), а также сигнал с выхода первого элемента ИЛИ 22, на входы третьего элемента ИЛИ 22 - все выходы дешифраторов 21, соответствуюш;ие р 3(75-,2 , 752 . . . ,75 ) , а также сигнал с выхода второго элемента ИЛИ 22. К выходам элементов ИЛИ 22 подключены элементы Н 23, выходы которых подключены к первым входам элементов И 24. На вторые входы элементов И 24 Подключены выходы дешифраторов 21 (выходы ), где i 1,2,..., N-1, i 2,3, 4). Выход первого элемента НЕ 23 подключен к входам тех элсментоп И 24, ма другие itx(.Aw коTtjpbK подключены вььход1)1 ,п-оров 21, с.оответствуюиц-ie значению р 2 (выходы 75 2 , 2,...,N-1). Выход второго элемента НЕ 23 подключен к входам тех элементов И 24, на другие входы которых подключены выходы дешифраторов 21, соответствуюш е Р 3 (выходы , где i 1,2,...,N-1). Соответственно, выходы третьего элемента НЕ 23 подключены к входам элементов И 24, на другие входы которых подключены выходы дешифраторов 21, соответствующие р 4 (выходы где 1 1, 2,..., N-1). Выходы 75 (i 1,2,...,N-1) дешифраторов 21 и выходы элементов И 24 подключены к входам соответствующих элементов ИЛИ 25, Таким образом, в любой момент времени высокий уровень напряжения присутствует на выходах только тех элементов ИЛИ 25, к входам которых подведен высокий уровень напряжения от дешифраторов 21 непосредственно или через соответствующие элементы И 24. В рассматриваемом примере высокий уровень напряжения присутствует только на выходе четвертого элемента ИЛИ 25. Таким образом, осуществляется отбор из всех содержащихся в блоке приоритетного ввода сообщений наивысшей категории срочности. Так, если во всех входных регистрах находятся сообщения одной и той же категории срочности, на всех выходах элементов ИЛИ 25 присутствует высокий уровень напряжения. Группы элементов ИЛИ 26, НЕ 27 и И 28 определяют последовательность ввода сообщений из входных регистров 20 в буферный регистр 8. При этом, если в рассматриваемый момент времени в нескольких входных регистрах 20 содержатся сообщения наивысшей категории срочности, то предпочтение в выборе сообщения, которое должно быть переписано в буферный регистр 8, отдается сообщению данной категории срочности, поступившему от источника 1 информации с минимальным номером. В данном случае в четвертом и пятом входных регистрах 20 находятся сообщения первор категории срочности. Первые выходы входных регистрор 20, по которым осуществляется запись сообщений в буферный регистр 8, подключены к входам элементов И 28 на другие входы которых подводятся сигналы с выходов элементов НЕ 27. На выходе четвертого элемента ИЛИ 25 присутствует высокий уровень напряжения, которьй, проходя через элемент ИЛИ 26, поступает на вход элемента НЕ 27. С выхода элемента Н 27 низкий уровень напряжения поступает на вход элемента И 28, запрещая тем самым вывод сообщения первой категории срочности из пятог входного регистра 20, в то время ка вьшод сообщения первой категории срочности из четвертого входного регистра 20 разрешен. Таким образом при отсутствии поступления новых сообщений в блок 2 приоритетного ввода сообщений последовательност вывода сообщений из. блока 2 приоритетного ввода сообщений следующая: а)сообщение ( р 1) из 4-го вхо ного регистра 20; б)сообщение ( р 1) из 5-го вхо ного регистра 20; в)сообщение (р 2) из 3-го вхо ного регистра 20; г)сообщение (р 3) из 1-го входного регистра 20. Таким образом, при наличии во вх ,нык регистрах 20 блока 2 приоритетного ввода сообщений сообщений претендующих на передачу их в буфер ный регистр, возможность передачи предоставляется только тому сообще,нию, которое в рассматриваемый моме времени представляет собой сообщение наивысшей категории срочности, среди сообщений дранной категории срочности - сообщению вводимому.от источника 1.информации с минимальным номером. Узел 12 управления (фиг. 3) рабо тает следующим образом. При наличии в буферном регистре очередного сообщения на одном из пе вых входов 29 узла 12 управления присутствует высокий уровень напряж ния, поступающий с выхода дешифрато ра 9 категории срочности сообщений. При выработке блоком 10 управления коммутацией сигнала Запись он поступает на второй вход 30 узла 12 управления, а именно на вход первого генератора 35 тактовых им,пульсов, который вьфабатывает после довательно четыре тактовьк импульса. Первый тактовый импульс поступает на вход 44 блока 37 учета вводимых сообщений, содержащего реверсивные счетчики (число их равно числу установленных для сообщений категорий срочности), каждый из которых хран.ит число, определяющее порядковый номер в общей очереди сообщений, записанных в блок памяти, последнего сообщения каждой категории срочности. Пусть в рассматриваемом мойент времени в блоке 11 памяти записаны два сообщения первой категории срочности, три - второй, четыре - третьей и два сообщения четвертой кат-егории срочности. В общей очереди сообщения выстраиваются о следующей последовательности: 1/1; 2/1; 3/2; 4/2; 5/2; 6/3; 7/3; 8/3; 9/3; 10/4; 11/4, где числитель номер очереди, знаменатель - категория срочности сообщения. Соответственно, в рассматриваемый момент времени первый реверсивный счетчик блока 37 учета вводимых сообщений хранит число 2, второй число 5, третий - число 9, четвертьм - число 11. Первый тактовый импульс с выхода 44 первого генератора 35 тактовых импульсов поступает на суммирующие входы только тех реверсивных счетчиков блока 37 учета вводимых сообщений, которые учитывают очередность сообщений категорий срочности не выше, чем категория срочности сообщения, записанного в буферном, регистре 8. Например, если в буферном регистре имеется сообщение второй категории срочности, то увеличивается содержимое второго, третьего и четвертого счетчиков. В результате воздействия первого тактового импульса содержимое счетчиков равно 2, 6,10 и 12 соответственно, причем содержимое второго реверсивного счетчика в рассматриваемом примере определяет порядковый номер в общей очереди сообщения, записанного в. буферном регистре 8. Блок 37 учета вводимых сообщений имеет К выходов 46 (по числу ячеек памяти в блоке памяти 11). На э.ти выходы подключаются выходы дешифраторов 52 содержимого реверсивных счетчиков 51, входящих в состав блока 37 учета вводимых сообщений. Причём подключаются выходы только того дешифратора. который соединен с реверсивным сче чиком, учитывающим сообщения той к тегории срочности, которая записан в. служебной части хранящегося в бу ферном регистре 8 сообщения. Особенностью дешифрации.содержимого реверсивных счетчиков является то, что высокие уровни напряжения прис ствуют на выходе, соответствующем числу, записанному в реверсивном счетчике, а также на всех других в ходах, соответствующих числам, большим числа, записанного в ревер сивном счетчике. На выходе блока 37учета вводимых сообщений присут ствует дешифрированное содержимое второго реверсивного счетчика, которое после воздействия первого тактового импульса генератора 35 тактовых импульсов равно 6. При К. 15 на выходах 46дПрисутствуют низкие уровни напряжения, а выходах 46-7- - высокие. Эти выходы подключены к первым входам блока 38 управления ячейками памяти, число которых равно К. Каждый блок 38 управления ячейкой памяти закреплен за каждой ячейкой памяти блока 11 памяти и содержит в своем составе реверсивный счетчик, содержимое которого определяет порядковый номер очереди сообщения, записанного в данной ячейке памяти блока 11. памяти, и дешифратор содержимого реверсивного счетчика. Нулевое содержимое реверсивного счетчика блока 38 управления ячейкой памяти соответствует незанятости ячейки памяти блока 11 памяти. Нулевые выходы 58 дешифраторов содержимого реверсивных счетчиков блока 38 управления ячей ками памяти подключены к входам элемента ИЛИ 39, присутствие высокого уровня напряжения ла выходе 3 которого является сигналом о наличии свободных ячеек памяти в бло ке 11 памяти. Второй тактовьй импульс с выхода 55 генератора 35 тактовых импульсов поступает на вт рые входы схем управления ячейками общего накопителя 38 и производит увеличение содержимого реверсивных счетчиков на единицу в тех блоках 38управления ячейками памяти, в которых номер очереди, записанный в реверсивных счетчиках, равен или больше числа, поступающего с выхода блока 37 учета вводимьк сообщений. Пусть сообщения, содержащиеся в блоке 11 памяти записаны в следующие ячейки памяти: 1/3; 2/10; 3/0,- 4/6; 5/2; 6/0; 7/4; 8/5; 9/10; 10/11; 11/9; 12/7; 13/1; 14/8; 15/0, где числитель - номер ячейки памяти блока 11 памяти; знаменатель номер очереди сообщения, записанного в ячейке памяти. Поскольку с выходов 46 на входы блока 38 управления ячейками памяти подается дешифрированное число 6, то увеличение содержимого реверсивных счетчиков на единицу по второму тактовому импульсу генератора 35 тактовых импульсов производится в схемах управления ячейками блока 11 памяти с номерами 2, 4, 10, 11, 12, 14. Эта процедура по своему сигналу равносильна процедуре раздвигания очереди с целью предоставления места в ней для записи нового сообщания. Элементы ИЛИ 40, НЕ 41 и И 42 обеспечивают выбор из всех свободных ячеек памяти блока 11 памяти одной ячейки, причем предпочтение отдается ячейке с минимальным номером. Выходы элементов И 43 подключены к входам элементов И 43, к другим входам которых подключены один из выходов генератора 35 тактовых импульсов. Таким образом, при наличии свободных ячеек памяти в блоке 11 памяти высокий уровень напряжения будет присутствовать на входе только одного элемента И 43, соответствующего свободной ячейке памяти с минимальным порядковым номером. В рассматриваемом примере это третья ячейка памяти. Третий тактовый импульс с третьего выхода генетатора 35 тактовых импульсов через один из элементов И 43 (в данном случае через третий элемент И 43) поступает в виде сигнала Запись 33 на вход блока 11 памяти, разрешая перезапись сообщения из буферного регистра 8 в свободную ячейку памяти блока 11 памяти. Четвертый тактовый и myльc 56 генератора 35 тактовых импульсов осуществляет запись в реверсивный счетчик соответствующего блока 38 управления ячейкой памяти (в данном случае это третий блок 38 управдения ячейкой памяти 38) порядкового номера очереди для вновь записан-

НОГО в данмую ячейку памяти сообщеиля, который подается с. выхода блока 37 учета вводиш к сообщений (в данном случае число 6). После оконч-апия четвертого тактового импульса 56, а следовательно, после окончания всего цикла записи сообщения в блок 11 памяти, в блоке 11 памяти формируется следующая очередь сообщений: 1/3; 2/11; 3/6; 4/7; 5/2; 6/0; 7/4; 8/5; 9/0; 10/12; 11/10; 12/8; 13/1; 14/9; 15/0, где числитель - номер ячейки памяти блока 11 памяти; знаменатель номер очереди сообщения, записанного в ячейке, памяти.

Таким образом, осуществляется запись вновь поступающего сообщения в блок 11 памяти.

Считывание сообщения из блока 11 памяти в элементы 15 памяти осуществляется следующим образом.

По сигналу Считывание 31, поступающему из блока 10 управления коммутацией на вход второго генератора 36 тактовых импульсов, вырабатывается первый тактовый импульс 57, который, поступая на входы блока 38 управления ячейками памяти, формирует на выходе 34 блока 38 управления ячейкой памяти, в реверсивном счетчике которой записана единица, сигнал считывания, разрещающий пе,ренос сообщения из данной ячейки памяти блока 11 памяти в соответствуюи1 1й элемент 15 памяти через элемент И 14. Второй тактовый импульс 45 .с выхода генератора 35 тактовых импульсов поступает на вычитающие входы реверсивных счетчиков блока 37 учета вводимых сообщений и блока 38 управления ячейками памяти, производя уменьщение ненулевого содержимого реверсивных счетчиков на единицу.. Таким образом, производится считывание сообщений из блока 11 памяти.

Блок 37 учета вводимых сообщений (фиг. 4) работает следующим образом.

Входы элементов И 47 подключены к выходам дешифратора 9 категории ,срочности сообщений. На другие входы элементов И 47 поступает первьш тактовый импульс 44 с первого генератор 35 тактовых импульсов. Выходы элементов И 47 подключены через элемент ИЛИ 49. к сум шрующим входам реверсивных счетчиков 51, число которых равно количеству категорий

срочности передаваемых сообщений. Суммируюи ие входы реверсивных счетчиков 51 скоммутированы таким образом, чтобы по первому тактовом импульсу 44 суммирование производилось только в тех реверсивных счетчиках 51, которые осуществляют учет сообщений категории срочности равной и меньщей категории срочности сообщения, находящегося в буферном регистре 8. Выходы реверсивных счетчиков 51 соединены с входами дещифраторов 52. Выходы дешифраторов 5 подведены к входам элементов И 53. Элемент И 53, на другие входы которы подведены сигналы 29 с выхода дешифратора 9 категории срочности сообщений, играют роль электронного переключателя и осуществляют подключение к выходам 46 схемы выходов того дешифратора 52 который подключен к выходу реверсивного счетчика 51 осуществляющего учет сообщений той же категории срочности, что и сообщение, находящееся в буферном регистре 8. Элементы ИЛИ 54 обеспечивают присутствие высокого уровня напряжения на всех выходных щинах 46, соответствующих числу, записанному в реверсивном счетчике 51, и числам, большим этого числа. Нулевые выходы дешифраторов 52 через элементы НЕ 50 подключены к входам элементов И 48 препятствуя поступлению импульса 45 на вычитаю1Л 1е входы реверсивных счетчиков, если в них записано число 0. Блок 38 управления ячейкой памяти (фиг. 5) работает следуюш 1м образом.

На входы элементов И 68 поступают сигналы с выхода 46 блока 37 учета вводимых сообщений. На другие входы элементов И 68 поступают сигналы с выходов дешифраторов 67, за исключением нулевого выхода (на фиг.5 нумерация выходов деишфратора 67 принята слева направо, начиная с нулевого выхода). К входам дешифратора 67 подведены сигналы с выхода реверсивного счетчика 66. Выходы элементов И 68 подключены к входам элемента {-ШИ 70 таким образом, что высокий уровень напряжения на выходе элемента ИЛИ 70 присутствует тогда, когда значение числа, поступающего из блока 37 учета вводимых сообщений, больше или равно числу, записанному в реверсивном счетчике 66 блока 38 управления ячейкой памяти. Выход элемента ИЛИ 70 подключен к входу элемента И 62 и нулевому входу триггера 60, Выход триггера 60 подключен к входу элемента И 62, на другой вход которого подключен генератор 61 импуль сов (мультивибратор в автоколебательном режиме). Предположим, что в соответствующей ячейке памяти блока 11 памяти находится сообщение, его порядковый номер очереди меньше порядкового номера очереди, определенного блоком 37 учета вводимых сообщений для вновь поступающего сообщения, находящегося в буферном регистре 8. В этом случае на выход элемента ИЛИ 70 присутствует низкий уровень напряжения. В режиме записи в узел 12 управления на входе 76. элемента И 59 присутствует низкий уровень напряжения, на входе элемента И 62 также низкий уровень напряжения. Поэтому последовательно поступающие в режиме записи на входы блока 38 управлени ячейкой памяти второй 55 и четвер тый 56 тактовые импульсы от генера тора 35 тактовых импульсов не изменяют содержимого реверсивного счетчика 66. Если же в рассматриваемой ячейк памяти блока 11 памяти содержится сообщение, порядковый номер очеред которого больше или равен порядков му номеру очереди, определенному б ком 37 учета вводимых сообщений дл сообщения, записанного в буферном регистре 8, то на выходе элемента ИЛИ 70 присутствует высокий уро вень напряжения, и, следовательно, в режиме Запись второй тактовьй импульс 55 генератора 35 тактовых импульсов через элементы И 62 и ИЛИ 63 поступает на суммирующий вход реверсивного счетчика 66, увеличивая его содержимое на единицу, тем самым изменяя порядковый номер очереди сообщения, записанно го в рассматриваемой ячейке памяти блока 11 памяти. Если в рассматриваемой ячейке памяти ничего не записано и при эт Бновь поступившее сообщение не зап

сывается в данную ячейку, то на входе 76 присутствует низкий уровень напряжения, так же как и на выходе

вом месте в очереди, то на единичном выходе дешифратора 67 присутствует высокий уровень напряжения. 7 элемента ИЛИ 70, а на выходе 58 высокий уровень напряжения. В этом случае состояние блока упр авления ячейкой памяти ни в режиме Запись, ни в режиме Считывание не изменяется . Если же ячейка памяти свободна и именно в нее должно быть записано находящееся в буферном регистре 8 сообщение, то на входе 76 присутствует высокий уровень напряжения, В режиме Запись четвертый тактовый импульс 56 через элемент И 59 поступает на единичный вход триггера 60, в результате чего на его выходе усIАнавливается высокий уровень напряг жения. Импульсы с выхода генератора 61 импульсов через элементы И 62 и ИЛИ 63 поступают на суммирующий вход реверсивного счетчика 66. В момент, когда число, записанное в реверсивном счетчике 66, станет равным числу, поступающему с выходов 46 блока 37 учета вводимых сообщений, на выходе элемента ИЛИ 70 возникает высокий уровень напряжения, который, поступая на нулевой вход триггера 60, изменяет его состояние, в результате чего поступление импульсов от генератора 61 импульсов на суммирующий вход реверсивного счетчика 66 прекращается. В результате этого в реверсивном счетчике записывается число, соответствующее порядковому номеру очереди вновь записанного в рассматриваемую ячейку памяти блока I1памяти сообщения. В режиме считывания блок 38 управг ления ячейкой памяти работает следующим образом. Если в соответствующей ячейке памяти блока 11 памяти нет сообщений, то состояние схемы не изменяется. Если в соответствующей ячейке памяти записано сообщение, порядковый номер которого больше единицы, то второй тактовый импульс 45 от генератора 36 тактовых импульсов, поступая на вычитающий вход реверсивного счетчика 66, уменьшает число, записанное в нем, на единицу, что соответствует продвижению сообщения к началу очереди. Если же сообщение, записанное в рассматривае„ой ячейке памяти, стоит на перI Поэтому в режиме считывания первый тактовый импульс 57 генератора 36 тактовых импульсов через элемент И 69 поступает в блок 11 памяти в вид сигнала Считывание 34, а второй тактовый импульс 45 производит уменьшение содержимого реверсивного счетчика 66 на единицу, переводя его в нулевое состояние, свидетельствующее об освобождении данной ячейки памяти. Блок 11 памяти (фиг. 6) работает следующим образом. Вькоды 71 буферного регистра 8 подключены к входам элементов И 73, на другие входы которых подаются сигналы Запись 33 от узла 12 управления. Выходы элементов И 73 подключены к входам ячеек 74 памяти представляющим собой регистры памяти . На вторые входы ячеек 74 памяти подаются сигналы Считывание 34 с выходов узла 12 управления, в результате воздействия которых содержащиеся в ячейках 74 памяти сообщения поступают по выходной шине 72 в соответствующие элементы памяти. Оценка эффективности предлагаемо го устройства. Исходные данные: четыре канала передачи, производительность которых равна соответственно 400, 1200, 200 и 50 бит/с, на вход устройства поступает входной поток сообщений четырех категорий срочности с суммарной интенсивностью определяем вьфажением где Л; - интенсивность поступления в устройстве сообщений j-й категории срочности; р - число категорий срочности (). Значения интенсивности Д. определяются выражением

0, 0,

(2) 0, 0,4Д.

Длина сообщений независимо от их категорий срочности равна 1200 бит.

(5}

R.

находят значения ;

- среднего времени задержки сообщений каждой j-й категории срочности, поступающих в каждый i-й канал передачи. Производят оценку среднего времени задержки сообщений каждой категории срочности в предлагаемом устройстве и сравнивают эти значения с величиной среднего времени задержки сообщений в базовом объекте при . следующих значениях коэффициента загрузки устройствар : а) р 0,3; б) р 0,9. Коэффициент загрузки р определяется выражением -длина сообщений; -количество каналов передачи; -производительность i-ro канала передачи. Предлагаемое устройство и базовый объект работают таким образом, что в каналы передачи поступают суммарные потоки сообщений с интенсивностями ЗJ. , определяемыми выражением где 1 - число участвующих в работе каналов передачи ( ). Оценка производится следующим образом. По заданному значению f из выражения (3) находят значение Д . Из выражения (4) определяют число участвующих в передаче каналов передачи и суммарные интенсивности потоков сообщений, поступающих в каждьй канал. С учетом соотнощений (2) находят нтенсивности потоков сообщений кажой категории срочности, поступаюих в каждьй канал передачи (значеия Я.- ) . По формуле По формуле M определяют среднее значение времен задержки сообщений каждой -й кате рии срочности в устройстве. По формуле определяют среднее значение времени задержки сообщений в каждом iканале передачи базового объекта. По формуле определяют среднее значение времени задержки сообщений в базовом объекте . В результате расчета установлено, что при р 0,3 и заданных исходных данных среднее время задержки сообщений в предлагаемом устройстве равно t 0,782 с l. с, 3 i 0,863 с, 0,988 с. Время задержки сообщений в базовом объекте равно t. 2 Ь Ч П,894 с. При JJ 0,9 среднее время задержки сообщений в предлагаемом устройстве равно: {-, 2,026 с, ,278 с, ,355 c,i4 16, с, в то время как в базовом объекте эти величины будут равны t 2 з -f4 8,504 с. Таким образом, среднее время задержки сообщений высших категорий срочности в предлагаемом устройстве меньше, чем в базовом объекте особенно при достаточно высоких значениях коэффициента загрузки устройства ( р - 0,7).

фи.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коммутации сообщений | 1983 |

|

SU1157556A1 |

| Устройство для коммутации сообщений | 1984 |

|

SU1247879A1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОММУТАЦИИ СООБЩЕНИЙ | 2009 |

|

RU2416121C2 |

| ЦЕНТРАЛЬНАЯ СТАНЦИЯ СИСТЕМЫ РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2003 |

|

RU2245001C1 |

| Устройство для приоритетного обслуживания сообщений | 1977 |

|

SU734688A1 |

| Устройство для моделирования систем массового обслуживания | 1987 |

|

SU1418740A1 |

| Устройство для приема информации | 1987 |

|

SU1495841A1 |

| СИСТЕМА РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2001 |

|

RU2195774C2 |

| СИСТЕМА РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2003 |

|

RU2263401C2 |

| Система радиосвязи с подвижными объектами | 1986 |

|

SU1401626A1 |

1. МНОГОКАНАЛЬНЫЙ КОММУТАТОР, содержащий элемент ИЛИ, выход которого подключен к первому входу первого элемента И, второй элемент И, выход которого подключен к первому входу блока управления коммутацией, вторые входы которого подключены к Соответствующим выходам блока задания пороговых значений, первые выходы блока управления коммутацией подключены к первым выходам соответствующих третьих элементов И, вторые входы которых объединены и подключены к выходу блока памяти, выходы третьих элементов И подключены к выходам соответствующих элементов памяти, первые выходы которых через блок выбора свободного канала подключены к третьим выходам блока управления коммутацией, вторые выходы элементов памяти являются выходами многоканального коммутатора, отличающийс я тем, что, с целью повьшеиия быстродействия многоканального коммутатора, в него введены узел управления, дещифратор, четвертый элемент И, буферный регистр, элемент НЕ, блок приоритетного ввода сообщений, входы которого являются информационными входами устройства, выходы блока приоритетного ввода сообщений подключены к входам элемента ИЛИ, первьш выход буферного регистра подключен через элемент НЕ к первым входам второго и четвертого элемента И и непосредственно к второму входу первого элемента И, выход которого подключен к входу буферного регистра, второй выход которого подключен к второму входу четвертого элемента И, выход которого через дешифратор подключен к первым входам узла управления, первый выход которого соединен с вторым входом второго элемента И, втоС рой и третий выходы узла управления соединены с первым и вторым входами блока памяти, второй вход которого подключен к третьему выходу буферного регистра, второй и трео оо тий вьЬсоды блока управления коммутацией соединены соответственно с а вторым и третьим входами узла управления. 4;аь 2. Коммутатор по п. 1, о т л и чающийся тем, что блок приоритетного ввода сообщений содержит элементы ИЛИ, элементы НЕ, и информационные каналы в каждом из которых, кроме первого и последнего, содержатся первьш и второй элементы И, регистр, дешифратор, группа элементов И, первый и второй элементы ИЛИ и элемент НЕ, выход пкрвого элемента И соединен с первым входом регистра, первый выход которого соединен с первым входом второго эле

46z

a

3ff3

61

61

1/V ff

-HI

ffff

JiL

xiT

57

7

Т

J4

ф5(

г/г. 5

сриеб

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для ПЕРЕДАЧИ ИНФОРМАЦИИ ПО НЕСКОЛЬКИМ КАНАЛАМ | 0 |

|

SU378932A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1984-04-15—Публикация

1983-01-06—Подача