(Л

CZ

4

х

D1

00

ния - повышение быстродействия и информационной гибкости устройства путем селекции каналов с высокоприоритетными сообщениями и их внеочеред- ным обслуживанием. Устройство содержит первый 1 и второй 2 блоки памяти, первый 3 и второй 4 регистры, дешифратор 5, коммутатор 6, элементы И 7 группы, первый 8, второй 9 и третий 10 элементы задержки, первый 11 и второй 12 элементы РШИ, первьвй 13 и второй 14 каналы селекции, в первом канале селекции - первый 15 и второй 16 триггеры первой группы, первый 17, второй 18 и третий 19 триггеры второй группы, первый 20, второй 21

и третий 22 элементы И, элемент ИЛИ 23, элемент задержки 24, во втором канале селекции - первый 25 и второй 26 триггеры первой группы, первый 27, второй 28 и третий 29 триггеры второй группы, первый 30, второй 31 и третий 32 элементы И, элемент ИЛИ 33, элемент задержки 34. Устройство позволяет обслужить информационный канал с более высоким приоритетом поступившего сообщения в первую очередь, а затем, при наличии в другом канале сообщения с менее высоким приоритетом, - другой информационный канал. Это в целом позволяет повысить быстродействие устройства. 2 ил

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для селекции признаков объектов | 1988 |

|

SU1716551A1 |

| Устройство для приема и передачи информации | 1988 |

|

SU1573462A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| УСТРОЙСТВО ПОДКЛЮЧЕНИЯ ИСТОЧНИКОВ ИНФОРМАЦИИ К ОБЩЕЙ МАГИСТРАЛИ | 2001 |

|

RU2194301C2 |

| Многоканальный коммутатор | 1983 |

|

SU1086447A1 |

| Устройство для ввода информации | 1985 |

|

SU1290337A1 |

| Устройство для ввода информации | 1983 |

|

SU1157545A1 |

| Программируемый коммутатор | 1985 |

|

SU1287277A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА УПРАВЛЕНИЯ МАРШРУТИЗАЦИЕЙ ТЕКСТОВЫХ ДОКУМЕНТОВ В СЕТИ ОБРАБОТКИ ДАННЫХ | 2005 |

|

RU2282237C1 |

| Устройство для ввода информации от датчиков | 1983 |

|

SU1149241A1 |

Изобретение относится к автоматизированным системам управления, в частности к устройству для приема информации, и может быть использовано для построения каналов приема данных сложных АСУ. Цель изобретения - повышение быстродействия и информационной гибкости устройства путем селекции каналов с высокоприоритетными сообщениями и их внеочередным обслуживанием. Устройство содержит первый 1 и второй 2 блоки памяти, первый 3 и второй 4 регистры, дешифратор 5, коммутатор 6, элементы И 7 группы, первый 8, второй 9 и третий 10 элементы задержки, первый 11 и второй 12 элементы ИЛИ, первый 13 и второй 14 каналы селекции, в первом канале селекции - первый 15 и второй 16 триггеры первой группы, первый 17, второй 18 и третий 19 триггеры второй группы, первый 20, второй 21 и третий 22 элементы И, элемент ИЛИ 23, элемент задержки 24, во втором канале селекции - первый 25 и второй 26 триггеры первой группы, первый 27, второй 28 и третий 29 триггеры второй группы, первый 30, второй 31 и третий 32 элементы И, элемент ИЛИ 33, элемент задержки 34. Устройство позволяет обслужить информационный канал с более высоким приоритетом поступившего сообщения в первую очередь, а затем, при наличии в другом канале сообщения с менее высоким приоритетом, обслужить другой информационный канал. Это в целом позволяет повысить быстродействие устройства. 2 илл.

Изобретение относится к автоматизированным системам управления, в частности к устройству для приема информации, и может быть использова- но для построения каналов приема данных сложных АСУ.

Цель изобретения - повьшение быстродействия и информационной гибкости устройства путем селекции каналов с высокоприоритетными сообщениями и их внеочередным обслуживанием.

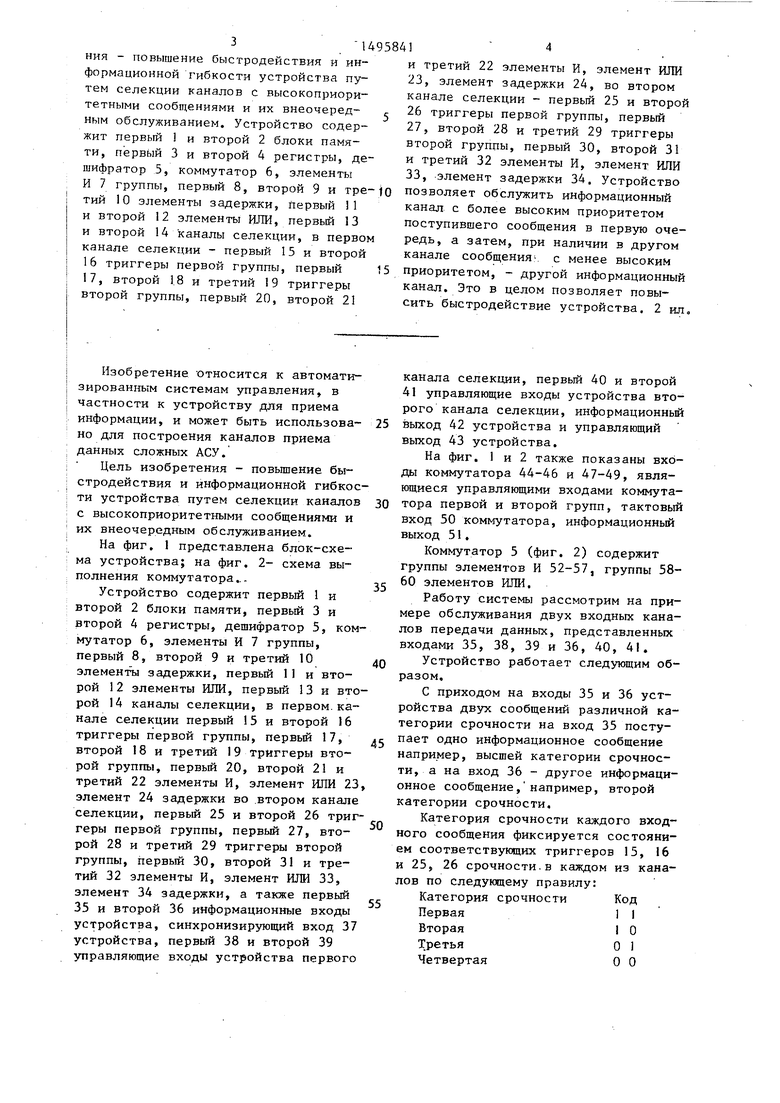

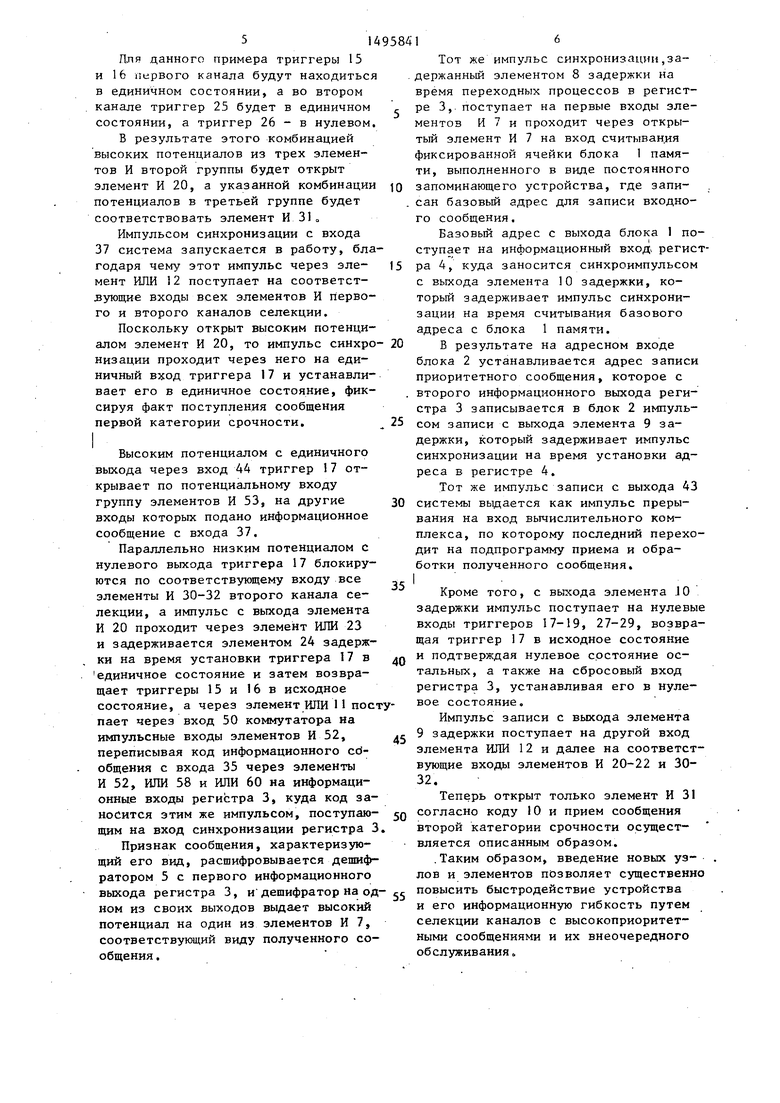

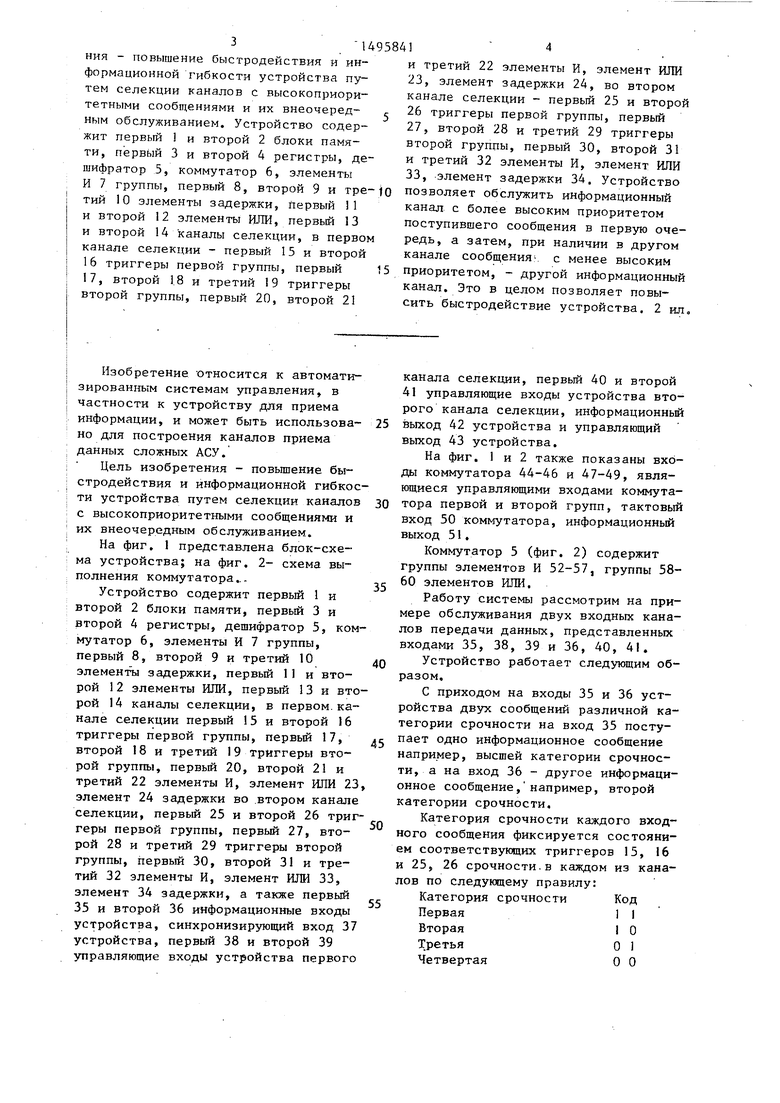

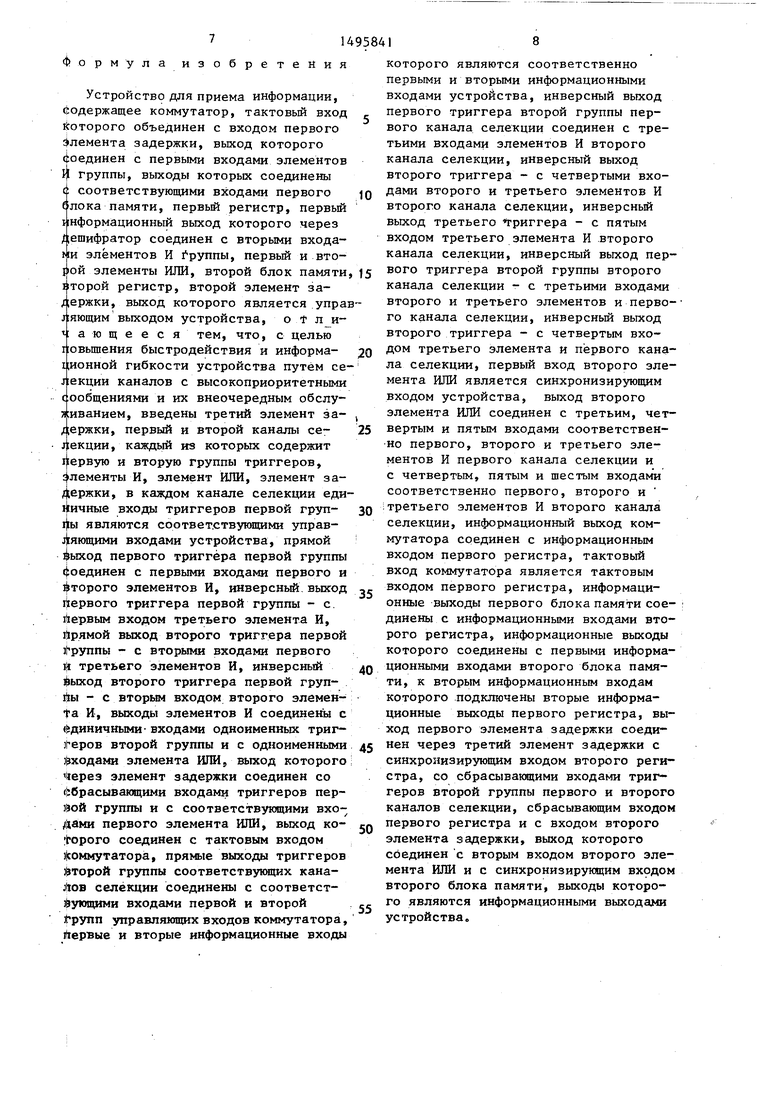

На фиг. 1 представлена блок-схема устройства; на фиг. 2- схема выполнения коммутатора...

Устройство содержит первый 1 и второй 2 блоки памяти, первый 3 и второй 4 регистры, дешифратор 5, коммутатор 6, элементы И 7 группы, первый В, второй 9 и третий 10 элемента задержки, первый 11 и второй 12 элементы ИЛИ, первый 13 и второй 14 каналы селекции, в первом, канале селекции первый 15 и второй 16 триггеры первой группы, первый 17, второй 18 и третий 19 триггеры второй группы, первый 20, второй 21 и третий 22 элементы И, элемент ШТИ 23 элемент 24 задержки во .втором канале селекции, первый 25 и второй 26 триггеры первой группы, первый 27, второй 28 и третий 29 триггеры второй группы, первый 30, второй 31 и третий 32 элементы И, элемент ИЛИ 33, элемент 34 задержки, а также первый 35 и второй 36 информационные входы устройства, синхронизирующий вход 37 устройства, первый 38 и второй 39 управляющие входы устройства первого

5

О

0

0

канала селекции, первый 40 и второй 41 управляющие входы устройства второго канала селекции, информационный выход 42 устройства и управляющий выход 43 устройства.

На фиг. 1 и 2 также показаны входы коммутатора 44-46 и 47-49, являющиеся управляющими входами коммутатора первой и второй групп, тактовый вход 50 коммутатора, информационный выход 51.

Коммутатор 5 (фиг. 2) содержит группы элементов И 52-57, группы 58- 60 элементов ИЛИ,

Работу системы рассмотрим на примере обслуживания двух входных каналов передачи данных, представленных входами 35, 38, 39 и 36, 40, 41.

Устройство работает следующим образом.

С приходом на входы 35 и 36 устройства двух сообщений различной категории срочности на вход 35 поступает одно информационное сообщение например, высшей категории срочности, а на вход 36 - другое информационное сообщение, например, второй категории срочности.

Категория срочности каждого входного сообщения фиксируется состоянием соответствующих триггеров 15, 16 и 25, 26 срочности-В каждом из каналов по следующему правилу:

Категория срочности Код ПерваяII

ВтораяI О

ТретьяО 1

ЧетвертаяО О

514

Лля данного примера триггеры 15 и 16 первого канала будут находиться в единичном состоянии, а во втором канале триггер 25 будет в единичном состоянии, а триггер 26 - в нулевом.

В результате этого комбинацией высоких потенциалов из трех элементов И второй группы будет открыт элемент И 20, а указанной комбинации потенциалов в третьей группе будет соответствовать элемент И ЗК

Импульсом синхронизации с входа 37 система запускается в работу, благодаря чему этот импульс через эле- мент ИЛИ 12 поступает на соответствующие входы всех элементов И первого и второго каналов селекции.

Поскольку открыт высоким потенциалом элемент И 20, то импульс синхро- низации проходит через него на единичный вход триггера 17 и устанавливает его в единичное состояние, фиксируя факт поступления сообщения первой категории срочности,

Высоким потенциалом с единичного выхода через вход 44 триггер 17 открывает по потенциальному входу группу элементов И 53, на другие входы которых подано информационное сообщение с входа 37.

Параллельно низким потенциалом с нулевого выхода триггера 17 блокируются по соответствующему входу все элементы И 30-32 второго канала селекции, а импульс с выхода элемента И 20 проходит через элемент ИЛИ 23 и задерживается элементом 24 задерж ки на время установки триггера 17 в единичное состояние и затем возвращает триггеры 15 и 16 в исходное состояние, а через элемент ИЛИ 11 поспает через вход 50 коммутатора на импульсные входы элементов И 52, переписывая код информационного cd- общения с входа 35 через элементы И 52, ШШ 58 и ИЛИ 60 на информационные входы регистра 3, куда код заносится этим же импульсом, поступаю- щим на вход синхронизации регистра 3

Признак сообщения, характеризующий его вид, расшифровывается дешифратором 5 с первого информационного

выхода регистра 3, и дешифратор на од- ееповысить быстродействие устройства

ном из своих выходов выдает высокийи его информационную гибкость путем

потенциал на один из элементов И 7,селекции каналов с высокоприоритетсоответствующий виду полученного со-ными сообщениями и их внеочередного

общения.обслуживания.

Q

5

0 5

О

Q

5

0

Тот же импульс синхронизации,за- .держанный элементом 8 задержки на время переходных процессов в регистре 3,- поступает на первые входы элементов И 7 и проходит через открытый элемент И 7 на вход считывания фиксированной ячейки блока 1 памяти, выполненного в виде постоянного запоминающего устройства, где запи- . сан базовый адрес для записи входного сообщения.

Базовый адрес с выхода блока 1 поступает на информационный вход регистра 4, куда заносится синхроимпульсом с выхода элемента 10 задержки, который задерживает импульс синхронизации на время считывания базового адреса с блока 1 памяти.

В результате на адресном входе блока 2 устанавливается адрес записи приоритетного сообщения, которое с . второго информационного выхода регистра 3 записывается в блок 2 импульсом записи с выхода элемента 9 задержки, который задерживает импульс синхронизации на время установки адреса в регистре 4.

Тот же импульс записи с выхода 43 системы выдается как импульс прерывания на вход вычислительного комплекса, по которому последний переходит на подпрограмму приема и обработки полученного сообщения. I .

Кроме того, с выхода элемента .10

задержки импульс поступает на нулевые входы триггеров 17-19, 27-29, возвращая триггер 17 в исходное состояние и подтверждая нулевое состояние остальных, а также на сбросовьш вход регистра 3, устанавливая его в нулевое состояние.

Импульс записи с выхода элемента 9 задержки поступает на другой вход элемента ШШ 12 и далее на соответствующие входы элементов И 20-22 и 30- 32.

Теперь открыт только элемент И 31 согласно коду 10 и прием сообщения второй категории срочности осуществляется описанным образом.

.Таким образом, введение новых узлов и элементов позволяет существенно

7149584

Формула изобретения

Устройство для приема информации, содержащее коммутатор, тактовый вход Которого объединен с входом первого Элемента задержки, выход которого фоединен с первыми входами элементов IJI группы, выходы которых соединены и соответствующими входами первого (лока памяти, первьй регистр, первьй 1 нформационный выход которого через / ещифратор соединен с вторыми входа- rи элементов И 1 руппы, первый и второй элементы ИЛИ, второй блок памяти торой регистр, второй элемент задержки, выход которого является управ J;яющим выходом устройства, о Т л и- 1:ающееся тем, что, с целью 1:овьщ1ения быстродействия и информа- 1 ионной гибкости устройства путём се- д:екции каналов с высокоприоритетными с ообщениями и их внеочередным обслу- л;иванием, введены третий элемент за- ;;ержки, первый и второй каналы се- ; екции, каждый из которых содержит 1 ервую и вторую группы триггеров, Элементы И, элемент ИЛИ, элемент за- Держки, в каждом канале селекции еди- 1|гичные входы триггеров первой груп- 1|1ы являются соответствующими управ- ; яющими входами устройства, прямой ыход первого триггера первой группы Соединен с первыми входами первого и фторого элементов И, инверсный выход первого триггера первой группы - с. йервым входом третьего элемента И, йрямой выход второго триггера первой зНруппы - с вторыми входами первого и третьего элементов И, инверсный $ыход второго триггера первой груп- йы - с вторым входом второго элемен- ta И, выходы элементов И соединены с Единичными-входами одноименных триг- ihepoB второй группы и с одноименными кодами элемента ИЛИ, выход которого элемент задержки соединен со Сбрасывающими входами триггеров пер- йой группы и с соответствующими входами первого элемента ИЛИ, выход ко- Дорого соединен с тактовым входом Коммутатора, прямые выходы триггеров йторой группы соответствукяцих кана- Лов селекции соединены с соответствующими входами первой и второй Л рупп управляншщх входов коммутатора, iliepBue и вторые информационные входы

8

которого являются соответственно первыми и вторыми информационными входами устройства, инверсный выход первого триггера второй группы первого канала селекции соединен с третьими входами элементов И второго канала селекции, инверсный выход второго триггера - с четвертыми входами второго и третьего элементов И второго канала селекции, инверсный выход третьего григгера - с пятым входом третьего элемента И .второго канала селекции, инверсный выход первого триггера второй группы второго канала селекции - с третьими входами второго и третьего элементов и первого канала селекции, инверсный выход второго триггера - с четвертым входом третьего элемента и первого канала селекции, первый вход второго элемента ИЛИ является синхронизирующим входом устройства, выход второго элемента ИЛИ соединен с третьим, четвертым и пятым входами соответственно первого, второго и третьего элементов И первого канала селекции и с четвертым, пятым и шестым входами соответственно первого, второго и третьего элементов И второго канала селекции, информационный выход коммутатора соединен с информационным входом первого регистра, тактовый вход коммутатора является тактовым входом первого регистра, информационные выходы первого блока памяти соединены с информационными входами второго регистра, информационные выходы которого соединены с первыми информационными входами второго блока памяти, к вторым информационным входам которого подключены вторые информационные выходы первого регистра, выход первого элемента задержки соединен через третий элемент задержки с синхронизирующим входом второго регистра, со сбрасывающими входами триггеров второй группы первого и второго каналов селекции, сбрасывающим входом первого регистра и с входом второго элемента задержки, выход которого соединен с вторым входом второго элемента ИЛИ и с синхронизирующим входом второго блока памяти, выходы которого являются информационными выходами устройства.

Составитель В.Струков Редактор А.Шандор Техред Л.Олийнык

Заказ 4273/49

Тираж 518

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Фиаг

Корректор Э.Лончакова

Подписное

| Устройство для приема и передачи информации | 1984 |

|

SU1203569A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1989-07-23—Публикация

1987-11-11—Подача