00 CD СП

ел

со

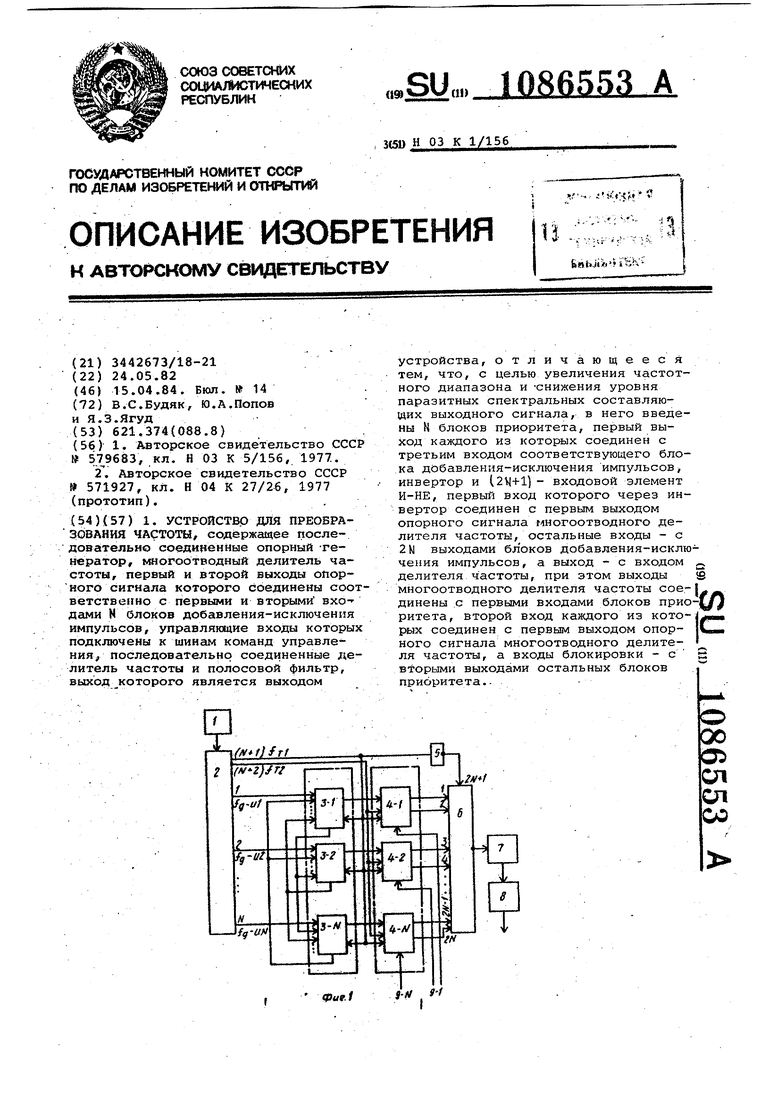

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фазовой синхронизации | 1983 |

|

SU1149425A2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2012 |

|

RU2480823C1 |

| Умножитель частоты | 1978 |

|

SU769714A1 |

| СПОСОБ ОБСЛУЖИВАНИЯ РАЗНОПРИОРИТЕТНЫХ ЗАПРОСОВ АБОНЕНТОВ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 2001 |

|

RU2179737C1 |

| Устройство для формирования сигналов частотной телеграфии | 1977 |

|

SU613517A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| СПОСОБ ОБСЛУЖИВАНИЯ ЗАПРОСОВ ПОЛЬЗОВАТЕЛЕЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ (ВАРИАНТЫ) | 1998 |

|

RU2140666C1 |

| Резервированное многоканальное устройство | 1981 |

|

SU1058098A1 |

| Способ фазовой привязки генерируемой последовательности импульсов к импульсу внешнего запуска | 2022 |

|

RU2785070C1 |

| Устройство для формирования сигналов двухчастотной и четырехчастотной телеграфии | 1977 |

|

SU678708A2 |

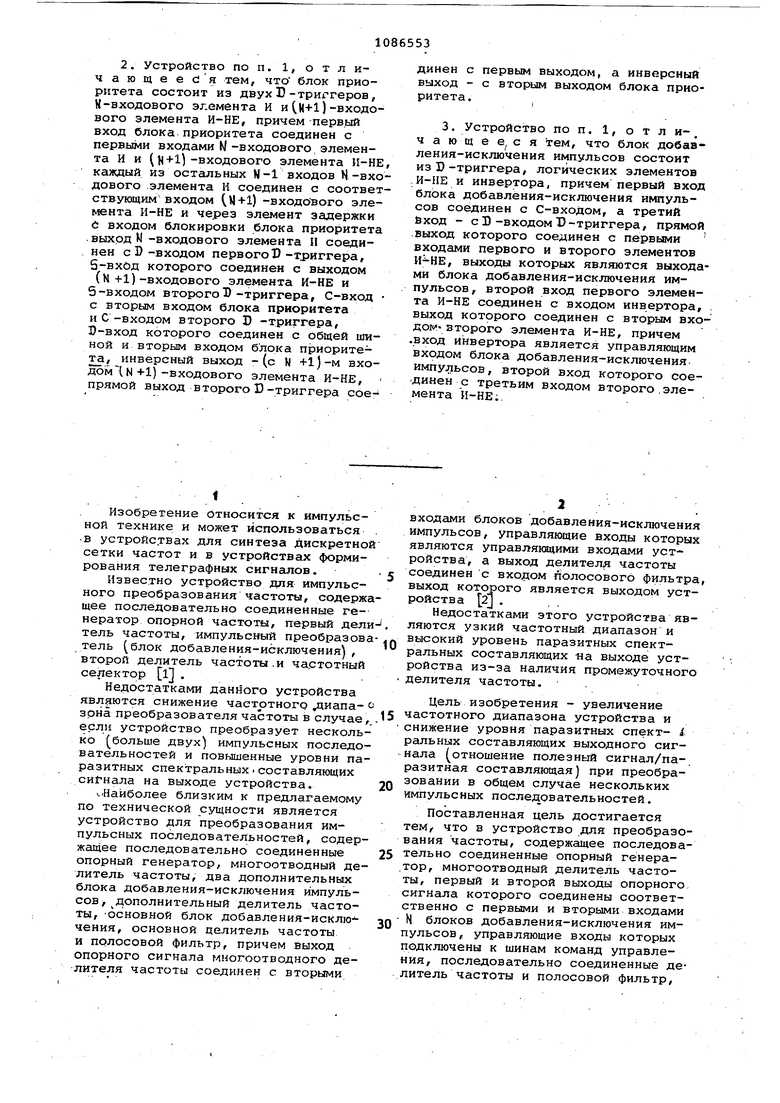

1. УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧАСТОТЫ, содержащее последовательно соединенные опорный -генератор, многоотводный делитель частоты, первый и второй выходы опорного сигнала которого соединены соответственно с первыми и вторыми входами Н блоков добавления-исключения импульсов, управлягацие входы которых подключены к шинам команд управления, последовательно соединенные делитель частоты и полосовой фильтр, выход которого является выходом устройства ,отличающееся тем, что, с целью увеличения частотного диапазона и -снижения уровня паразитных спектральных составляющих выходного сигнала, в него введены К блоков приоритета, первый выход каждого из которых соединен с третьим входом соответствующего блока добавления-исключения импульсов, инвертор и 12VJ+1) - входовой элемент И-НЕ, первый вход которого через инвертор соединен с первым выходом опорного сигнала многоотводного делителя частоты, остальные входы - с 2Ы выходами блоков добавления-исключения импульсов, а выход - с входом .-j делителя частоты, при этом выходы S многоотводного делителя частоты сое-1 динены с первыми входами блоков прио- Гу ритета, второй вход каждого из кото-j JP, рых соединен с первым выходом опор- {|«ш ного сигнала многоотводного делите- ля частоты, а входы блокировки - с S вторыми выходами остальных блоков приоритета.

puf.lS-ff .

Изобретение относится к импульсной технике и может использоваться в устройствах для синтеза дискретной сетки частот и в устройствах формирования телеграфных сигналов.

Известно устройство для импульсного преобразования частоты, содержащее последовательно соединенные генератор опорной частоты, первый дели тель частоты, импульсный преобразова тель (блок добавления-исключения), второй делитель частоты.и частотный селектор ij .

Недостатками данного устройства являются снижение частотного 1иапазрна преобразователя частоты в случае, если устройство преобразует несколько больше двух) импульсных последовательностей и повышенные уровни паразитных спектральных.составляющих сигнала на выходе устройства.

.Наиболее близким к предлагаемому по технической сущности является устройство для преобразования импульсных последовательностей, содержащее последовательно соединенные опорный генератор, многоотводный делитель частоты, два дополнительных блока добавления-исключения импульсов дополнительный делитель частоты, -основной блок добавления-исключения, ОСНОВНОЙ целитель частоты и полосовой фильтр, причем выход опорного сигнала многоотводного делителя частоты соединен с вторыми

динен с первым выходом, а инверсный выход - с вторым выходом блока приоритета.

входами блоков добавления-исключения импульсов, управляющие входы которых являются управлякядими входами устройства, а выход делител,я частоты соединен с входом полосового фильтра выход которого является выходом устройства 2 .

Недостатками этого устройства являются узкий частотный диапазон и высокий уровень паразитных спектральных составляющих «а выходе устройства из-за наличия промежуточного делителя частоты.

Цель изобретения - увеличение частотного диапазона устройства и снижение уровня паразитных спект- 1 ральных составляющих выходного сигнала (отношение полезный сигнал/па-, разитная составляющая) при преобразовании в общем случае нескольких импульсных последовательностей.

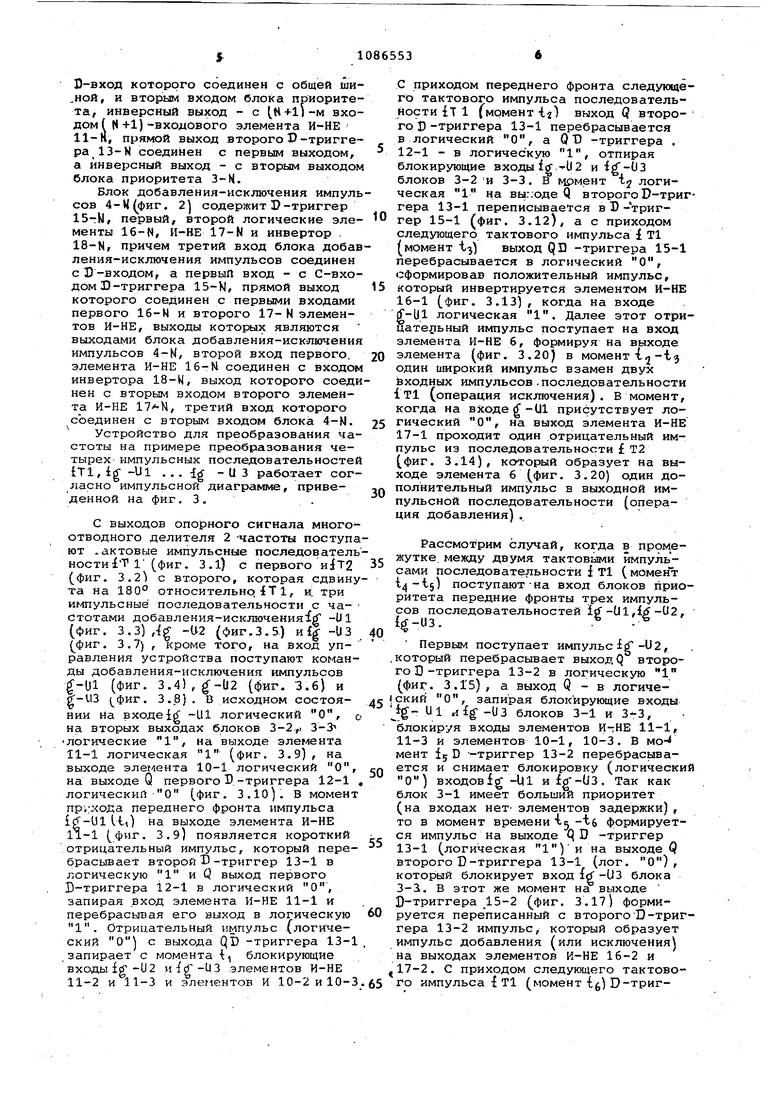

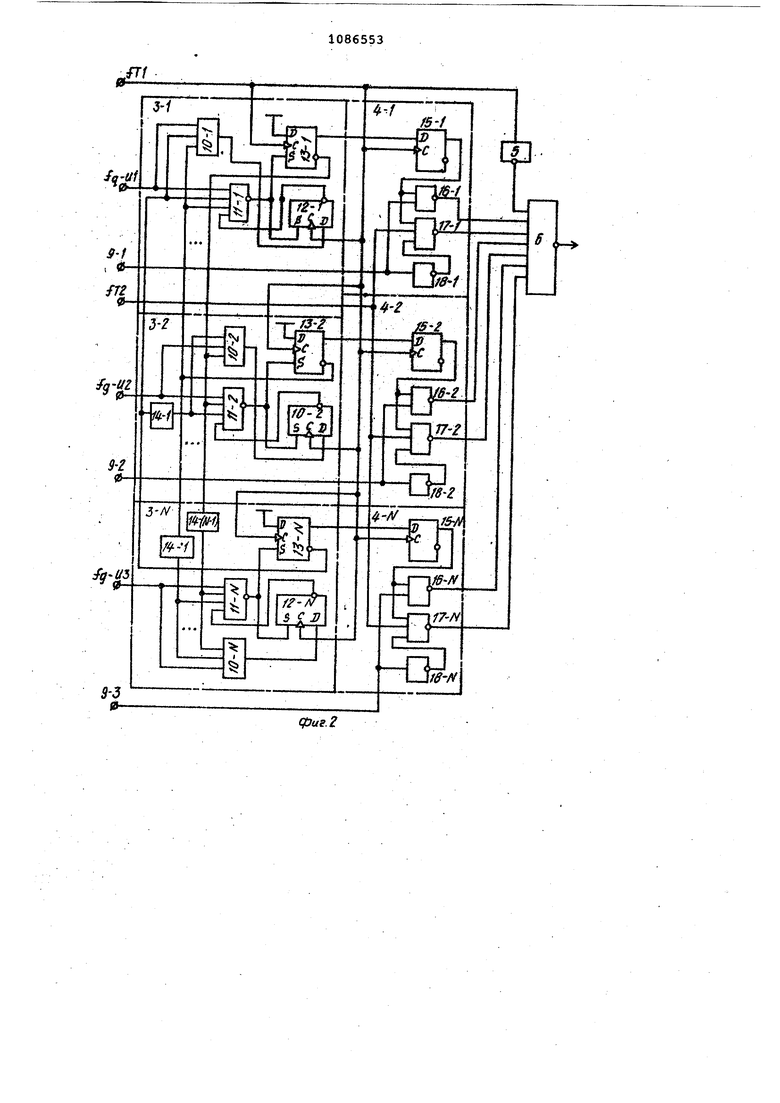

Поставленная цель достигается тем/ что в устройство для преобразования частоты, содержащее последовательно соединенные опорный гёнера.тор, многоотводный делитель частоты, первый и второй выходы опорного, сигнала которого соединены соответственно с первыми и вторыми входами К блоков добавления-исключения импульсов , управляющие входы которых подключены к шинам команд управления, последовательно соединенные делитель частоты и полосовой фильтр. выход которого является выходом ycTройства, введены N блоков приоритета, первый выход каждого из которых соединен с. третьим входом соответст вукяцего блока добавления-исключения импульсов, инвертор и (2Ц+1)-входовой элемент И-НЕ, первый вход которого через инвертор соединен с первым опорного сигнала много отводного делителя частоты, остальные входы - с 2 N выходами блоков добгюления-исключения импульсов, а выход - с входом делителя частоты, при этом выходы многоотводного делителя частоты соединены с первыми входами блоков приоритета, второй Вход каждого из которых соединен с первым выходом опорного сигнала мно гоотводного делителя частоты, а входы блокировки - с вторьа«4и выходами остальных блоков приоритета. При этом блок приоритета состоит из двух) -триггеров, N -входового элемента И и (N+1 -входового элемен та Ы-НЕ, причем первый вход блока приоритета соединен с первыми входами N-входового элемента И и (Ц +1) входового элемента И-НЕ, каждый иэ остальных Н-1 входов Ч-входового элемента К соединен с соответствующим входом (N+I)-входового элемента И-НЕ и через элемент задержки с вхо дом блокировки блока приоритета, йы ход М-входового элемента И соединен с В-входом первогоБ -триггера, S-вход которого соединен с выходом (Ы +1 -входового элемента И-НЕ и 5-входом второго)-триггера, С-вход соединен с вторыг входом блока прио ритета и с С-входом второго) -триггера, D -зход которого соединен с. общей шиной и вторым входом блока приоритета, инверсный выход - с (Н +1)-м входом (N+1 -входовогр„. элемента И-НЕ, прямой выход второго D-триггера соединен с первым выходо а инверсный выход - с вторым выходом блока приоритета. Кротле того, блок добавления-исклк чения импульсов состоит изD-триггера, логических элементдв И-НЕ и инве тора, причем первый вход блока добав ления-исключения импульсов соединен с С-входом, а третий вход - сD-входом D-триггера, прямой выхбд которого соединен с первыми входами первого и .второго элементов И-НЁ, выходы которых являются выходами блока добавления-исключения импульсов, вто ,рой вход первого элемента И-НЕ соеди нен с входом инвертора, выход которого соединен с вторьм входом второго элемента И-НЕ, причем вход является управляющим входом блока /хобавления-исключения импульсов, второй вход которого соединен с третьим входом второго элемента И-НЕ. . На фиг. 1 представлена структурная электрическая схема устройства для преобразования частоты; на фиг,2принципиальная электрическая схема блоков приоритеола и блоков добавле ния-искдпочения импульсов Гдля Ц-3) ; на фиг. 3 - временныедиаграммы, поясняющие работу устройства. Устройство для преобразования частоты (фиг. 1 состоит из опорного генератора 1, многоотводного делителя 2 частоты, W блоков приоритета |3-1, ...,. 3-,К,М блоков добавленияисключения илшуль(ов 4-1, ..., 4-И, инвертора 5, (2Н+1)-входового элемента И-НЕ б, делителя 7 частоты, полЬсового фильтра 8, причем выход опорttofo генератора 1 соединен с входом многоотводного делителя 2 частоты, Ц-выходов которого соединены соответственно с первыми входами/ч блоков 3-1, ..., 3-М, выходы блоков 4-1 - 4-U соответственно соединены с 2М-в5:одами элемента И-НЕ б, (2Н+1)-й вход которого соединен с выходом инвертора 5, вход которого соединен с первыми входами блоков 4-1, ..., 4-N добавления-исключения импульсов, вторыми входами блоков 3-1, ..., 3-N и первым выходом опорного сигнала многоотводного делителя 2 частоты, второй выход которого соединен с вторыми входами блоков 4-1-4-К, а входы блокировки каждого из блоков 3-1, ..., 3-N соединены с вторыми выходами остальных блоков приоритета 3-1,..., 3-У, управляющие входы блоков 4-1,..., 4-N соединены соответственно с шина ми 9-1 - 9-К команд управления -Ul, ...,tf -UN, выход элемента И-НЕ 6 через делитель 7 соединен с полосрвыц фильтром 8, выход которого яв.ляа.т.ся. выходом устройства. Блок приоритета 3- фиг. 2J содержит Н -входовой Логический элемент И 10-N, N +1У-ВХОДОВОЙ элемент ИНЕ 11,B-триггеры 12-)J, второй 13-N, (Н -1) элементов задержки 14-1, ..., , причем первый вход блока приоритета 3-N соединен с первыми входамиНвходового элемента И 10-М и Н+lV BJOflOBoro элемента И-НЁ 11-N остальные Н-1 входов N -входового элемента И 10-М соединены с соответствующими входами (Н +l)-входового элемента И-НЕ llni) и . элементы з адержки 14-1, . . . ,) с входами блокировки блока приб|)йтета 3-N, выход М-входового элемента И 10-N соединен с D-входом первого U-триггера 12-Н,5-вход которого соединен с выходом (М +1 -входового элемента И-НЕ 11-14 и5-входом второго D-триггера 13-К, С-вход соединен с С-входом второго D-триггера 13-N,

D-вход которого соединен с общей ши.ной, и вторым входом блока приоритета, инверсный выход - с М+1)-м входом ( Н +1) -входового элемента И-НЕ 11-Н, прямой выход второгоD-триггера 13- N соединен с первым выходом, а инверсный выход - с вторым выходом блока приоритета 3-Н.

Блок добавления-исключения импульсов 4-М(фиг. 2 содержитD-триггер 15-rW, первый, второй логические элементы 16-N, Н-НЕ 17-N и инвертор . 18-N, причем третий вход блока добавления-исключения импульсов соединен с D-входом, а первый вход - с С-входом 3)-триггера 15-VJ, прямой выход которого соединен с первыми входами первого 16-N и второго 17-Н элементов И-НЕ, выходы которых являются выходами блока добавления-исключения импульсов 4-N, второй вход первого, элемента И-НЕ 16-N соединен с входом инвертора 18-W, выход которого соединен с вторым входом второго элемента И-НЕ , третий вход которого соединен с вторым входом блока 4-N.

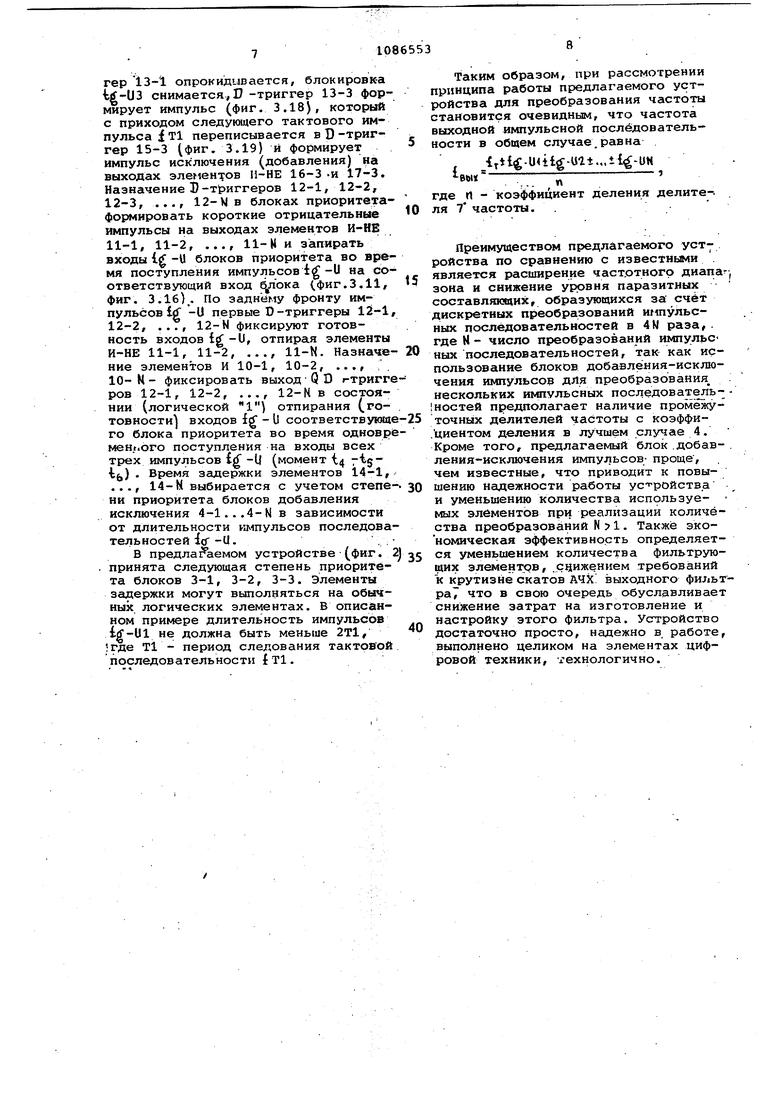

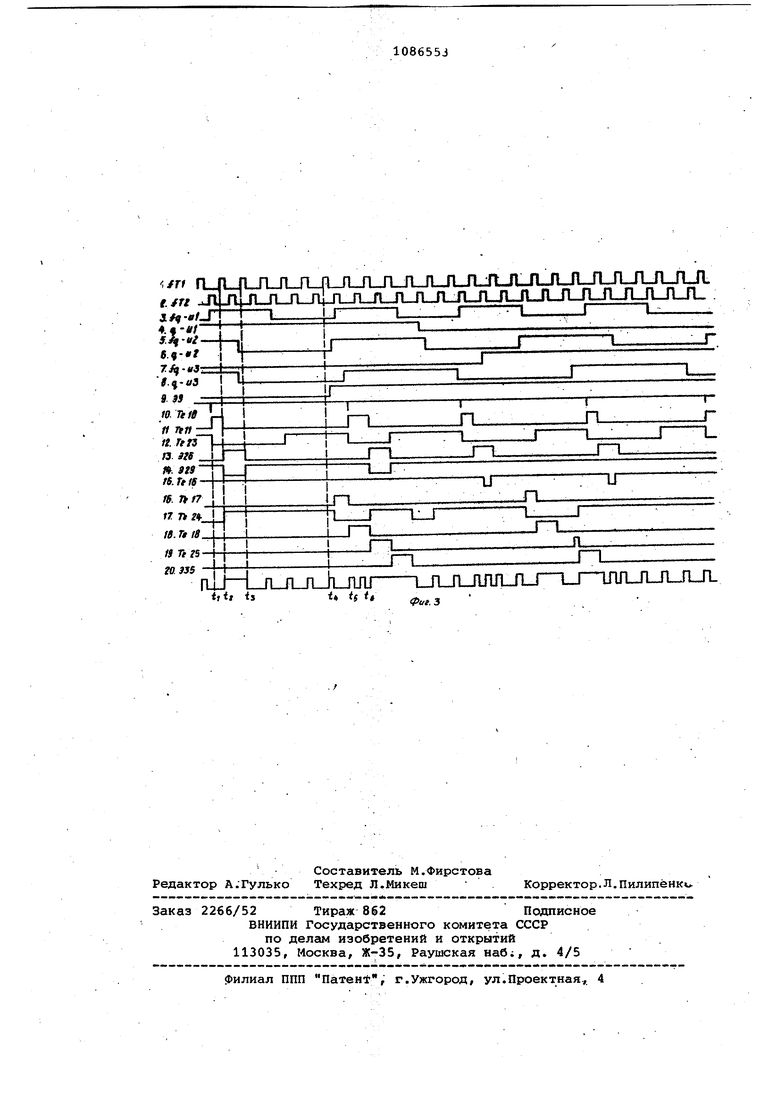

Устройство для преобразования частоты на примере преобразования четырех импульсных последовательностей {Tljig -Ul . . . Ig -из работает согласно импульсной диаграмме, приведенной на фиг, 3.

С выходов опорного сигнала многоотводного делителя 2 -частоты поступают .актовые импульсные последовательности Т1 (фиг. 3.1) с первого (фиг. 3.2 с второго, которая сдвинута на 180° относительнр iT 1, к. три и myльcныё последовательности с ча- Стотами добавления-исключения й -Ul (фиг. 3.3) ,-f -U2 (фиг.3.5) Kt -из (фиг. 3.7) , кроме того, на вход управления устройства поступают команды добавления-исключения импульсов -Ц (фиг. 3.4),g-a2 (фиг. 3.6) и -113 (фиг. 3.8). В исходном состоянии На входе -U1 логический О, о на вторых выходах блоков 3-2,j 3-3 Логические 1, на выходе элемента 11-1 логическая 1 (фиг. 3.9), на выходе элемента 10-1 логический О, на выходе Q первого D.-триггера 12-1 , логический О (фиг. З.Ю). В момент пр1:: ода переднего фронта импульса ig-(Jl (-li) на выходе элемента И-НЕ 11-1 (фиг. 3.9) появляется короткий отрицательный импульс, который перебрасывает второй Т)-триггер 13-1 в логическую 1 и Q выход первого D-триггера 12-1 в логический О, запирая вход элемента И-НЕ 11-1 и перебрасывая его выход в логическую 1. Отрицательный импульс {логический О) с выхода QI) -триггера 13-1 запирает с момента { блокирующие входы й-и2 н{0-из элементов И-НЕ 11-2 и 11-3 и элепентов И 10-2 и 10-3

С приходом переднего фронта следующего тактового импульса последовательности Т 1 (моментЧг) выход Q второго D-триггера 13-1 перебрасывается в логический О, а Q Т) -триггера . 12-1 - в логическую 1, отпирая блокирующие входы frf.02 и ig-{J3 блоков 3-2 И 3-3. В момент iy логическая 1 на выг.оде Q второго D-триггера 13-1 переписывается в D -триггер 15-1 (фиг. 3.12), а с приходом следующего тактового импульса f Т1 (момент 1з) выход QD -триггера 15-1 перебрасывается в логический О, сформировав положительный импульс, который инвертируется элементом И-НЕ 16-1 (фиг. 3.13), когда на входе -Ul логическая 1. Далее этот отрицатерьный импульс поступает на вход элемента И-НЕ 6, формируя на выходе элемента (фиг. 3.20) в момент i 3 один широкий импульс взамен двух йходных импульсов-последовательности 1т1 (операция исключения). В момент, когда на входе -Ul присутствует логический О, на выход элемента И-НЕ 17-1 проходит один отрицательный импульс из последовательности f Т2 (фиг. 3.14), который образует на выходе элемента 6 (фиг. 3.20) один дополнительный импульс в выходной импульсной последовательности (операция добавления).

Рассмотрим случай, когда в промежутке. между двумя тактовыми ймпульсами последовательности i Т1 (момент ) поступают-на вход блоков приоритета передние фронты трех импульсов последовательностей ,frf-02, {rf-U3..

Первым поступает импульсitf -U2, .который перебрасывает выход) второго D-триггера 13-2 в логическую 1 (фиг. 3.15) , а выход Q - в логиче ский О, запирая блокирующие входы U1 nfg -из блоков 3-1 и 3-3, блокируя входы элементов И-;НЕ 11-1, 11-3 и элементов 10-1, 10-3. В момент ij D -триггер 13-2 перебрасьшается и снимает блокировку (логический О) входов -Ill иfg--UЗ. Так как блок 3-1 имеет больший приоритет (на входах нет- элементов задержки), то в момент времени tj -tfe формируется импульс на выходе Я 2 -триггер

13-1 (логическая 1)и на выходе Q второго D-триггера 13-1 (лог. О) который блокирует вход itf -U3 блока 3-31. В этот же момент на выходе D-триггера 15-2 (фиг. 3.1) формируется переписанный с второгоD-триггера 13-2 импульс, который образует импульс добавления (или исключения) на выходах элементов И-НЕ 16-2 и 17-2. С приходом следующего тактового импульса { Т1 (момент-t) D-тригrep 13-1 опрокидывается, блокировка снимается,D -триггер 13-3 формирует импульс (фиг. 3.18), который с приходом следующего тактового импульса i Tl переписывается в D-триггер 15-3 (фиг. 3.19) и формирует импульс исключения (добавления) а выходах элементов И-НЕ 16-3 -и 17-3. Назначение D-Tt HrrepoB 12-1, 12-2, 12-3, ..., 12-VI в блоках приоритетаформировать короткие отрицательные импульсы на выходах элементов И-НВ 11-1, 11-2, ..., 11-К и запирать входы {.f -U блоков приоритета во время поступления импульсов на соответствующий вход ока (фиг.3.11, фиг. 3.1б). По заднему фронту импульсов -и первые D-триггеры 12-1 12-2, ..., 12-N фиксируют готовность входов -U, отпирая элементы И-НБ 11-1, 11-2, ..., 11-N. Назначение элементов И 10-1, 10-2, ..,, Г. 10-М - фиксировать выход Q D г-тригге ров 12-1, 12-2, ..., 12-N в состоянии (логической 1) отпирания (готовности входов f - и соответствующе го блока приоритета во время одновре мен;.ого поступления на входы всех трех импульсов -U (момент t4 7% tj,) . Время задержки элементов 14-1, ..., 14-М выбирается с учетом степени приоритета блоков добавления исключения 4-1...4-N в зависимости от длительности импульсов последовательностей io -U. В предлагаемом устройстве (фиг. 2 принята следующая степень приоритета блоков 3-1, 3-2, 3-3. Элементы задержки могут выполняться на обычных логических элементах. В описанном примере длительность импульсов ig-Ul не должна быть меньше 2Т1, где Т1 - период следования тактовой последовательности {Т1. Таким образом, при рассмотрении принципа работы предлагаемого устройства для преобразования частоты становится очевидным, что частота выходной импульсной последовательности в общем случае,равна 1 { -ш л -лг±,., 1, . , где И - коэффициент деления делите-ля 7 частоты. . Преимуществом предлагаемого устройства по сравнению с известными . является расширение част.отногр диапа, зона и снижение уровня паразитных составляющих, образующихся за счёт дискретных преобразований импульсных последовательностей в 4Ы раза, где М- число преобразований импульсных последовательностей, так как использование блоков добавления-исключения импульсов для преобразования нескольких импульсных посдедователь- ностей предполагает наличие промежуточных делителей частоты с коэффициентом деления в лучшем случае 4. Кроме того, предлагаемый блок.добав- . ления-исключения импульсов- проще, чем известные, что приводит к повышению надежности работы устройства и уменьшению количества испольэуе- мых элементов при реализации количества преобразований N 1. Также экономическая эффективность определяется уменьшением количества фильтрующих элементов, .сцижением требований к крутизне скатов АЧХ выходного фильтра7 что в свою очередь обуславливает снижение затрат на изготовление и настройку этого фильтра. Устройство достаточно просто, надежно в работе, выполнено целиком на элементах цифровой техники, технологично.

Авторы

Даты

1984-04-15—Публикация

1982-05-24—Подача