2. Устройство по п. 1, отличающееся тем, что блок фазирования содержит RS-триггер, первый, второй и третий элементы И, дешифратор и инвертор, вход которого и первый вход третьего элемента И являются первым входом блока фазирования, вторым входом которого является первый вход первого элемента И, к второму входу которого подключен выход RS-триггера, к входам S и R

которого подключены соответственно выходы второго и третьего элементов И, при этом выход инвертора подключен к первому входу второго элемента И, к второму входу которого и второму входу третьего элемента И подключен выход дешифратора, вход которого является третьим входом блока фазирования, выходом которого является выход первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фазовой синхронизации | 1982 |

|

SU1062879A1 |

| Устройство формирования синхронизирующих последовательностей | 1982 |

|

SU1166331A1 |

| Видеорегенератор для систем связи с импульсно-кодовой модуляцией | 1977 |

|

SU792603A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1774497A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Резервированный генератор импульсов | 1989 |

|

SU1619440A1 |

| Устройство фазовой автоподстройки частоты | 1979 |

|

SU930695A1 |

| Устройство для импульсного регулиро-ВАНия фАзОВОгО пОлОжЕНия POTOPA СиН-ХРОННОгО элЕКТРОдВигАТЕля | 1979 |

|

SU817960A1 |

| Устройство тактовой синхронизациии РЕгЕНЕРАции | 1979 |

|

SU809620A1 |

| Устройство дискретной фазовой автоподстройки частоты | 1980 |

|

SU866771A1 |

1. УСТРОЙСТВО ДЛЯ ФАЗОВОЙ СИНХРОНИЗАЦИИ по авт. св. № 1062879, отличающееся тем, что, с целью повышения точности фазовой синхронизации путем определения истинных значений фазы принимаемого сигнала, в него введены блок формирования импульса установки, блок фазирования, блок дискретной автоподстройки фазы, одновибратор, делитель частоты и элемент ЗИ, к первому входу которого, а также к первым входам блока формирования импульса установки и блока фазирования подключен выход мультиплексера, к. второму входу элемента ЗИ через одновибратор подключен выход элемента ИЛИ, а к третьему входу элемента ЗИ подключен выход синхронизатора, при этом выход задающего генератора подключен к первому входу блока дискретной автоподстройки фазы и к второму входу блока формирования импульса установки и через делитель частоты - к входу линии задержки и третьему входу блока формирования импульса установки, выход которого подключен к второму входу блока фазирования, выход которого подключен к второму входу блока дискретной автоподстройки фазы, выход которого подключен к третьему входу блока фазирования, а к третьему входу блока дискретной автоподстройки фазы подключен выход элемента ЗИ. ;О ю ел

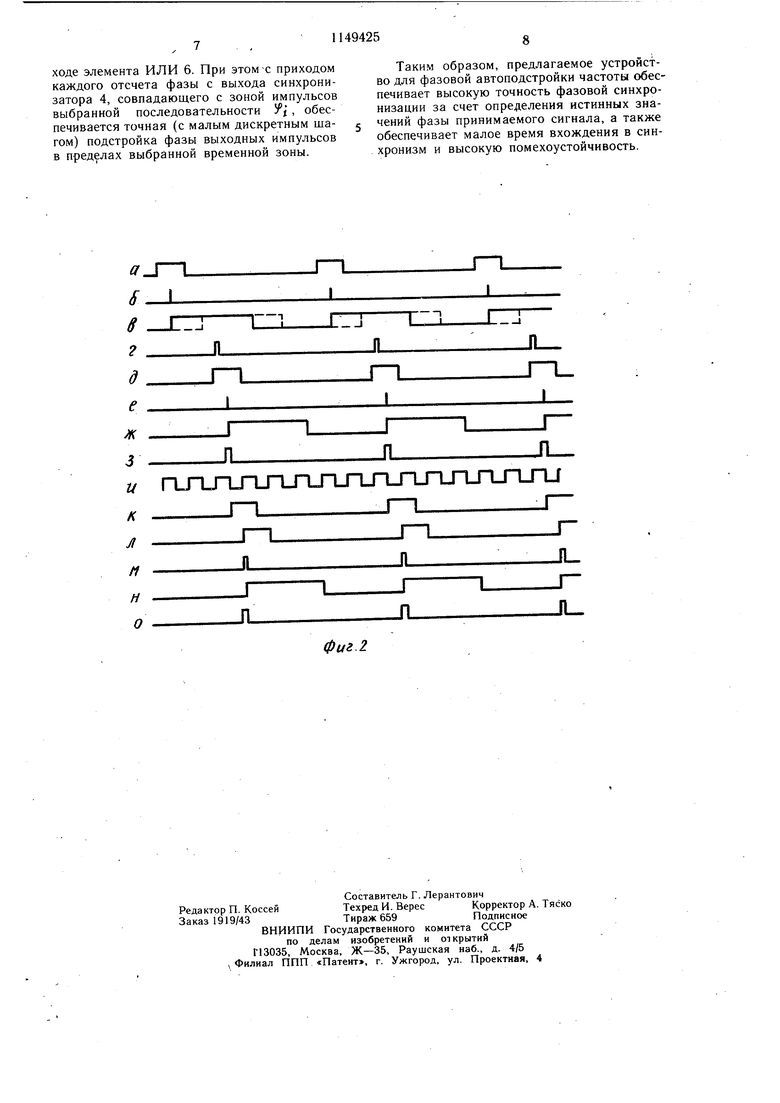

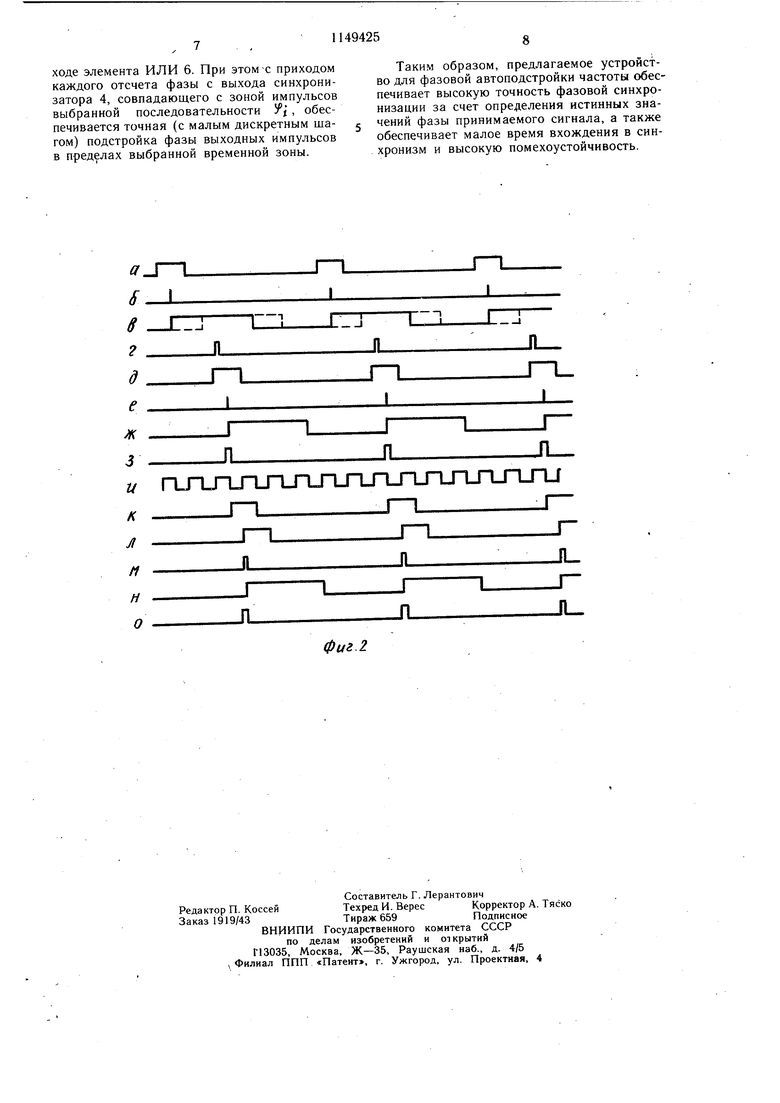

Изобретение относится к электросвязи и может использоваться для выделения тактовой частоты из принимаемого дискретного сигнала. По основному авт. св. № 1062879 известно устройство для фазовой синхронизации, содержашее задаюший генератор и линию задержки, выходы которой соединены со входами мультиплексора и соответственно с первыми входами элементов И, выходы которых подключены к соответствуюш,им входам блока счетчиков, выходы которого соединены соответственно со входами блока памяти и входами элемента ИЛИ, выход которого соединен с первым входом счетчика и управляющим входом блока памяти, выход которого соединен с управляющим входом мультиплексора, а выход синхронизатора соединен со вторыми входами элементов И и вторым входом счетчика, выход которого соединен с управляющим входом блока счетчиков, при этом выход задающего генератора подключен ко входу линии задержки 1. Однако известное устройство обладает низкой точностью фазовой синхронизации. Цель изобретения - повышение точноети фазовой синхронизации путем определения истинных значений фазы принимаемого сигнала. Цель достигается тем, что в устройство для фазовой синхронизации, содержащее задающий генератор и линию задержки, выходы которой соединены с входами мультиплексора и соответственно с первыми входами элементов И, выходы которых подклю„. чены к соответствующим входам блока счетчиков, выходы которого соединены соответственно со входами блока памяти и входами элемента ИЛИ, выход которого соединен с первым входом счетчика, и управляющим входом блока памяти, выход которого соединен с управляющим входом мультиплексора, а выход синхронизатора соединен со вторыми входами элементов И и вторым-входом счетчика, выход которого соединен с управляющим входом блока счетчиков, введены блок формирования импульса установки, блок фазирования, блок дискретной автоподстройки фазы, одновибратор, делитель частоты и элемент ЗИ, к первому входу которого, а также к первым входам блока формирования импульса установки и блока фазирования подключен выход мультиплексера, к второму входу элемента ЗИ через одновибратор подключен выход элемента ИЛИ, а к третьему входу элемента ЗИ подключен выход синхронизатора, при этом выход задающего генератора подключен к первому входу блока дискретной автоподстройки фазы и к второму входу блока формирования импульса установки и через делитель частоты - к входу линии задержки и третьему входу блока формирования импульса установки, выход которого подключен к второму входу блока фазирования, выход которого подключен к второму входу блока дискретной автоподстройки фазы, выход которого подключен к третьему входу блока фазирования, а к третьему входу блока дискретной автоподстройки фазы подключен выход элемента ЗИ. При этом блок фазирования содержит RS-триггер, первый, второй и третий -элементы И, дешифратор и инвертор, вход которого и первый вход третьего элемента И являются первым 1входом блока фазирования вторым входом которого является первый, вход первого элемента И, к второму входу которого подключен выход RS-триггера, к входам S и R которого подключены соответствующие выходы второго и третьего элементов И, при этом выход инвертора подключен к первому входу второго элемента И, к второму входу которого и второму входу третьего элемента И подключен выход дешифратора, вход которого яв ияется третьим входом блока фазирования, выходом которого является выход первого элемента И. На фиг. 1 представлена структурная электрическая схема устройства; на фиг. 2 - импульсные диаграммы, поясняющие его работу. Устройство для фазовой синхронизации содержит задающий генератор 1, линию 2 задержки, элементы И 3, синхронизатор 4, 5, элемент ИЛИ 6, блок 7 счетчиков, блок 8 памяти, мультиплексер 9, делитель 10 частоты, блок 11 дискретной автоподстройки фазы, содержащий элемент 12 добавления-вычитания, делитель 13 частоты, фазовый детектор 14, реверсивный счетчик 15, блок 16 формирования импульса установки, блок 17, фазирования, элемент ЗИ 18, одновибратор 19, блок 17 фазирования содержит первый элемент И 20, RS-триггер 21, второй и третий элементы И 22 и 23, инвертор 24, дешифратор 25 блок 16 формирования импульса установки содержит инвертор 26, D-триггеры 27 и 28, элемент И 29. Устройство для фазовай синхронизации работает следующим образом. Последовательность импульсов с выхода .задающего генератора 1 через делитель 10 частоты поступает на вход линии 2 задержки, которая может быть выполнена на регистре сдвига. Последовательности fi,z,, на отводах линии задержки 2 сдвинуты по фазе друг относительно друга на величину € , равную длительности импульсов последоваJeльнocти Ifj . При этом период следования Т импульсов последовательности должен соответствовать длительности тактового интервала передаваемого дискретного сигнала, а число используемых отводов линии 2 задержки должно быть равно величине 1 v Элементы И 3 обеспечивают подключение узких импульсов синхронизатора 4, представляющих собой результаты измерения фазы принимаемых импульсов дискретного сигнала, к соответствующим, входам блока 7 счетчиков в -момент совпадения на их входах импульсов синхронизатора 4 и импульсов соответствующих последовательностей линии 2 задержки. Блок 7 счетчиков может представить собой набор 1 отдельных счетчиков, управляющие входы которых объединены, а емкость каждого равна т. Если в течение следования импульсы синхронизатора 4, подсчет которых ведется счетчиком 5, с емкостью, равной п, m импульсов, поступают на i-й вход блока 7 счетчиков, то на соответствующем его выходе появляется импульс в момент времени tj, который запоминается блоком 8 памяти в виде i-ro номера. Блок 8 памяти может представлять собой, например, набор р-триггеров, информационные входы которых подключены к соответствующим выходам счетчиков, а запись информации осуществляется в момент поступления задержки по времени импульса с выхода элемента ИЛИ 6 на счетные входы D-триггеров. Далее в блоке памяти 8 информация на выходе соответствующего D-триггера шифруется в виде i-ro номера, поступает на управляющий вход мультиплексера 9 и на выходе мультиплексера 9 появляется последовательность У с i-rp выхода линии 2 задержки, совпадающая с определенной точностью с истинными значениями фазы принимаемого сигнала, которые формируются в синхронизаторе 4. Одновременно импульс с i-ro выхода блока 7 счетчиков через элемент ИЛИ 6 производит установку счетчика 5 в последнее п-1 состояние, при котором на его выходе формируется импульс, устанавливающий в нуль блок 7 счетчиков. С приходом последующего импульса синхронизатора 4 счетчик 5 начинает счет заново, и процесс анализа повторяется. Если при поступлении п импульсов синхронизатора 4 на вход счетчика 5 ни на один вход блока счетчиков 7 не поступило m импульсов, то после прихода п-го импульса синхронизатора 4 блок 7 счетчиков устанавливается в нуль выходным импульсом счетчика 5. С приходом (п+1)-го импульса синхронизатора 4 счетчик 5 начинает счет заново, при этом фазы выходного сигнала устройства для фазовой синхронизации не меняются, так как блок 8 памяти не производит перезапись входной информации. Корррекция фазы выходного сигнала производится только в том случае, когда в процесс измерений фазы принимаемого сигнала в блоке 7т счетчиков измерений совпадают с истинными значениями фазы. Рассмотрим случай, когда длительность элементарной посылки информации Т разбита на шесть импульсных последовательностей (1 6) с длительностью импульсов Т последовательности Уу , 1 - 6, В начальный момент, когда на вход устройства не поступает информация, с выхода мультиплексера 9 снимается произвольная последовательность j (фиг. 2а), при этом на выходе одновибратора 19- логический «О, который запирает элемент ЗИ 18 и соответственно вход фазового детектора 14. Узел 16 формирования импульса установки формирует узкий импульс (фиг. 26), соответствующий середине длительности импульса последовательности У (фиг. 2а), при этом фаза импульсной последовательности на выходе делителя 13 частоты в блоке 11 дискретной автоподстройки фазы 11 может быть произвольной (фиг. 2в) штриховая линия). В следующий момент блок 16 формирования импульса установки-устанавливает делитель 13 частоты в такое положение, что передний фронт выходного импульса делителя частоты 13 (фиг. 2в) совпадает с серединой и.мпульса последовательности fi. В таком исходном состоянии устройство находится до прихода информационного сигнала. При подаче двоичной информации на вход устройства на выходе синхронизатора 4 появляются импульсы (фиг. 2), соответствующие действительным отсчетам фазы приходящего сигнала. Большинство этих

импульсов проходят через тот элемент И 3, на который поступает последовательность с фазой, наиболее близкой к фазе принимаемого сигнала. С помощью блока 7 счетчиков, счетчика 5 и элемента ИЛИ 6 осуществляется статистическая обработка отсчетов фазы принимаемого сигнала и запоминание результатов в блоке 8 памяти, после чего на выход мультиплексера 9 коммутируется импульсная последовательность У с i-ro выхода линии 2 задержки (фиг. 2), с фазой, наиболее близкой к фазе принимаемого сигнала. При этом блок 16 формирования импульса установки с помощью двух тактовых последовательностей формирует импульс установки (фиг. 2е), который, пройдя через блок 17 фазирования, устанавливает делитель 13 частоты таким образом, что передний фронт его выходного импульса, (фиг. 2ж) совпадает с серединой импульса последовательности fs (фиг. 2д). Одновреме-нно с выбором требуемой последовательности У/ ийпульсы с выхода элемента ИЛИ 6 запускают одновибратор 19, который формирует положительный импульс определенной длительности, отпирающий элемент ЗИ 18 и вход фазового детектора 14. В результате на вход фазового детектора 14 начинают поступать отсчеты принимаемого сигнала с выхода синхронизатора 4, Kotopbie совпадают по фазе с временной зоной (шириной импульсов) импульсной последовательности У , поступающей с выхода мультиплексера 9 на вход фазового детектора 14 через элемент ЗИ 18, и в блоке 11 дискретной автоподстройки фазы осуществляется точная подстройка фазы выходного сигнала устройства в пределах дискретно выбранной зоны.

Для того, чтобы не происходило принудительной установки делителя 13 частоты при плавном изменении фазы сигнала информации в пределах соседних зон (при выборе другой последовательности у в блоке 17 фазирования формируется с помощью дешифратора 25 импульс опознавания состояния делителя 13 частоты таким образом, что бы его середина (фиг. 23) точно совпадала iC передним фронтом выходного импульса делителя 13 частоты (фиг. 2ж). Конструктивно такой-дешифратор может состоять из двух дешифраторов, опознающих конечный и начальный отрезок выходного импульса делителя 13 частоты, и элемента ИЛИ 6, в котором оба импульса суммируются. Выходной импульс дещифратора 25 сравнивается во втором и третьих элементах И 22 и 23 соответственно с инвертированной и прямой импульсной последовательностью Уу с выхода мультиплексера 9. В случае, если импульс опознавания не совпадает с шириной импульса (зоной) импульсной последовательности УЧ , то он проходит через второй элемент И 22 и cбpac Jвaeт RS-триггер 21 в состояние логической «1, открывая первый

элемент И 20, через который на вход делителя 13 частоты поступает импульс установки. После установки делителя 13 частоты импульс опознавания проходит через треg тий элемент И 23 и сбрасывает RS-триггер 21 в состояние логического «О, запирая первый элемент И 20 по входу. Таким образом, если в начале сеанса связи передний фронт выходного импульса делителя 13 частоты не совпадает с щириной импульса выбранной

0 последовательности У/ , то блок 17 фазирования принудительно устанавливает длительность 13 частоты, обеспечивая тем самым малое время вхождения в синхронизм для замкнутой системы синхронизации, обеспечиваю- щей точную подстройку фазы. На третий вход блока 16 формирования импульса установки поступает тактовая последовательность (фиг. 2и), а на второй вход - последовательность с частотой задающего генератора 1. На выходе D-триггера 27 выходной импульс мультиплексера 9 (фиг. 2д) сдвигается на половину его длительности (фиг. 2к) и далее сдвигается D-триггером 28 на такт, равный периоду частоты задающего генератора 1, в результате чего на выходе элемента И 29 формируется узкий импульс установки (фиг. 2е), жестко привязанный к середине импульса последовательности У (фиг. 2д).

Рассмотрим случай, когда в результате ухода отсчетов в фазы с выхода синхронизатора 4 относительно фазы сигнала задающего генератора 1 устройства выбирает соседнюю зону (другую последовательность У/ фиг. 2л). В этот момент импульсы с выхода синхронизатора 4 (фиг. 2м) и передний фронт импульса на выходе устройства

(фиг. 2н), находятся примерно на границе двух соседних зон импульсных последовательностей (фиг. 2(3, л). При смене зон импульс с выхода дешифратора 25 (фиг. 20), имеющий определенную длительность, проходит через третий элемент И 23, попрежнему удерживая RS-триггер 21 в состоянии логического «О, запирающего по входу первый элемент И 20. Длительность импульса опознавания с выхода дешифратора 25 должна быть больще того временного смещения выходных импульсов, образующегося за счет медленной подстройки за время перехода из одной зоны в другую (при смене соседних последовательностей). Таким образом, осуществляется точная автоподстройка фазы сигнала в блоке 11 дискретной авQ топодстройки фазы без резких скачков фазы, связанных с внешней установкой делителя 13 частоты.

Длительность формируемого одновибратором 19 импульса должна соответствовать 5 среднему времени между двумя соседними обнаружениями истинных отсчетов фазы принимаемого неискаженного сигнала, т.е. между двумя соседними импульсами на выходе элемента ИЛИ 6. При этом -с приходом каждого отсчета фазы с выхода синхронизатора 4, совпадающего с зоной импульсов выбранной последовательности У, обеспечивается точная (с малым дискретным шагом) подстройка фазы выходных импульсов в пределах выбранной временной зоны.

а 5

(T.

л

Фиг.г

Таким образом, предлагаемое устройство для фазовой автоподстройки частоты обеспечивает высокую точность фазовой синхронизации за счет определения истинных значений фазы принимаемого сигнала, а также обеспечивает малое время вхождения в синхронизм и высокую помехоустойчивость.

JU

JL

л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для фазовой синхронизации | 1982 |

|

SU1062879A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-04-07—Публикация

1983-11-23—Подача