2.Схема поп.1,отличающ а я с я тем, что блок управления содержит элемент И-НЕ, первый и второй входы питания которого соединены соответственно с первым и вторы входами питания блока управления, первый, второй входы и выход которого соединены соответственно с первы вторым входами и выходом элемента И-НЕ,

3.Схема поп.1, отличающаяся тем, что блок формирования импульса при включении источника питания содержит резистор

и конденсатор, первая обкладка которого соединена с первым входом питания блока формирования импульса при .включении питания, выход которого соединен со второй обкладкой конденсатора и с первым выводом резистора, второй вывод которого соединен со вторым входом питания блока формирования импульса при включении питания

4.Схема поп.1, отличающ а я с я тем, что в качестве транзистора используется полевой транзистор.

5.Интегральная схема, содержащая общую шину, входную шину, функциональный логический блок и транзистор имеющий два выхода с основным типом проводимости между ними и управляющий вход. Причем потенциал между управляющим входом и одним из входов

транзистора управляет его проводимос-тью, отличающаяся тем что с целью уменьщёния потребления мощности, в нее введены два резистора , блок управления и блок формирования импульса при включении питания , выход которого соединен с перBbw входом блока управления, второй вход которого соединен со входной шиной и соединен через первый резис тор с первым входом транзистора, второй вход которого соединен через второй резистор с общей шиной, вход управления транзистора соединен с первым выходом блока управления ,вто-г рой выход которого соединен со входом функционального логического блок

6.Схема по п. 5, о т ли ч а, ющ а я с я тем, что блок управления содержит два элемента НЕ и элемент И-НЕ, первый вход которого соединен со вторым входом блока управления, первый вход которого соединен через первый элемент НЕ со вторым входом элемента И-НЕ, выход которого соединен с первым выходом блока управлени и со входом второго элемента НЕ, выход которого соединен со вторым выходом блока управления.

7.Схема по п.5, отличающаяся тем, что в качестве транзистора использован полевой транзистор.

| название | год | авторы | номер документа |

|---|---|---|---|

| СДВИГОВЫЙ РЕГИСТР | 1994 |

|

RU2116678C1 |

| Генератор сигналов цветовой поднесущей для телевизионного приемника | 1976 |

|

SU1145943A3 |

| ИМПУЛЬСНЫЙ ИСТОЧНИК ПИТАНИЯ ТЕЛЕВИЗОРА ДЛЯ ВЫРАБАТЫВАНИЯ ВЫХОДНОГО НАПРЯЖЕНИЯ ПИТАНИЯ ВО ВРЕМЯ ДЕЖУРНОГО РЕЖИМА И РАБОЧЕГО РЕЖИМА | 1990 |

|

RU2113756C1 |

| Интегральная схема | 1967 |

|

SU457237A3 |

| Пиковый детектор | 1973 |

|

SU940657A3 |

| Жидклкристаллическое устройство со схемой защиты | 1975 |

|

SU563931A3 |

| Цифровое устройство обработки видеосигнала | 1985 |

|

SU1382413A3 |

| Усилитель тока | 1974 |

|

SU528894A3 |

| Устройство обработки видеосигнала | 1980 |

|

SU1306491A3 |

| УСТРОЙСТВО ВОЗБУЖДЕНИЯ КИНЕСКОПА С ГАММА-КОРРЕКЦИЕЙ | 1995 |

|

RU2183386C2 |

1. Интегральная схема, содержащая две шины питания, входную шину, функциональный логический блок и транзистор, имеющий два входа с основным-типом проводимости между ними и управляющий вход, причем потенциал между управляющим входом и одним из входов транзистора управляет его проводимостью, вход функционального логическогр блока соединен со входной шиной и с первым входом транзистора, второй вход которого соединен с первой шиной питания,о тличающаяся тем, что, с целью уменьшения потребления мощности, в нее введены блок управления и блок формирования импульса при включении питания, первьй и второй входы питания которых соединены соответственно с первой и второй шинами питания, выход блока формирова1 ния импульса при включении питания соединен с первым входом блока упСО равления, второй вход и вькод которого соединены соответственно со входной шиной и с управляющим входом транзистора.

1

Изобретение относится к интегральной схемотехнике и служит для установления потенциала на несоединенных входных клемах больших интегральных схем на полевых транзисторах.

Известна интегральная схема, содержащая входную шину, общую щину, функциональный логический блок, резистор и полевой транзистор,диод.

В известном устройстве дпя защиты входа функционального логического блока от статического электричества служит диод, включенный между входно и общей шинами 1.

Недостатком известного устройства является то, что при подаче на входную шину потенциала питания через диод течет относительно большой ток, что приводит к увеличению потребляемой мощности.

Известна интегральная схема, содержащая две шины питания, входную шину, функциональный логический блок и транзистор, имеющий два входа с основным типом проводимости между ними,и управляющий вход, причем потенциал между управляюа1им входом и одним из входов транзистора управляет его проводимостью, вход функционального логического блока соединен со

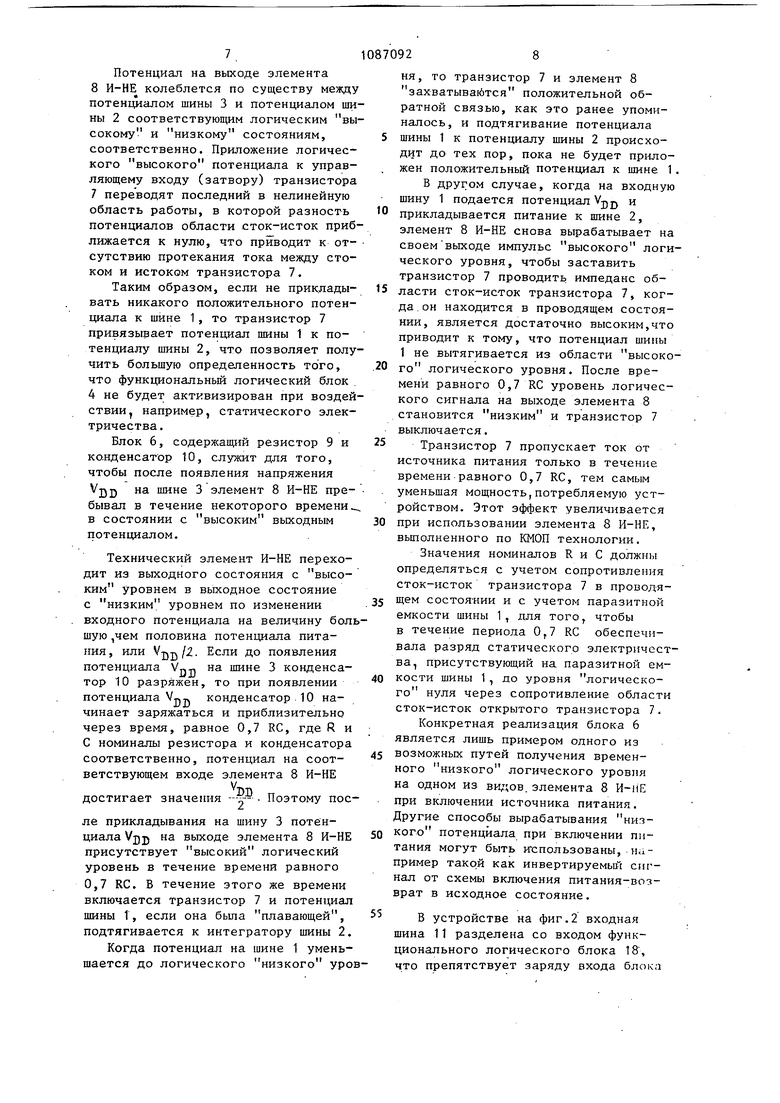

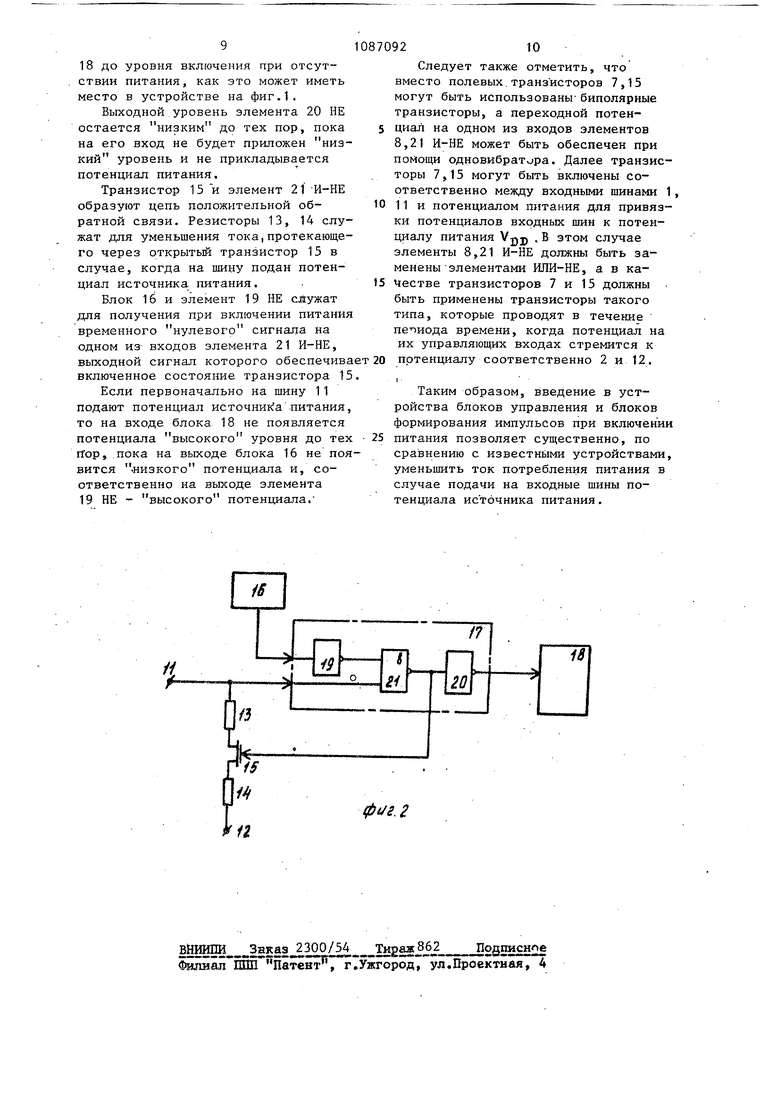

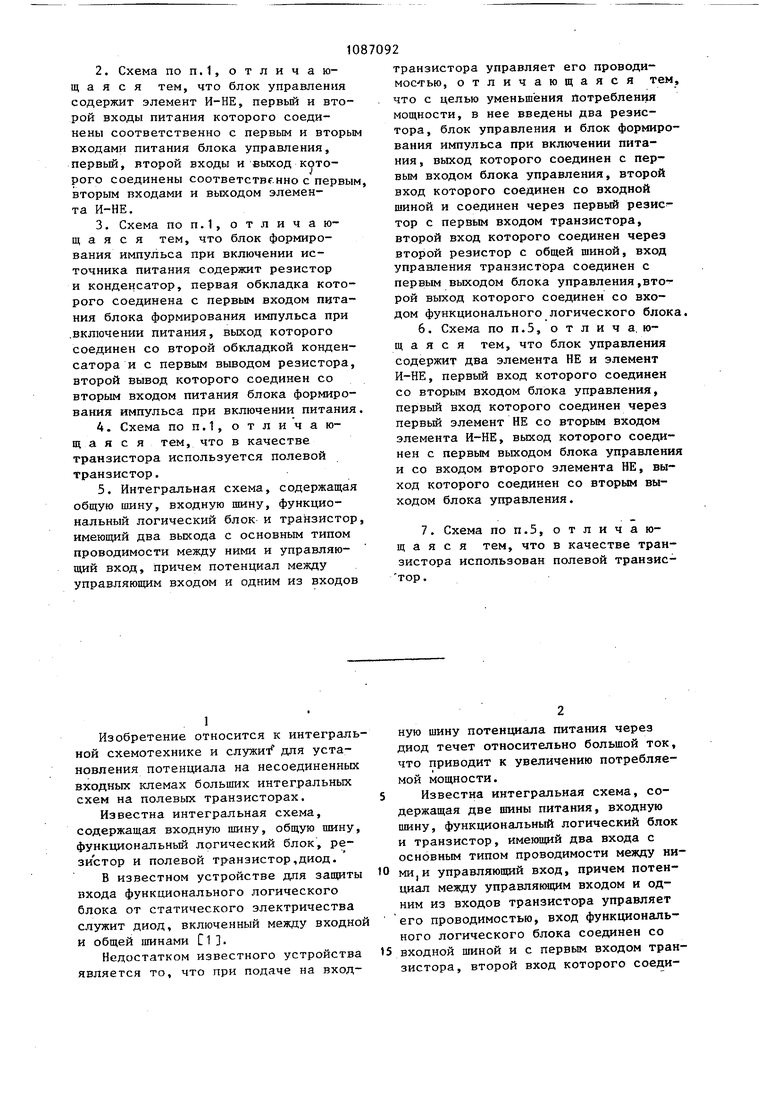

входной шиной и с первым входом транзистора, второй вход которого соединен с первой шиной питания, управля щий вход транзистора соединен со входной шиной. В известном устройстве наличие транзистора на входе функционального логического обеспечивает относительно высокую входную проводимость входа функционального логического блока и служит для исключения инициализации входа функциональ ного логического блока при воздействии случайных статистических заря дов, позтому в случае отсутствия нужды в инициализации входа функцио нального логического блока (т.е. в отсутствие нужды в реализации одной из многих функциональных возмож ностей устройства) вход может быть оставлен плавающим С 23. Недостатком известного устройства является то, что в случае, когда требуется инициализировать вход функционального логического блока, т.е. при соединении входной шины со второй шиной питания, через тран зистор течет относительно большой ток, который может составить существенную часть от тока потребления функционального логического блока, при этом соответственно увеличивает ся мощность потребления. Такое состояние является особенно нежелательным там, где питание подается от источника питания с малой емкостью, например от батареи для питания часов, калькуляторов и т.д. Цель изобретения - уменьшение потребляемой мощности.Для достижения поставленной цели в интегральную схему, содержащую две шины питания, входную шину, функциональный логический блок и транзистор, имеющий два входа с основным типом проводимости между ним и управляющий вход, причем потенциа между управляюпщм входом и одним из входов транзистора управляет его проводимостью, вход функционального логического блока соединен со вход ной шиной и с первым входом транзис тора, второй вход которого соединен с первой шиной питания, введены блок управления и блок формирования импульса при включении питания, первый и второй входы питания котор соединены соответственно с первой и второй шинами питания, выход блока ,формирования импульса при включении питания соединен с первым входом блока управления, второй вход и выход которого соединены соответственно со входной шиной и с управляющим входом транзистора. В интегральной схеме блок управления содержит элемент И-НЕ,первый и второй входы питания которого соединены соответственно с первым и вторым входами питания блока управления, первый, второй входы и выход которого соединены соответственно с первым, вторым входами и выходом элемента И-НЕ. В интегральной схеме блок формирования импульса при включении источника питания содержит резистор и конденсатор, первая обкладка которого соединена с первым входом питания блока формирования импульса при включении питания, выход которого соединен со второй обкладкой конденсатора и с первым выводом резистора, второй вывод которого соединен со вторым входом питания блока формирования импульса при включении питания. В интегральной схеме в качестве транзистора используется полевой транзистор. В интегральную схему, содержащую общую шину, входную шину,функциональный логический блок и транзистор, имеющий два выхода с основным типом проводимости между ними и управляющий вход, причем потенциал между управляющим.входом и одним из входов транзистора управляет его проводимостью, введены два резистора, блок управления и блок формирования импульса при включении питания, выход которого соединен с первым входом блока управления, второй вход которого соединен со входной шиной и соединен через первьй резистор с первым входом транзистора, второй вход которого соединен через второй резистор с общей шиной, вход управления транзистора соединен с первым выходом блока управления , второй выход которого соединен со входом функционального логического блока. В интегральной схеме блок управления содержит два элемента НЕ и элемент И-НЕ, первый вход которого соединен со вторым входом блока уп5равления, первый вход которого соединен через порвый элемент НЕ со вторым входом элемента И-НЕ, выход которого соединен с первым выходом блока yпpaвлeнJiя и со входом второг элемента НЕ, выход которого соединен со вторым выходом блока управления. В интегральной схеме в качестве транзистора использован полевой транзистор. На фиг.1 приведена схема первого варианта интегральной схемы; на фиг.2 - то же, второй вариант интегральной схемы.. Схема содержит входную шину 1, шины 2,3 питания, функциональный логический блок 4, блок 5 управлени блок 6 формирования импульсов при включении питания, транзистор 7, элемент 8 И-НЕ, резистор 9 и конденсатор 10, входы 5-1, 5-2 питания блока 5 управления, входы 6-1, 6-2 питания блока 6 формирования импуль са при включении питания. На фиг.2 обозначено: входная шина 11,.общая шина 12, резисторы 13, 14, транзистор 15, блок 16 формирования импульса при включении питани блок 17 управления, функциональный логический блок 18, элементы 19, 20 НЕ и элемент 21 И-НЕ. На фиг.1 входная шина 1 соединена со входом функционального логического блока 4, с первым входом блока 5 управления и с первым входо транзистора 7, второй вход которого соединен с шиной 2 питания, со входами 5-2, 6-2 питания соответственн блока 5 управления и блока 6 формированйя импульса при В1спючении питания, вход 6-1 питания которого соединен с шиной 3 питания и со вхо дом 5-1 питания блока 5 управления, .второй вход и выход которого соеди55ены соответственно с выходом блока 6 формирования импульса при вклю чении питания и с управляющим входо транзистора 7. Выход, первьй и второй входы бло ка 5 упра-нпения соединены соответст венно с выходом, первым и вторым входом элемента 8 И-НЕ, первьш и вт рой входы питания которого соединен соответственно со входами питания 5-2, 5-1 блока 5 управления. Вход 6-2 питания блока 6 формиро ,вания импульса при включений пита92ния соединен через конденсатор 10 с выходом блока 6 формирования импульса при включении -питания, выход которого соединен через резистор 9 со входом 6-1 питания блока 6 формирования импульса при включении питания. На фиг.2 входная шина 11 соединена с первым входом блока 17 управления и соединена через резистор 13 с первым входом транзистора 15,второй вход которого соединен через резистор с общей шиной 12, выход блока 16 формирования импульса при включении питания соединен со вторым входом блока 17 управления,первый и второй выходы которого соединены соответственно со входом управления транзистора 15 и со входом функционального логического блока 18. Первый вход блока 17 управления соединен с первым входом элемента 21 И-НЕ,второй вход которого соединен с выходом элемента 19 НЕ, вход которого соединен со вторым входом блока 17 управления, первый выкод которого соединен с выходом элемента 21 И-НЕ и со входом элемента 20 НЕ,- вькод которого соединен со вторым выходом блока 17 управления. Устройство на фиг.1 привязывает входную шину 1 к потенциалу шины 2 в случае, когда на входную щину 1 ничего не подается и предотвращает потерю -шунтирующего тока через транзистор 7 в случае, когда входная шина соединяется с щиной 3. Когда вход стока транзистора 7 соединен со входной шиной 1 а вход истока - с шиной 2, то транзистор7 селективно устанавливается в состояние ироводимос и, определяемое потенциалом на шине 1. Элемент 8 И-НЕ обеспечивает получение логического выходного потейциала, достаточного для перевода транзистора 7 в проводящее состояние всякий раз, когда потенциал на любом входе элемента 8 И-НЕ имеет логический низкий уровень, который близок потенциалу н;а шине 2. Положительная обратная связь, получаемая за счет соединений транзистора 7 и элемента 8 И-НЕ,удерживает потенциал на шине 1 в области близкой к потенциалу на шине 2, что поддерживает в неактивном состоянии функциональный логический блок 4. 7 Потенциал на выходе элемента 8 И-НЕ колеблется по существу между потенциалом шины 3 и потенциалом ши ны 2 соответствующим логическим вы сокому и низкому состояниям, соответственно. Приложение логического высокого потенциала к управляющему входу (затвору) транзистора 7 переводят последний в нелинейную область работы, в которой разность потенциалов области сток-исток приб лижается к нулю, что приводит к отсутствию протекания тока между стоком и истоком транзистора 7. Таким образом, если не прикладывать никакого положительного потенциала к шине 1, то транзистор 7 привязывает потенциал шины 1 к потенциалу шины 2, что позволяет полу чить большую определенность того, что функциональный логический блок 4 не будет активизирован при воздей ствии, например, статического электричества. Блок 6, содержащий резистор 9 и конденсатор 10, служит для того, чтобы после появления напряжения Vjju на шине 3 элемент 8 И-НЕ пребывал в течение некоторого времени высоким вькодным в состоянии с потенциалом. Технический элемент И-НЕ переходит из выходного состояния с высоким уровнем в выходное состояние с низким уровнем по изменении входного потенциала на величину бол шую ,чем половина потенциала питания, или V-Q-JJ/2. Если до появления потенциала VQJ, на шине 3 конденсатор 10 разряжен, то при появлении потенциала Vjjj. конденсатор 10 начинает заряжаться и приблизительно через время, равное 0,7 RC, где R и С номиналы резистора и конденсатора соответственно, потенциал на соответствующем входе элемента 8 И-НЕ достигает значения -у- . Поэтому пос ле прикладывания на шину 3 потенциала Vj)j) на выходе элемента 8 И-НЕ присутствует высокий логический уровень в течение времени равного 0,7 RC. В течение этого же времени включается транзистор 7 и потенциал щины 1, если она бьта плавающей, подтягивается к интегратору шины 2. Когда потенциал на шине 1 уменьшается до логического низкого уро 92 ня, то транзистор 7 и элемент 8 захватывается положительной обратной связью, как это ранее упоминалось, и подтягивание потенциала шины 1 к потенциалу шины 2 происходит до тех пор, пока не будет приложен положительный потенциал к шине 1. В другом случае, когда на входную шину 1 подается потенциал V-p и прикладывается питание к шине 2, элемент 8 И-НЕ снова вырабатывает на своемвыходе импульс высокого логического уровня, чтобы заставить транзистор 7 проводить импеданс области сток-исток транзистора 7, когда . он находится в проводящем состоянии, является достаточно высоким,что приводит к тому, что потенциал шины 1 не вытягивается из области высокого логического уровня. После времени равного 0,7 RC уровень логического сигнала на выходе элемента 8 становится низким и транзистор 7 выключается. Транзистор 7 пропускает ток от источника питания только в течение времени равного 0,7 RC, тем самым уменьшая мощность,потребляемую устройством. Этот эффект увеличивается при использовании элемента 8 И-НЕ, вьшолненного по КМОП технологии. Значения номиналов R и С должны определяться с учетом сопротивления сток-исток транзистора 7 в проводящем состоянии и с учетом паразитной емкости шины 1, для того, чтобы в течение периода 0,7 RC обеспечивала разряд статического электричества, присутствующий на паразитной емкости шины 1, до уровня логического нуля через сопротивление области сток-исток открытого транзистора 7. Конкретная реализация блока 6 является лишь примером одного из возможных путей получения временного низкого логического уровня на одном из ви/дов. элемента 8 И-иЕ при включении источника питания. Другие способы вырабатывания низкого потенциала при включении питания могут быть и-спользованы, например такой как инвертируемый сигнал от схемы включения питания-возврат в исходное состояние. g устройстве на фиг.2 входная шина 11 разделена со входом функционального логического блока 18, что препятствует заряду входа блока 18 до уровня включения при отсутствии питания, как это может иметь место в устройстве на фиг.1. Выходной уровень элемента 20 НЕ остается низким до тех пор, пока на его вход не будет приложен низкий уровень и не прикладыва ется потенциал питания. Транзистор 15 и элемент 21 И-НЕ образуют цепь положительной обратной связи. Резисторы 13, 14 служат для уменьшения тока,протекающего через открытьй транзистор 15 в случае, когда на шину подан потенциал источника- питания. Блок 16 и элемент 19 НЕ сйужат для получения при включении питания временного нулевого сигнала на одном из- входов элемента 21 И-НЕ, одном ИЗ ВХидиъ jjiciit n J о. 1 . , выходной сигнал которого обеспечив включенное состояние транзистора 1 Если первоначально на шину 11 подают потенциал источник:а питания то на входе блока 18 не появляется потенциала высокого уровня до те гГор, пока на выходе блока 16 не по вится -низкого потенциала и, соответственно на выходе элемента 19 НЕ - высокого потенциала.

.

k3

/

. г 210 Следует также отметить, что вместо полевых.транзисторов 7,15 могут быть использованыбиполярные транзисторы, а переходной потенциал на одном из входов элементов 8,21 И-НЕ может быть обеспечен при помощи одновибратора. Далее транзисторы 7,15 могут быть включены соответственно между входными шинами 1, 11 и потенциалом питания для привязки потенциалов входных шин к потенциалу питания VjjJ) . В этом случае элементы 8,21 И-НЕ должны быть заменены элементами ИЛИ-НЕ, а в каЧестве транзисторов 7 и 15 должны быть применены транзисторы такого типа, которые проводят в течение времени, когда потенциал на их управляющих входах стремится к потенциалу соответственно 2 и 12. Таким образом, введение в устройства блоков управления и блоков формирования импульсов при включении питания позволяет существенно, по сравнению с известными устройствами, уменьшить ток потребления питания в случае подачи на входные шины потенциала источника питания.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3636385, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 4130988, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-04-15—Публикация

1980-05-16—Подача