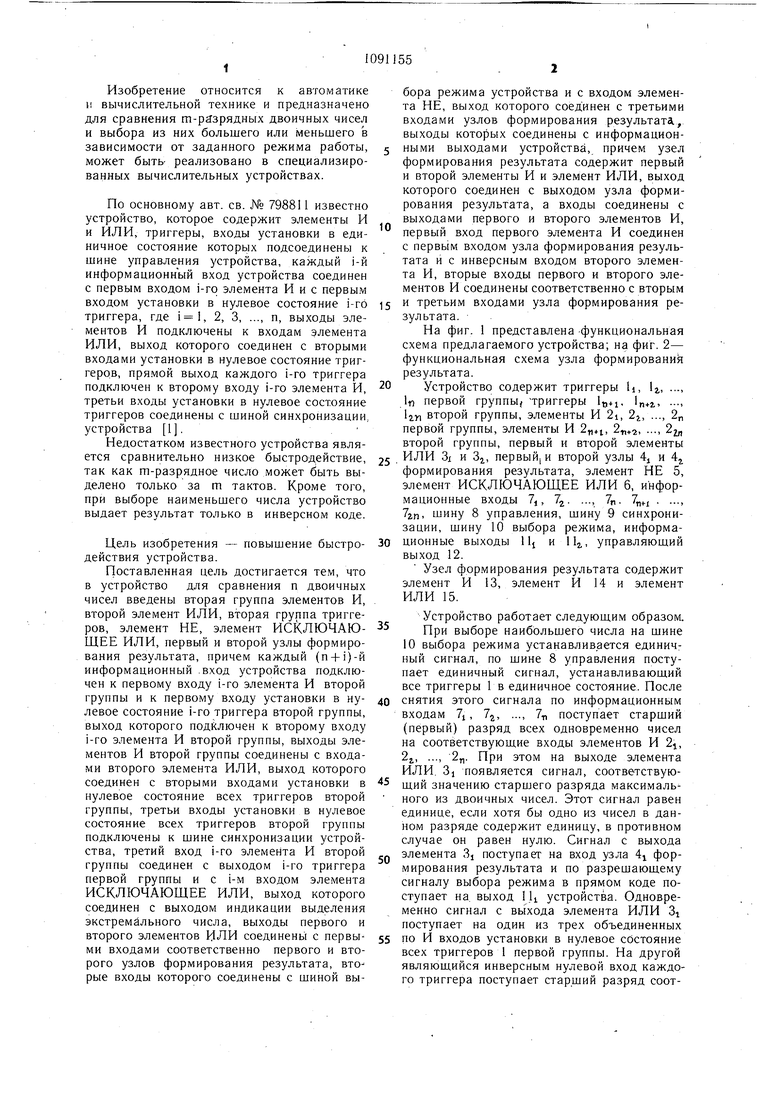

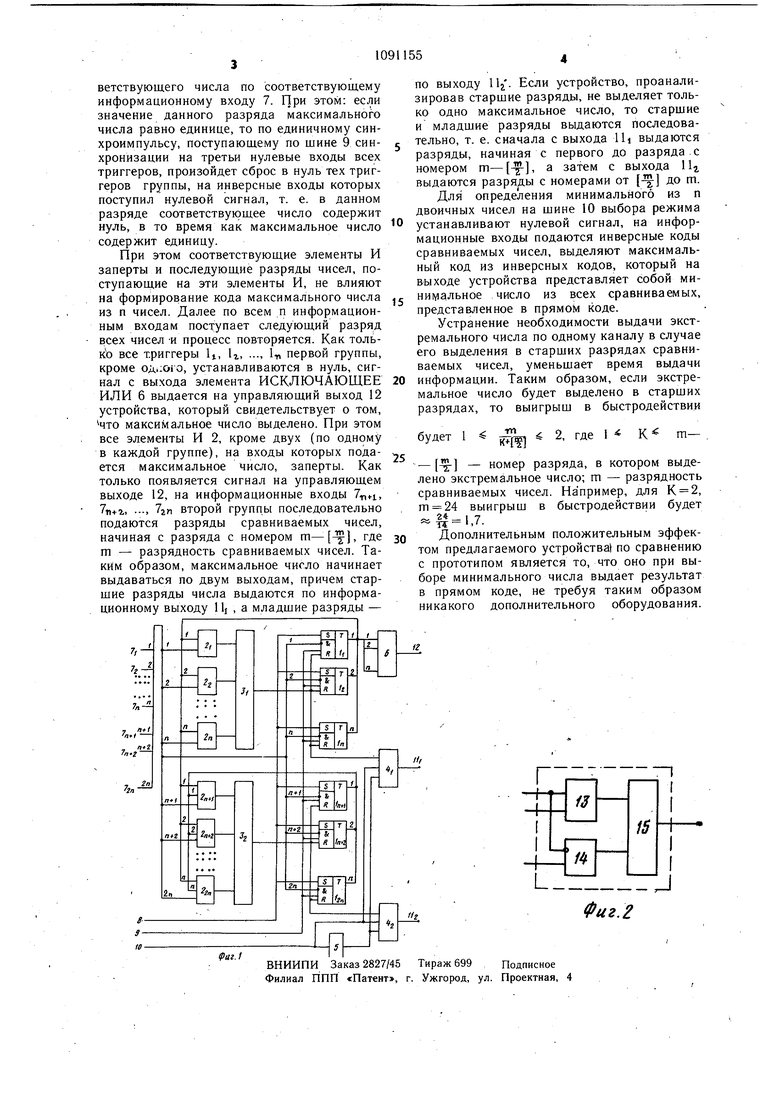

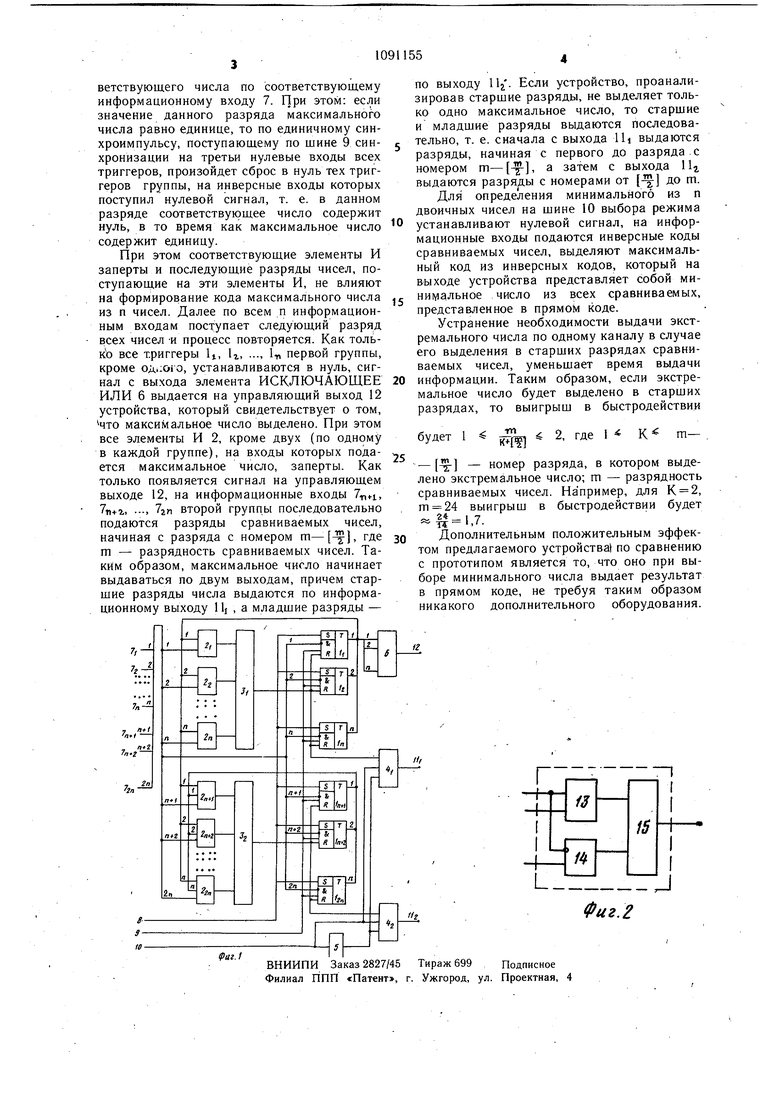

Изобретение относится к автоматике и вычислительной технике и предназначено для сравнения т-ргзрядных двоичных чисел и выбора из них большего или меньшего в зависимости от заданного режима работы, может быть- реализовано в специализированных вычислительных устройствах. По основному авт. св. № 798811 известно устройство, которое содержит элементы И и ИЛИ, триггеры, входы установки в единичное состояние которых подсоединены к шине управления устройства, каждый i-й информационный вход устройства соединен с первым входом i-ro элемента И и с первым входом установки в нулевое состояние i-ro триггера, где , 2, 3, ..., п, выходы элементов И подключены к входам элемента ИЛИ, выход которого соединен с вторыми входами установки в нулевое состояние триггеров, прямой выход каждого i-ro триггера подключен к второму входу i-ro элемента И, третьи входы установки в нулевое состояние триггеров соединены с шиной синхронизации, устройства 1. Недостатком известного устройства является сравнительно низкое быстродействие, так как т-разрядное число может быть выделено только за m тактов. Кроме того, при выборе наименьшего числа устройство выдает результат только в инверсном коде. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для сравнения п двоичных чисел введены вторая группа элементов И, второй элемент ИЛИ, вторая rpyrina триггеров, элемент НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй узлы формирования результата, причем каждый (п + 1)-й информационный .вход устройства подключен к первому входу i-ro элемента И второй группы и к первому входу установки в нулевое состояние i-ro триггера второй группы, выход которого подключен к второму входу i-ro элемента И второй группы, выходы элементов И второй группы соединены с входами второго элемента ИЛИ, выход которого соединен с вторыми входами установки в нулевое состояние всех триггеров второй группы, третьи входы установки в нулевое состояние всех триггеров второй группы подключены к шине синхронизации устройства, третий вход i-ro элемента И второй группы соединен с выходом i-ro триггера первой группы и с i-м входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с выходом индикации выделения экстремального числа, выходы первого и второго элементов ИЛИ соединены с первыми входами соответственно первого и второго узлов формирования результата, вто рые входы которого соединены с шиной выбора режима устройства и с входом элемента НЕ, выход которого соединен с третьими входами узлов формирования результата.,, выходы которых соединены с информационными выходами устройства, причем узел формирования результата содержит первый и второй элементы И и элемент ИЛИ, выход которого соединен с выходом узла формирования результата, а входы соединены с выходами первого и второго элементов И, первый вход первого элемента И соединен с первым входом узла формирования результата и с инверсным входом второго элемента И, вторые входы первого и второго элементов И соединены соответственно с вторым и третьим входами узла формирования результата. На фиг. 1 представлена -функциональная схема предлагаемого устройства; на фиг. 2- функциональная схема узла формирований результата. Устройство содержит триггеры U, l, ..., 1я первой группы, -триггеры 1„+1, lin второй группы, элементы И 2i, 2, ..., 2„ первой группы, элементы И 2„+1, 2t,+2, ..., щ второй группы, первый и второй элементы ИЛИ 3i и 3j, первый, и второй узлы 4 и 4 формирования результата, элемент НЕ 5, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ б, информационные входы , 7. ..., 7г. 7,. . ..., , шину 8 управления, шину 9 синхронизации, шину 10 выбора режима, информационные выходы 1 Ij и П-р,, управляющий выход 12. Узел формирования результата содержит элемент И 13, элемент И 14 и элемент ИЛИ 15. Устройство работает следующим образом. При выборе наибольшего числа на шине 10 выбора режима устанавливается единичный сигнал, по шине 8 управления поступает единичный сигнал, устанавливающий все триггеры 1 в единичное состояние. После снятия этого сигнала по информационным входам 7i, 7г, ..., 7т, поступает старший (первый) разряд всех одновременно чисел на соответствующие входы элементов И 2, 2j, ..., 2„. При этом на выходе элемента ИЛИ. 3i появляется сигнал, соответствуюший значению старшего разряда максимального из двоичных чисел. Этот сигнал равен единице, если хотя бы одно из чисел в данном разряде содержит единицу, в противном случае он равен нулю. Сигнал с выхода элемента 3 поступает на вход узла 4 формирования результата и по разрешающему сигналу выбора режима в прямом коде поступает на. выход 111 устройства. Одновременно сигнал с вь1хода элемента ИЛИ 3i поступает на один из трех объединенных по И входов установки в нулевое состояние всех триггеров 1 первой группы. На другой являющийся инверсным нулевой вход каждого триггера поступает старший разряд соответствующего числа по соответствующему информационному входу 7. При этом: если значение данного разряда максимального числа равно единице, то по единичному синхроимпульсу, поступающему по шине 9 синхронизации на третьи нулевые входы всех триггеров, произойдет сброс в нуль тех триггеров группы, на инверсные входы которых поступил нулевой сигнал, т. е. в данном разряде соответствующее число содержит нуль, в то время как максимальное число содержит единицу.

При этом соответствующие элементы И заперты и последующие разряды чисел, поступаюи.1,ие на эти элементы И, не влияют на формирование кода максимального числа из п чисел. Далее по всем п информационным входам поступает следующий разряд всех чисел -и процесс повторяется. Как толькЪ все триггеры It, U, ..., 1-n первой группы, кроме од.:йго, устанавливаются в нуль, сигнал с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 выдается на управляющий выход 12 устройства, который свидетельствует о том, что максимальное число выделено. При этом все элементы И 2, кроме двух (по одному в каждой группе), на входы которых подается максимальное число, заперты. Как только появляется сигнал на управляющем выходе 12, на информационные входы Трп, 7пч.г, .- 7гп второй группы последовательно подаются разряды сравниваемых чисел, начиная с разряда с номером m-, где m - разрядность сравниваемых чисел. Таким образом, максимальное число начинает выдаваться по двум выходам, причем старшие разряды числа выдаются по информационному выходу 1 Ij , а младшие разряды -

по выходу llj. Если устройство, проанализировав старшие разряды, не выделяет только одно максимальное число, то старшие и младшие разряды выдаются последовательно, т. е. сначала с выхода lli выдаются разряды, начиная с первого до разряда с номером m- -у-, а затем с выхода 1 Ij, выдаются разря цы с номерами от - до т.

Для определения минимального из п двоичных чисел на шине 10 выбора режима устанавливают нулевой сигнал, на информационные входы подаются инверсные коды сравниваемых чисел, выделяют максимальный код из инверсных кодов, который на выходе устройства представляет собой минимальное число из всех сравниваемых, представленное в прямом коде.

Устранение необходимости выдачи экстремального числа по одному каналу в случае его выделения в старших разрядах сравниваемых чисел, уменьшает время выдачи информации. Таким образом, если экстремальное число будет выделено в старших разрядах, то выигрыш в быстродействии

т

К

4 2, где 1

1

m-

- - номер разряда, в котором выделено экстремальное число; m - разрядность сравниваемых чисел. Например, для К 2, т 24 выигрыш в быстродействии будет

24- 1 7 TI- .

Дополнительным положительным эффектом предлагаемого устройства) по сравнению с прототипом является то, что оно при выборе минимального числа выдает результат в прямом коде, не требуя таким образом никакого дополнительного оборудования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Устройство для сортировки чисел | 1986 |

|

SU1310803A1 |

| Устройство для сортировки двоичных чисел | 1983 |

|

SU1104504A1 |

| Устройство для сравнения двоичных чисел | 1979 |

|

SU840889A1 |

| Устройство контроля веса материала в бункерах | 1980 |

|

SU972243A1 |

| Устройство для сравнения чисел | 1981 |

|

SU960799A1 |

| Устройство для выбора упорядоченной последовательности данных | 1982 |

|

SU1059565A1 |

| Устройство для сортировки чисел | 1990 |

|

SU1781680A1 |

| Устройство для определения экстремальных чисел | 1989 |

|

SU1661754A1 |

| Устройство для упорядочения массива чисел | 1990 |

|

SU1803909A1 |

УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ п ДВОИЧНЫХ ЧИСЕЛ по авт. св. № 798811, отличающееся тем, что, с целью повышения быстродействия, в него введены вторая группа элементов И, второй элемент ИЛИ, вторая группа триггеров, элемент НЕ, элемент -ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй узлы формирования результата, причем каждый (п + 1)-й информационный вход устройства подключен к первому входу i-ro элемента И второй группы и к первому входу установки в нулевое состояние i-ro триггера второй группы, выход которого подключен к второму входу i-ro элемента И второй группы, выходы элементов И второй группы соединены с входами второго элемента ИЛИ, выход которого соединен с вторыми входами установки в нулевое состояние всех триггеров второй группы, третьи входы установки в нулевое состояние всех триггеров второй группы подключены к шине синхронизации устройства, третий вход i-ro элемента И второй группы соединен с выходом i-ro триггера первой группы и i-м входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с выходом индикации выделения экстремального числа, выходы первого и второго элементов ИЛИ соединены с первыми входами соответственно первого и второго узлов формирования результата, вторые входы которых соединены с шиной выбора режима устройства и с входом элемента НЕ, выход которого соединен с третьими входами узлов формирования результата, выходы которых соединены с информационными выходами устройства, причем узел формирования результата содержит первый и второй (Л элементы И и элемент ИЛИ, выход которого соединен с выходом узла формирования результата, а входы соединены с выходами первого и второго элементов И, первый вход первого элемента И соединен с первым входом узла формирования результата и с инверсным входом второго элемента И, вторые входы первого и второго элементов И соединены соответственно с вторым и третьим входами узла формирования результата. со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сравнения двоич-НыХ чиСЕл | 1979 |

|

SU798811A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-05-07—Публикация

1983-01-14—Подача